#### NXP USA Inc. - MC9S08SH16CTGR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh16ctgr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08SH32 Series. | 19 |

|-----|-----------------------------------|----|

| 1.2 | MCU Block Diagram                 | 20 |

|     | System Clock Distribution         |    |

### Chapter 2 Pins and Connections

| 2.1 | Device | Pin Assignment                           |  |

|-----|--------|------------------------------------------|--|

|     |        | mended System Connections                |  |

|     |        | Power                                    |  |

|     | 2.2.2  | Oscillator (XOSC)                        |  |

|     |        | RESET                                    |  |

|     | 2.2.4  | Background / Mode Select (BKGD/MS)       |  |

|     | 2.2.5  | General-Purpose I/O and Peripheral Ports |  |

## Chapter 3 Modes of Operation

| Introdu  | etion                                                                  | 31                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feature  | 3                                                                      | 31                                                                                                                                                                                  |

| Run Mo   | de                                                                     | 31                                                                                                                                                                                  |

| Active 1 | Background Mode                                                        | 31                                                                                                                                                                                  |

|          |                                                                        |                                                                                                                                                                                     |

| Stop M   | odes                                                                   | 32                                                                                                                                                                                  |

| -        |                                                                        |                                                                                                                                                                                     |

|          | 1                                                                      |                                                                                                                                                                                     |

|          | ±                                                                      |                                                                                                                                                                                     |

|          | Features<br>Run Mo<br>Active H<br>Wait Mo<br>Stop Mo<br>3.6.1<br>3.6.2 | Introduction<br>Features<br>Run Mode<br>Active Background Mode<br>Wait Mode<br>Stop Modes<br>3.6.1 Stop3 Mode<br>3.6.2 Stop2 Mode<br>3.6.3 On-Chip Peripheral Modules in Stop Modes |

### Chapter 4 Memory

| 4.1 | MC9S0    | 8SH32 Series Memory Map         | . 37 |

|-----|----------|---------------------------------|------|

| 4.2 | Reset an | nd Interrupt Vector Assignments | . 38 |

| 4.3 | Register | Addresses and Bit Assignments   | . 39 |

|     | -        | ~                               |      |

| 4.5 | FLASH    |                                 | . 46 |

|     | 4.5.1    | Features                        | . 47 |

|     | 4.5.2    | Program and Erase Times         | . 47 |

|     |          |                                 |      |

#### **Chapter 4 Memory**

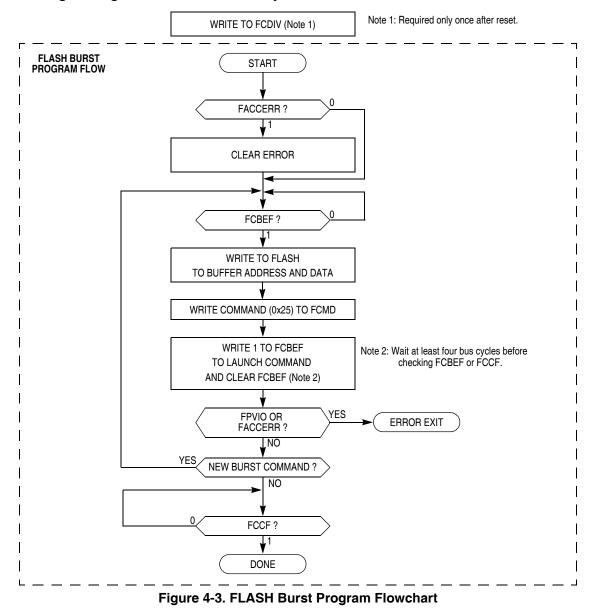

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

The status flag corresponding to the interrupt source must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

### 5.5.2 External Interrupt Request Pin (IRQ)

External interrupts are managed by the IRQ status and control register, IRQSC. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

### 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in IRQSC must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

The IRQ pin, when enabled, defaults to use an internal pull device (IRQPDD = 0), the device is a pull-up or pull-down depending on the polarity chosen. If the user desires to use an external pull-up or pull-down, the IRQPDD can be written to a 1 to turn off the internal device.

BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

#### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ .

The voltage measured on the internally pulled up IRQ pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the IRQ pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In the edge and level detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

### 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

#### Chapter 5 Resets, Interrupts, and General System Control

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction; stack the PCL, PCH, X, A, and CCR CPU registers; set the I bit; and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

| Vector<br>Priority | Vector<br>Number                   | Address<br>(High/Low) | Vector<br>Name | Module         | Source                                        | Enable                           | Description                                                            |  |

|--------------------|------------------------------------|-----------------------|----------------|----------------|-----------------------------------------------|----------------------------------|------------------------------------------------------------------------|--|

|                    | 31                                 | 0xFFC0/0xFFC1         | —              | —              | —                                             | _                                | —                                                                      |  |

| Lowest             | 30                                 | 0xFFC2/0xFFC3         | Vacmp          | ACMP           | ACF                                           | ACIE                             | Analog comparator                                                      |  |

| Lowest             | 29                                 | 0xFFC4/0xFFC5         | —              | _              | —                                             | —                                | —                                                                      |  |

|                    | 28                                 | 0xFFC6/0xFFC7         | _              |                | —                                             | —                                | —                                                                      |  |

|                    | 27                                 | 0xFFC8/0xFFC9         | —              |                | —                                             | —                                | —                                                                      |  |

|                    | 26                                 | 0xFFCA/0xFFCB         | Vmtim          | MTIM           | TOF                                           | TOIE                             | MTIM overflow                                                          |  |

|                    | 25                                 | 0xFFCC/0xFFCD         | Vrtc           | RTC            | RTIF                                          | RTIE                             | Real-time interrupt                                                    |  |

|                    | 24                                 | 0xFFCE/0xFFCF         | Viic           | IIC            | IICIS                                         | IICIE                            | IIC control                                                            |  |

|                    | 23                                 | 0xFFD0/0xFFD1         | Vadc           | ADC            | COCO                                          | AIEN                             | ADC                                                                    |  |

|                    | 22                                 | 0xFFD2/0xFFD3         | —              | _              | _                                             | _                                | _                                                                      |  |

|                    | 21                                 | 0xFFD4/0xFFD5         | Vportb         | Port B         | PTBIF                                         | PTBIE                            | Port B Pins                                                            |  |

|                    | 20                                 | 0xFFD6/0xFFD7         | Vporta         | Port A         | PTAIF                                         | PTAIE                            | Port A Pins                                                            |  |

|                    | 19                                 | 0xFFD8/0xFFD9         |                |                | _                                             |                                  | _                                                                      |  |

|                    | 18                                 | 0xFFDA/0xFFDB         | Vscitx         | SCI            | TDRE, TC                                      | TIE, TCIE                        | SCI transmit                                                           |  |

|                    | 17                                 | 0xFFDC/0xFFDD         | Vscirx         | SCI            | IDLE, RDRF,<br>LDBKDIF,<br>RXEDGIF            | ILIE, RIE,<br>LBKDIE,<br>RXEDGIE | SCI receive                                                            |  |

|                    | 16                                 | 0xFFDE/0xFFDF         | Vscierr        | SCI            | OR, NF,<br>FE, PF                             | ORIE, NFIE,<br>FEIE, PFIE        | SCI error                                                              |  |

|                    | 15                                 | 0xFFE0/0xFFE1         | Vspi           | SPI            | SPIF, MODF,<br>SPTEF                          | SPIE, SPIE, SPTIE                | SPI                                                                    |  |

|                    | 14                                 | 0xFFE2/0xFFE3         | Vtpm2ovf       | TPM2           | TOF                                           | TOIE                             | TPM2 overflow                                                          |  |

|                    | 13                                 | 0xFFE4/0xFFE5         | Vtpm2ch1       | TPM2           | CH1F                                          | CH1IE                            | TPM2 channel 1                                                         |  |

|                    | 12                                 | 0xFFE6/0xFFE7         | Vtpm2ch0       | TPM2           | CH0F                                          | CH0IE                            | TPM2 channel 0                                                         |  |

|                    | 11 0xFFE8/0xFFE9 Vtpm1ovf TPM1 TOF |                       | TOIE           | TPM1 overflow  |                                               |                                  |                                                                        |  |

|                    | 10                                 | 0xFFEA/0xFFEB         | —              | —              | —                                             | _                                | —                                                                      |  |

|                    | 9                                  | 0xFFEC/0xFFED         | —              | —              | —                                             | _                                | —                                                                      |  |

|                    | 8                                  | 0xFFEE/0xFFEF         | —              | _              | —                                             | _                                | —                                                                      |  |

|                    | 7                                  | 0xFFF0/0xFFF1         | —              | _              | —                                             | —                                | —                                                                      |  |

|                    | 6                                  | 0xFFF2/0xFFF3         | Vtpm1ch1       | TPM1           | CH1F                                          | CH1IE                            | TPM1 channel 1                                                         |  |

|                    | 5                                  | 0xFFF4/0xFFF5         | Vtpm1ch0       | TPM1           | CH0F                                          | CHOIE                            | TPM1 channel 0                                                         |  |

|                    | 4                                  | 0xFFF6/0xFFF7         | —              | _              | —                                             | —                                | —                                                                      |  |

|                    | 3                                  | 0xFFF8/0xFFF9         | Vlvd           | System control | LVWF                                          | LVWIE                            | Low-voltage warning                                                    |  |

|                    | 2                                  | 0xFFFA/0xFFFB         | Virq           | IRQ            | IRQF                                          | IRQIE                            | IRQ pin                                                                |  |

|                    | 1                                  | 0xFFFC/0xFFFD         | Vswi           | Core           | SWI Instruction                               | —                                | Software interrupt                                                     |  |

|                    | 0                                  | 0xFFFE/0xFFFF         | Vreset         | System control | COP,<br>LVD,<br>RESET pin,<br>Illegal opcode, | COPE<br>LVDRE<br>                | Watchdog timer<br>Low-voltage detect<br>External pin<br>Illegal opcode |  |

| Highest            |                                    |                       |                |                | Illegal address                               |                                  | Illegal address                                                        |  |

#### Table 5-2. Vector Summary

Chapter 6 Parallel Input/Output Control

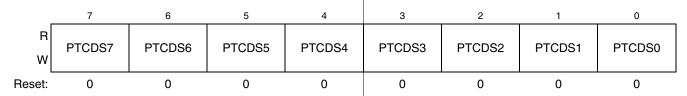

## 6.6.3.5 Port C Drive Strength Selection Register (PTCDS)

Figure 6-23. Drive Strength Selection for Port C Register (PTCDS)

#### Table 6-22. PTCDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCDS[7:0] | <ul> <li>Output Drive Strength Selection for Port C Bits — Each of these control bits selects between low and high output drive for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port C bit n.</li> <li>1 High output drive strength selected for port C bit n.</li> </ul> |

### 6.6.3.6 Ganged Output Drive Control Register (GNGC)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0     |

|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| R<br>W | GNGPS7 | GNGPS6 | GNGPS5 | GNGPS4 | GNGPS3 | GNGPS2 | GNGPS1 | GNGEN |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0     |

Figure 6-24. Ganged Output Drive Control Register (GNGC)

#### Table 6-23. GNGC Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>GNGP[7:1] | <ul> <li>Ganged Output Pin Select Bits— These write-once control bits selects whether the associated pin (see Table 6-1 for pins available) is enabled for ganged output. When GNGEN = 1, all enabled ganged output pins will be controlled by the data, drive strength and slew rate settings for PTCO.</li> <li>O Associated pin is not part of the ganged output drive.</li> <li>1 Associated pin is part of the ganged output drive. Requires GNGEN = 1.</li> </ul> |

| 0<br>GNGEN       | <ul> <li>Ganged Output Drive Enable Bit— This write-once control bit selects whether the ganged output drive feature is enabled.</li> <li>0 Ganged output drive disabled.</li> <li>1 Ganged output drive enabled. PTC0 forced to output regardless of the value of PTCDD0 in PTCDD.</li> </ul>                                                                                                                                                                          |

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

## 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

## 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

## 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

### 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

## 7.4.1 Reset Sequence

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction boundary before responding to a reset event). For a more detailed discussion about how the MCU recognizes resets and determines the source, refer to the Resets, Interrupts, and System Configuration chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the instruction queue in preparation for execution of the first program instruction.

### 7.4.2 Interrupt Sequence

When an interrupt is requested, the CPU completes the current instruction before responding to the interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence started.

The CPU sequence for an interrupt is:

- 1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

- 2. Set the I bit in the CCR.

- 3. Fetch the high-order half of the interrupt vector.

- 4. Fetch the low-order half of the interrupt vector.

- 5. Delay for one free bus cycle.

- 6. Fetch three bytes of program information starting at the address indicated by the interrupt vector to fill the instruction queue in preparation for execution of the first instruction in the interrupt service routine.

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

# 8.7 Functional Description

The analog comparator can be used to compare two analog input voltages applied to ACMP+ and ACMP-; or it can be used to compare an analog input voltage applied to ACMP- with an internal bandgap reference voltage. ACBGS is used to select between the bandgap reference voltage or the ACMP+ pin as the input to the non-inverting input of the analog comparator. The comparator output is high when the non-inverting input is greater than the inverting input, and is low when the non-inverting input is less than the inverting input. ACMOD is used to select the condition which will cause ACF to be set. ACF can be set on a rising edge of the comparator output, a falling edge of the comparator output, or either a rising or a falling edge (toggle). The comparator output can be read directly through ACO. The comparator output can be driven onto the ACMPO pin using ACOPE.

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

| ADCH  | Input Select |

|-------|--------------|

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

#### Figure 9-4. Input Channel Select (continued)

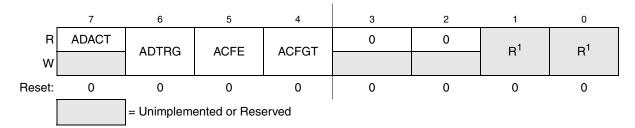

## 9.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

#### Figure 9-5. Status and Control Register 2 (ADCSC2)

#### Table 9-4. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | <ul> <li>Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>0 Conversion not in progress</li> <li>1 Conversion in progress</li> </ul>                                                                                                                                                                                                                              |

| 6<br>ADTRG | <ul> <li>Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion.</li> <li>Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.</li> <li>Software trigger selected</li> <li>Hardware trigger selected</li> </ul> |

| ADICLK | Selected Clock Source      |  |  |  |  |  |

|--------|----------------------------|--|--|--|--|--|

| 00     | Bus clock                  |  |  |  |  |  |

| 01     | Bus clock divided by 2     |  |  |  |  |  |

| 10     | Alternate clock (ALTCLK)   |  |  |  |  |  |

| 11     | Asynchronous clock (ADACK) |  |  |  |  |  |

#### Table 9-8. Input Clock Select

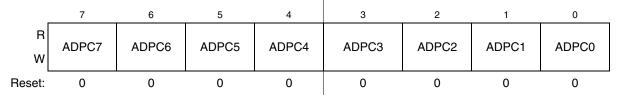

#### Pin Control 1 Register (APCTL1) 9.3.8

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

## 9.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

### 9.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

## 9.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

### 9.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 9-12.

| Conversion Type                                            | ADICLK | ADLSMP | Max Total Conversion Time                |

|------------------------------------------------------------|--------|--------|------------------------------------------|

| Single or first continuous 8-bit                           | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 0      | 5 $\mu$ s + 20 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 1      | 5 $\mu$ s + 40 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 1      | 5 $\mu$ s + 43 ADCK + 5 bus clock cycles |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}$     | xx     | 0      | 17 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}$    | xx     | 0      | 20 ADCK cycles                           |

| Subsequent continuous 8-bit; $f_{BUS} \ge f_{ADCK}/11$     | xx     | 1      | 37 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}/11$ | xx     | 1      | 40 ADCK cycles                           |

Table 9-12. Total Conversion Time vs. Control Conditions

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1 ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

Conversion time =  $\frac{23 \text{ ADCK cyc}}{8 \text{ MHz/1}} + \frac{5 \text{ bus cyc}}{8 \text{ MHz}} = 3.5 \text{ }\mu\text{s}$

Number of bus cycles =  $3.5 \ \mu s \ x \ 8 \ MHz = 28 \ cycles$

### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet ADC specifications.

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

# 9.4.5 Automatic Compare Function

The compare function can be configured to check for either an upper limit or lower limit. After the input is sampled and converted, the result is added to the two's complement of the compare value (ADCCVH and ADCCVL). When comparing to an upper limit (ACFGT = 1), if the result is greater-than or equal-to the compare value, COCO is set. When comparing to a lower limit (ACFGT = 0), if the result is less than the compare value, COCO is set. The value generated by the addition of the conversion result and the two's complement of the compare value is transferred to ADCRH and ADCRL.

Upon completion of a conversion while the compare function is enabled, if the compare condition is not true, COCO is not set and no data is transferred to the result registers. An ADC interrupt is generated upon the setting of COCO if the ADC interrupt is enabled (AIEN = 1).

### NOTE

The compare function can be used to monitor the voltage on a channel while the MCU is in either wait or stop3 mode. The ADC interrupt will wake the MCU when the compare condition is met.

## 9.4.6 MCU Wait Mode Operation

The WAIT instruction puts the MCU in a lower power-consumption standby mode from which recovery is very fast because the clock sources remain active. If a conversion is in progress when the MCU enters wait mode, it continues until completion. Conversions can be initiated while the MCU is in wait mode by means of the hardware trigger or if continuous conversions are enabled.

The bus clock, bus clock divided by two, and ADACK are available as conversion clock sources while in wait mode. The use of ALTCLK as the conversion clock source in wait is dependent on the definition of ALTCLK for this MCU. Consult the module introduction for information on ALTCLK specific to this MCU.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from wait mode if the ADC interrupt is enabled (AIEN = 1).

## 9.4.7 MCU Stop3 Mode Operation

The STOP instruction is used to put the MCU in a low power-consumption standby mode during which most or all clock sources on the MCU are disabled.

## 9.4.7.1 Stop3 Mode With ADACK Disabled

If the asynchronous clock, ADACK, is not selected as the conversion clock, executing a STOP instruction aborts the current conversion and places the ADC in its idle state. The contents of ADCRH and ADCRL are unaffected by stop3 mode. After exiting from stop3 mode, a software or hardware trigger is required to resume conversions.

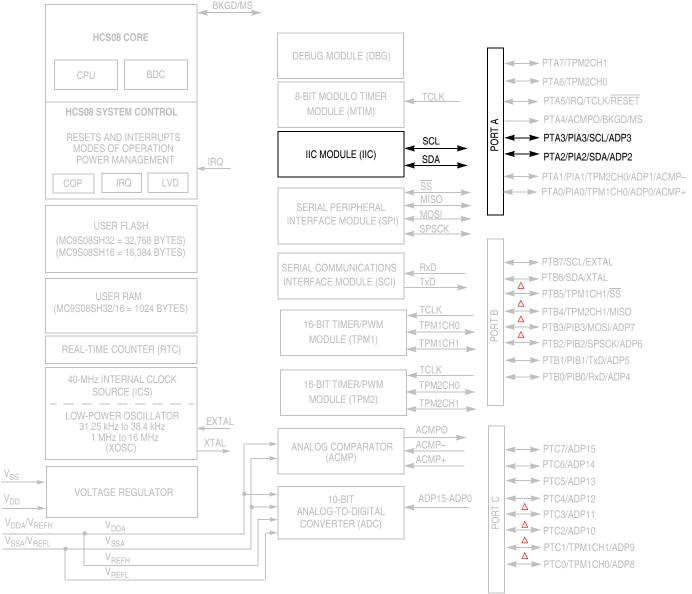

$\triangle$  = Pin can be enabled as part of the ganged output drive feature

- NOTE: PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages: V<sub>DDA</sub>/V<sub>REFH</sub> and V<sub>SSA</sub>/V<sub>REFL</sub> , are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 10-1. MC9S08SH32 Series Block Diagram Highlighting IIC Block and Pins

## 10.4.1.5 Repeated Start Signal

As shown in Figure 10-9, a repeated start signal is a start signal generated without first generating a stop signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

## 10.4.1.6 Arbitration Procedure

The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

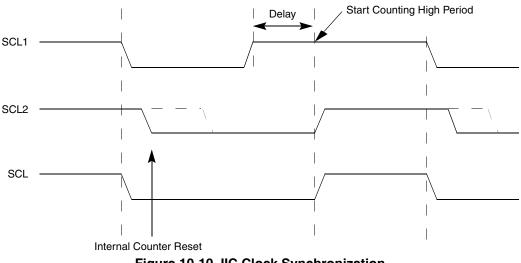

### 10.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 10-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 10-10. IIC Clock Synchronization

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0 Transmitter active (sending data, a preamble, or a break).         1 Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:         • Write to the SCI data register (SCIxD) to transmit new data         • Queue a preamble by changing TE from 0 to 1         • Queue a break character by writing 1 to SBK in SCIxC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). To clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD).</li> <li>0 Receive data register empty.</li> <li>1 Receive data register full.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of<br>activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is<br>all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times<br>depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't<br>start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the<br>previous character do not count toward the full character time of logic high needed for the receiver to detect an<br>idle line.To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been<br>cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE<br>will get set only once even if the receive line remains idle for an extended period.0No idle line detected.1Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Table 14-5. SCIxS1 Field Descriptions

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuration                                 |

|-------|-----------|-------------|-----------------------|-----------------------------------------------|

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                   |

|       |           | 10          |                       | Capture on falling edge only                  |

|       |           | 11          |                       | Capture on rising or<br>falling edge          |

|       | 01        | 01          | Output compare        | Toggle output on<br>compare                   |

|       |           | 10          |                       | Clear output on compare                       |

|       |           | 11          |                       | Set output on compare                         |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear<br>output on compare) |

|       |           | X1          |                       | Low-true pulses (set output on compare)       |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up) |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)    |

| Table 16-7. | Mode, | Edge, | and | Level | Selection |

|-------------|-------|-------|-----|-------|-----------|

|-------------|-------|-------|-----|-------|-----------|

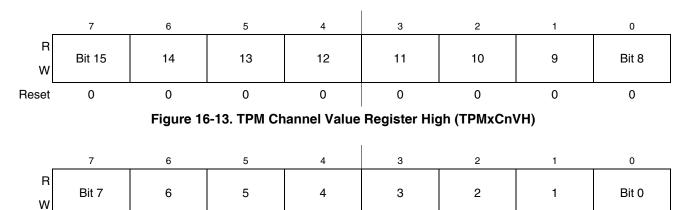

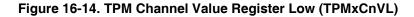

### 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

0

0

0

0

In input capture mode, reading either byte (TPMxCnVH or TPMxCnVL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This latching mechanism also resets

0

Reset

0

0

0

#### Chapter 17 Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 17.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

## 17.4.3.5 Debug FIFO High Register (DBGFH)

This register provides read-only access to the high-order eight bits of the FIFO. Writes to this register have no meaning or effect. In the event-only trigger modes, the FIFO only stores data into the low-order byte of each FIFO word, so this register is not used and will read 0x00.

Reading DBGFH does not cause the FIFO to shift to the next word. When reading 16-bit words out of the FIFO, read DBGFH before reading DBGFL because reading DBGFL causes the FIFO to advance to the next word of information.

## 17.4.3.6 Debug FIFO Low Register (DBGFL)

This register provides read-only access to the low-order eight bits of the FIFO. Writes to this register have no meaning or effect.

Reading DBGFL causes the FIFO to shift to the next available word of information. When the debug module is operating in event-only modes, only 8-bit data is stored into the FIFO (high-order half of each FIFO word is unused). When reading 8-bit words out of the FIFO, simply read DBGFL repeatedly to get successive bytes of data from the FIFO. It isn't necessary to read DBGFH in this case.

Do not attempt to read data from the FIFO while it is still armed (after arming but before the FIFO is filled or ARMF is cleared) because the FIFO is prevented from advancing during reads of DBGFL. This can interfere with normal sequencing of reads from the FIFO.

Reading DBGFL while the debugger is not armed causes the address of the most-recently fetched opcode to be stored to the last location in the FIFO. By reading DBGFH then DBGFL periodically, external host software can develop a profile of program execution. After eight reads from the FIFO, the ninth read will return the information that was stored as a result of the first read. To use the profiling feature, read the FIFO eight times without using the data to prime the sequence and then begin using the data to get a delayed picture of what addresses were being executed. The information stored into the FIFO on reads of DBGFL (while the FIFO is not armed) is the address of the most-recently fetched opcode.

| # | Characteristic                                          | Conditions                    | С  | Symb                                   | Min  | Typ <sup>1</sup> | Max  | Unit             | Comment                                                |

|---|---------------------------------------------------------|-------------------------------|----|----------------------------------------|------|------------------|------|------------------|--------------------------------------------------------|

| 1 | Supply current                                          | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | т  | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 133              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | т  | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 218              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | т  | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Ρ  | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.58<br>2        | 1    | mA               | ADC current<br>only                                    |

|   | ADC<br>asynchronous<br>clock source                     | High speed (ADLPC=0)          | Р  | f <sub>ADACK</sub>                     | 2    | 3.3              | 5    | MHz              | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub>           |

| 2 |                                                         | Low power (ADLPC=1)           |    |                                        | 1.25 | 2                | 3.3  |                  |                                                        |

| 3 | Conversion<br>time (including<br>sample time)           | Short sample<br>(ADLSMP=0)    | D  | t <sub>ADC</sub>                       |      | 20               | _    | ADCK<br>cycles   | See ADC<br>Chapter for<br>conversion<br>time variances |

| 3 |                                                         | Long sample<br>(ADLSMP=1)     |    |                                        | _    | 40               | _    |                  |                                                        |

| 4 | Sample time                                             | Short sample<br>(ADLSMP=0)    | D  | t <sub>ADS</sub>                       | _    | 3.5              | _    | ADCK<br>cycles   |                                                        |

|   |                                                         | Long sample<br>(ADLSMP=1)     |    |                                        |      | 23.5             | —    |                  |                                                        |

|   |                                                         | 28-pin packages only          |    |                                        |      |                  |      |                  |                                                        |

|   | Total<br>unadjusted<br>error (includes<br>quantization) | 10-bit mode                   |    | E <sub>TUE</sub>                       | _    | ±1               | ±2.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    | Ρ  |                                        | _    | ±0.5             | ±1   |                  |                                                        |

|   |                                                         | 20-pin packages               |    |                                        |      | •                |      |                  |                                                        |

| 5 |                                                         | 10-bit mode                   | Р  | _                                      |      | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    | r- | E <sub>TUE</sub>                       |      | ±0.7             | ±1.5 | LOD              |                                                        |

|   |                                                         | 16-pin packages               |    |                                        |      |                  |      |                  |                                                        |

|   |                                                         | 10-bit mode                   | P  | E <sub>TUE</sub>                       | _    | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    |    |                                        |      | ±0.7             | ±1.5 |                  |                                                        |