Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh16ctj |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08SH32 Data Sheet

Covers MC9S08SH32 MC9S08SH16

> MC9S08SH32 Rev. 3 3/2014

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2007-2014. All rights reserved.

# **Section Number**

Title

### Page

| 17.2 Background Debug Controller (BDC)                      |  |

|-------------------------------------------------------------|--|

| 17.2.1 BKGD Pin Description                                 |  |

| 17.2.2 Communication Details                                |  |

| 17.2.3 BDC Commands                                         |  |

| 17.2.4 BDC Hardware Breakpoint                              |  |

| 17.3 On-Chip Debug System (DBG)                             |  |

| 17.3.1 Comparators A and B                                  |  |

| 17.3.2 Bus Capture Information and FIFO Operation           |  |

| 17.3.3 Change-of-Flow Information                           |  |

| 17.3.4 Tag vs. Force Breakpoints and Triggers               |  |

| 17.3.5 Trigger Modes                                        |  |

| 17.3.6 Hardware Breakpoints                                 |  |

| 17.4 Register Definition                                    |  |

| 17.4.1 BDC Registers and Control Bits                       |  |

| 17.4.2 System Background Debug Force Reset Register (SBDFR) |  |

| 17.4.3 DBG Registers and Control Bits                       |  |

| -                                                           |  |

# Appendix A Electrical Characteristics

| A.1  | Introduction                                |     |

|------|---------------------------------------------|-----|

| A.2  | Parameter Classification                    |     |

| A.3  | Absolute Maximum Ratings                    |     |

| A.4  | Thermal Characteristics                     |     |

| A.5  | ESD Protection and Latch-Up Immunity        |     |

| A.6  | DC Characteristics                          |     |

| A.7  | Supply Current Characteristics              | 292 |

| A.8  | External Oscillator (XOSC) Characteristics  | 296 |

| A.9  | Internal Clock Source (ICS) Characteristics | 298 |

| A.10 | Analog Comparator (ACMP) Electricals        | 299 |

| A.11 | ADC Characteristics                         | 300 |

| A.12 | AC Characteristics                          | 304 |

|      | A.12.1 Control Timing                       |     |

|      | A.12.2 TPM/MTIM Module Timing               | 306 |

|      | A.12.3 SPI                                  | 307 |

| A.13 | Flash Specifications                        | 310 |

| A.14 | EMC Performance                             |     |

|      | A.14.1 Radiated Emissions                   |     |

|      |                                             |     |

# Appendix B Ordering Information and Mechanical Drawings

| B.1 | Orderin | g Information           | 313 | , |

|-----|---------|-------------------------|-----|---|

|     |         | Device Numbering Scheme |     |   |

# 2.2.3 **RESET**

After a power-on reset (POR), the PTA5/IRQ/TCLK/RESET pin defaults to a general-purpose I/O port pin, PTA5. Setting RSTPE in SOPT1 configures the pin to be the RESET pin with an open-drain drive containing an internal pull-up device. After configured as RESET, the pin will remain RESET until the next POR. The RESET pin when enabled can be used to reset the MCU from an external source when the pin is driven low.

Internal power-on reset and low-voltage reset circuitry typically make external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background debug connector so a development system can directly reset the MCU system. If desired, a manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

Whenever any non-POR reset is initiated (whether from an external signal or from an internal system), the  $\overline{\text{RESET}}$  pin if enabled is driven low for about 66 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ .

The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### NOTE

In EMC-sensitive applications, an external RC filter is recommended on the  $\overline{\text{RESET}}$  pin. See Figure 2-4 for an example.

### 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.3, "System Background Debug Force Reset Register (SBDFR)," for more information), the PTA4/ACMPO/BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. When enabled as the BKGD/MS pin (BKGDPE = 1), an internal pullup device is automatically enabled.

The background debug communication function is enabled when BKGDPE in SOPT1 is set. BKGDPE is set following any reset of the MCU and must be cleared to use the PTA4/ACMPO/BKGD/MS pin's alternative pin function.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

#### **Chapter 3 Modes of Operation**

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After entering background debug mode, all background commands are available.

### 3.6.2 Stop2 Mode

Stop2 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. Most of the internal circuitry of the MCU is powered off in stop2 with the exception of the RAM. Upon entering stop2, all I/O pin control signals are latched so that the pins retain their states during stop2.

Exit from stop2 is performed by asserting the wake-up pin (PTA5/IRQ/TCLK/RESET) on the MCU.

In addition, the real-time counter (RTC) can wake the MCU from stop2, if enabled.

Upon wake-up from stop2 mode, the MCU starts up as from a power-on reset (POR):

- All module control and status registers are reset

- The LVD reset function is enabled and the MCU remains in the reset state if V<sub>DD</sub> is below the LVD trip point (low trip point selected due to POR)

- The CPU takes the reset vector

In addition to the above, upon waking up from stop2, the PPDF bit in SPMSC2 is set. This flag is used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

To maintain I/O states for pins that were configured as general-purpose I/O before entering stop2, the user must restore the contents of the I/O port registers, which have been saved in RAM, to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the pins will switch to their reset states when PPDACK is written.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

### 3.6.3 On-Chip Peripheral Modules in Stop Modes

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even in the exception case (ENBDM = 1), where clocks to the background debug logic continue to operate, clocks to the peripheral systems are halted to reduce power consumption. Refer to Section 3.6.2, "Stop2 Mode," and Section 3.6.1, "Stop3 Mode," for specific information on system behavior in stop modes.

Chapter 4 Memory

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x1845            | PTAPS         | 0      | 0      | 0      | 0      | PTAPS3 | PTAPS2 | PTAPS1 | PTAPS0 |

| 0x1846            | PTAES         | 0      | 0      | 0      | 0      | PTAES3 | PTAES2 | PTAES1 | PTAES0 |

| 0x1847            | Reserved      | _      | —      | —      | —      | —      | _      | _      | —      |

| 0x1848            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1849            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x184A            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x184B            | Reserved      | _      | —      | —      | —      | —      | _      | _      | —      |

| 0x184C            | PTBSC         | 0      | 0      | 0      | 0      | PTBIF  | PTBACK | PTBIE  | PTBMOD |

| 0x184D            | PTBPS         | 0      | 0      | 0      | 0      | PTBPS3 | PTBPS2 | PTBPS1 | PTBPS0 |

| 0x184E            | PTBES         | 0      | 0      | 0      | 0      | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| 0x184F            | Reserved      | _      | —      | —      | —      | —      | _      | _      | —      |

| 0x1850            | PTCPE         | PTCPE7 | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1851            | PTCSE         | PTCSE7 | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x1852            | PTCDS         | PTCDS7 | PTCDS6 | PTCDS5 | PTCDS4 | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x1853            | GNGC          | GNGPS7 | GNGPS6 | GNGPS5 | GNGPS4 | GNGPS3 | GNGPS2 | GNGPS1 | GNGEN  |

| 0x1854            | Reserved      | _      | —      | —      | —      | —      | 1      | 1      | 1      |

| 0x1855            | Reserved      | _      | —      | —      | —      | —      | 1      | 1      | 1      |

| 0x1856            | Reserved      | —      |        | —      | —      | —      | 0      | 0      | 0      |

| 0x1857–<br>0x185F | Reserved      | _      | —      | —      | _      | —      | —      | —      | _      |

### Table 4-3. High-Page Register Summary (Sheet 2 of 2)

# 4.4 RAM

The MC9S08SH32 Series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention ( $V_{RAM}$ ).

For compatibility with M68HC05 MCUs, the HCS08 resets the stack pointer to 0x00FF. In the MC9S08SH32 Series, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale Semiconductor-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.6, "Security", for a detailed description of the security feature.

# 4.5 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I,* Freescale Semiconductor document order number HCS08RMv1/D.

must be programmed to logic 0 to enable block protection. Therefore the value 0xF8 must be programmed into NVPROT to protect addresses 0xFA00 through 0xFFFF.

### Figure 4-4. Block Protection Mechanism

One use for block protection is to block protect an area of FLASH memory for a bootloader program. This bootloader program then can be used to erase the rest of the FLASH memory and reprogram it. Because the bootloader is protected, it remains intact even if MCU power is lost in the middle of an erase and reprogram operation.

# 4.5.7 Vector Redirection

Whenever any block protection is enabled, the reset and interrupt vectors will be protected. Vector redirection allows users to modify interrupt vector information without unprotecting bootloader and reset vector space. Vector redirection is enabled by programming the FNORED bit in the NVOPT register located at address 0xFFBF to zero. For redirection to occur, at least some portion but not all of the FLASH memory must be block protected by programming the NVPROT register located at address 0xFFBD. All of the interrupt vectors (memory locations 0xFFC0–0xFFFD) are redirected, though the reset vector (0xFFFE:FFFF) is not.

For example, if 512 bytes of FLASH are protected, the protected address region is from 0xFE00 through 0xFFFF. The interrupt vectors (0xFFC0–0xFFFD) are redirected to the locations 0xFDC0–0xFDFD. Now, if an SPI interrupt is taken for instance, the values in the locations 0xFDE0:FDE1 are used for the vector instead of the values in the locations 0xFFE0:FFE1. This allows the user to reprogram the unprotected portion of the FLASH with new program code including new interrupt vector values while leaving the protected area, which includes the default vector locations, unchanged.

# 4.6 Security

The MC9S08SH32 Series includes circuitry to prevent unauthorized access to the contents of FLASH and RAM memory. When security is engaged, FLASH and RAM are considered secure resources. Direct-page registers, high-page registers, and the background debug controller are considered unsecured resources. Programs executing within secure memory have normal access to any MCU memory locations and resources. Attempts to access a secure memory location with a program executing from an unsecured memory space or through the background debug interface are blocked (writes are ignored and reads return all 0s).

Security is engaged or disengaged based on the state of two nonvolatile register bits (SEC01:SEC00) in the FOPT register. During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into the working FOPT register in high-page register space. A user engages security by programming the NVOPT location which can be done at the same time the FLASH memory is programmed. The 1:0 state disengages security and the other three combinations engage security. Notice the erased state (1:1) makes

Chapter 8 Analog Comparator (S08ACMPV3)

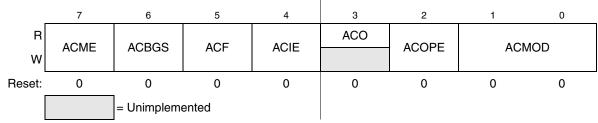

## 8.6.1.1 ACMP Status and Control Register (ACMPSC)

ACMPSC contains the status flag and control bits which are used to enable and configure the ACMP.

#### Figure 8-3. ACMP Status and Control Register

| Table 8-2. ACMP Status and Control Register Field Descriptions |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACME    | <ul> <li>Analog Comparator Module Enable — ACME enables the ACMP module.</li> <li>0 ACMP not enabled</li> <li>1 ACMP is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| 6<br>ACBGS   | <ul> <li>Analog Comparator Bandgap Select — ACBGS is used to select between the bandgap reference voltage or the ACMP+ pin as the input to the non-inverting input of the analog comparatorr.</li> <li>0 External pin ACMP+ selected as non-inverting input to comparator</li> <li>1 Internal reference select as non-inverting input to comparator</li> <li>Note: refer to this chapter introduction to verify if any other config bits are necessary to enable the bandgap reference in the chip level.</li> </ul> |

| 5<br>ACF     | <ul> <li>Analog Comparator Flag — ACF is set when a compare event occurs. Compare events are defined by ACMOD.</li> <li>ACF is cleared by writing a one to ACF.</li> <li>0 Compare event has not occurred</li> <li>1 Compare event has occurred</li> </ul>                                                                                                                                                                                                                                                           |

| 4<br>ACIE    | <ul> <li>Analog Comparator Interrupt Enable — ACIE enables the interrupt from the ACMP. When ACIE is set, an interrupt will be asserted when ACF is set.</li> <li>0 Interrupt disabled</li> <li>1 Interrupt enabled</li> </ul>                                                                                                                                                                                                                                                                                       |

| 3<br>ACO     | Analog Comparator Output — Reading ACO will return the current value of the analog comparator output. ACO is reset to a 0 and will read as a 0 when the ACMP is disabled (ACME = 0).                                                                                                                                                                                                                                                                                                                                 |

| 2<br>ACOPE   | <ul> <li>Analog Comparator Output Pin Enable — ACOPE is used to enable the comparator output to be placed onto the external pin, ACMPO.</li> <li>0 Analog comparator output not available on ACMPO</li> <li>1 Analog comparator output is driven out on ACMPO</li> </ul>                                                                                                                                                                                                                                             |

| 1:0<br>ACMOD | Analog Comparator Mode — ACMOD selects the type of compare event which sets ACF.<br>00 Encoding 0 — Comparator output falling edge<br>01 Encoding 1 — Comparator output rising edge<br>10 Encoding 2 — Comparator output falling edge<br>11 Encoding 3 — Comparator output rising or falling edge                                                                                                                                                                                                                    |

result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 9-12.

| Conversion Type                                            | ADICLK | ADLSMP | Max Total Conversion Time                |

|------------------------------------------------------------|--------|--------|------------------------------------------|

| Single or first continuous 8-bit                           | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 0      | 5 $\mu$ s + 20 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 1      | 5 μs + 40 ADCK + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 11     | 1      | 5 $\mu$ s + 43 ADCK + 5 bus clock cycles |

| Subsequent continuous 8-bit; $f_{BUS} \ge f_{ADCK}$        | xx     | 0      | 17 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}$    | xx     | 0      | 20 ADCK cycles                           |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}/11$  | xx     | 1      | 37 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}/11$ | xx     | 1      | 40 ADCK cycles                           |

Table 9-12. Total Conversion Time vs. Control Conditions

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1 ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

Conversion time =  $\frac{23 \text{ ADCK cyc}}{8 \text{ MHz/1}} + \frac{5 \text{ bus cyc}}{8 \text{ MHz}} = 3.5 \text{ }\mu\text{s}$

Number of bus cycles =  $3.5 \ \mu s \ x \ 8 \ MHz = 28 \ cycles$

### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet ADC specifications.

MC9S08SH32 Series Data Sheet, Rev. 3

# Chapter 10 Inter-Integrated Circuit (S08IICV2)

# 10.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

### NOTE

The SDA and SCL should not be driven above  $V_{DD}$ . These pins are pseudo open-drain containing a protection diode to  $V_{DD}$ .

### **10.1.1 Module Configuration**

The IIC module pins, SDA and SCL can be repositioned under software control using IICPS in SOPT1 as as shown in Table 10-1. IICPS in SOPT1 selects which general-purpose I/O ports are associated with IIC operation.

| IICPS in SOPT1 | Port Pin for SDA | Port Pin for SCL |

|----------------|------------------|------------------|

| 0 (default)    | PTA2             | PTA3             |

| 1              | PTB6             | PTB7             |

### Table 10-1. IIC Position Options

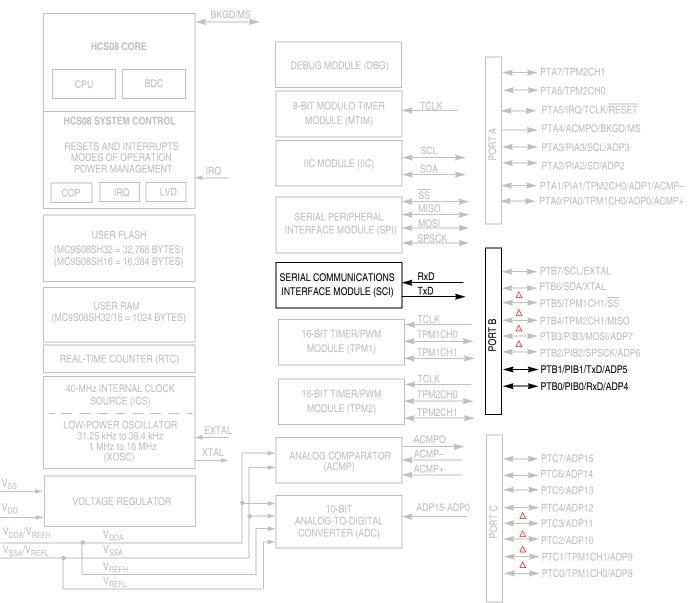

Figure 10-1 shows the MC9S08SH32 Series block diagram with the IIC module highlighted.

Inter-Integrated Circuit (S08IICV2)

| Table 10-8. IIC | D Field | Descriptions |

|-----------------|---------|--------------|

|-----------------|---------|--------------|

| Field | Description                                                                                                                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data</b> — In master transmit mode, when data is written to the IICD, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |

### NOTE

When transitioning out of master receive mode, the IIC mode should be switched before reading the IICD register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

The TX bit in IICC must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, reading the IICD does not initiate the receive.

Reading the IICD returns the last byte received while the IIC is configured in master receive or slave receive modes. The IICD does not reflect every byte transmitted on the IIC bus, nor can software verify that a byte has been written to the IICD correctly by reading it back.

In master transmit mode, the first byte of data written to IICD following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7 to bit 1) concatenated with the required  $R/\overline{W}$  bit (in position bit 0).

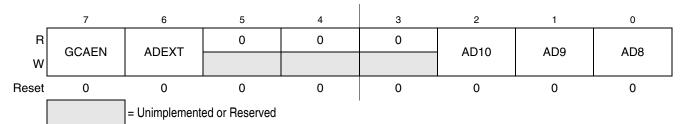

# 10.3.6 IIC Control Register 2 (IICC2)

### Figure 10-8. IIC Control Register (IICC2)

#### Table 10-9. IICC2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |  |

| 6<br>ADEXT      | Address Extension. The ADEXT bit controls the number of bits used for the slave address.         0       7-bit address scheme         1       10-bit address scheme                             |  |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |  |

#### MC9S08SH32 Series Data Sheet, Rev. 3

Chapter 12 Modulo Timer (S08MTIMV1)

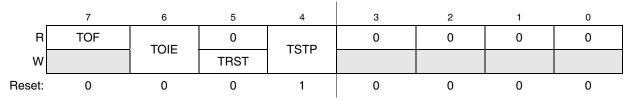

# 12.3.1 MTIM Status and Control Register (MTIMSC)

MTIMSC contains the overflow status flag and control bits which are used to configure the interrupt enable, reset the counter, and stop the counter.

#### Figure 12-4. MTIM Status and Control Register

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TOF  | <ul> <li>MTIM Overflow Flag — This read-only bit is set when the MTIM counter register overflows to \$00 after reaching the value in the MTIM modulo register. Clear TOF by reading the MTIMSC register while TOF is set, then writing a 0 to TOF. TOF is also cleared when TRST is written to a 1 or when any value is written to the MTIMMOD register.</li> <li>0 MTIM counter has not reached the overflow value in the MTIM modulo register.</li> <li>1 MTIM counter has reached the overflow value in the MTIM modulo register.</li> </ul> |  |  |  |  |  |

| 6<br>TOIE | <ul> <li>MTIM Overflow Interrupt Enable — This read/write bit enables MTIM overflow interrupts. If TOIE is set, then an interrupt is generated when TOF = 1. Reset clears TOIE. Do not set TOIE if TOF = 1. Clear TOF first, then set TOIE.</li> <li>0 TOF interrupts are disabled. Use software polling.</li> <li>1 TOF interrupts are enabled.</li> </ul>                                                                                                                                                                                     |  |  |  |  |  |

| 5<br>TRST | <ul> <li>MTIM Counter Reset — When a 1 is written to this write-only bit, the MTIM counter register resets to \$00 and TOF is cleared. Reading this bit always returns 0.</li> <li>0 No effect. MTIM counter remains at current state.</li> <li>1 MTIM counter is reset to \$00.</li> </ul>                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 4<br>TSTP | <ul> <li>MTIM Counter Stop — When set, this read/write bit stops the MTIM counter at its current value. Counting resumes from the current value when TSTP is cleared. Reset sets TSTP to prevent the MTIM from counting.</li> <li>0 MTIM counter is active.</li> <li>1 MTIM counter is stopped.</li> </ul>                                                                                                                                                                                                                                      |  |  |  |  |  |

| 3:0       | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

# 12.3.2 MTIM Clock Configuration Register (MTIMCLK)

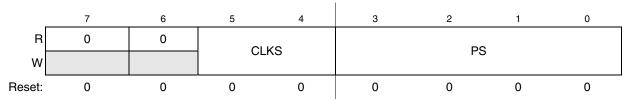

MTIMCLK contains the clock select bits (CLKS) and the prescaler select bits (PS).

Figure 12-5. MTIM Clock Configuration Register

### Table 12-3. MTIM Clock Configuration Register Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:6         | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 5:4<br>CLKS | Clock Source Select — These two read/write bits select one of four different clock sources as the input to the MTIM prescaler. Changing the clock source while the counter is active does not clear the counter. The count continues with the new clock source. Reset clears CLKS to 000.         00       Encoding 0. Bus clock (BUSCLK)         01       Encoding 1. Fixed-frequency clock (XCLK)         10       Encoding 3. External source (TCLK pin), falling edge         11       Encoding 4. External source (TCLK pin), rising edge         All other encodings default to the bus clock (BUSCLK).                                                                                   |  |  |  |  |  |

| 3:0<br>PS   | Clock Source Prescaler — These four read/write bits select one of nine outputs from the 8-bit prescaler.<br>Changing the prescaler value while the counter is active does not clear the counter. The count continues with the<br>new prescaler value. Reset clears PS to 0000.<br>0000 Encoding 0. MTIM clock source ÷ 1<br>0001 Encoding 1. MTIM clock source ÷ 2<br>0010 Encoding 2. MTIM clock source ÷ 4<br>0011 Encoding 3. MTIM clock source ÷ 8<br>0100 Encoding 4. MTIM clock source ÷ 16<br>0101 Encoding 5. MTIM clock source ÷ 32<br>0110 Encoding 6. MTIM clock source ÷ 128<br>1000 Encoding 8. MTIM clock source ÷ 256<br>All other encodings default to MTIM clock source ÷ 256. |  |  |  |  |  |

# Chapter 13 Real-Time Counter (S08RTCV1)

# 13.1 Introduction

The RTC module consists of one 8-bit counter, one 8-bit comparator, several binary-based and decimal-based prescaler dividers, two clock sources, and one programmable periodic interrupt. This module can be used for time-of-day, calendar or any task scheduling functions. It can also serve as a cyclic wake up from low power modes without the need of external components.

Chapter 14 Serial Communications Interface (S08SCIV4)

#### $\triangle$ = Pin can be enabled as part of the ganged output drive feature

NOTE: - PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages:  $V_{DDA}/V_{REFH}$  and  $V_{SSA}/V_{REFL}$ , are double bonded to  $V_{DD}$  and  $V_{SS}$  respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 14-1. MC9S08SH32 Series Block Diagram Highlighting SCI Block and Pins

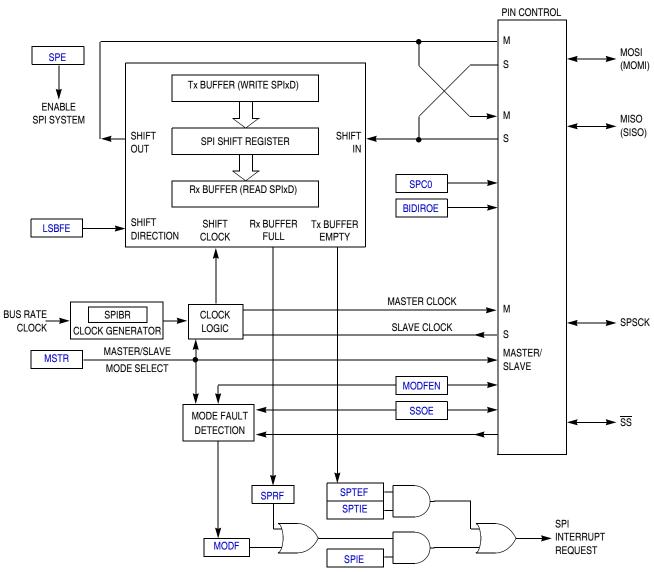

Chapter 15 Serial Peripheral Interface (S08SPIV3)

Figure 15-3. SPI Module Block Diagram

# 15.1.3 SPI Baud Rate Generation

As shown in Figure 15-4, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

# 17.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.

Chapter 17 Development Support

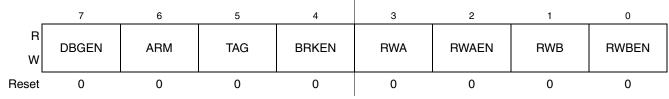

# 17.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 17-7. Debug Control Register (DBGC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>DBGEN | Debug Module Enable — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.<br>0 DBG disabled<br>1 DBG enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 6<br>ARM   | <ul> <li>Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If         BRKEN = 0, this bit has no meaning or effect.         0 CPU breaks requested as force type requests         1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 4<br>BRKEN | <ul> <li>Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests.</li> <li>O CPU break requests not enabled</li> <li>1 Triggers cause a break request to the CPU</li> </ul> |  |  |  |  |  |  |

| 3<br>RWA   | <ul> <li>R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A.</li> <li>0 Comparator A can only match on a write cycle</li> <li>1 Comparator A can only match on a read cycle</li> </ul>                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 2<br>RWAEN | <ul> <li>Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.</li> <li>0 R/W is not used in comparison A</li> <li>1 R/W is used in comparison A</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 1<br>RWB   | <ul> <li>R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.</li> <li>0 Comparator B can match only on a write cycle</li> <li>1 Comparator B can match only on a read cycle</li> </ul>                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 0<br>RWBEN | <ul> <li>Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.</li> <li>0 R/W is not used in comparison B</li> <li>1 R/W is used in comparison B</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

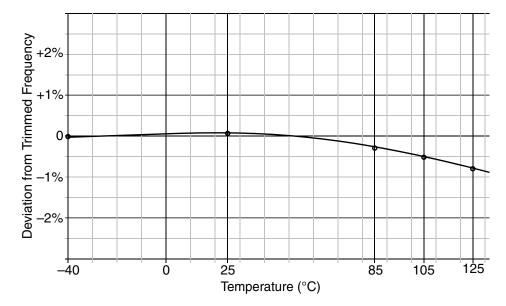

Figure A-8. Typical Frequency Deviation vs Temperature (ICS Trimmed to 16MHz bus@25°C, 5V, FEI)<sup>1</sup>

# A.10 Analog Comparator (ACMP) Electricals

Table A-10. Analog Comparator Electrical Specifications

| # | С   | Rating                                 | Symbol             | Min            | Typical | Max             | Unit |

|---|-----|----------------------------------------|--------------------|----------------|---------|-----------------|------|

| 1 | _   | Supply voltage                         | V <sub>DD</sub>    | 2.7            | _       | 5.5             | V    |

| 2 | C/T | Supply current (active)                | I <sub>DDAC</sub>  | —              | 20      | 35              | μA   |

| 3 | D   | Analog input voltage                   | V <sub>AIN</sub>   | $V_{SS} - 0.3$ | _       | V <sub>DD</sub> | V    |

| 4 | D   | Analog input offset voltage            | V <sub>AIO</sub>   | —              | 20      | 40              | mV   |

| 5 | D   | Analog Comparator hysteresis           | V <sub>H</sub>     | 3.0            | 6.0     | 20.0            | mV   |

| 6 | D   | Analog input leakage current           | I <sub>ALKG</sub>  | _              | _       | 1.0             | μA   |

| 7 | D   | Analog Comparator initialization delay | t <sub>AINIT</sub> | _              | _       | 1.0             | μs   |

<sup>1.</sup> Based on the average of several hundred units from a typical characterization lot.