Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 23                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 16x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                             |

| Supplier Device Package    | 28-TSSOP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh16ctlr |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

#### Page

| 15.4 | Register Definition                    | 227 |

|------|----------------------------------------|-----|

|      | 15.4.1 SPI Control Register 1 (SPIxC1) |     |

|      | 15.4.2 SPI Control Register 2 (SPIxC2) | 228 |

|      | 15.4.3 SPI Baud Rate Register (SPIxBR) | 229 |

|      | 15.4.4 SPI Status Register (SPIxS)     | 230 |

|      | 15.4.5 SPI Data Register (SPIxD)       | 231 |

| 15.5 | Functional Description                 | 232 |

|      | 15.5.1 SPI Clock Formats               | 232 |

|      | 15.5.2 SPI Interrupts                  | 235 |

|      | 15.5.3 Mode Fault Detection            | 235 |

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV3)

| 16.1 | Introduction                                                | 237 |

|------|-------------------------------------------------------------|-----|

|      | 16.1.1 TPM Configuration Information                        | 237 |

|      | 16.1.2 TPM Pin Repositioning                                | 237 |

|      | 16.1.3 Features                                             |     |

|      | 16.1.4 Modes of Operation                                   | 239 |

|      | 16.1.5 Block Diagram                                        | 240 |

| 16.2 | Signal Description                                          |     |

|      | 16.2.1 Detailed Signal Descriptions                         |     |

| 16.3 | Register Definition                                         |     |

|      | 16.3.1 TPM Status and Control Register (TPMxSC)             |     |

|      | 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL)            |     |

|      | 16.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)     |     |

|      | 16.3.4 TPM Channel n Status and Control Register (TPMxCnSC) |     |

|      | 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)      |     |

| 16.4 | Functional Description                                      | 252 |

|      | 16.4.1 Counter                                              | 253 |

|      | 16.4.2 Channel Mode Selection                               | 255 |

| 16.5 | Reset Overview                                              |     |

|      | 16.5.1 General                                              |     |

|      | 16.5.2 Description of Reset Operation                       |     |

| 16.6 | Interrupts                                                  |     |

|      | 16.6.1 General                                              |     |

|      | 16.6.2 Description of Interrupt Operation                   | 259 |

|      |                                                             |     |

# Chapter 17 Development Support

| 17.1 | Introduction                     | 261 |

|------|----------------------------------|-----|

|      | 17.1.1 Forcing Active Background |     |

|      | 17.1.2 Features                  |     |

MC9S08SH32 Series Data Sheet, Rev. 3

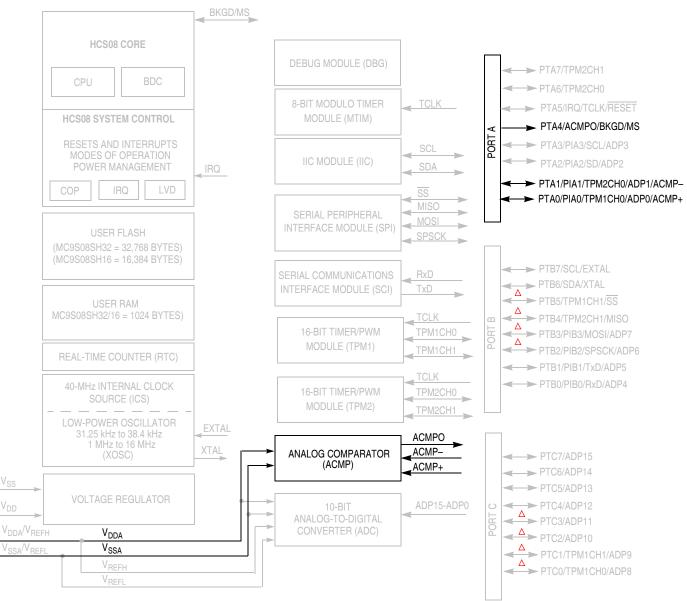

# Chapter 1 Device Overview

The MC9S08SH32 members of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

# 1.1 Devices in the MC9S08SH32 Series

Table 1-1 summarizes the feature set available in the MC9S08SH32 series of MCUs.

| Feature              | 9S08SH32      |    |    | 9S08SH16 |    |    |

|----------------------|---------------|----|----|----------|----|----|

| FLASH size (bytes)   | 32768 16384   |    |    |          |    |    |

| RAM size (bytes)     |               |    | 10 | 24       |    |    |

| Pin quantity         | 28            | 20 | 16 | 28       | 20 | 16 |

| ACMP                 |               |    | y  | es       |    |    |

| ADC channels         | 16 12 8 16 12 |    |    |          |    | 8  |

| DBG                  |               |    | ye | es       |    |    |

| ICS                  | yes           |    |    |          |    |    |

| IIC                  | yes           |    |    |          |    |    |

| IRQ                  |               |    | y  | es       |    |    |

| MTIM                 |               |    | y  | es       |    |    |

| Pin Interrupts       |               |    | ł  | 3        |    |    |

| Pin I/O <sup>1</sup> | 23            | 17 | 13 | 23       | 17 | 13 |

| RTC                  |               |    | y  | es       |    |    |

| SCI                  |               |    | ye | es       |    |    |

| SPI                  | yes           |    |    |          |    |    |

| TPM1 channels        |               |    | :  | 2        |    |    |

| TPM2 channels        |               |    | :  | 2        |    |    |

| XOSC                 |               |    | y  | es       |    |    |

#### Table 1-1. MC9S08SH32 Series Features by MCU and Package

<sup>1</sup> Port I/O count does not include the output-only PTA4/ACMPO/BKGD/MS.

Chapter 2 Pins and Connections

#### **Chapter 3 Modes of Operation**

Background commands are of two types:

- Non-intrusive commands, defined as commands that can be issued while the user program is running. Non-intrusive commands can be issued through the BKGD/MS pin while the MCU is in run mode; non-intrusive commands can also be executed when the MCU is in the active background mode. Non-intrusive commands include:

- Memory access commands

- Memory-access-with-status commands

- BDC register access commands

- The BACKGROUND command

- Active background commands, which can only be executed while the MCU is in active background mode. Active background commands include commands to:

- Read or write CPU registers

- Trace one user program instruction at a time

- Leave active background mode to return to the user application program (GO)

The active background mode is used to program a bootloader or user application program into the FLASH program memory before the MCU is operated in run mode for the first time. When the MC9S08SH32 Series is shipped from the Freescale Semiconductor factory, the FLASH program memory is erased by default unless specifically noted so there is no program that could be executed in run mode until the FLASH memory is initially programmed. The active background mode can also be used to erase and reprogram the FLASH memory after it has been previously programmed.

For additional information about the active background mode, refer to Chapter 17, "Development Support."

## 3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and resumes processing, beginning with the stacking operations leading to the interrupt service routine.

While the MCU is in wait mode, there are some restrictions on which background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode.

# 3.6 Stop Modes

One of two stop modes is entered upon execution of a STOP instruction when STOPE in SOPT1. In any stop mode, the bus and CPU clocks are halted. The ICS module can be configured to leave the reference clocks running. See Chapter 11, "Internal Clock Source (S08ICSV2)," for more information.

#### Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

|------------------------------------|------------------|--------|---------|-------|--------|---------|-------|---------|----------|

| 0x00 <b>2B</b> –<br>0x00 <b>37</b> | Reserved         | _      | _       | _     | _      | _       | _     | _       | _        |

| 0x00 <b>38</b>                     | SCIBDH           | LBKDIE | RXEDGIE | 0     | SBR12  | SBR11   | SBR10 | SBR9    | SBR8     |

| 0x00 <b>39</b>                     | SCIBDL           | SBR7   | SBR6    | SBR5  | SBR4   | SBR3    | SBR2  | SBR1    | SBR0     |

| 0x00 <b>3A</b>                     | SCIC1            | LOOPS  | SCISWAI | RSRC  | М      | WAKE    | ILT   | PE      | PT       |

| 0x00 <b>3B</b>                     | SCIC2            | TIE    | TCIE    | RIE   | ILIE   | TE      | RE    | RWU     | SBK      |

| 0x00 <b>3C</b>                     | SCIS1            | TDRE   | TC      | RDRF  | IDLE   | OR      | NF    | FE      | PF       |

| 0x00 <b>3D</b>                     | SCIS2            | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID   | BRK13 | LBKDE   | RAF      |

| 0x00 <b>3E</b>                     | SCIC3            | R8     | T8      | TXDIR | TXINV  | ORIE    | NEIE  | FEIE    | PEIE     |

| 0x00 <b>3F</b>                     | SCID             | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>40</b> –<br>0x00 <b>47</b> | Reserved         |        |         | _     |        |         |       | _       |          |

| 0x00 <b>48</b>                     | ICSC1            | CL     | KS      |       | RDIV   |         | IREFS | IRCLKEN | IREFSTEN |

| 0x00 <b>49</b>                     | ICSC2            | BE     | NV      | RANGE | HGO    | LP      | EREFS | ERCLKEN | EREFSTEN |

| 0x00 <b>4A</b>                     | ICSTRM           |        |         |       | TR     | MI      |       |         |          |

| 0x00 <b>4B</b>                     | ICSSC            | 0      | 0       | 0     | IREFST | CLł     | KST   | OSCINIT | FTRIM    |

| 0x00 <b>4C</b> –<br>0x00 <b>4F</b> | Reserved         |        | _       | _     | _      |         | _     | _       | _        |

| 0x00 <b>50</b>                     | SPIC1            | SPIE   | SPE     | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE    |

| 0x00 <b>51</b>                     | SPIC2            | 0      | 0       | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0     |

| 0x00 <b>52</b>                     | SPIBR            | 0      | SPPR2   | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0     |

| 0x00 <b>53</b>                     | SPIS             | SPRF   | 0       | SPTEF | MODF   | 0       | 0     | 0       | 0        |

| 0x00 <b>54</b>                     | Reserved         | 0      | 0       | 0     | 0      | 0       | 0     | 0       | 0        |

| 0x00 <b>55</b>                     | SPID             | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>56</b> –<br>0x00 <b>57</b> | Reserved         |        |         | _     |        |         |       | _       | -        |

| 0x00 <b>58</b>                     | IICA             | AD7    | AD6     | AD5   | AD4    | AD3     | AD2   | AD1     | 0        |

| 0x00 <b>59</b>                     | licf             | ML     | JLT     |       |        | IC      | R     |         |          |

| 0x00 <b>5A</b>                     | IICC1            | IICEN  | IICIE   | MST   | TX     | TXAK    | RSTA  | 0       | 0        |

| 0x00 <b>5B</b>                     | IICS             | TCF    | IAAS    | BUSY  | ARBL   | 0       | SRW   | IICIF   | RXAK     |

| 0x00 <b>5C</b>                     | IICD             |        |         |       | DA     |         |       |         |          |

| 0x00 <b>5D</b>                     | IICC2            | GCAEN  | ADEXT   | 0     | 0      | 0       | AD10  | AD9     | AD8      |

| 0x00 <b>5E</b> –<br>0x00 <b>5F</b> | Reserved         | _      | _       | _     | _      | _       | _     | _       | —        |

| 0x00 <b>60</b>                     | TPM2SC           | TOF    | TOIE    | CPWMS | CLKSB  | CLKSA   | PS2   | PS1     | PS0      |

| 0x00 <b>61</b>                     | TPM2CNTH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>62</b>                     | TPM2CNTL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>63</b>                     | TPM2MODH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>64</b>                     | TPM2MODL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>65</b>                     | TPM2C0SC         | CH0F   | CH0IE   | MS0B  | MS0A   | ELS0B   | ELS0A | 0       | 0        |

MC9S08SH32 Series Data Sheet, Rev. 3

```

Chapter 4 Memory

```

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| Address            | Register Name | Bit 7   | 6      | 5      | 4       | 3       | 2       | 1       | Bit 0   |

|--------------------|---------------|---------|--------|--------|---------|---------|---------|---------|---------|

| 0x1800             | SRS           | POR     | PIN    | COP    | ILOP    | ILAD    | 0       | LVD     | 0       |

| 0x1801             | SBDFR         | 0       | 0      | 0      | 0       | 0       | 0       | 0       | BDFR    |

| 0x1802             | SOPT1         | CO      | PT     | STOPE  | 0       | 0       | IICPS   | BKGDPE  | RSTPE   |

| 0x1803             | SOPT2         | COPCLKS | COPW   | 0      | ACIC    | T2CH1PS | T2CH0PS | T1CH1PS | T1CH0PS |

| 0x1804 —<br>0x1805 | Reserved      | _       |        |        | _       |         | _       |         |         |

| 0x1806             | SDIDH         | 0       |        | -      | —       | ID11    | ID10    | ID9     | ID8     |

| 0x1807             | SDIDL         | ID7     | ID6    | ID5    | ID4     | ID3     | ID2     | ID1     | ID0     |

| 0x1808             | Reserved      | _       | _      | _      | —       | _       |         | _       | —       |

| 0x1809             | SPMSC1        | LVWF    | LVWACK | LVWIE  | LVDRE   | LVDSE   | LVDE    | 0       | BGBE    |

| 0x180A             | SPMSC2        | 0       | 0      | LVDV   | LVWV    | PPDF    | PPDACK  | _       | PPDC    |

| 0x180B–<br>0x180F  | Reserved      |         |        |        |         |         |         |         |         |

| 0x1810             | DBGCAH        | Bit 15  | 14     | 13     | 12      | 11      | 10      | 9       | Bit 8   |

| 0x1811             | DBGCAL        | Bit 7   | 6      | 5      | 4       | 3       | 2       | 1       | Bit 0   |

| 0x1812             | DBGCBH        | Bit 15  | 14     | 13     | 12      | 11      | 10      | 9       | Bit 8   |

| 0x1813             | DBGCBL        | Bit 7   | 6      | 5      | 4       | 3       | 2       | 1       | Bit 0   |

| 0x1814             | DBGFH         | Bit 15  | 14     | 13     | 12      | 11      | 10      | 9       | Bit 8   |

| 0x1815             | DBGFL         | Bit 7   | 6      | 5      | 4       | 3       | 2       | 1       | Bit 0   |

| 0x1816             | DBGC          | DBGEN   | ARM    | TAG    | BRKEN   | RWA     | RWAEN   | RWB     | RWBEN   |

| 0x1817             | DBGT          | TRGSEL  | BEGIN  | 0      | 0       | TRG3    | TRG2    | TRG1    | TRG0    |

| 0x1818             | DBGS          | AF      | BF     | ARMF   | 0       | CNT3    | CNT2    | CNT1    | CNT0    |

| 0x1819–<br>0x181F  | Reserved      |         |        |        |         |         |         |         |         |

| 0x1820             | FCDIV         | DIVLD   | PRDIV8 |        | •       | D       | IV      |         |         |

| 0x1821             | FOPT          | KEYEN   | FNORED | 0      | 0       | 0       | 0       | SE      | EC      |

| 0x1822             | Reserved      | _       |        | _      | —       |         | _       |         | —       |

| 0x1823             | FCNFG         | 0       | 0      | KEYACC | 0       | 0       | 0       | 0       | 0       |

| 0x1824             | FPROT         |         |        |        | FPS     |         |         |         | FPDIS   |

| 0x1825             | FSTAT         | FCBEF   | FCCF   | FPVIOL | FACCERR | 0       | FBLANK  | 0       | 0       |

| 0x1826             | FCMD          |         |        |        | FC      | MD      |         |         |         |

| 0x1827–<br>0x183F  | Reserved      | -       |        |        |         |         |         |         | —       |

| 0x1840             | PTAPE         | PTAPE7  | PTAPE6 | PTAPE5 | PTAPE4  | PTAPE3  | PTAPE2  | PTAPE1  | PTAPE0  |

| 0x1841             | PTASE         | PTASE7  | PTASE6 | PTASE5 | PTASE4  | PTASE3  | PTASE2  | PTASE1  | PTASE0  |

| 0x1842             | PTADS         | PTADS7  | PTADS6 | PTADS5 | PTADS4  | PTADS3  | PTADS2  | PTADS1  | PTADS0  |

| 0x1843             | Reserved      | —       | —      | —      | —       | —       |         | —       | —       |

| 0x1844             | PTASC         | 0       | 0      | 0      | 0       | PTAIF   | PTAACK  | PTAIE   | PTAMOD  |

#### Table 4-3. High-Page Register Summary (Sheet 1 of 2)

MC9S08SH32 Series Data Sheet, Rev. 3

#### Chapter 5 Resets, Interrupts, and General System Control

recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug.

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR, A, X, and PC registers to their pre-interrupt values by reading the previously saved information from the stack.

#### NOTE

For compatibility with M68HC08 devices, the H register is not automatically saved and restored. It is good programming practice to push H onto the stack at the start of the interrupt service routine (ISR) and restore it immediately before the RTI that is used to return from the ISR.

If more than one interrupt is pending when the I bit is cleared, the highest priority source is serviced first (see Table 5-2).

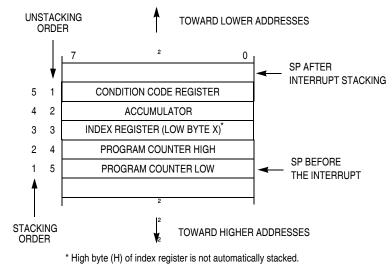

#### 5.5.1 Interrupt Stack Frame

Figure 5-1 shows the contents and organization of a stack frame. Before the interrupt, the stack pointer (SP) points at the next available byte location on the stack. The current values of CPU registers are stored on the stack starting with the low-order byte of the program counter (PCL) and ending with the CCR. After stacking, the SP points at the next available location on the stack which is the address that is one less than the address where the CCR was saved. The PC value that is stacked is the address of the instruction in the main program that would have executed next if the interrupt had not occurred.

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

## 5.6 Low-Voltage Detect (LVD) System

The MC9S08SH32 Series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be higher.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. The low voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching the low voltage condition. When a low voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

# 5.7 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to Table 4-2 and Table 4-3 in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1 and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

#### 5.7.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

|                     | 7              | 6                 | 5                 | 4                 | 3                 | 2              | 1   | 0 |

|---------------------|----------------|-------------------|-------------------|-------------------|-------------------|----------------|-----|---|

| R                   | POR            | PIN               | COP               | ILOP              | ILAD              | 0              | LVD | 0 |

| W                   |                | Wr                | iting 0x55, 0xA   | A to SRS addr     | ess clears COI    | P watchdog tim | er. |   |

| POR:                | 1              | 0                 | 0                 | 0                 | 0                 | 0              | 1   | 0 |

| LVR:                | u <sup>1</sup> | 0                 | 0                 | 0                 | 0                 | 0              | 1   | 0 |

| Any other<br>reset: | 0              | Note <sup>2</sup> | Note <sup>2</sup> | Note <sup>2</sup> | Note <sup>2</sup> | 0              | 0   | 0 |

<sup>1</sup> u = unaffected

<sup>2</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-4. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                     |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                             |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out.</li> <li>This reset source can be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                        |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

#### Chapter 6 Parallel Input/Output Control

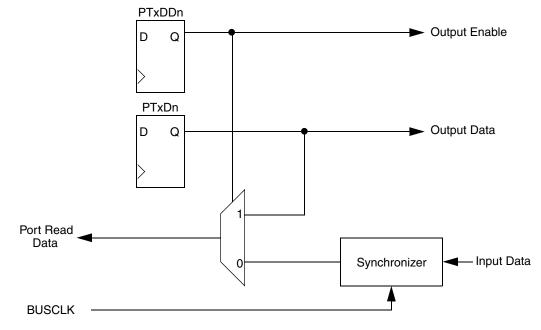

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven momentarily with an old data value that happened to be in the port data register.

Figure 6-1. Parallel I/O Block Diagram

### 6.2 Pull-up, Slew Rate, and Drive Strength

Associated with the parallel I/O ports is a set of registers located in the high page register space that operate independently of the parallel I/O registers. These registers are used to control pull-ups, slew rate, and drive strength for the pins.

An internal pull-up device can be enabled for each port pin by setting the corresponding bit in the pull-up enable register (PTxPEn). The pull-up device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function regardless of the state of the corresponding pull-up enable register bit. The pull-up device is also disabled if the pin is controlled by an analog function.

Slew rate control can be enabled for each port pin by setting the corresponding bit in the slew rate control register (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins that are configured as inputs.

An output pin can be selected to have high output drive strength by setting the corresponding bit in the drive strength select register (PTxDSn). When high drive is selected, a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the MCU are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this, the EMC emissions may be affected by enabling pins as high drive.

$\triangle$  = Pin can be enabled as part of the ganged output drive feature

- NOTE: PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages: VDDA/VREFH and VSSA/VREFL, are double bonded to VDD and VSS respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 8-1. MC9S08SH32 Series Block Diagram Highlighting ACMP Block and Pins

| ADICLK | Selected Clock Source      |  |  |  |  |  |

|--------|----------------------------|--|--|--|--|--|

| 00     | Bus clock                  |  |  |  |  |  |

| 01     | Bus clock divided by 2     |  |  |  |  |  |

| 10     | Alternate clock (ALTCLK)   |  |  |  |  |  |

| 11     | Asynchronous clock (ADACK) |  |  |  |  |  |

#### Table 9-8. Input Clock Select

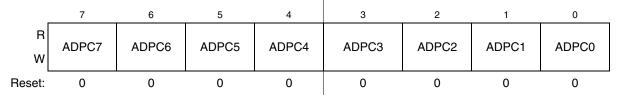

#### Pin Control 1 Register (APCTL1) 9.3.8

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC1 | <ul> <li>ADC Pin Control 1 — ADPC1 is used to control the pin associated with channel AD1.</li> <li>0 AD1 pin I/O control enabled</li> <li>1 AD1 pin I/O control disabled</li> </ul> |

| 0<br>ADPC0 | <ul> <li>ADC Pin Control 0 — ADPC0 is used to control the pin associated with channel AD0.</li> <li>0 AD0 pin I/O control enabled</li> <li>1 AD0 pin I/O control disabled</li> </ul> |

#### Table 9-9. APCTL1 Register Field Descriptions (continued)

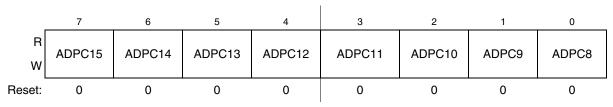

# 9.3.9 Pin Control 2 Register (APCTL2)

APCTL2 is used to control channels 8–15 of the ADC module.

Figure 9-12. Pin Control 2 Register (APCTL2)

#### Table 9-10. APCTL2 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>ADPC15 | <ul> <li>ADC Pin Control 15 — ADPC15 is used to control the pin associated with channel AD15.</li> <li>0 AD15 pin I/O control enabled</li> <li>1 AD15 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 6<br>ADPC14 | <ul> <li>ADC Pin Control 14 — ADPC14 is used to control the pin associated with channel AD14.</li> <li>0 AD14 pin I/O control enabled</li> <li>1 AD14 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 5<br>ADPC13 | <ul> <li>ADC Pin Control 13 — ADPC13 is used to control the pin associated with channel AD13.</li> <li>0 AD13 pin I/O control enabled</li> <li>1 AD13 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 4<br>ADPC12 | <ul> <li>ADC Pin Control 12 — ADPC12 is used to control the pin associated with channel AD12.</li> <li>0 AD12 pin I/O control enabled</li> <li>1 AD12 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 3<br>ADPC11 | <ul> <li>ADC Pin Control 11 — ADPC11 is used to control the pin associated with channel AD11.</li> <li>0 AD11 pin I/O control enabled</li> <li>1 AD11 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 2<br>ADPC10 | <ul> <li>ADC Pin Control 10 — ADPC10 is used to control the pin associated with channel AD10.</li> <li>0 AD10 pin I/O control enabled</li> <li>1 AD10 pin I/O control disabled</li> </ul> |  |  |  |  |  |

result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 9-12.

| Conversion Type                                            | ADICLK | ADLSMP | Max Total Conversion Time                |

|------------------------------------------------------------|--------|--------|------------------------------------------|

| Single or first continuous 8-bit                           | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 0      | 5 $\mu$ s + 20 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 1      | 5 $\mu$ s + 40 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 1      | 5 $\mu$ s + 43 ADCK + 5 bus clock cycles |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}$     | xx     | 0      | 17 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}$    | xx     | 0      | 20 ADCK cycles                           |

| Subsequent continuous 8-bit; $f_{BUS} \ge f_{ADCK}/11$     | xx     | 1      | 37 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}/11$ | xx     | 1      | 40 ADCK cycles                           |

Table 9-12. Total Conversion Time vs. Control Conditions

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1 ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

Conversion time =  $\frac{23 \text{ ADCK cyc}}{8 \text{ MHz/1}} + \frac{5 \text{ bus cyc}}{8 \text{ MHz}} = 3.5 \text{ }\mu\text{s}$

Number of bus cycles =  $3.5 \ \mu s \ x \ 8 \ MHz = 28 \ cycles$

#### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet ADC specifications.

MC9S08SH32 Series Data Sheet, Rev. 3

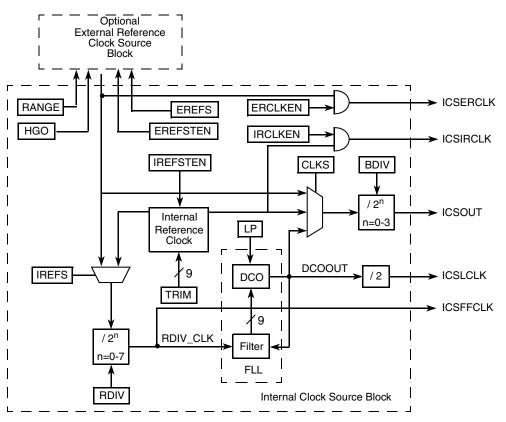

Chapter 11 Internal Clock Source (S08ICSV2)

Figure 11-2. Internal Clock Source (ICS) Block Diagram

### 11.1.4 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

### 11.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

### 11.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

### 11.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.1 Introduction

The serial peripheral interface (SPI) module provides for full-duplex, synchronous, serial communication between the MCU and peripheral devices. These peripheral devices can include other microcontrollers, analog-to-digital converters, shift registers, sensors, memories, and so forth.

The SPI runs at a baud rate up to that of the bus clock divided by two in master mode and bus clock divided by four in slave mode. The SPI operation can be interrupt driven or software can poll the status flags.

All devices in the MC9S08SH32 Series MCUs contain one SPI module, as shown in the following block diagram. Figure 15-1 shows the MC9S08SH32 Series block diagram with the SPI modules highlighted.

## 15.3 Modes of Operation

#### 15.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

## 15.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

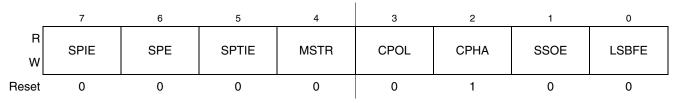

### 15.4.1 SPI Control Register 1 (SPIxC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 15-5. SPI Control Register 1 (SPIxC1)

| Table | 15-1. | SPIxC1 | Field | Descriptions |

|-------|-------|--------|-------|--------------|

|-------|-------|--------|-------|--------------|

| Field      | Description                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                    |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>SPI system inactive</li> <li>SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                    |

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV3)

# 16.1 Introduction

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–1). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

All MC9S08SH32 Series MCUs have two TPM modules.

Figure 16-1 shows the MC9S08SH32 Series block diagram with the TPM modules highlighted.

### **16.1.1 TPM Configuration Information**

The external clock for the MTIM module, TCLK, is selected by setting CLKS = 1:1 or 1:0 in MTIMCLK, which selects the TCLK pin input. The TCLK input can be enabled as external clock inputs to both the MTIM and TPM modules simultaneously.

## 16.1.2 TPM Pin Repositioning

The TPM modules pins, TPM1CHx and TPM2CHx can be repositioned under software control using TxCHnPS bits in SOPT2 as shown in Table 16-1.

| TxCHxPS in SOPT2 | Port Pin for TPM2CH1 | Port Pin for TPM2CH0 | Port Pin for TPM1CH1 | Port Pin for TPM1CH0 |  |

|------------------|----------------------|----------------------|----------------------|----------------------|--|

| 0 (default)      | PTB4                 | PTA1                 | PTB5                 | PTA0                 |  |

| 1                | PTA7                 | PTA6                 | PTC1                 | PTC0                 |  |

Table 16-1. TPM Position Options

#### Chapter 16 Timer/PWM Module (S08TPMV3)

• Edge-aligned PWM mode

The value of a 16-bit modulo register plus 1 sets the period of the PWM output signal. The channel value register sets the duty cycle of the PWM output signal. The user may also choose the polarity of the PWM output signal. Interrupts are available at the end of the period and at the duty-cycle transition point. This type of PWM signal is called edge-aligned because the leading edges of all PWM signals are aligned with the beginning of the period, which is the same for all channels within a TPM.

• Center-aligned PWM mode

Twice the value of a 16-bit modulo register sets the period of the PWM output, and the channel-value register sets the half-duty-cycle duration. The timer counter counts up until it reaches the modulo value and then counts down until it reaches zero. As the count matches the channel value register while counting down, the PWM output becomes active. When the count matches the channel value register while counting up, the PWM output becomes inactive. This type of PWM signal is called center-aligned because the centers of the active duty cycle periods for all channels are aligned with a count value of zero. This type of PWM is required for types of motors used in small appliances.

This is a high-level description only. Detailed descriptions of operating modes are in later sections.

### 16.1.5 Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPMxCHn (timer channel n) where n is the channel number (1-8). The TPM shares its I/O pins with general purpose I/O port pins (refer to I/O pin descriptions in full-chip specification for the specific chip implementation).

Figure 16-2 shows the TPM structure. The central component of the TPM is the 16-bit counter that can operate as a free-running counter or a modulo up/down counter. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter (the values 0x0000 or 0xFFFF effectively make the counter free running). Software can read the counter value at any time without affecting the counting sequence. Any write to either half of the TPMxCNT counter resets the counter, regardless of the data value written.

| # | Characteristic                                          | Conditions                    | С   | Symb                                   | Min  | Typ <sup>1</sup> | Max  | Unit             | Comment                                                |

|---|---------------------------------------------------------|-------------------------------|-----|----------------------------------------|------|------------------|------|------------------|--------------------------------------------------------|

| 1 | Supply current                                          | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 133              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 218              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _    | μA               | ADC current<br>only                                    |

|   |                                                         | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Ρ   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.58<br>2        | 1    | mA               | ADC current<br>only                                    |

|   | ADC                                                     | High speed (ADLPC=0)          | Р   | f <sub>adack</sub>                     | 2    | 3.3              | 5    | MHz              | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub>           |

| 2 | asynchronous<br>clock source                            | Low power (ADLPC=1)           |     |                                        | 1.25 | 2                | 3.3  |                  |                                                        |

| 3 | Conversion<br>time (including<br>sample time)           | Short sample<br>(ADLSMP=0)    | D   | t <sub>ADC</sub>                       |      | 20               | _    | ADCK<br>cycles   | See ADC<br>Chapter for<br>conversion<br>time variances |

| 3 |                                                         | Long sample<br>(ADLSMP=1)     |     |                                        | _    | 40               | _    |                  |                                                        |

| 4 | Sample time                                             | Short sample<br>(ADLSMP=0)    | - D | t <sub>ADS</sub>                       | _    | 3.5              | _    | ADCK<br>cycles   |                                                        |

|   |                                                         | Long sample<br>(ADLSMP=1)     |     |                                        |      | 23.5             | —    |                  |                                                        |

|   |                                                         | 28-pin packages only          |     |                                        |      |                  |      |                  |                                                        |

|   | Total<br>unadjusted<br>error (includes<br>quantization) | 10-bit mode                   |     | E <sub>TUE</sub>                       | _    | ±1               | ±2.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    | Р   |                                        | _    | ±0.5             | ±1   |                  |                                                        |

|   |                                                         | 20-pin packages               |     |                                        |      | •                |      |                  |                                                        |

| 5 |                                                         | 10-bit mode                   | P   |                                        |      | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    | r-  | E <sub>TUE</sub>                       |      | ±0.7             | ±1.5 | LOD              |                                                        |

|   |                                                         | 16-pin packages               |     |                                        |      |                  |      |                  |                                                        |

|   |                                                         | 10-bit mode                   | P   | E <sub>TUE</sub>                       | _    | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |

|   |                                                         | 8-bit mode                    |     |                                        |      | ±0.7             | ±1.5 |                  |                                                        |