# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 28-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh16cwl |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1                  | 10/2007          | Updated The ACMP and TPM modules to version 3 and made numerous revisions to the Electricals. Updated device numbering scheme.                                                                                                                                                   |  |  |  |  |  |  |

| 2                  | 4/2008           | Updated some electricals and made some minor grammatical/formatting revi-<br>sions. Corrected the SPI block module version. Removed incorrect ADC temper-<br>ature sensor value from the Features section. Updated the package information<br>with a sample mask set identifier. |  |  |  |  |  |  |

| 3                  | 3/2014           | Added a note to the Section 9.1, "Introduction"; updated Section 11.4.5, "Internal<br>Reference Clock"; updated Section A.14.1, "Radiated Emissions"; updated<br>Figure 4-1, Figure 4-6; updated Table 4-4; updated Table 7-2.                                                   |  |  |  |  |  |  |

© Freescale Semiconductor, Inc., 2007-2014. All rights reserved.

This product incorporates SuperFlash® Technology licensed from SST.

\_\_\_\_\_

# **List of Chapters**

| Chapter 1  | Device Overview                                | 19  |

|------------|------------------------------------------------|-----|

| Chapter 2  | Pins and Connections                           | 23  |

| Chapter 3  | Modes of Operation                             | 31  |

| Chapter 4  | Memory                                         | 37  |

| Chapter 5  | Resets, Interrupts, and General System Control | 59  |

| Chapter 6  | Parallel Input/Output Control                  | 75  |

| Chapter 7  | Central Processor Unit (S08CPUV3)              | 93  |

| Chapter 8  | Analog Comparator 5-V (S08ACMPV3)              | 113 |

| Chapter 9  | Analog-to-Digital Converter (S08ADC10V1)       | 121 |

| Chapter 10 | Inter-Integrated Circuit (S08IICV2)            | 149 |

| Chapter 11 | Internal Clock Source (S08ICSV2)               | 167 |

| Chapter 12 | Modulo Timer (S08MTIMV1)                       | 181 |

| Chapter 13 | Real-Time Counter (S08RTCV1)                   | 191 |

| Chapter 14 | Serial Communications Interface (S08SCIV4)     | 201 |

| Chapter 15 | Serial Peripheral Interface (S08SPIV3)         | 221 |

| Chapter 16 | Timer Pulse-Width Modulator (S08TPMV3)         | 237 |

| Chapter 17 | Development Support                            | 261 |

| Appendix A | Electrical Characteristics                     | 283 |

| Appendix B | Ordering Information and Mechanical Drawings   | 313 |

### **Section Number**

Title

### Page

|     | 9.4.4     | Conversion Control                 | . 137 |

|-----|-----------|------------------------------------|-------|

|     | 9.4.5     | Automatic Compare Function         | . 140 |

|     | 9.4.6     | MCU Wait Mode Operation            | . 140 |

|     | 9.4.7     | MCU Stop3 Mode Operation           | . 140 |

|     | 9.4.8     | MCU Stop1 and Stop2 Mode Operation | . 141 |

| 9.5 | Initializ | ation Information                  | . 141 |

|     | 9.5.1     | ADC Module Initialization Example  | . 141 |

| 9.6 | Applica   | tion Information                   | . 143 |

|     | 9.6.1     | External Pins and Routing          | . 143 |

|     | 9.6.2     | Sources of Error                   | . 145 |

# Chapter 10 Inter-Integrated Circuit (S08IICV2)

| 10.1 | Introduction                                 | 149 |

|------|----------------------------------------------|-----|

|      | 10.1.1 Module Configuration                  | 149 |

|      | 10.1.2 Features                              | 151 |

|      | 10.1.3 Modes of Operation                    | 151 |

|      | 10.1.4 Block Diagram                         | 151 |

| 10.2 | External Signal Description                  | 152 |

|      | 10.2.1 SCL — Serial Clock Line               | 152 |

|      | 10.2.2 SDA — Serial Data Line                | 152 |

| 10.3 | Register Definition                          |     |

|      | 10.3.1 IIC Address Register (IICA)           | 153 |

|      | 10.3.2 IIC Frequency Divider Register (IICF) | 153 |

|      | 10.3.3 IIC Control Register (IICC1)          | 156 |

|      | 10.3.4 IIC Status Register (IICS)            | 156 |

|      | 10.3.5 IIC Data I/O Register (IICD)          | 157 |

|      | 10.3.6 IIC Control Register 2 (IICC2)        | 158 |

| 10.4 | Functional Description                       | 159 |

|      | 10.4.1 IIC Protocol                          | 159 |

|      | 10.4.2 10-bit Address                        | 162 |

|      | 10.4.3 General Call Address                  | 163 |

| 10.5 | Resets                                       | 163 |

| 10.6 | Interrupts                                   | 163 |

|      | 10.6.1 Byte Transfer Interrupt               | 163 |

|      | 10.6.2 Address Detect Interrupt              | 164 |

|      | 10.6.3 Arbitration Lost Interrupt            | 164 |

| 10.7 | Initialization/Application Information       | 165 |

# Chapter 11 Internal Clock Source (S08ICSV2)

| 11.1 | Introduction |  |  | 167 |

|------|--------------|--|--|-----|

|------|--------------|--|--|-----|

Chapter 1 Device Overview

# 1.3 System Clock Distribution

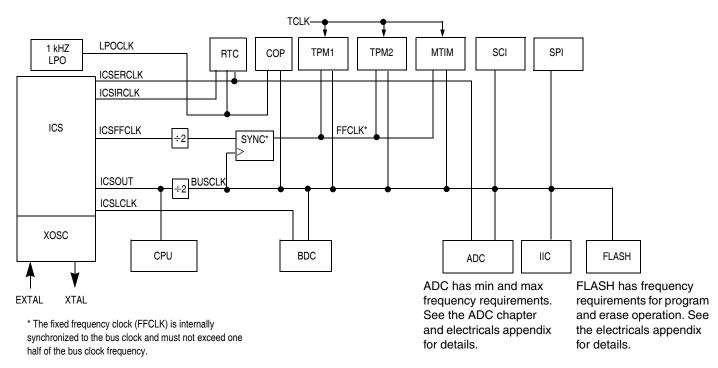

Figure 1-2 shows a simplified clock connection diagram. Some modules in the MCU have selectable clock inputs as shown. The clock inputs to the modules indicate the clock(s) that are used to drive the module function.

The following defines the clocks used in this MCU:

- BUSCLK The frequency of the bus is always half of ICSOUT.

- ICSOUT Primary output of the ICS and is twice the bus frequency.

- ICSLCLK Development tools can select this clock source to speed up BDC communications in systems where the bus clock is configured to run at a very slow frequency.

- ICSERCLK External reference clock can be selected as the RTC clock source and as the alternate clock for the ADC module.

- ICSIRCLK Internal reference clock can be selected as the RTC clock source.

- ICSFFCLK Fixed frequency clock can be selected as clock source for the TPM1, TPM2 and MTIM modules.

- LPOCLK Independent 1-kHz clock source that can be selected as the clock source for the COP and RTC modules.

- TCLK External input clock source for TPM1, TPM2 and MTIM and is referenced as TPMCLK in TPM chapters.

Figure 1-2. System Clock Distribution Diagram

MC9S08SH32 Series Data Sheet, Rev. 3

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08SH32 Series are described in this chapter. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

# 3.2 Features

- Active background mode for code development

- Wait mode CPU shuts down to conserve power; system clocks are running and full regulation is maintained

- Stop modes System clocks are stopped and voltage regulator is in standby

- Stop3 All internal circuits are powered for fast recovery

- Stop2 Partial power down of internal circuits, RAM content is retained

# 3.3 Run Mode

This is the normal operating mode for the MC9S08SH32 Series. This mode is selected upon the MCU exiting reset if the BKGD/MS pin is high. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE–0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip debug module (DBG), provide the means for analyzing MCU operation during software development.

Active background mode is entered in any of the following ways:

- When the BKGD/MS pin is low during POR or immediately after issuing a background debug force reset (see Section 5.7.3, "System Background Debug Force Reset Register (SBDFR)")

- When a BACKGROUND command is received through the BKGD/MS pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

After entering active background mode, the CPU is held in a suspended state waiting for serial background commands rather than executing instructions from the user application program.

### 4.5.1 Features

Features of the FLASH memory include:

- FLASH size

- MC9S08SH32: 32,768 bytes (64 pages of 512 bytes each)

- MC9S08SH16: 16,384 bytes (32 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection and vector redirection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

### 4.5.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.7.1, "FLASH Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses are used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu$ s. Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |

|----------------------|----------------|------------------------|

| Byte program         | 9              | 45 μs                  |

| Byte program (burst) | 4              | 20 μs <sup>1</sup>     |

| Page erase           | 4000           | 20 ms                  |

| Mass erase           | 20,000         | 100 ms                 |

#### Table 4-5. Program and Erase Times

<sup>1</sup> Excluding start/end overhead

Chapter 6 Parallel Input/Output Control

# 6.6 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

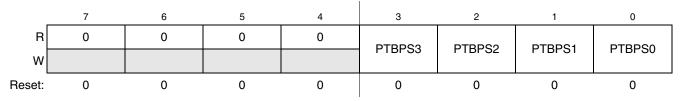

### 6.6.2.7 Port B Interrupt Pin Select Register (PTBPS)

Figure 6-17. Port B Interrupt Pin Select Register (PTBPS)

#### Table 6-16. PTBPS Register Field Descriptions

| Field | Description                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Interrupt Pin Selects — Each of the PTBPSn bits enable the corresponding port B interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

### 6.6.2.8 Port B Interrupt Edge Select Register (PTBES)

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R      | 0 | 0 | 0 | 0 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| W      |   |   |   |   | FIDESS | FIDESZ | FIDEST | FIDESU |

| Reset: | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

#### Figure 6-18. Port B Edge Select Register (PTBES)

#### Table 6-17. PTBES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Edge Selects — Each of the PTBESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Bit-Manipulation | Branch | Branch Read-Modify-Write |  |  |                         |  | Control Register/Memory |  |                        |      |      |                                                                                              |                        |                                   |

|------------------|--------|--------------------------|--|--|-------------------------|--|-------------------------|--|------------------------|------|------|----------------------------------------------------------------------------------------------|------------------------|-----------------------------------|

|                  |        |                          |  |  | 9E60 6<br>NEG<br>3 SP1  |  |                         |  |                        |      |      | 9ED0 5<br>SUB<br>4 SP2                                                                       | 9EE0 4<br>SUB<br>3 SP1 |                                   |

|                  |        |                          |  |  | 9E61 6<br>CBEQ<br>4 SP1 |  |                         |  |                        |      |      | 9ED1 5<br>CMP<br>4 SP2                                                                       | 9EE1 4<br>CMP<br>3 SP1 |                                   |

|                  |        |                          |  |  |                         |  |                         |  |                        |      |      | 9ED2 5<br>SBC<br>4 SP2                                                                       | 3 SP1                  |                                   |

|                  |        |                          |  |  | 9E63 6<br>COM<br>3 SP1  |  |                         |  |                        |      |      | 9ED3 5<br>CPX<br>4 SP2                                                                       | 9EE3 4<br>CPX<br>3 SP1 | 9EF3 6<br>CPHX<br>3 SP1           |

|                  |        |                          |  |  | 9E64 6<br>LSR<br>3 SP1  |  |                         |  |                        |      |      | 9ED3 5<br>CPX<br>4 SP2<br>9ED4 5<br>AND<br>4 SP2<br>9ED5 5<br>BIT<br>4 SP2<br>9ED6 5<br>1 D4 | 9EE4 4<br>AND<br>3 SP1 |                                   |

|                  |        |                          |  |  |                         |  |                         |  |                        |      |      | 9ED5 5<br>BIT<br>4 SP2                                                                       | 9EE5 4<br>BIT<br>3 SP1 |                                   |

|                  |        |                          |  |  | 9E66 6<br>ROR<br>3 SP1  |  |                         |  |                        |      |      | 9ED6 5<br>LDA<br>4 SP2<br>9ED7 5                                                             | 9EE6 4<br>LDA<br>3 SP1 |                                   |

|                  |        |                          |  |  | 9E67 6<br>ASR<br>3 SP1  |  |                         |  |                        |      |      | 4 SP2                                                                                        | STA<br>3 SP1           |                                   |

|                  |        |                          |  |  | 9E68 6<br>LSL<br>3 SP1  |  |                         |  |                        |      |      | 9ED8 5<br>EOR<br>4 SP2                                                                       | 3 SP1                  |                                   |

|                  |        |                          |  |  | 9E69 6<br>ROL<br>3 SP1  |  |                         |  |                        |      |      | 9ED9 5<br>ADC<br>4 SP2                                                                       | ADC<br>3 SP1           |                                   |

|                  |        |                          |  |  | 9E6A 6<br>DEC<br>3 SP1  |  |                         |  |                        |      |      | 9EDA 5<br>ORA<br>4 SP2                                                                       | ORA<br>3 SP1           |                                   |

|                  |        |                          |  |  | 9E6B 8<br>DBNZ<br>4 SP1 |  |                         |  |                        |      |      | 9EDB 5<br>ADD<br>4 SP2                                                                       | ADD                    |                                   |

|                  |        |                          |  |  | 9E6C 6<br>INC<br>3 SP1  |  |                         |  |                        |      |      |                                                                                              |                        |                                   |

|                  |        |                          |  |  | 9E6D 5<br>TST<br>3 SP1  |  |                         |  |                        |      |      |                                                                                              |                        |                                   |

|                  |        |                          |  |  |                         |  |                         |  | 9EAE 5<br>LDHX<br>2 IX | LDHX | IDHX |                                                                                              | אחו                    | 9EFE 5<br>LDHX<br>3 SP1<br>9EFF 5 |

|                  |        |                          |  |  | 9E6F 6<br>CLR<br>3 SP1  |  |                         |  |                        |      |      | 9EDF 5<br>STX<br>4 SP2                                                                       | 9EEF 4<br>STX<br>3 SP1 | 9EFF 5<br>STHX<br>3 SP1           |

#### Table 7-3. Opcode Map (Sheet 2 of 2)

Inherent Immediate Direct Extended DIR to DIR IX+ to DIR INH IMM DIR EXT DD IX+D

REL IX IX1 IX2 IMD DIX+ Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal 9E60 6 NEG Number of Bytes 3 SP1 Addressing Mode

MC9S08SH32 Series Data Sheet, Rev. 3

### 9.1.6 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 10 bits resolution.

- Up to 28 analog inputs.

- Output formatted in 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop3 modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Selectable asynchronous hardware conversion trigger.

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

### 9.1.7 Block Diagram

Figure 9-2 provides a block diagram of the ADC module

# 12.3.2 MTIM Clock Configuration Register (MTIMCLK)

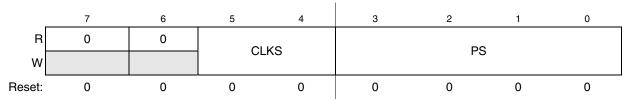

MTIMCLK contains the clock select bits (CLKS) and the prescaler select bits (PS).

Figure 12-5. MTIM Clock Configuration Register

#### Table 12-3. MTIM Clock Configuration Register Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:6         | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 5:4<br>CLKS | Clock Source Select — These two read/write bits select one of four different clock sources as the input to the MTIM prescaler. Changing the clock source while the counter is active does not clear the counter. The count continues with the new clock source. Reset clears CLKS to 000.         00       Encoding 0. Bus clock (BUSCLK)         01       Encoding 1. Fixed-frequency clock (XCLK)         10       Encoding 3. External source (TCLK pin), falling edge         11       Encoding 4. External source (TCLK pin), rising edge         All other encodings default to the bus clock (BUSCLK).                                                                                   |  |  |  |  |  |  |  |  |

| 3:0<br>PS   | Clock Source Prescaler — These four read/write bits select one of nine outputs from the 8-bit prescaler.<br>Changing the prescaler value while the counter is active does not clear the counter. The count continues with the<br>new prescaler value. Reset clears PS to 0000.<br>0000 Encoding 0. MTIM clock source ÷ 1<br>0001 Encoding 1. MTIM clock source ÷ 2<br>0010 Encoding 2. MTIM clock source ÷ 4<br>0011 Encoding 3. MTIM clock source ÷ 8<br>0100 Encoding 4. MTIM clock source ÷ 16<br>0101 Encoding 5. MTIM clock source ÷ 32<br>0110 Encoding 6. MTIM clock source ÷ 128<br>1000 Encoding 8. MTIM clock source ÷ 256<br>All other encodings default to MTIM clock source ÷ 256. |  |  |  |  |  |  |  |  |

Chapter 15 Serial Peripheral Interface (S08SPIV3)

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 15-5. SPI Baud Rate Prescaler Divisor

#### Table 15-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |

|----------------|--------------|

| 0:0:0          | 2            |

| 0:0:1          | 4            |

| 0:1:0          | 8            |

| 0:1:1          | 16           |

| 1:0:0          | 32           |

| 1:0:1          | 64           |

| 1:1:0          | 128          |

| 1:1:1          | 256          |

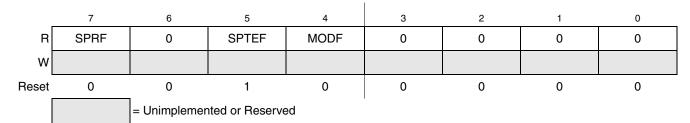

# 15.4.4 SPI Status Register (SPIxS)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 15-8. SPI Status Register (SPIxS)

Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPIxD) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPIxD. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 15.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPIxD) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

# 15.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 15-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the

Chapter 15 Serial Peripheral Interface (S08SPIV3)

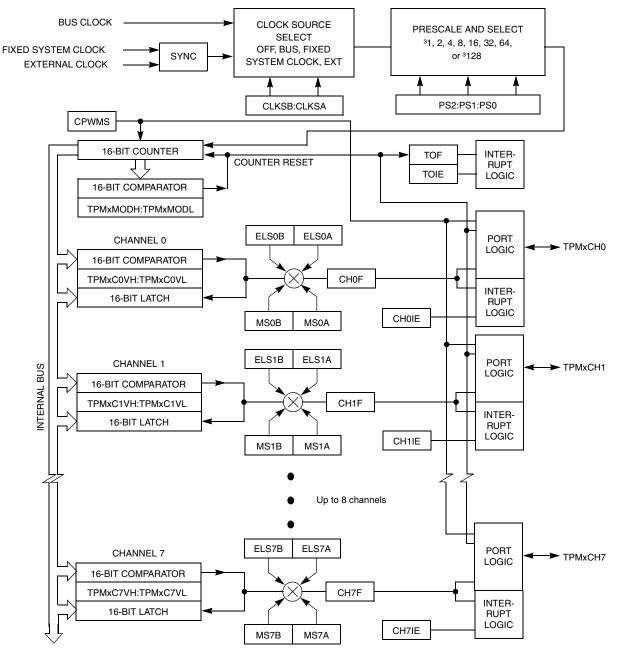

Chapter 16 Timer/PWM Module (S08TPMV3)

Figure 16-2. TPM Block Diagram

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

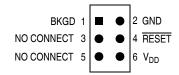

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 17-1. BDM Tool Connector

### 17.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 17.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

#### **Chapter 17 Development Support**

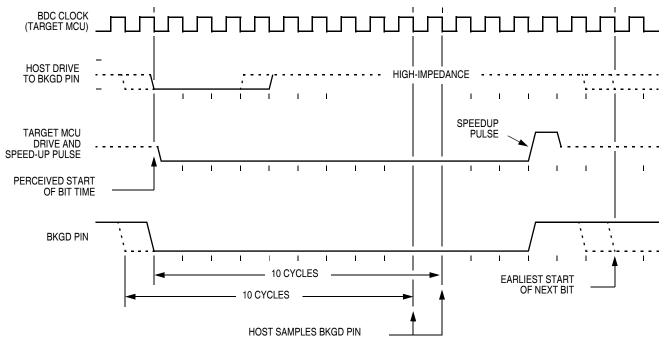

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

Chapter 17 Development Support

# 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)