Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 13                                                         |

| Program Memory Size        | 32KB (32K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | 16-TSSOP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh32ctg |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 4 Memory

## 4.5.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased.

#### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte that is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag, which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized before using any FLASH commands. This must be done only once following a reset.

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.7.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x0055 and 0x00AA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x0055 or 0x00AA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.7.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out  $(2^{10} \text{ cycles})$ .

| Contro  | ol Bits   | Clock Source | COP Window <sup>1</sup> Opens | COP Overflow Count                             |  |

|---------|-----------|--------------|-------------------------------|------------------------------------------------|--|

| COPCLKS | COPT[1:0] | Clock Source | (COPW = 1)                    |                                                |  |

| N/A     | 0:0       | N/A          | N/A                           | COP is disabled                                |  |

| 0       | 0:1       | 1 kHz        | N/A                           | 2 <sup>5</sup> cycles (32 ms <sup>2</sup> )    |  |

| 0       | 1:0       | 1 kHz        | N/A                           | 2 <sup>8</sup> cycles (256 ms <sup>1</sup> )   |  |

| 0       | 1:1       | 1 kHz        | N/A                           | 2 <sup>10</sup> cycles (1.024 s <sup>1</sup> ) |  |

| 1       | 0:1       | Bus          | 6144 cycles                   | 2 <sup>13</sup> cycles                         |  |

| 1       | 1:0       | Bus          | 49,152 cycles                 | 2 <sup>16</sup> cycles                         |  |

| 1       | 1:1       | Bus          | 196,608 cycles                | 2 <sup>18</sup> cycles                         |  |

#### Table 5-1. COP Configuration Options

<sup>1</sup> Windowed COP operation requires the user to clear the COP timer in the last 25% of the selected timeout period. This column displays the minimum number of clock counts required before the COP timer can be reset when in windowed COP mode (COPW = 1).

<sup>2</sup> Values shown in milliseconds based on  $t_{LPO} = 1$  ms. See  $t_{LPO}$  in the appendix Section A.12.1, "Control Timing," for the tolerance of this value.

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address       — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                        |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

#### Table 5-4. SRS Register Field Descriptions

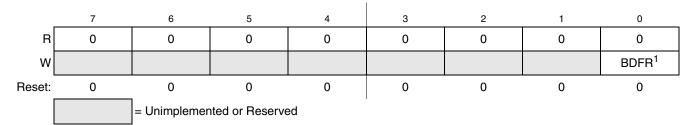

### 5.7.3 System Background Debug Force Reset Register (SBDFR)

This high page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

#### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

#### Table 5-5. SBDFR Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

**Chapter 6 Parallel Input/Output Control**

## 6.6.3 Port C Registers

Port C is controlled by the registers listed below.

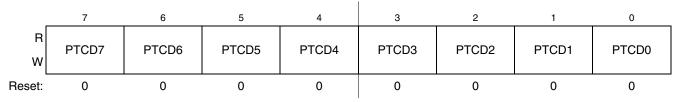

## 6.6.3.1 Port C Data Register (PTCD)

#### Figure 6-19. Port C Data Register (PTCD)

#### Table 6-18. PTCD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCD[7:0] | Port C Data Register Bits — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

### 6.6.3.2 Port C Data Direction Register (PTCDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-20. Port C Data Direction Register (PTCDD)

#### Table 6-19. PTCDD Register Field Descriptions

| Field             | Description                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCDD[7:0] | <b>Data Direction for Port C Bits</b> — These read/write bits control the direction of port C pins and what is read for PTCD reads.                                             |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port C bit n and PTCD reads return the contents of PTCDn.</li> </ol> |

# 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

# 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

## 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

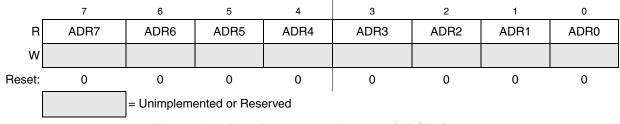

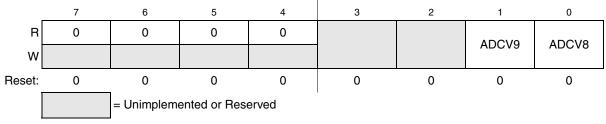

Figure 9-7. Data Result Low Register (ADCRL)

## 9.3.5 Compare Value High Register (ADCCVH)

This register holds the upper two bits of the 10-bit compare value. These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled. In 8-bit operation, ADCCVH is not used during compare.

Figure 9-8. Compare Value High Register (ADCCVH)

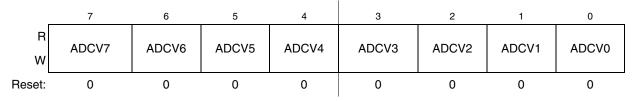

## 9.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 10-bit compare value, or all 8 bits of the 8-bit compare value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in either 10-bit or 8-bit mode.

## 9.3.7 Configuration Register (ADCCFG)

ADCCFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

### 9.4.4.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADCRH and ADCRL. This is indicated by the setting of COCO. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADCRH and ADCRL if the previous data is in the process of being read while in 10-bit MODE (the ADCRH register has been read but the ADCRL register has not). When blocking is active, the data transfer is blocked, COCO is not set, and the new result is lost. In the case of single conversions with the compare function enabled and the compare condition false, blocking has no effect and ADC operation is terminated. In all other cases of operation, when a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled).

If single conversions are enabled, the blocking mechanism could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

### 9.4.4.3 Aborting Conversions

Any conversion in progress will be aborted when:

- A write to ADCSC1 occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCSC2, ADCCFG, ADCCVH, or ADCCVL occurs. This indicates a mode of operation change has occurred and the current conversion is therefore invalid.

- The MCU is reset.

- The MCU enters stop mode with ADACK not enabled.

When a conversion is aborted, the contents of the data registers, ADCRH and ADCRL, are not altered but continue to be the values transferred after the completion of the last successful conversion. In the case that the conversion was aborted by a reset, ADCRH and ADCRL return to their reset states.

### 9.4.4.4 Power Control

The ADC module remains in its idle state until a conversion is initiated. If ADACK is selected as the conversion clock source, the ADACK clock generator is also enabled.

Power consumption when active can be reduced by setting ADLPC. This results in a lower maximum value for  $f_{ADCK}$  (see the electrical specifications).

### 9.4.4.5 Total Conversion Time

The total conversion time depends on the sample time (as determined by ADLSMP), the MCU bus frequency, the conversion mode (8-bit or 10-bit), and the frequency of the conversion clock ( $f_{ADCK}$ ). After the module becomes active, sampling of the input begins. ADLSMP is used to select between short and long sample times. When sampling is complete, the converter is isolated from the input channel and a successive approximation algorithm is performed to determine the digital value of the analog signal. The

### 10.1.2 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

- General call recognition

- 10-bit address extension

### 10.1.3 Modes of Operation

A brief description of the IIC in the various MCU modes is given here.

- **Run mode** This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module continues to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- **Stop mode** The IIC is inactive in stop3 mode for reduced power consumption. The stop instruction does not affect IIC register states. Stop2 resets the register contents.

### 10.1.4 Block Diagram

Figure 10-2 is a block diagram of the IIC.

Chapter 11 Internal Clock Source (S08ICSV2)

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

## 11.4.1.2 FLL Engaged External (FEE)

The FLL engaged external (FEE) mode is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 0

- RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

In FLL engaged external mode, the ICSOUT clock is derived from the FLL clock which is controlled by the external reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the external reference clock is enabled.

## 11.4.1.3 FLL Bypassed Internal (FBI)

The FLL bypassed internal (FBI) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is active or LP bit is written to 0

In FLL bypassed internal mode, the ICSOUT clock is derived from the internal reference clock. The FLL clock is controlled by the internal reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK will be available for BDC communications, and the internal reference clock is enabled.

## 11.4.1.4 FLL Bypassed Internal Low Power (FBILP)

The FLL bypassed internal low power (FBILP) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is not active and LP bit is written to 1

In FLL bypassed internal low power mode, the ICSOUT clock is derived from the internal reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications, and the internal reference clock is enabled.

RTCPS and the RTCLKS[0] bit select the desired divide-by value. If a different value is written to RTCPS, the prescaler and RTCCNT counters are reset to 0x00. Table 13-6 shows different prescaler period values.

| RTCPS | 1-kHz Internal Clock<br>(RTCLKS = 00) | 1-MHz External Clock<br>(RTCLKS = 01) | 32-kHz Internal Clock<br>(RTCLKS = 10) | 32-kHz Internal Clock<br>(RTCLKS = 11) |

|-------|---------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|

| 0000  | Off                                   | Off                                   | Off                                    | Off                                    |

| 0001  | 8 ms                                  | 1.024 ms                              | 250 μs                                 | 32 ms                                  |

| 0010  | 32 ms                                 | 2.048 ms                              | 1 ms                                   | 64 ms                                  |

| 0011  | 64 ms                                 | 4.096 ms                              | 2 ms                                   | 128 ms                                 |

| 0100  | 128 ms                                | 8.192 ms                              | 4 ms                                   | 256 ms                                 |

| 0101  | 256 ms                                | 16.4 ms                               | 8 ms                                   | 512 ms                                 |

| 0110  | 512 ms                                | 32.8 ms                               | 16 ms                                  | 1.024 s                                |

| 0111  | 1.024 s                               | 65.5 ms                               | 32 ms                                  | 2.048 s                                |

| 1000  | 1 ms                                  | 1 ms                                  | 31.25 μs                               | 31.25 ms                               |

| 1001  | 2 ms                                  | 2 ms                                  | 62.5 μs                                | 62.5 ms                                |

| 1010  | 4 ms                                  | 5 ms                                  | 125 μs                                 | 156.25 ms                              |

| 1011  | 10 ms                                 | 10 ms                                 | 312.5 μs                               | 312.5 ms                               |

| 1100  | 16 ms                                 | 20 ms                                 | 0.5 ms                                 | 0.625 s                                |

| 1101  | 0.1 s                                 | 50 ms                                 | 3.125 ms                               | 1.5625 s                               |

| 1110  | 0.5 s                                 | 0.1 s                                 | 15.625 ms                              | 3.125 s                                |

| 1111  | 1 s                                   | 0.2 s                                 | 31.25 ms                               | 6.25 s                                 |

| T | able | 13-6. | Prescaler | Period |

|---|------|-------|-----------|--------|

|   |      |       |           |        |

The RTC modulo register (RTCMOD) allows the compare value to be set to any value from 0x00 to 0xFF. When the counter is active, the counter increments at the selected rate until the count matches the modulo value. When these values match, the counter resets to 0x00 and continues counting. The real-time interrupt flag (RTIF) is set when a match occurs. The flag sets on the transition from the modulo value to 0x00. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00.

The RTC allows for an interrupt to be generated when RTIF is set. To enable the real-time interrupt, set the real-time interrupt enable bit (RTIE) in RTCSC. RTIF is cleared by writing a 1 to RTIF.

## 13.4.1 RTC Operation Example

This section shows an example of the RTC operation as the counter reaches a matching value from the modulo register.

## 14.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- · Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

#### 14.1.2 Modes of Operation

See Section 14.3, "Functional Description," For details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Stop mode operation

- Loop mode

- Single-wire mode

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>WAKE | Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.         0 Idle-line wakeup.         1 Address-mark wakeup.                                                                                                                                                                                                                                                           |

| 2<br>ILT  | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of logic high level needed by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit. |

| 1<br>PE   | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significant bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                       |

| 0<br>PT   | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                    |

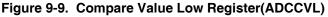

# 14.2.3 SCI Control Register 2 (SCIxC2)

This register can be read or written at any time.

Figure 14-7. SCI Control Register 2 (SCIxC2)

#### Table 14-4. SCIxC2 Field Descriptions

| Field     | Description                                                                                                                                                  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)0Hardware interrupts from TDRE disabled (use polling).1Hardware interrupt requested when TDRE flag is 1.                 |  |  |

| 6<br>TCIE | Transmission Complete Interrupt Enable (for TC)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 </td |  |  |

| 5<br>RIE  | Receiver Interrupt Enable (for RDRF)0Hardware interrupts from RDRF disabled (use polling).1Hardware interrupt requested when RDRF flag is 1.                 |  |  |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)0 Hardware interrupts from IDLE disabled (use polling).1 Hardware interrupt requested when IDLE flag is 1.              |  |  |

Chapter 14 Serial Communications Interface (S08SCIV4)

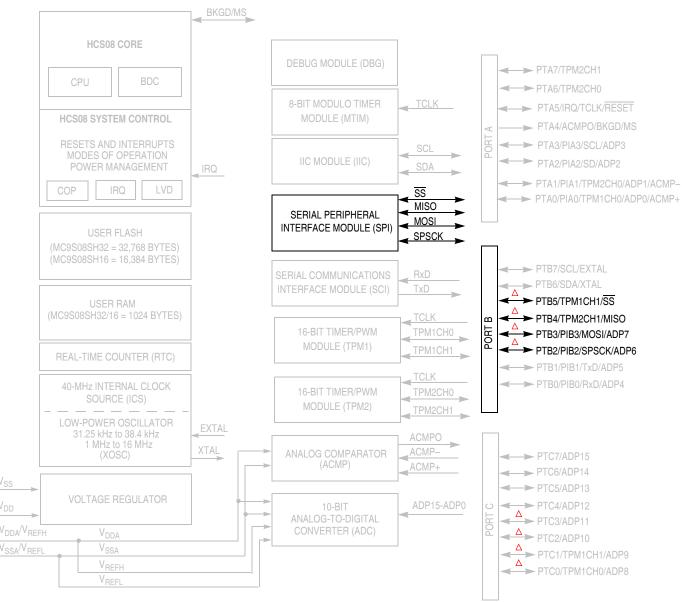

$\triangle$  = Pin can be enabled as part of the ganged output drive feature

- NOTE: PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages: V<sub>DDA</sub>/V<sub>REFH</sub> and V<sub>SSA</sub>/V<sub>REFL</sub>, are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 15-1. MC9S08SH32 Series Block Diagram Highlighting SPI Block and Pin

### 16.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

### 16.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

#### Chapter 16 Timer/PWM Module (S08TPMV3)

(becomes unlatched) when the TPMxCnSC register is written (whether BDM mode is active or not). Any write to the channel registers will be ignored during the input capture mode.

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxCnSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the channel register are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution. The value read from the TPMxCnVH and TPMxCnVL registers in BDM mode is the value of these registers and not the value of their read buffer.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. After both bytes are written, they are transferred as a coherent 16-bit value into the timer-channel registers according to the value of CLKSB:CLKSA bits and the selected mode, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written.

- If (CLKSB:CLKSA not = 0:0 and in output compare mode) then the registers are updated after the second byte is written and on the next change of the TPM counter (end of the prescaler counting).

- If (CLKSB:CLKSA not = 0:0 and in EPWM or CPWM modes), then the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL - 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

The latching mechanism may be manually reset by writing to the TPMxCnSC register (whether BDM mode is active or not). This latching mechanism allows coherent 16-bit writes in either big-endian or little-endian order which is friendly to various compiler implementations.

When BDM is active, the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active even if one or both halves of the channel register are written while BDM is active. Any write to the channel registers bypasses the buffer latches and directly write to the channel register while BDM is active. The values written to the channel register while BDM is active are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

## 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

#### **Chapter 17 Development Support**

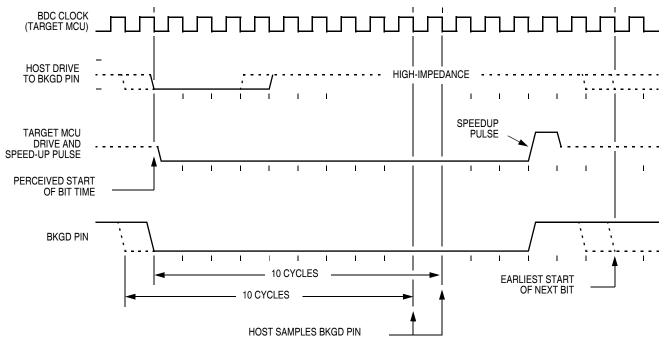

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

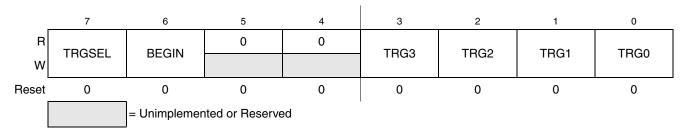

## 17.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

#### Figure 17-8. Debug Trigger Register (DBGT)

#### Table 17-5. DBGT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>TRGSEL     | <ul> <li>Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.</li> <li>0 Trigger on access to compare address (force)</li> <li>1 Trigger if opcode at compare address is executed (tag)</li> </ul> |  |  |  |  |

| 6<br>BEGIN      | <ul> <li>Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs assumed to be begin traces.</li> <li>0 Data stored in FIFO until trigger (end trace)</li> <li>1 Trigger initiates data storage (begin trace)</li> </ul>                                                                                                                       |  |  |  |  |

| 3:0<br>TRG[3:0] | Select Trigger ModeSelects one of nine triggering modes, as described below.0000A-only0001A OR B0010A Then B0011Event-only B (store data)0100A then event-only B (store data)0101A AND B data (full mode)0110A AND NOT B data (full mode)0111Inside range: $A \leq address \leq B$ 1000Outside range: address < A or address > B1001- 1111 (No trigger)                                                                                                                                                              |  |  |  |  |

#### **Appendix A Electrical Characteristics**

- <sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- $^7~$  The  $\overline{\text{RESET}}$  pin does not have a clamp diode to  $V_{\text{DD}}$  Do not drive this pin above  $V_{\text{DD}}$

- <sup>8</sup> Maximum is highest voltage that POR is guaranteed.

- <sup>9</sup> Simulated, not tested.

- $^{10}$  Factory trimmed at V<sub>DD</sub> = 5.0 V, Temp = 25°C.

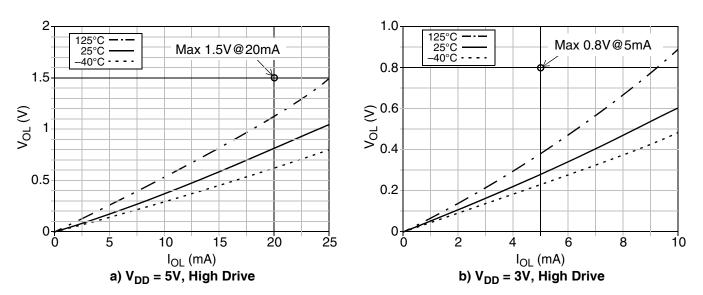

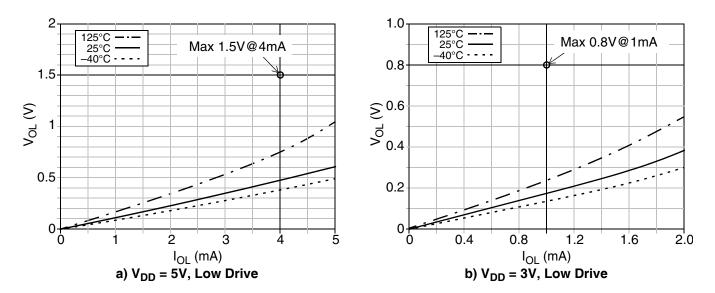

Figure A-1. Typical V<sub>OL</sub> vs I<sub>OL</sub>, High Drive Strength

Figure A-2. Typical  $V_{OL} \mbox{ vs } I_{OL},$  Low Drive Strength

MC9S08SH32 Series Data Sheet, Rev. 3

Appendix A Electrical Characteristics

# A.8 External Oscillator (XOSC) Characteristics

Table A-8. Oscillator Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| # | С | Rating                                                        | Symbol                         | Min                                                        | Typ <sup>1</sup> | Max  | Unit |

|---|---|---------------------------------------------------------------|--------------------------------|------------------------------------------------------------|------------------|------|------|

| 1 | с | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)      |                                |                                                            |                  |      |      |

|   |   | Low range (RANGE = 0)                                         | f <sub>lo</sub>                | 32                                                         | —                | 38.4 | kHz  |

|   |   | High range (RANGE = 1) FEE or FBE mode $^2$                   | f <sub>hi</sub>                | 1                                                          | —                | 5    | MHz  |

|   |   | High range (RANGE = 1, HGO = 1) FBELP mode                    | f <sub>hi-hgo</sub>            | 1                                                          | —                | 16   | MHz  |

|   |   | High range (RANGE = 1, HGO = 0) FBELP mode                    | f <sub>hi-lp</sub>             | 1                                                          | —                | 8    | MHz  |

| 2 | - | Load capacitors                                               | C <sub>1,</sub> C <sub>2</sub> | See crystal or resonator<br>manufacturer's recommendation. |                  |      |      |

| 3 |   | Feedback resistor                                             |                                |                                                            |                  |      |      |

|   |   | Low range (32 kHz to 100 kHz)                                 | R <sub>F</sub>                 | —                                                          | 10               | —    | MΩ   |

|   |   | High range (1 MHz to 16 MHz)                                  |                                | _                                                          | 1                | _    | MΩ   |

|   |   | Series resistor                                               |                                |                                                            |                  |      |      |

|   |   | Low range, low gain (RANGE = 0, HGO = 0)                      | R <sub>s</sub>                 | —                                                          | 0                | —    | kΩ   |

| 4 |   | Low range, high gain (RANGE = 0, HGO = 1)                     |                                | —                                                          | 100              | —    | kΩ   |

|   |   | High range, low gain (RANGE = 1, HGO = 0)                     |                                | —                                                          | 0                | _    | kΩ   |

|   |   | High range, high gain (RANGE = 1, HGO = 1)                    |                                |                                                            |                  |      |      |

|   |   | ≥ 8 MHz                                                       |                                | —                                                          | 0                | 0    | kΩ   |

|   |   | 4 MHz                                                         |                                | —                                                          | 0                | 10   | kΩ   |

|   |   | 1 MHz                                                         |                                | _                                                          | 0                | 20   | kΩ   |

|   | Т | Crystal start-up time <sup>3</sup>                            |                                |                                                            |                  |      |      |

| 5 |   | Low range, low gain (RANGE = 0, HGO = 0)                      | t<br>CSTL-LP                   | —                                                          | 200              | —    | ms   |

|   |   | Low range, high gain (RANGE = 0, HGO = 1)                     | t<br>CSTL-HGO                  | —                                                          | 400              | —    | ms   |

|   |   | High range, low gain (RANGE = 1, HGO = $0$ ) <sup>4</sup>     | t<br>CSTH-LP                   | —                                                          | 5                | —    | ms   |

|   |   | High range, high gain (RANGE = 1, HGO = 1) <sup>4</sup>       | t<br>CSTH-HGO                  | —                                                          | 20               | —    | ms   |

| 6 | т | Square wave input clock frequency (EREFS = 0,<br>ERCLKEN = 1) |                                |                                                            |                  |      |      |

|   |   | FEE or FBE mode <sup>2</sup>                                  | f                              | 0.03125                                                    | —                | 5    | MHz  |

|   |   | FBELP mode                                                    | f <sub>extal</sub>             | 0                                                          | —                | 40   | MHz  |

$^1\,$  Typical data was characterized at 5.0 V, 25°C or is recommended value.

<sup>2</sup> The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> Characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

<sup>4</sup> 4 MHz crystal