Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh32ctj |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

Title

| 13.3 | Register Definition                            |     |

|------|------------------------------------------------|-----|

|      | 13.3.1 RTC Status and Control Register (RTCSC) |     |

|      | 13.3.2 RTC Counter Register (RTCCNT)           | 196 |

|      | 13.3.3 RTC Modulo Register (RTCMOD)            | 196 |

| 13.4 | Functional Description                         | 196 |

|      | 13.4.1 RTC Operation Example                   | 197 |

| 13.5 | Initialization/Application Information         | 198 |

# Chapter 14 Serial Communications Interface (S08SCIV4)

| 14.1 | Introduc | tion                                       | 201 |

|------|----------|--------------------------------------------|-----|

|      | 14.1.1   | Features                                   | 203 |

|      | 14.1.2   | Modes of Operation                         | 203 |

|      | 14.1.3   | Block Diagram                              | 204 |

| 14.2 | Register | Definition                                 | 206 |

|      |          | SCI Baud Rate Registers (SCIxBDH, SCIxBDL) |     |

|      |          | SCI Control Register 1 (SCIxC1)            |     |

|      |          | SCI Control Register 2 (SCIxC2)            |     |

|      | 14.2.4   | SCI Status Register 1 (SCIxS1)             | 209 |

|      |          | SCI Status Register 2 (SCIxS2)             |     |

|      |          | SCI Control Register 3 (SCIxC3)            |     |

|      |          | SCI Data Register (SCIxD)                  |     |

| 14.3 |          | nal Description                            |     |

|      |          | Baud Rate Generation                       |     |

|      |          | Transmitter Functional Description         |     |

|      |          | Receiver Functional Description            |     |

|      |          | Interrupts and Status Flags                |     |

|      | 14.3.5   | Additional SCI Functions                   | 218 |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| 15.1 | Introduction                                 |     |

|------|----------------------------------------------|-----|

|      | 15.1.1 Features                              |     |

|      | 15.1.2 Block Diagrams                        | 223 |

|      | 15.1.3 SPI Baud Rate Generation              |     |

| 15.2 | External Signal Description                  |     |

|      | 15.2.1 SPSCK — SPI Serial Clock              |     |

|      | 15.2.2 MOSI — Master Data Out, Slave Data In |     |

|      | 15.2.3 MISO — Master Data In, Slave Data Out |     |

|      | 15.2.4 $\overline{SS}$ — Slave Select        |     |

| 15.3 | Modes of Operation                           |     |

|      | 15.3.1 SPI in Stop Modes                     |     |

|      |                                              |     |

# 4.5.5 Access Errors

An access error occurs whenever the command execution protocol is violated.

Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

- Writing to a FLASH address before the internal FLASH clock frequency has been set by writing to the FCDIV register

- Writing to a FLASH address while FCBEF is not set (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a FLASH address before launching the previous command (There is only one write to FLASH for every command.)

- Writing a second time to FCMD before launching the previous command (There is only one write to FCMD for every command.)

- Writing to any FLASH control register other than FCMD after writing to a FLASH address

- Writing any command code other than the five allowed codes (0x05, 0x20, 0x25, 0x40, or 0x41) to FCMD

- Writing any FLASH control register other than the write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD

- The MCU enters stop mode while a program or erase command is in progress (The command is aborted.)

- Writing the byte program, burst program, or page erase command code (0x20, 0x25, or 0x40) with a background debug command while the MCU is secured (The background debug controller can only do blank check and mass erase commands when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command

# 4.5.6 FLASH Block Protection

The block protection feature prevents the protected region of FLASH from program or erase changes. Block protection is controlled through the FLASH protection register (FPROT). When enabled, block protection begins at any 512 byte boundary below the last address of FLASH, 0xFFFF. (See Section 4.7.4, "FLASH Protection Register (FPROT and NVPROT)").

After exit from reset, FPROT is loaded with the contents of the NVPROT location, which is in the nonvolatile register block of the FLASH memory. FPROT cannot be changed directly from application software so a runaway program cannot alter the block protection settings. Because NVPROT is within the last 512 bytes of FLASH, if any amount of memory is protected, NVPROT is itself protected and cannot be altered (intentionally or unintentionally) by the application software. FPROT can be written through background debug commands, which allows a way to erase and reprogram a protected FLASH memory.

The block protection mechanism is illustrated in Figure 4-4. The FPS bits are used as the upper bits of the last address of unprotected memory. This address is formed by concatenating FPS7:FPS1 with logic 1 bits as shown. For example, to protect the last 1536 bytes of memory (addresses 0xFA00 through 0xFFFF), the FPS bits must be set to 1111 100, which results in the value 0xF9FF as the last address of unprotected memory. In addition to programming the FPS bits to the appropriate value, FPDIS (bit 0 of NVPROT)

| f <sub>Bus</sub> | PRDIV8<br>(Binary) | DIV<br>(Decimal) | f <sub>FCLK</sub> | Program/Erase Timing Pulse<br>(5 μs Min, 6.7 μs Max) |

|------------------|--------------------|------------------|-------------------|------------------------------------------------------|

| 20 MHz           | 1                  | 12               | 192.3 kHz         | 5.2 μs                                               |

| 10 MHz           | 0                  | 49               | 200 kHz           | 5 μs                                                 |

| 8 MHz            | 0                  | 39               | 200 kHz           | 5 μs                                                 |

| 4 MHz            | 0                  | 19               | 200 kHz           | 5 μs                                                 |

| 2 MHz            | 0                  | 9                | 200 kHz           | 5 μs                                                 |

| 1 MHz            | 0                  | 4                | 200 kHz           | 5 μs                                                 |

| 200 kHz          | 0                  | 0                | 200 kHz           | 5 μs                                                 |

| 150 kHz          | 0                  | 0                | 150 kHz           | 6.7 μs                                               |

### Table 4-7. FLASH Clock Divider Settings

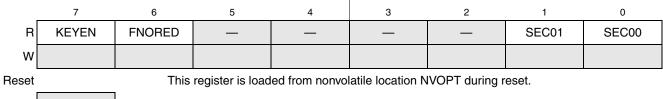

# 4.7.2 FLASH Options Register (FOPT and NVOPT)

During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into FOPT. To change the value in this register, erase and reprogram the NVOPT location in FLASH memory as usual and then issue a new MCU reset.

= Unimplemented or Reserved

### Figure 4-6. FLASH Options Register (FOPT)

### Table 4-8. FOPT Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>KEYEN       | <ul> <li>Backdoor Key Mechanism Enable — When this bit is 0, the backdoor key mechanism cannot be used to disengage security. The backdoor key mechanism is accessible only from user (secured) firmware. BDM commands cannot be used to write key comparison values that would unlock the backdoor key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 No backdoor key access allowed.</li> <li>1 If user firmware writes an 8-byte value that matches the nonvolatile backdoor key (NVBACKKEY through NVBACKKEY+7 in that order), security is temporarily disengaged until the next MCU reset.</li> </ul> |

| 6<br>FNORED      | <ul> <li>Vector Redirection Disable — When this bit is 1, then vector redirection is disabled.</li> <li>0 Vector redirection enabled.</li> <li>1 Vector redirection disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1:0<br>SEC0[1:0] | Security State Code — This 2-bit field determines the security state of the MCU as shown in Table 4-9. When the MCU is secure, the contents of RAM and FLASH memory cannot be accessed by instructions from any unsecured source including the background debug interface. SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH. For more detailed information about security, refer to Section 4.6, "Security."                                                                                                                                                                                                           |

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address       — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                        |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

### Table 5-4. SRS Register Field Descriptions

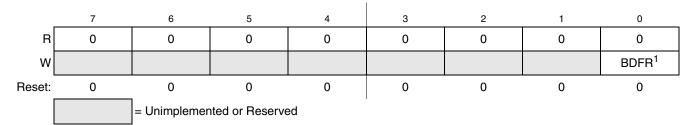

## 5.7.3 System Background Debug Force Reset Register (SBDFR)

This high page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

### Table 5-5. SBDFR Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

# Chapter 6 Parallel Input/Output Control

This section explains software controls related to parallel input/output (I/O) and pin control. The MC9S08SH32 has three parallel I/O ports which include a total of 23 I/O pins and one output-only pin. See Chapter 2, "Pins and Connections," for more information about pin assignments and external hardware considerations of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, communication systems, or pin interrupts as shown in Table 2-1. The peripheral modules have priority over the general-purpose I/O functions so that when a peripheral is enabled, the I/O functions associated with the shared pins are disabled.

After reset, the shared peripheral functions are disabled and the pins are configured as inputs (PTxDDn = 0). The pin control functions for each pin are configured as follows: slew rate disabled PTxSEn = 0, low drive strength selected (PTxDSn = 0), and internal pull-ups disabled (PTxPEn = 0).

## NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program must either enable on-chip pull-up devices or change the direction of unconnected pins to outputs so the pins do not float.

# 6.1 Port Data and Data Direction

Reading and writing of parallel I/Os are performed through the port data registers. The direction, either input or output, is controlled through the port data direction registers. The parallel I/O port function for an individual pin is illustrated in the block diagram shown in Figure 6-1.

The data direction control bit (PTxDDn) determines whether the output buffer for the associated pin is enabled, and also controls the source for port data register reads. The input buffer for the associated pin is always enabled unless the pin is enabled as an analog function or is an output-only pin.

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTxDDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

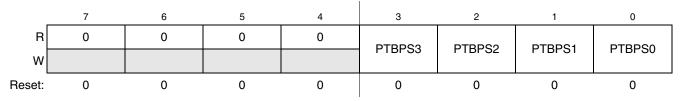

# 6.6.2.7 Port B Interrupt Pin Select Register (PTBPS)

Figure 6-17. Port B Interrupt Pin Select Register (PTBPS)

### Table 6-16. PTBPS Register Field Descriptions

| Field | Description                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Interrupt Pin Selects — Each of the PTBPSn bits enable the corresponding port B interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

## 6.6.2.8 Port B Interrupt Edge Select Register (PTBES)

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R      | 0 | 0 | 0 | 0 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| W      |   |   |   |   | FIDESS | FIDESZ | FIDEST | FIDESU |

| Reset: | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

### Figure 6-18. Port B Edge Select Register (PTBES)

### Table 6-17. PTBES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Edge Selects — Each of the PTBESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

| Table 7-3. Opcode Map                     |                        |                       |                       |                       |                       |                      |                       |                        |                      | 012)                 |                      |                      |                      |                      |                     |

|-------------------------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| Bit-Manipulation Branch Read-Modify-Write |                        |                       |                       |                       |                       |                      | ntrol                 |                        |                      |                      | /Memory              |                      |                      |                      |                     |

| 00 5<br>BRSET0<br>3 DIR                   | 10 5<br>BSET0<br>2 DIR | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH | 50 1<br>NEGX<br>1 INH | 60 5<br>NEG<br>2 IX1 | 70 4<br>NEG<br>1 IX   | 80 9<br>RTI<br>1 INH   | 90 3<br>BGE<br>2 REL | A0 2<br>SUB<br>2 IMM | SUB<br>2 DIR         | C0 4<br>SUB<br>3 EXT | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5                                      | 11 5                   | 21 3                  | 31 5                  | 41 4                  | 51 4                  | 61 5                 | 71 5                  | 81 6                   | 91 3                 | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                                    | BCLR0                  | BRN                   | CBEQ                  | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                  | RTS                    | BLT                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 3 DIR                 | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+                 | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                                      | 12 5                   | 22 3                  | 32 5                  | 42 5                  | 52 6                  | 62 1                 | 72 1                  | 82 5+                  | 92 3                 | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                                    | BSET1                  | BHI                   | LDHX                  | MUL                   | DIV                   | NSA                  | DAA                   | BGND                   | BGT                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 3 EXT                 | 1 INH                 | 1 INH                 | 1 INH                | 1 INH                 | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                                      | 13 5                   | 23 3                  | 33 5                  | 43 1                  | 53 1                  | 63 5                 | 73 4                  | 83 11                  | 93 3                 | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                                    | BCLR1                  | BLS                   | COM                   | COMA                  | COMX                  | COM                  | COM                   | SWI                    | BLE                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                                      | 14 5                   | 24 3                  | 34 5                  | 44 1                  | 54 1                  | 64 5                 | 74 4                  | 84 1                   | 94 2                 | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |

| BRSET2                                    | BSET2                  | BCC                   | LSR                   | LSRA                  | LSRX                  | LSR                  | LSR                   | TAP                    | TXS                  | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                                      | 15 5                   | 25 3                  | 35 4                  | 45 3                  | 55 4                  | 65 3                 | 75 5                  | 85 1                   | 95 2                 | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                                    | BCLR2                  | BCS                   | STHX                  | LDHX                  | LDHX                  | CPHX                 | CPHX                  | TPA                    | TSX                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                                      | 16 5                   | 26 3                  | 36 5                  | 46 1                  | 56 1                  | 66 5                 | 76 4                  | 86 3                   | 96 5                 | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                                    | BSET3                  | BNE                   | ROR                   | RORA                  | RORX                  | ROR                  | ROR                   | PULA                   | STHX                 | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                                      | 17 5                   | 27 3                  | 37 5                  | 47 1                  | 57 1                  | 67 5                 | 77 4                  | 87 2                   | 97 1                 | AIS                  | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                                    | BCLR3                  | BEQ                   | ASR                   | ASRA                  | ASRX                  | ASR                  | ASR                   | PSHA                   | TAX                  |                      | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                                      | 18 5                   | 28 3                  | 38 5                  | 48 1                  | 58 1                  | 68 5                 | 78 4                  | 88 3                   | 98 1                 | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                                    | BSET4                  | BHCC                  | LSL                   | LSLA                  | LSLX                  | LSL                  | LSL                   | PULX                   | CLC                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5<br>BRCLR4<br>3 DIR                   | 19 5<br>BCLR4<br>2 DIR | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH | 59 1<br>ROLX<br>1 INH | 69 5<br>ROL<br>2 IX1 | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX           | 99 1<br>SEC<br>1 INH |                      | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5                                      | 1A 5                   | 2A 3                  | 3A 5                  | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                  | 8A 3                   | 9A 1                 | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                                    | BSET5                  | BPL                   | DEC                   | DECA                  | DECX                  | DEC                  | DEC                   | PULH                   | CLI                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                                      | 1B 5                   | 2B 3                  | 3B 7                  | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                  | 8B 2                   | 9B 1                 | ADD                  | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                                    | BCLR5                  | BMI                   | DBNZ                  | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                  | PSHH                   | SEI                  |                      | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 3 DIR                 | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                                      | 1C 5                   | 2C 3                  | 3C 5                  | 4C 1                  | 5C 1                  | 6C 5                 | 7C 4                  | 8C 1                   | 9C 1                 |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                                    | BSET6                  | BMC                   | INC                   | INCA                  | INCX                  | INC                  | INC                   | CLRH                   | RSP                  |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                                      | 1D 5                   | 2D 3                  | 3D 4                  | 4D 1                  | 5D 1                  | 6D 4                 | 7D 3                  |                        | 9D 1                 | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                                    | BCLR6                  | BMS                   | TST                   | TSTA                  | TSTX                  | TST                  | TST                   |                        | NOP                  | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  |                        | 1 INH                | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR                   | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2         | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                                      | 1F 5                   | 2F 3                  | 3F 5                  | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1                 | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                                    | BCLR7                  | BIH                   | CLR                   | CLRA                  | CLRX                  | CLR                  | CLR                   | WAIT                   | TXA                  | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08SH32 Series Data Sheet, Rev. 3

Opcode in Hexadecimal F0 3 SUB 1 IX HCS08 Cycles Instruction Mnemonic Addressing Mode

| ADICLK | Selected Clock Source      |

|--------|----------------------------|

| 00     | Bus clock                  |

| 01     | Bus clock divided by 2     |

| 10     | Alternate clock (ALTCLK)   |

| 11     | Asynchronous clock (ADACK) |

### Table 9-8. Input Clock Select

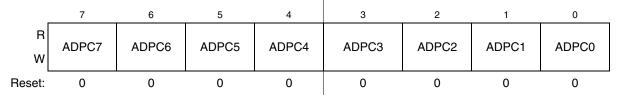

#### Pin Control 1 Register (APCTL1) 9.3.8

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 9-12.

| Conversion Type                                            | ADICLK | ADLSMP | Max Total Conversion Time                |

|------------------------------------------------------------|--------|--------|------------------------------------------|

| Single or first continuous 8-bit                           | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 0      | 5 $\mu$ s + 20 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit                          | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles      |

| Single or first continuous 8-bit                           | 11     | 1      | 5 μs + 40 ADCK + 5 bus clock cycles      |

| Single or first continuous 10-bit                          | 11     | 1      | 5 $\mu$ s + 43 ADCK + 5 bus clock cycles |

| Subsequent continuous 8-bit; $f_{BUS} \ge f_{ADCK}$        | xx     | 0      | 17 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}$    | xx     | 0      | 20 ADCK cycles                           |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}/11$  | xx     | 1      | 37 ADCK cycles                           |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}/11$ | xx     | 1      | 40 ADCK cycles                           |

Table 9-12. Total Conversion Time vs. Control Conditions

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1 ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

Conversion time =  $\frac{23 \text{ ADCK cyc}}{8 \text{ MHz/1}} + \frac{5 \text{ bus cyc}}{8 \text{ MHz}} = 3.5 \text{ }\mu\text{s}$

Number of bus cycles =  $3.5 \ \mu s \ x \ 8 \ MHz = 28 \ cycles$

## NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet ADC specifications.

MC9S08SH32 Series Data Sheet, Rev. 3

### Table 10-7. IICS Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TCF   | <ul> <li>Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                         |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave address or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.</li> <li>0 Not addressed</li> <li>1 Addressed as a slave</li> </ul>                                                                                                                    |

| 5<br>BUSY  | <ul> <li>Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.</li> <li>0 Bus is idle</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                    |

| 4<br>ARBL  | <ul> <li>Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.</li> <li>0 Standard bus operation</li> <li>1 Loss of arbitration</li> </ul>                                                                                                                                                                       |

| 2<br>SRW   | <ul> <li>Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>O Slave receive, master writing to slave</li> <li>1 Slave transmit, master reading from slave</li> </ul>                                                                                                                                       |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit:</li> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> <li>No interrupt pending</li> <li>1 Interrupt pending</li> </ul> |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received</li> <li>1 No acknowledge received</li> </ul>                                                                           |

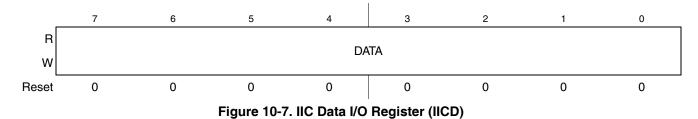

# 10.3.5 IIC Data I/O Register (IICD)

MC9S08SH32 Series Data Sheet, Rev. 3

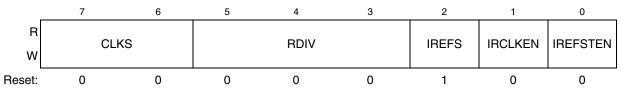

# 11.3.1 ICS Control Register 1 (ICSC1)

Figure 11-3. ICS Control Register 1 (ICSC1)

| Table 11-2. ICS Control Register 1 F | ield Descriptions |

|--------------------------------------|-------------------|

|--------------------------------------|-------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | <ul> <li>Clock Source Select — Selects the clock source that controls the bus frequency. The actual bus frequency depends on the value of the BDIV bits.</li> <li>O Output of FLL is selected.</li> <li>O1 Internal reference clock is selected.</li> <li>10 External reference clock is selected.</li> <li>11 Reserved, defaults to 00.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

| 5:3<br>RDIV   | Reference Divider — Selects the amount to divide down the FLL reference clock selected by the IREFS bits.         Resulting frequency must be in the range 31.25 kHz to 39.0625 kHz.         000       Encoding 0 — Divides reference clock by 1 (reset default)         001       Encoding 1 — Divides reference clock by 2         010       Encoding 2 — Divides reference clock by 4         011       Encoding 3 — Divides reference clock by 8         100       Encoding 4 — Divides reference clock by 16         101       Encoding 5 — Divides reference clock by 32         110       Encoding 6 — Divides reference clock by 64         111       Encoding 7 — Divides reference clock by 128 |

| 2<br>IREFS    | Internal Reference Select — The IREFS bit selects the reference clock source for the FLL.<br>1 Internal reference clock selected<br>0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — The IRCLKEN bit enables the internal reference clock for use as<br>ICSIRCLK.<br>1 ICSIRCLK active<br>0 ICSIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — The IREFSTEN bit controls whether or not the internal reference clock remains enabled when the ICS enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if ICS is in FEI, FBI, or FBILP mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul>                                                                                                                                                                                                                                                                                                                                |

| Chapter 13 Real-Time           | Counter (S08RTC) | /1)      |         |          |      |          |

|--------------------------------|------------------|----------|---------|----------|------|----------|

| •                              | ,                | ,        |         |          |      |          |

| Internal 1-kHz<br>Clock Source |                  | nnn      | nnn     | nnn      |      | nnn      |

| RTC Clock<br>(RTCPS = 0xA)     |                  | <u> </u> | <u></u> | <u> </u> |      | <u> </u> |

| RTCCNT                         | 0x52             | 0x53     | 0x54    | 0x55     | 0x00 | 0x01     |

|                                |                  |          |         |          |      |          |

| RTIF                           |                  |          |         |          |      |          |

|                                |                  |          |         |          |      |          |

| RTCMOD                         |                  |          | 0x      | 55       |      |          |

Figure 13-6. RTC Counter Overflow Example

In the example of Figure 13-6, the selected clock source is the 1-kHz internal oscillator clock source. The prescaler (RTCPS) is set to 0xA or divide-by-4. The modulo value in the RTCMOD register is set to 0x55. When the counter, RTCCNT, reaches the modulo value of 0x55, the counter overflows to 0x00 and continues counting. The real-time interrupt flag, RTIF, sets when the counter value changes from 0x55 to 0x00. A real-time interrupt is generated when RTIF is set, if RTIE is set.

# 13.5 Initialization/Application Information

This section provides example code to give some basic direction to a user on how to initialize and configure the RTC module. The example software is implemented in C language.

The example below shows how to implement time of day with the RTC using the 1-kHz clock source to achieve the lowest possible power consumption. Because the 1-kHz clock source is not as accurate as a crystal, software can be added for any adjustments. For accuracy without adjustments at the expense of additional power consumption, the external clock (ERCLK) or the internal clock (IRCLK) can be selected with appropriate prescaler and modulo values.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0 Transmitter active (sending data, a preamble, or a break).         1 Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:         • Write to the SCI data register (SCIxD) to transmit new data         • Queue a preamble by changing TE from 0 to 1         • Queue a break character by writing 1 to SBK in SCIxC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). To clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD).</li> <li>0 Receive data register empty.</li> <li>1 Receive data register full.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of<br>activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is<br>all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times<br>depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't<br>start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the<br>previous character do not count toward the full character time of logic high needed for the receiver to detect an<br>idle line.To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been<br>cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE<br>will get set only once even if the receive line remains idle for an extended period.0No idle line detected.1Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Table 14-5. SCIxS1 Field Descriptions

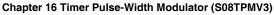

$\triangle$  = Pin can be enabled as part of the ganged output drive feature

- NOTE: PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages: VDDA/VREFH and VSSA/VREFL, are double bonded to VDD and VSS respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 16-1. MC9S08SH32 Series Block Diagram Highlighting TPM Block and Pins

### Chapter 16 Timer/PWM Module (S08TPMV3)

The TPM channels are programmable independently as input capture, output compare, or edge-aligned PWM channels. Alternately, the TPM can be configured to produce CPWM outputs on all channels. When the TPM is configured for CPWMs, the counter operates as an up/down counter; input capture, output compare, and EPWM functions are not practical.

If a channel is configured as input capture, an internal pullup device may be enabled for that channel. The details of how a module interacts with pin controls depends upon the chip implementation because the I/O pins and associated general purpose I/O controls are not part of the module. Refer to the discussion of the I/O port logic in a full-chip specification.

Because center-aligned PWMs are usually used to drive 3-phase AC-induction motors and brushless DC motors, they are typically used in sets of three or six channels.

# 16.2 Signal Description

Table 16-2 shows the user-accessible signals for the TPM. The number of channels may be varied from one to eight. When an external clock is included, it can be shared with the same pin as any TPM channel; however, it could be connected to a separate input pin. Refer to the I/O pin descriptions in full-chip specification for the specific chip implementation.

| Name                 | Function                                                              |

|----------------------|-----------------------------------------------------------------------|

| EXTCLK <sup>1</sup>  | External clock source which may be selected to drive the TPM counter. |

| TPMxCHn <sup>2</sup> | I/O pin associated with TPM channel n                                 |

**Table 16-2. Signal Properties**

<sup>1</sup> When preset, this signal can share any channel pin; however depending upon full-chip implementation, this signal could be connected to a separate external pin.

<sup>2</sup> n=channel number (1 to 8)

Refer to documentation for the full-chip for details about reset states, port connections, and whether there is any pullup device on these pins.

TPM channel pins can be associated with general purpose I/O pins and have passive pullup devices which can be enabled with a control bit when the TPM or general purpose I/O controls have configured the associated pin as an input. When no TPM function is enabled to use a corresponding pin, the pin reverts to being controlled by general purpose I/O controls, including the port-data and data-direction registers. Immediately after reset, no TPM functions are enabled, so all associated pins revert to general purpose I/O control.

# 16.2.1 Detailed Signal Descriptions

This section describes each user-accessible pin signal in detail. Although Table 16-2 grouped all channel pins together, any TPM pin can be shared with the external clock source signal. Since I/O pin logic is not part of the TPM, refer to full-chip documentation for a specific derivative for more details about the interaction of TPM pin functions and general purpose I/O controls including port data, data direction, and pullup controls.

Chapter 16 Timer/PWM Module (S08TPMV3)

## 16.6.2.1.2 Center-Aligned PWM Case

When CPWMS=1, TOF gets set when the timer counter changes direction from up-counting to down-counting at the end of the terminal count (the value in the modulo register). In this case the TOF corresponds to the end of a PWM period.

## 16.6.2.2 Channel Event Interrupt Description

The meaning of channel interrupts depends on the channel's current mode (input-capture, output-compare, edge-aligned PWM, or center-aligned PWM).

## 16.6.2.2.1 Input Capture Events

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select no edge (off), rising edges, falling edges or any edge as the edge which triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the two-step sequence described in Section 16.6.2, "Description of Interrupt Operation."

## 16.6.2.2.2 Output Compare Events

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the two-step sequence described Section 16.6.2, "Description of Interrupt Operation."

## 16.6.2.2.3 PWM End-of-Duty-Cycle Events

For channels configured for PWM operation there are two possibilities. When the channel is configured for edge-aligned PWM, the channel flag gets set when the timer counter matches the channel value register which marks the end of the active duty cycle period. When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle period which are the times when the timer counter matches the channel value register. The flag is cleared by the two-step sequence described Section 16.6.2, "Description of Interrupt Operation."

# 17.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

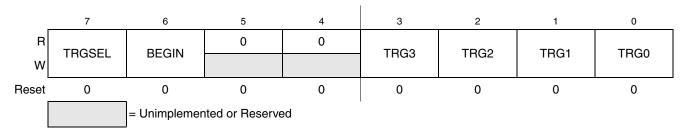

### Figure 17-8. Debug Trigger Register (DBGT)

### Table 17-5. DBGT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TRGSEL     | <ul> <li>Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.</li> <li>0 Trigger on access to compare address (force)</li> <li>1 Trigger if opcode at compare address is executed (tag)</li> </ul> |

| 6<br>BEGIN      | <ul> <li>Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.</li> <li>0 Data stored in FIFO until trigger (end trace)</li> <li>1 Trigger initiates data storage (begin trace)</li> </ul>                                                                                                             |

| 3:0<br>TRG[3:0] | Select Trigger ModeSelects one of nine triggering modes, as described below.0000A-only0001A OR B0010A Then B0011Event-only B (store data)0100A then event-only B (store data)0101A AND B data (full mode)0110A AND NOT B data (full mode)0111Inside range: $A \leq address \leq B$ 1000Outside range: address < A or address > B1001- 1111 (No trigger)                                                                                                                                                              |

Appendix A Electrical Characteristics

# A.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

| #  | С | Characteristic                                                 | Symbol                           | Condition                                                             | Min                    | Typ <sup>1</sup> | Max                  | Unit |

|----|---|----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|------------------------|------------------|----------------------|------|

| 1  |   | Operating Voltage                                              | V <sub>DD</sub>                  | —                                                                     | 2.7                    |                  | 5.5                  | V    |

|    | С | All I/O pins,                                                  |                                  | 5 V, $I_{Load} = -4 \text{ mA}$                                       | V <sub>DD</sub> – 1.5  | _                | —                    | V    |

|    | Ρ | low-drive strength                                             |                                  | 5 V, $I_{Load} = -2 \text{ mA}$                                       | V <sub>DD</sub> – 0.8  | _                | —                    | V    |

| 2  | С | Output high                                                    | V <sub>OH</sub>                  | 3 V, $I_{Load} = -1 \text{ mA}$                                       | V <sub>DD</sub> – 0.8  | _                | —                    | V    |

| 2  | С | voltage                                                        |                                  | 5 V, $I_{Load} = -20 \text{ mA}$                                      | V <sub>DD</sub> – 1.5  |                  | —                    | V    |

|    | Ρ | All I/O pins,                                                  |                                  | 5 V, $I_{Load} = -10 \text{ mA}$                                      | V <sub>DD</sub> – 0.8  |                  | —                    | V    |

|    | С | high-drive strength                                            |                                  | 3 V, I <sub>Load</sub> = -5 mA                                        | V <sub>DD</sub> – 0.8  |                  | —                    | V    |

| 3  | D | Output high Max total I <sub>OH</sub> for<br>current all ports | I <sub>OHT</sub>                 | $V_{OUT} < V_{DD}$                                                    | 0                      |                  | -100                 | mA   |

|    | С | All I/O pins                                                   |                                  | 5 V, I <sub>Load</sub> = 4 mA                                         | _                      | _                | 1.5                  | V    |

|    | Ρ | low-drive strength                                             |                                  | 5 V, I <sub>Load</sub> = 2 mA                                         | _                      | _                | 0.8                  | V    |

| 4  | С | Output low                                                     | V <sub>OL</sub>                  | 3 V, I <sub>Load</sub> = 1 mA                                         | _                      | _                | 0.8                  | V    |

| -  | С | voltage                                                        |                                  | 5 V, I <sub>Load</sub> = 20 mA                                        | —                      |                  | 1.5                  | V    |