# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 28-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh32ctl |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

Title

### Page

|      | 11.1.1   | Module Configuration              | 167 |

|------|----------|-----------------------------------|-----|

|      |          | Features                          |     |

|      | 11.1.3   | Block Diagram                     | 169 |

|      | 11.1.4   | Modes of Operation                | 170 |

| 11.2 | External | Signal Description                | 171 |

|      |          | Definition                        |     |

|      | 11.3.1   | ICS Control Register 1 (ICSC1)    | 172 |

|      |          | ICS Control Register 2 (ICSC2)    |     |

|      |          | ICS Trim Register (ICSTRM)        |     |

|      |          | ICS Status and Control (ICSSC)    |     |

| 11.4 | Function | nal Description                   | 175 |

|      | 11.4.1   | Operational Modes                 | 175 |

|      | 11.4.2   | Mode Switching                    | 177 |

|      | 11.4.3   | Bus Frequency Divider             | 178 |

|      | 11.4.4   | Low Power Bit Usage               | 178 |

|      | 11.4.5   | Internal Reference Clock          | 178 |

|      | 11.4.6   | Optional External Reference Clock | 178 |

|      | 11.4.7   | Fixed Frequency Clock             | 179 |

|      |          |                                   |     |

# Chapter 12 Modulo Timer (S08MTIMV1)

| Introduction                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.1.1 MTIM Configuration Information              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.1.2 Features                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.1.3 Modes of Operation                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Definition                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.3.1 MTIM Status and Control Register (MTIMSC)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.3.2 MTIM Clock Configuration Register (MTIMCLK) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.3.3 MTIM Counter Register (MTIMCNT)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.3.4 MTIM Modulo Register (MTIMMOD)              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Functional Description                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12.4.1 MTIM Operation Example                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                    | <ul> <li>12.1.1 MTIM Configuration Information</li> <li>12.1.2 Features</li> <li>12.1.3 Modes of Operation</li> <li>12.1.4 Block Diagram</li> <li>External Signal Description</li> <li>Register Definition</li> <li>12.3.1 MTIM Status and Control Register (MTIMSC)</li> <li>12.3.2 MTIM Clock Configuration Register (MTIMCLK)</li> <li>12.3.3 MTIM Counter Register (MTIMCNT)</li> <li>12.3.4 MTIM Modulo Register (MTIMMOD)</li> <li>Functional Description</li> </ul> |

# Chapter 13 Real-Time Counter (S08RTCV1)

| 13.1 | Introduction                | 191 |

|------|-----------------------------|-----|

|      | 13.1.1 Features             | 193 |

|      | 13.1.2 Modes of Operation   | 193 |

|      | 13.1.3 Block Diagram        | 194 |

| 13.2 | External Signal Description |     |

MC9S08SH32 Series Data Sheet, Rev. 3

# **Section Number**

Title

### Page

| 15.4 | Register Definition                    | 227 |

|------|----------------------------------------|-----|

|      | 15.4.1 SPI Control Register 1 (SPIxC1) |     |

|      | 15.4.2 SPI Control Register 2 (SPIxC2) | 228 |

|      | 15.4.3 SPI Baud Rate Register (SPIxBR) | 229 |

|      | 15.4.4 SPI Status Register (SPIxS)     | 230 |

|      | 15.4.5 SPI Data Register (SPIxD)       | 231 |

| 15.5 | Functional Description                 | 232 |

|      | 15.5.1 SPI Clock Formats               | 232 |

|      | 15.5.2 SPI Interrupts                  | 235 |

|      | 15.5.3 Mode Fault Detection            |     |

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV3)

| 16.1 | Introduction                                                | 237 |

|------|-------------------------------------------------------------|-----|

|      | 16.1.1 TPM Configuration Information                        | 237 |

|      | 16.1.2 TPM Pin Repositioning                                | 237 |

|      | 16.1.3 Features                                             |     |

|      | 16.1.4 Modes of Operation                                   | 239 |

|      | 16.1.5 Block Diagram                                        | 240 |

| 16.2 | Signal Description                                          |     |

|      | 16.2.1 Detailed Signal Descriptions                         |     |

| 16.3 | Register Definition                                         |     |

|      | 16.3.1 TPM Status and Control Register (TPMxSC)             |     |

|      | 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL)            |     |

|      | 16.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)     |     |

|      | 16.3.4 TPM Channel n Status and Control Register (TPMxCnSC) |     |

|      | 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)      |     |

| 16.4 | Functional Description                                      | 252 |

|      | 16.4.1 Counter                                              | 253 |

|      | 16.4.2 Channel Mode Selection                               | 255 |

| 16.5 | Reset Overview                                              |     |

|      | 16.5.1 General                                              |     |

|      | 16.5.2 Description of Reset Operation                       |     |

| 16.6 | Interrupts                                                  |     |

|      | 16.6.1 General                                              |     |

|      | 16.6.2 Description of Interrupt Operation                   | 259 |

|      |                                                             |     |

# Chapter 17 Development Support

| 17.1 | Introduction                     | 261 |

|------|----------------------------------|-----|

|      | 17.1.1 Forcing Active Background |     |

|      | 17.1.2 Features                  |     |

MC9S08SH32 Series Data Sheet, Rev. 3

Chapter 2 Pins and Connections

| Devinhevel              | Mode             |                            |  |  |  |  |

|-------------------------|------------------|----------------------------|--|--|--|--|

| Peripheral              | Stop2            | Stop3                      |  |  |  |  |

| CPU                     | Off              | Standby                    |  |  |  |  |

| RAM                     | Standby          | Standby                    |  |  |  |  |

| FLASH                   | Off              | Standby                    |  |  |  |  |

| Parallel Port Registers | Off              | Standby                    |  |  |  |  |

| ADC                     | Off              | Optionally On <sup>1</sup> |  |  |  |  |

| ACMP                    | Off              | Optionally On <sup>2</sup> |  |  |  |  |

| BDM                     | Off <sup>3</sup> | Optionally On              |  |  |  |  |

| ICS                     | Off              | Optionally On <sup>4</sup> |  |  |  |  |

| IIC                     | Off              | Standby                    |  |  |  |  |

| LVD/LVW                 | Off <sup>5</sup> | Optionally On              |  |  |  |  |

| MTIM                    | Off              | Standby                    |  |  |  |  |

| RTC                     | Optionally On    | Optionally On              |  |  |  |  |

| SCI                     | Off              | Standby                    |  |  |  |  |

| SPI                     | Off              | Standby                    |  |  |  |  |

| ТРМ                     | Off              | Standby                    |  |  |  |  |

| Voltage Regulator       | Standby          | Optionally On <sup>6</sup> |  |  |  |  |

| XOSC                    | Off              | Optionally On <sup>7</sup> |  |  |  |  |

| I/O Pins                | States Held      | States Held                |  |  |  |  |

#### Table 3-2. Stop Mode Behavior

<sup>1</sup> Requires the asynchronous ADC clock and LVD to be enabled, else in standby.

<sup>2</sup> Requires the LVD to be enabled when compare to internal bandgap reference option is enabled.

- <sup>3</sup> If ENBDM is set when entering stop2, the MCU will actually enter stop3.

- <sup>4</sup> IRCLKEN and IREFSTEN set in ICSC1, else in standby.

- <sup>5</sup> If LVDSE is set when entering stop2, the MCU will actually enter stop3.

- <sup>6</sup> Voltage regulator will be on if BDM is enabled or if LVD is enabled when entering stop3.

<sup>7</sup> ERCLKEN and EREFSTEN set in ICSC2, else in standby. For high frequency range (RANGE in ICSC2 set) requires the LVD to also be enabled in stop3.

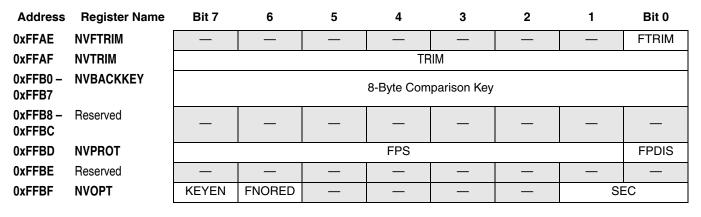

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key, NVBACKKEY, which can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

#### Table 4-4. Nonvolatile Register Summary

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the FLASH if needed (normally through the background debug interface) and verifying that FLASH is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC) to the unsecured state (1:0).

Chapter 5 Resets, Interrupts, and General System Control

# 5.7.5 System Options Register 2 (SOPT2)

This high page register contains bits to configure MCU specific features on the MC9S08SH32 Series devices.

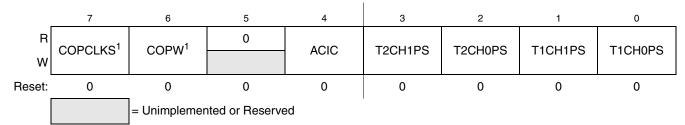

#### Figure 5-6. System Options Register 2 (SOPT2)

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Table 5-7. SOPT2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPCLKS | <ul> <li>COP Watchdog Clock Select — This write-once bit selects the clock source of the COP watchdog.</li> <li>Internal 1-kHz clock is source to COP.</li> <li>Bus clock is source to COP.</li> </ul>                                                                                                                                                                                 |

| 6<br>COPW    | <ul> <li>COP Window — This write-once bit selects the COP operation mode. When set, the 0x55-0xAA write sequence to the SRS register must occur in the last 25% of the selected period. Any write to the SRS register during the first 75% of the selected period will reset the MCU.</li> <li>0 Normal COP operation</li> <li>1 Window COP operation (only if COPCLKS = 1)</li> </ul> |

| 4<br>ACIC    | <ul> <li>Analog Comparator to Input Capture Enable— This bit connects the output of ACMP to TPM1 input channel 0.</li> <li>0 ACMP output not connected to TPM1 input channel 0.</li> <li>1 ACMP output connected to TPM1 input channel 0.</li> </ul>                                                                                                                                   |

| 3<br>T2CH1PS | <ul> <li>TPM2CH1 Pin Select— This selects the location of the TPM2CH1 pin of the TPM2 module.</li> <li>TPM2CH1 on PTB4.</li> <li>TPM2CH1 on PTA7.</li> </ul>                                                                                                                                                                                                                           |

| 2<br>T2CH0PS | <ul> <li>TPM2CH0 Pin Select— This bit selects the location of the TPM2CH0 pin of the TPM2 module.</li> <li>0 TPM2CH0 on PTA1.</li> <li>1 TPM2CH0 on PTA6.</li> </ul>                                                                                                                                                                                                                   |

| 1<br>T1CH1PS | <ul> <li>TPM1CH1 Pin Select— This selects the location of the TPM1CH1 pin of the TPM1 module.</li> <li>0 TPM1CH1 on PTB5.</li> <li>1 TPM1CH1 on PTC1.</li> </ul>                                                                                                                                                                                                                       |

| 0<br>T1CH0PS | <ul> <li>TPM1CH0 Pin Select— This bit selects the location of the TPM1CH0 pin of the TPM1 module.</li> <li>TPM1CH0 on PTA0.</li> <li>TPM1CH0 on PTC0.</li> </ul>                                                                                                                                                                                                                       |

# Chapter 7 Central Processor Unit (S08CPUV3)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

# 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08SH32 Series Data Sheet, Rev. 3

### 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

# 7.4.1 Reset Sequence

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction boundary before responding to a reset event). For a more detailed discussion about how the MCU recognizes resets and determines the source, refer to the Resets, Interrupts, and System Configuration chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the instruction queue in preparation for execution of the first program instruction.

## 7.4.2 Interrupt Sequence

When an interrupt is requested, the CPU completes the current instruction before responding to the interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence started.

The CPU sequence for an interrupt is:

- 1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

- 2. Set the I bit in the CCR.

- 3. Fetch the high-order half of the interrupt vector.

- 4. Fetch the low-order half of the interrupt vector.

- 5. Delay for one free bus cycle.

- 6. Fetch three bytes of program information starting at the address indicated by the interrupt vector to fill the instruction queue in preparation for execution of the first instruction in the interrupt service routine.

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

|                         | Table 7-3. Opcode Map (Sheet 1 of 2) |                       |                       |                       |                       |                      |                       |                        |                      |                      |                      |                      |                      |                      |                     |

|-------------------------|--------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

|                         | ipulation                            | Branch                |                       |                       | d-Modify-W            |                      | i                     |                        | ntrol                |                      |                      |                      | /Memory              |                      |                     |

| 00 5<br>BRSET0<br>3 DIR | 10 5<br>BSET0<br>2 DIR               | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH | 50 1<br>NEGX<br>1 INH | 60 5<br>NEG<br>2 IX1 | 70 4<br>NEG<br>1 IX   | 80 9<br>RTI<br>1 INH   | 90 3<br>BGE<br>2 REL | A0 2<br>SUB<br>2 IMM | SUB<br>2 DIR         | C0 4<br>SUB<br>3 EXT | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5                    | 11 5                                 | 21 3                  | 31 5                  | 41 4                  | 51 4                  | 61 5                 | 71 5                  | 81 6                   | 91 3                 | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                  | BCLR0                                | BRN                   | CBEQ                  | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                  | RTS                    | BLT                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 3 DIR                 | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+                 | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                    | 12 5                                 | 22 3                  | 32 5                  | 42 5                  | 52 6                  | 62 1                 | 72 1                  | 82 5+                  | 92 3                 | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                  | BSET1                                | BHI                   | LDHX                  | MUL                   | DIV                   | NSA                  | DAA                   | BGND                   | BGT                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 3 EXT                 | 1 INH                 | 1 INH                 | 1 INH                | 1 INH                 | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                    | 13 5                                 | 23 3                  | 33 5                  | 43 1                  | 53 1                  | 63 5                 | 73 4                  | 83 11                  | 93 3                 | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                  | BCLR1                                | BLS                   | COM                   | COMA                  | COMX                  | COM                  | COM                   | SWI                    | BLE                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                    | 14 5                                 | 24 3                  | 34 5                  | 44 1                  | 54 1                  | 64 5                 | 74 4                  | 84 1                   | 94 2                 | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |

| BRSET2                  | BSET2                                | BCC                   | LSR                   | LSRA                  | LSRX                  | LSR                  | LSR                   | TAP                    | TXS                  | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                    | 15 5                                 | 25 3                  | 35 4                  | 45 3                  | 55 4                  | 65 3                 | 75 5                  | 85 1                   | 95 2                 | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                  | BCLR2                                | BCS                   | STHX                  | LDHX                  | LDHX                  | CPHX                 | CPHX                  | TPA                    | TSX                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                    | 16 5                                 | 26 3                  | 36 5                  | 46 1                  | 56 1                  | 66 5                 | 76 4                  | 86 3                   | 96 5                 | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                  | BSET3                                | BNE                   | ROR                   | RORA                  | RORX                  | ROR                  | ROR                   | PULA                   | STHX                 | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                    | 17 5                                 | 27 3                  | 37 5                  | 47 1                  | 57 1                  | 67 5                 | 77 4                  | 87 2                   | 97 1                 | AIS                  | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                  | BCLR3                                | BEQ                   | ASR                   | ASRA                  | ASRX                  | ASR                  | ASR                   | PSHA                   | TAX                  |                      | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                    | 18 5                                 | 28 3                  | 38 5                  | 48 1                  | 58 1                  | 68 5                 | 78 4                  | 88 3                   | 98 1                 | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                  | BSET4                                | BHCC                  | LSL                   | LSLA                  | LSLX                  | LSL                  | LSL                   | PULX                   | CLC                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5<br>BRCLR4<br>3 DIR | 19 5<br>BCLR4<br>2 DIR               | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH | 59 1<br>ROLX<br>1 INH | 69 5<br>ROL<br>2 IX1 | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX           | 99 1<br>SEC<br>1 INH |                      | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5                    | 1A 5                                 | 2A 3                  | 3A 5                  | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                  | 8A 3                   | 9A 1                 | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                  | BSET5                                | BPL                   | DEC                   | DECA                  | DECX                  | DEC                  | DEC                   | PULH                   | CLI                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                    | 1B 5                                 | 2B 3                  | 3B 7                  | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                  | 8B 2                   | 9B 1                 | ADD                  | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                  | BCLR5                                | BMI                   | DBNZ                  | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                  | PSHH                   | SEI                  |                      | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 3 DIR                 | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                    | 1C 5                                 | 2C 3                  | 3C 5                  | 4C 1                  | 5C 1                  | 6C 5                 | 7C 4                  | 8C 1                   | 9C 1                 |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                  | BSET6                                | BMC                   | INC                   | INCA                  | INCX                  | INC                  | INC                   | CLRH                   | RSP                  |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                    | 1D 5                                 | 2D 3                  | 3D 4                  | 4D 1                  | 5D 1                  | 6D 4                 | 7D 3                  |                        | 9D 1                 | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                  | BCLR6                                | BMS                   | TST                   | TSTA                  | TSTX                  | TST                  | TST                   |                        | NOP                  | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  |                        | 1 INH                | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR               | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2         | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                    | 1F 5                                 | 2F 3                  | 3F 5                  | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1                 | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                  | BCLR7                                | BIH                   | CLR                   | CLRA                  | CLRX                  | CLR                  | CLR                   | WAIT                   | TXA                  | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                   | 2 DIR                                | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

#### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08SH32 Series Data Sheet, Rev. 3

Opcode in Hexadecimal F0 3 SUB 1 IX HCS08 Cycles Instruction Mnemonic Addressing Mode

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

| ADCH  | Input Select |

|-------|--------------|

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

#### Figure 9-4. Input Channel Select (continued)

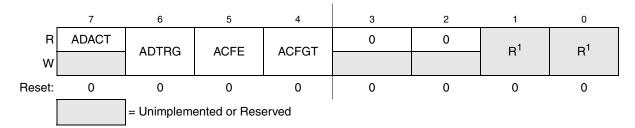

# 9.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

#### Figure 9-5. Status and Control Register 2 (ADCSC2)

#### Table 9-4. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | <ul> <li>Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>0 Conversion not in progress</li> <li>1 Conversion in progress</li> </ul>                                                                                                                                                                                                                              |

| 6<br>ADTRG | <ul> <li>Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion.</li> <li>Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.</li> <li>Software trigger selected</li> <li>Hardware trigger selected</li> </ul> |

Chapter 12 Modulo Timer (S08MTIMV1)

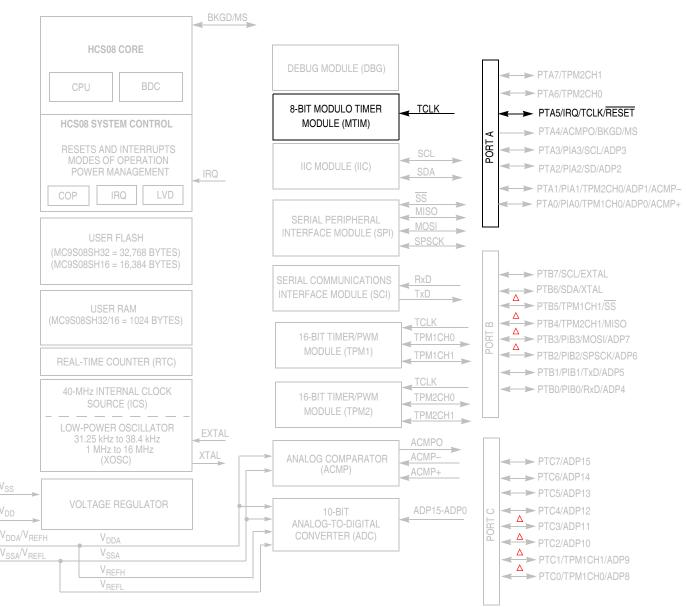

$\triangle$  = Pin can be enabled as part of the ganged output drive feature

- NOTE: PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages: V<sub>DDA</sub>/V<sub>REFH</sub> and V<sub>SSA</sub>/V<sub>REFL</sub>, are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 12-1. MC9S08SH32 Series Block Diagram Highlighting MTIM Block and Pins

# 12.1.2 Features

Timer system features include:

- 8-bit up-counter

- Free-running or 8-bit modulo limit

- Software controllable interrupt on overflow

- Counter reset bit (TRST)

- Counter stop bit (TSTP)

- Four software selectable clock sources for input to prescaler:

- System bus clock rising edge

- Fixed frequency clock (XCLK) rising edge

- External clock source on the TCLK pin rising edge

- External clock source on the TCLK pin falling edge

- Nine selectable clock prescale values:

- Clock source divide by 1, 2, 4, 8, 16, 32, 64, 128, or 256

## 12.1.3 Modes of Operation

This section defines the MTIM's operation in stop, wait and background debug modes.

### 12.1.3.1 MTIM in Wait Mode

The MTIM continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the MTIM can be used to bring the MCU out of wait mode if the timer overflow interrupt is enabled. For lowest possible current consumption, the MTIM should be stopped by software if not needed as an interrupt source during wait mode.

### 12.1.3.2 MTIM in Stop Modes

The MTIM is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the MTIM cannot be used as a wake up source from stop modes.

Waking from stop1 and stop2 modes, the MTIM will be put into its reset state. If stop3 is exited with a reset, the MTIM will be put into its reset state. If stop3 is exited with an interrupt, the MTIM continues from the state it was in when stop3 was entered. If the counter was active upon entering stop3, the count will resume from the current value.

## 12.1.3.3 MTIM in Active Background Mode

The MTIM suspends all counting until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as an MTIM reset did not occur (TRST written to a 1 or MTIMMOD written).

#### Chapter 13 Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

{

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59){

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59){

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23) {

Days ++;

Hours = 0;

}

```

# 14.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- · Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

### 14.1.2 Modes of Operation

See Section 14.3, "Functional Description," For details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Stop mode operation

- Loop mode

- Single-wire mode

Chapter 14 Serial Communications Interface (S08SCIV4)

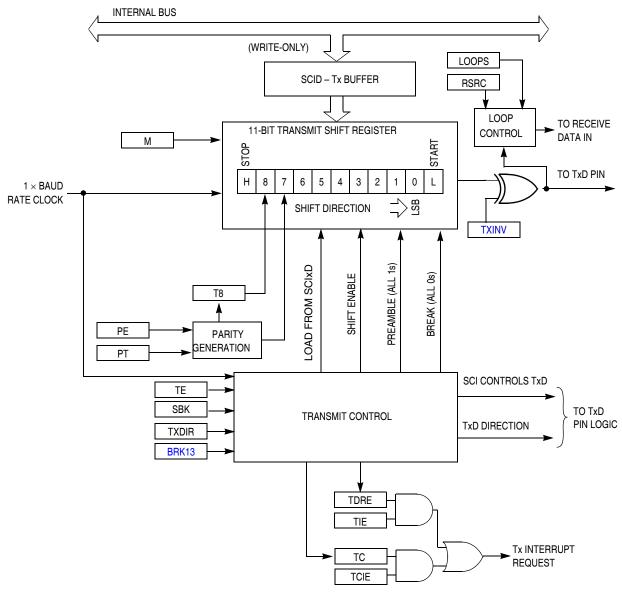

# 14.1.3 Block Diagram

Figure 14-2 shows the transmitter portion of the SCI.

Figure 14-2. SCI Transmitter Block Diagram

message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

### 14.3.3.2.1 Idle-Line Wakeup

When WAKE = 0, the receiver is configured for idle-line wakeup. In this mode, RWU is cleared automatically when the receiver detects a full character time of the idle-line level. The M control bit selects 8-bit or 9-bit data mode that determines how many bit times of idle are needed to constitute a full character time (10 or 11 bit times because of the start and stop bits).

When RWU is one and RWUID is zero, the idle condition that wakes up the receiver does not set the IDLE flag. The receiver wakes up and waits for the first data character of the next message which will set the RDRF flag and generate an interrupt if enabled. When RWUID is one, any idle condition sets the IDLE flag and generates an interrupt if enabled, regardless of whether RWU is zero or one.

The idle-line type (ILT) control bit selects one of two ways to detect an idle line. When ILT = 0, the idle bit counter starts after the start bit so the stop bit and any logic 1s at the end of a character count toward the full character time of idle. When ILT = 1, the idle bit counter does not start until after a stop bit time, so the idle detection is not affected by the data in the last character of the previous message.

### 14.3.3.2.2 Address-Mark Wakeup

When WAKE = 1, the receiver is configured for address-mark wakeup. In this mode, RWU is cleared automatically when the receiver detects a logic 1 in the most significant bit of a received character (eighth bit in M = 0 mode and ninth bit in M = 1 mode).

Address-mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames. The logic 1 MSB of an address frame clears the RWU bit before the stop bit is received and sets the RDRF flag. In this case the character with the MSB set is received even though the receiver was sleeping during most of this character time.

## 14.3.4 Interrupts and Status Flags

The SCI system has three separate interrupt vectors to reduce the amount of software needed to isolate the cause of the interrupt. One interrupt vector is associated with the transmitter for TDRE and TC events. Another interrupt vector is associated with the receiver for RDRF, IDLE, RXEDGIF and LBKDIF events, and a third vector is used for OR, NF, FE, and PF error conditions. Each of these ten interrupt sources can be separately masked by local interrupt enable masks. The flags can still be polled by software when the local masks are cleared to disable generation of hardware interrupt requests.

The SCI transmitter has two status flags that optionally can generate hardware interrupt requests. Transmit data register empty (TDRE) indicates when there is room in the transmit data buffer to write another transmit character to SCIxD. If the transmit interrupt enable (TIE) bit is set, a hardware interrupt will be requested whenever TDRE = 1. Transmit complete (TC) indicates that the transmitter is finished transmitting all data, preamble, and break characters and is idle with TxD at the inactive level. This flag is often used in systems with modems to determine when it is safe to turn off the modem. If the transmit complete interrupt enable (TCIE) bit is set, a hardware interrupt will be requested whenever TC = 1.

Chapter 15 Serial Peripheral Interface (S08SPIV3)

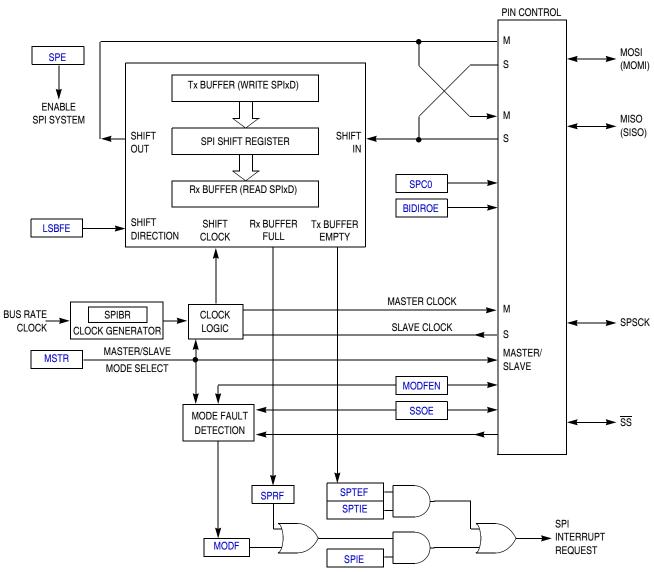

Figure 15-3. SPI Module Block Diagram

# 15.1.3 SPI Baud Rate Generation

As shown in Figure 15-4, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

#### Chapter 16 Timer/PWM Module (S08TPMV3)

When a channel is configured for edge-aligned PWM (CPWMS=0, MSnB=1 and ELSnB:ELSnA not = 0:0), the data direction is overridden, the TPMxCHn pin is forced to be an output controlled by the TPM, and ELSnA controls the polarity of the PWM output signal on the pin. When ELSnB:ELSnA=1:0, the TPMxCHn pin is forced high at the start of each new period (TPMxCNT=0x0000), and the pin is forced low when the channel value register matches the timer counter. When ELSnA=1, the TPMxCHn pin is forced high when the channel value register matches the timer counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

| TPMxCNTH:TPMxCNTL     |   | 0 | 1 | 2 | 3 | 4 |   | 5 | 6 | 7 | 8 | 0 | 1 | 2 |  |

|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| TPMxCHn —<br>CHnF BIT |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| TOF BIT               | 1 |   |   |   |   |   | 1 |   |   |   |   |   |   |   |  |

Figure 16-3. High-True Pulse of an Edge-Aligned PWM

| TPMxCNTH:TPMxCNTL | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 0 | 1 | 2 |  |

|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|

| TPMxCHn           | 1 |   |   |   |   |   |   |   |   |   |   |   |  |

|                   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| CHnF BIT          | 1 |   |   |   |   |   |   |   |   | ! |   |   |  |

|                   | 1 |   |   |   |   |   |   |   |   |   |   |   |  |

| TOF BIT           |   |   |   |   |   | 1 |   |   |   |   |   |   |  |

Figure 16-4. Low-True Pulse of an Edge-Aligned PWM

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

# Appendix A Electrical Characteristics

# A.1 Introduction

This section contains electrical and timing specifications for the MC9S08SH32 Series of microcontrollers available at the time of publication.

# A.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters are achieved through the design characterization by measuring a statistically relevant sample size across process variations.                                                                         |

| Т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table A-1. Parameter Classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# A.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-2 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused

Appendix A Electrical Characteristics

# A.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

| #  | С | Characteristic                                                 | Symbol                           | Condition                                                             | Min                    | Typ <sup>1</sup> | Max                  | Unit |

|----|---|----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|------------------------|------------------|----------------------|------|

| 1  |   | Operating Voltage                                              | V <sub>DD</sub>                  | _                                                                     | 2.7                    |                  | 5.5                  | V    |

|    | С | All I/O pins,                                                  |                                  | 5 V, $I_{Load} = -4 \text{ mA}$                                       | V <sub>DD</sub> – 1.5  | _                | —                    | V    |

|    | Ρ | low-drive strength                                             |                                  | 5 V, $I_{Load} = -2 \text{ mA}$                                       | V <sub>DD</sub> – 0.8  | _                | —                    | V    |

| 2  | С | Output high                                                    | V <sub>OH</sub>                  | 3 V, $I_{Load} = -1 \text{ mA}$                                       | V <sub>DD</sub> – 0.8  | _                | —                    | V    |

| 2  | С | voltage                                                        |                                  | 5 V, $I_{Load} = -20 \text{ mA}$                                      | V <sub>DD</sub> – 1.5  |                  | —                    | V    |

|    | Ρ | All I/O pins,                                                  |                                  | 5 V, $I_{Load} = -10 \text{ mA}$                                      | V <sub>DD</sub> – 0.8  |                  | —                    | V    |

|    | С | high-drive strength                                            |                                  | 3 V, I <sub>Load</sub> = -5 mA                                        | V <sub>DD</sub> – 0.8  |                  | —                    | V    |

| 3  | D | Output high Max total I <sub>OH</sub> for<br>current all ports | I <sub>OHT</sub>                 | $V_{OUT} < V_{DD}$                                                    | 0                      |                  | -100                 | mA   |

|    | С | All I/O pins                                                   |                                  | 5 V, I <sub>Load</sub> = 4 mA                                         | _                      | _                | 1.5                  | V    |

|    | Ρ | low-drive strength                                             |                                  | 5 V, I <sub>Load</sub> = 2 mA                                         | _                      | _                | 0.8                  | V    |

| 4  | С | Output low                                                     | V <sub>OL</sub>                  | 3 V, I <sub>Load</sub> = 1 mA                                         | _                      | _                | 0.8                  | V    |

| -  | С | voltage                                                        |                                  | 5 V, I <sub>Load</sub> = 20 mA                                        | —                      |                  | 1.5                  | V    |

|    | Ρ | All I/O pins                                                   |                                  | 5 V, I <sub>Load</sub> = 10 mA                                        | -                      |                  | 0.8                  | V    |

|    | С | high-drive strength                                            |                                  | 3 V, I <sub>Load</sub> = 5 mA                                         | —                      |                  | 0.8                  | V    |

| 5  | D | Output Max total I <sub>OL</sub> for<br>low current all ports  | I <sub>OLT</sub>                 | $V_{OUT} > V_{SS}$                                                    | 0                      | —                | 100                  | mA   |

| 6  | Ρ | Input high voltage; all digital inputs                         | V <sub>IH</sub>                  | 5V                                                                    | 0.65 x V <sub>DD</sub> |                  | —                    | V    |

| Ŭ  | С |                                                                |                                  | 3V                                                                    | 0.7 x V <sub>DD</sub>  |                  | —                    | V    |

| 7  | Р | Input low voltage; all digital inputs                          | V <sub>IL</sub>                  | 5V                                                                    | —                      | _                | $0.35 \times V_{DD}$ | V    |

|    | С |                                                                |                                  | 3V                                                                    |                        | _                | $0.35 \times V_{DD}$ | V    |

| 8  | С | Input hysteresis                                               | V <sub>hys</sub>                 | —                                                                     | 0.06 x V <sub>DD</sub> |                  | —                    | V    |

| 9  | Ρ | Input leakage current (per pin)                                | I <sub>In</sub>                  | $V_{In} = V_{DD} \text{ or } V_{SS}$                                  | —                      | _                | 1                    | μA   |

|    |   | Hi-Z (off-state) leakage current (per pin)                     |                                  |                                                                       |                        |                  |                      |      |

| 10 | Ρ | input/output port pins                                         | I <sub>OZ</sub>                  | V <sub>In</sub> = V <sub>DD</sub> or V <sub>SS</sub> ;<br>temperature | —                      | _                | 1                    | μA   |

|    |   | PTA5/IRQ/TCLK/RESET,<br>PTB6/SDA/XTAL pins                     |                                  | $V_{In} = V_{DD} \text{ or } V_{SS}$                                  | _                      | _                | 2                    | μΑ   |

| 11 | _ | Pullup or Pulldown <sup>2</sup> resistors; when enabled        |                                  |                                                                       |                        |                  |                      |      |

|    | P |                                                                | R <sub>PU</sub> ,R <sub>PD</sub> | —                                                                     | 17                     | 37               | 52                   | kΩ   |

|    | С | PTA5/IRQ/TCLK/RESET <sup>3</sup>                               | R <sub>PU</sub>                  | —                                                                     | 17                     | 37               | 52                   | kΩ   |

### Table A-6. DC Characteristics