#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 28-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh32cwlr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

### Title

### Page

|     | 4.5.3    | Program and Erase Command Execution          | 48 |

|-----|----------|----------------------------------------------|----|

|     | 4.5.4    | Burst Program Execution                      | 49 |

|     | 4.5.5    | Access Errors                                | 51 |

|     | 4.5.6    | FLASH Block Protection                       | 51 |

|     | 4.5.7    | Vector Redirection                           | 52 |

| 4.6 | Security | Ι                                            | 52 |

| 4.7 | FLASH    | Registers and Control Bits                   | 53 |

|     | 4.7.1    | FLASH Clock Divider Register (FCDIV)         | 54 |

|     | 4.7.2    | FLASH Options Register (FOPT and NVOPT)      | 55 |

|     | 4.7.3    | FLASH Configuration Register (FCNFG)         | 56 |

|     | 4.7.4    | FLASH Protection Register (FPROT and NVPROT) | 56 |

|     | 4.7.5    | FLASH Status Register (FSTAT)                | 57 |

|     | 4.7.6    | FLASH Command Register (FCMD)                | 58 |

|     |          |                                              |    |

### Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introduo | ction                                                          | 59 |

|-----|----------|----------------------------------------------------------------|----|

| 5.2 | Feature  | S                                                              | 59 |

| 5.3 | MCU R    | eset                                                           | 59 |

| 5.4 | Comput   | er Operating Properly (COP) Watchdog                           | 60 |

| 5.5 | Interrup | ts                                                             | 61 |

|     | 5.5.1    | Interrupt Stack Frame                                          | 62 |

|     | 5.5.2    | External Interrupt Request Pin (IRQ)                           | 63 |

|     | 5.5.3    | Interrupt Vectors, Sources, and Local Masks                    | 63 |

| 5.6 | Low-Vo   | bltage Detect (LVD) System                                     | 65 |

|     | 5.6.1    | 1                                                              |    |

|     | 5.6.2    | Low-Voltage Detection (LVD) Reset Operation                    | 65 |

|     | 5.6.3    | Low-Voltage Warning (LVW) Interrupt Operation                  | 65 |

| 5.7 | Reset, I | nterrupt, and System Control Registers and Control Bits        |    |

|     | 5.7.1    | Interrupt Pin Request Status and Control Register (IRQSC)      |    |

|     | 5.7.2    | System Reset Status Register (SRS)                             |    |

|     | 5.7.3    | System Background Debug Force Reset Register (SBDFR)           | 68 |

|     | 5.7.4    | System Options Register 1 (SOPT1)                              | 69 |

|     | 5.7.5    | System Options Register 2 (SOPT2)                              | 70 |

|     | 5.7.6    | System Device Identification Register (SDIDH, SDIDL)           |    |

|     | 5.7.7    | System Power Management Status and Control 1 Register (SPMSC1) | 72 |

|     | 5.7.8    | System Power Management Status and Control 2 Register (SPMSC2) | 73 |

|     |          |                                                                |    |

### Chapter 6 Parallel Input/Output Control

| 6.1 | Port Data and Data Direction           | 75 |

|-----|----------------------------------------|----|

| 6.2 | Pull-up, Slew Rate, and Drive Strength | 76 |

MC9S08SH32 Series Data Sheet, Rev. 3

# Chapter 4 Memory

# 4.1 MC9S08SH32 Series Memory Map

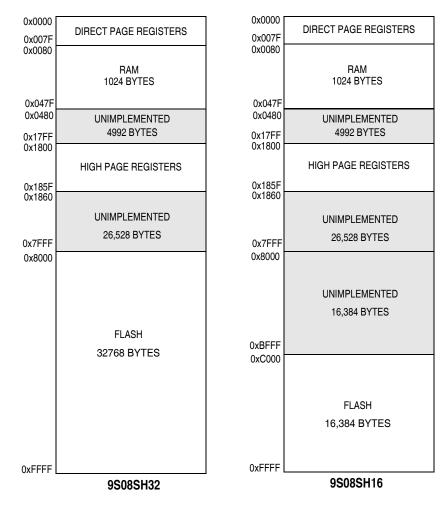

As shown in Figure 4-1, on-chip memory in the MC9S08SH32 Series series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x185F)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

MC9S08SH32 Series Data Sheet, Rev. 3

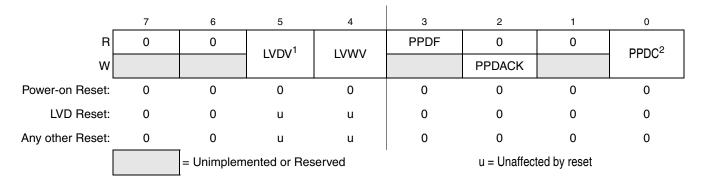

# 5.7.8 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU. This register should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-10. System Power Management Status and Control 2 Register (SPMSC2)

| Field       | Description                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-12.                                        |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-12.                                                                                            |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |

#### Table 5-11. SPMSC2 Register Field Descriptions

Chapter 6 Parallel Input/Output Control

# 6.6 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

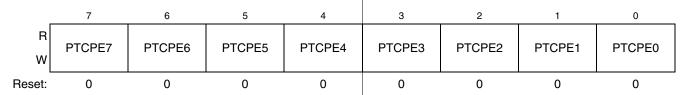

### 6.6.3.3 Port C Pull Enable Register (PTCPE)

Figure 6-21. Internal Pull Enable for Port C Register (PTCPE)

#### Table 6-20. PTCPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCPE[7:0] | <ul> <li>Internal Pull Enable for Port C Bits — Each of these control bits determines if the internal pull-up device is enabled for the associated PTC pin. For port C pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up device disabled for port C bit n.</li> <li>1 Internal pull-up device enabled for port C bit n.</li> </ul> |

### 6.6.3.4 Port C Slew Rate Enable Register (PTCSE)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTCSE7 | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-22. Slew Rate Enable for Port C Register (PTCSE)

#### Table 6-21. PTCSE Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTCSE[7:0] | <ul> <li>Output Slew Rate Enable for Port C Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port C bit n.</li> <li>Output slew rate control enabled for port C bit n.</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV3)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08SH32 Series Data Sheet, Rev. 3

Chapter 7 Central Processor Unit (S08CPUV3)

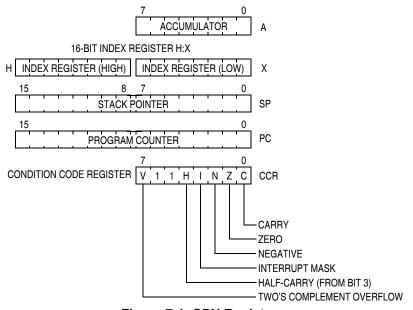

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

### 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where the specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

### 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

## 8.5 External Signal Description

The ACMP has two analog input pins, ACMP+ and ACMP- and one digital output pin ACMPO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 8-2, the ACMP- pin is connected to the inverting input of the comparator, and the ACMP+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 8-2, the ACMPO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 8-1.

| Signal | Function                                                    | I/O |

|--------|-------------------------------------------------------------|-----|

| ACMP-  | Inverting analog input to the ACMP.<br>(Minus input)        | I   |

| ACMP+  | Non-inverting analog input to the ACMP.<br>(Positive input) | I   |

| ACMPO  | Digital output of the ACMP.                                 | 0   |

**Table 8-1. Signal Properties**

### 8.6 Memory Map

### 8.6.1 Register Descriptions

The ACMP includes one register:

• An 8-bit status and control register

Refer to the direct-page register summary in the memory section of this data sheet for the absolute address assignments for all ACMP registers. This section refers to registers and control bits only by their names.

Some MCUs may have more than one ACMP, so register names include placeholder characters to identify which ACMP is being referenced.

# 8.7 Functional Description

The analog comparator can be used to compare two analog input voltages applied to ACMP+ and ACMP-; or it can be used to compare an analog input voltage applied to ACMP- with an internal bandgap reference voltage. ACBGS is used to select between the bandgap reference voltage or the ACMP+ pin as the input to the non-inverting input of the analog comparator. The comparator output is high when the non-inverting input is greater than the inverting input, and is low when the non-inverting input is less than the inverting input. ACMOD is used to select the condition which will cause ACF to be set. ACF can be set on a rising edge of the comparator output, a falling edge of the comparator output, or either a rising or a falling edge (toggle). The comparator output can be read directly through ACO. The comparator output can be driven onto the ACMPO pin using ACOPE.

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

| ADCH  | Input Select |

|-------|--------------|

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

#### Figure 9-4. Input Channel Select (continued)

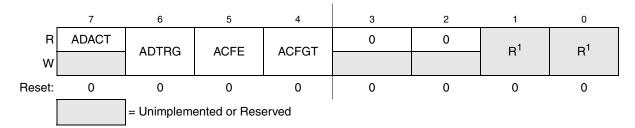

### 9.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

#### Figure 9-5. Status and Control Register 2 (ADCSC2)

#### Table 9-4. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | <ul> <li>Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>0 Conversion not in progress</li> <li>1 Conversion in progress</li> </ul>                                                                                                                                                                                                                              |

| 6<br>ADTRG | <ul> <li>Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion.</li> <li>Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.</li> <li>Software trigger selected</li> <li>Hardware trigger selected</li> </ul> |

### 13.1.1 Features

Features of the RTC module include:

- 8-bit up-counter

- 8-bit modulo match limit

- Software controllable periodic interrupt on match

- Three software selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1-kHz internal low-power oscillator (LPO)

- External clock (ERCLK)

- 32-kHz internal clock (IRCLK)

### 13.1.2 Modes of Operation

This section defines the operation in stop, wait and background debug modes.

#### 13.1.2.1 Wait Mode

The RTC continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the RTC can bring the MCU out of wait mode if the real-time interrupt is enabled. For lowest possible current consumption, the RTC should be stopped by software if not needed as an interrupt source during wait mode.

#### 13.1.2.2 Stop Modes

The RTC continues to run in stop2 or stop3 mode if the RTC is enabled before executing the STOP instruction. Therefore, the RTC can bring the MCU out of stop modes with no external components, if the real-time interrupt is enabled.

The LPO clock can be used in stop2 and stop3 modes. ERCLK and IRCLK clocks are only available in stop3 mode.

Power consumption is lower when all clock sources are disabled, but in that case, the real-time interrupt cannot wake up the MCU from stop modes.

### 13.1.2.3 Active Background Mode

The RTC suspends all counting during active background mode until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as the RTCMOD register is not written and the RTCPS and RTCLKS bits are not altered.

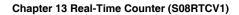

# 13.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 13-4. RTC Counter Register (RTCCNT)

#### Table 13-4. RTCCNT Field Descriptions

| Field         | Id Description                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |  |  |  |  |  |

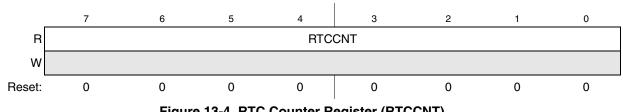

# 13.3.3 RTC Modulo Register (RTCMOD)

| Field         | Description                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |  |  |  |  |

# 13.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

Chapter 14 Serial Communications Interface (S08SCIV4)

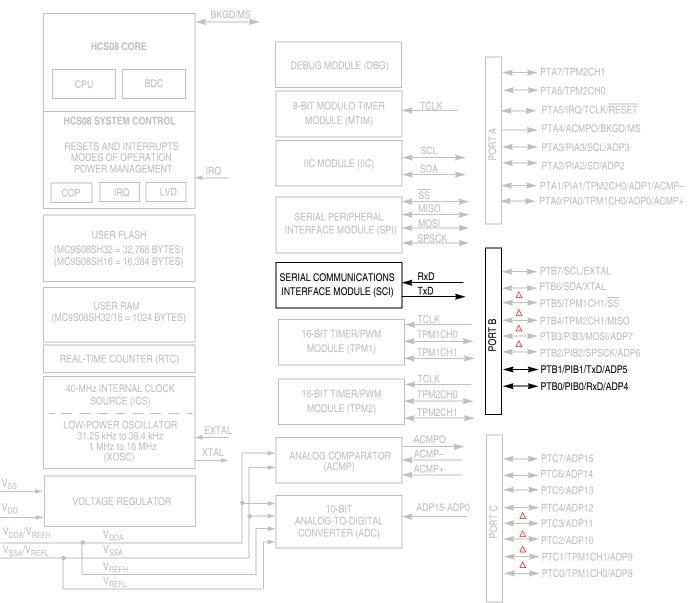

#### $\triangle$ = Pin can be enabled as part of the ganged output drive feature

NOTE: - PTC7-PTC0 and PTA7-PTA6 not available on 16--pin Packages

- PTC7-PTC4 and PTA7-PTA6 not available on 20-pin Packages

- For the 16-pin and 20-pin packages:  $V_{DDA}/V_{REFH}$  and  $V_{SSA}/V_{REFL}$ , are double bonded to  $V_{DD}$  and  $V_{SS}$  respectively.

- When PTA4 is configured as BKGD, pin becomes bi-directional.

Figure 14-1. MC9S08SH32 Series Block Diagram Highlighting SCI Block and Pins

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3<br>TE  | Transmitter Enable         0       Transmitter off.         1       Transmitter on.         TE must be 1 in order to use the SCI transmitter. When TE = 1, the SCI forces the TxD pin to act as an output for the SCI system.         When the SCI is configured for single-wire operation (LOOPS = RSRC = 1), TXDIR controls the direction of traffic on the single SCI communication line (TxD pin).         TE also can be used to queue an idle character by writing TE = 0 then TE = 1 while a transmission is in progress.         Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.         When TE is written to 0, the transmitter keeps control of the port TxD pin until any data, queued idle, or queued break character finishes transmitting before allowing the pin to revert to a general-purpose I/O pin. |  |  |  |  |  |  |

| 2<br>RE  | <ul> <li>Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin. If LOOPS = 1 the RxD pin reverts to being a general-purpose I/O pin even if RE = 1.</li> <li>0 Receiver off.</li> <li>1 Receiver on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 1<br>RWU | Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more details.         0       Normal SCI receiver operation.         1       SCI receiver in standby waiting for wakeup condition.                                                                                                                                                                    |  |  |  |  |  |  |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 (13 or 14 if BRK13 = 1) bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

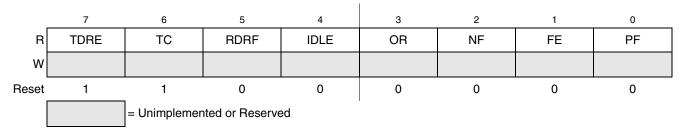

### 14.2.4 SCI Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

Figure 14-8. SCI Status Register 1 (SCIxS1)

#### Chapter 16 Timer/PWM Module (S08TPMV3)

• Edge-aligned PWM mode

The value of a 16-bit modulo register plus 1 sets the period of the PWM output signal. The channel value register sets the duty cycle of the PWM output signal. The user may also choose the polarity of the PWM output signal. Interrupts are available at the end of the period and at the duty-cycle transition point. This type of PWM signal is called edge-aligned because the leading edges of all PWM signals are aligned with the beginning of the period, which is the same for all channels within a TPM.

• Center-aligned PWM mode

Twice the value of a 16-bit modulo register sets the period of the PWM output, and the channel-value register sets the half-duty-cycle duration. The timer counter counts up until it reaches the modulo value and then counts down until it reaches zero. As the count matches the channel value register while counting down, the PWM output becomes active. When the count matches the channel value register while counting up, the PWM output becomes inactive. This type of PWM signal is called center-aligned because the centers of the active duty cycle periods for all channels are aligned with a count value of zero. This type of PWM is required for types of motors used in small appliances.

This is a high-level description only. Detailed descriptions of operating modes are in later sections.

### 16.1.5 Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPMxCHn (timer channel n) where n is the channel number (1-8). The TPM shares its I/O pins with general purpose I/O port pins (refer to I/O pin descriptions in full-chip specification for the specific chip implementation).

Figure 16-2 shows the TPM structure. The central component of the TPM is the 16-bit counter that can operate as a free-running counter or a modulo up/down counter. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter (the values 0x0000 or 0xFFFF effectively make the counter free running). Software can read the counter value at any time without affecting the counting sequence. Any write to either half of the TPMxCNT counter resets the counter, regardless of the data value written.

#### **Chapter 17 Development Support**

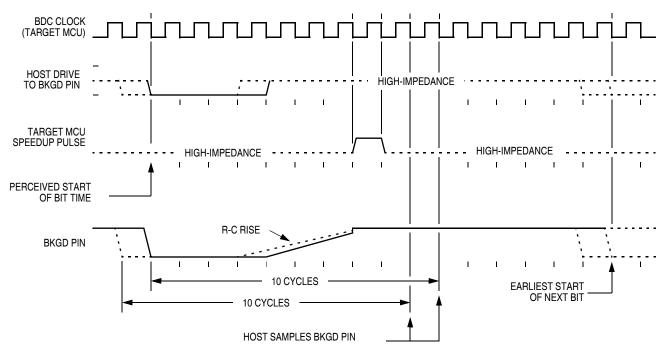

Figure 17-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host should sample the bit level about 10 cycles after it started the bit time.

Figure 17-3. BDC Target-to-Host Serial Bit Timing (Logic 1)

Chapter 17 Development Support

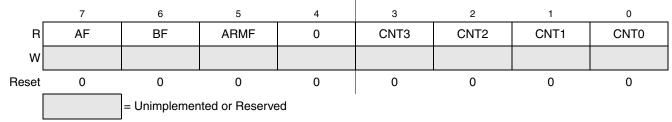

#### 17.4.3.9 **Debug Status Register (DBGS)**

This is a read-only status register.

#### Figure 17-9. Debug Status Register (DBGS)

| Table 17-6. DBGS Register Field Descriptions |

|----------------------------------------------|

|----------------------------------------------|

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>AF         | <ul> <li>Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.</li> <li>0 Comparator A has not matched</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 6<br>BF         | <ul> <li>Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.</li> <li>0 Comparator B has not matched</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 5<br>ARMF       | <ul> <li>Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writin to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). I debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |  |  |  |  |  |  |  |

| # | Characteristic                                          | Conditions                    | С   | Symb                                   | Min  | Typ <sup>1</sup> | Max  | Unit             | Comment                                                |  |

|---|---------------------------------------------------------|-------------------------------|-----|----------------------------------------|------|------------------|------|------------------|--------------------------------------------------------|--|

| 1 | Supply current                                          | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 133              | _    | μA               | ADC current<br>only                                    |  |

|   |                                                         | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 218              | _    | μA               | ADC current<br>only                                    |  |

|   |                                                         | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | т   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _    | μA               | ADC current<br>only                                    |  |

|   |                                                         | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Ρ   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.58<br>2        | 1    | mA               | ADC current<br>only                                    |  |

|   | ADC                                                     | High speed (ADLPC=0)          | Р   | f <sub>adack</sub>                     | 2    | 3.3              | 5    | MHz              | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub>           |  |

| 2 | asynchronous<br>clock source                            | Low power (ADLPC=1)           | 1   |                                        | 1.25 | 2                | 3.3  |                  |                                                        |  |

| 3 | Conversion<br>time (including                           | Short sample<br>(ADLSMP=0)    | D   | t <sub>ADC</sub>                       |      | 20               | _    | ADCK<br>cycles   | See ADC<br>Chapter for<br>conversion<br>time variances |  |

|   | sample time)                                            | Long sample<br>(ADLSMP=1)     |     |                                        | _    | 40               | _    |                  |                                                        |  |

| 4 | Sample time                                             | Short sample<br>(ADLSMP=0)    | D   | t <sub>ADS</sub>                       | _    | 3.5              | _    | ADCK<br>cycles   |                                                        |  |

|   |                                                         | Long sample<br>(ADLSMP=1)     |     |                                        |      | 23.5             | —    |                  |                                                        |  |

|   |                                                         | 28-pin packages only          |     |                                        |      |                  |      |                  |                                                        |  |

|   | Total<br>unadjusted<br>error (includes<br>quantization) | 10-bit mode                   |     | E <sub>TUE</sub>                       | _    | ±1               | ±2.5 | LSB <sup>2</sup> |                                                        |  |

|   |                                                         | 8-bit mode                    | Ρ   |                                        | _    | ±0.5             | ±1   |                  |                                                        |  |

|   |                                                         | 20-pin packages               |     |                                        |      |                  |      |                  |                                                        |  |

| 5 |                                                         | 10-bit mode                   | Р   | E_                                     |      | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |  |

|   |                                                         | 8-bit mode                    | r-  | E <sub>TUE</sub>                       |      | ±0.7             | ±1.5 | LOD              |                                                        |  |

|   |                                                         | 16-pin packages               |     |                                        |      |                  |      |                  |                                                        |  |

|   |                                                         | 10-bit mode                   | – P | E <sub>TUE</sub>                       | _    | ±.5              | ±3.5 | LSB <sup>2</sup> |                                                        |  |

|   |                                                         | 8-bit mode                    |     |                                        |      | ±0.7             | ±1.5 | 200              |                                                        |  |

### A.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

### A.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter           | Symbol              | Conditions                                                         | Frequency              | f <sub>OSC</sub> /f <sub>BUS</sub> | Level <sup>1</sup><br>(Max) | Unit |

|---------------------|---------------------|--------------------------------------------------------------------|------------------------|------------------------------------|-----------------------------|------|

|                     | V <sub>RE_TEM</sub> | $V_{DD} = 5 V$<br>$T_A = +25^{\circ}C$<br>package type<br>28 TSSOP | 0.15 – 50 MHz          |                                    | 12                          | dBμV |

|                     |                     |                                                                    | 50 – 150 MHz           | 4 MHz crystal<br>20 MHz bus        | 12                          |      |

| Radiated emissions, |                     |                                                                    | 150 – 500 MHz          |                                    | 6                           |      |

| electric field      |                     |                                                                    | 500 – 1000 MHz         |                                    | -8                          |      |

|                     |                     |                                                                    | IEC Level <sup>2</sup> |                                    | Ν                           | _    |

|                     |                     |                                                                    | SAE Level <sup>3</sup> | 1                                  | 2                           | _    |

Table A-17. Radiated Emissions, Electric Field

<sup>1</sup> Data based on qualification test results.

$^2~$  IEC Level Maximums: N  $\leq$  12dBµV, L  $\leq$  24dBµV, I  $\leq$  36dBµV

$^3$  SAE Level Maximums: 1  $\leq$  10dBµV, 2  $\leq$  20dBµV, 3  $\leq$  30dBµV, 4  $\leq$  40dBµV