Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 30MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 5x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 20-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc824m201jdh20j |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8. Functional description

## 8.1 ARM Cortex-M0+ core

The ARM Cortex-M0+ core runs at an operating frequency of up to 30 MHz using a two-stage pipeline. The core revision is r0p1.

Integrated in the core are the NVIC and Serial Wire Debug with four breakpoints and two watchpoints. The ARM Cortex-M0+ core supports a single-cycle I/O enabled port for fast GPIO access.

The core includes a single-cycle multiplier and a system tick timer.

## 8.2 On-chip flash program memory

The LPC82x contain up to 32 KB of on-chip flash program memory. The flash memory supports a 64 Byte page size with page write and erase.

## 8.3 On-chip SRAM

The LPC82x contain a total of 8 KB on-chip static RAM data memory in two separate SRAM blocks with one combined clock for both SRAM blocks.

## 8.4 On-chip ROM

The on-chip ROM contains the bootloader and the following Application Programming Interfaces (APIs):

- In-System Programming (ISP) and In-Application Programming (IAP) support for flash including IAP erase page command.

- Power profiles for configuring power consumption and PLL settings

- 32-bit integer division routines

- APIs to use the following peripherals:

- SPI

- USART

- I2C

- ADC

## 8.5 Memory map

The LPC82x incorporates several distinct memory regions. <u>Figure 6</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The ARM private peripheral bus includes the ARM core registers for controlling the NVIC, the system tick timer (SysTick), and the reduced power modes.

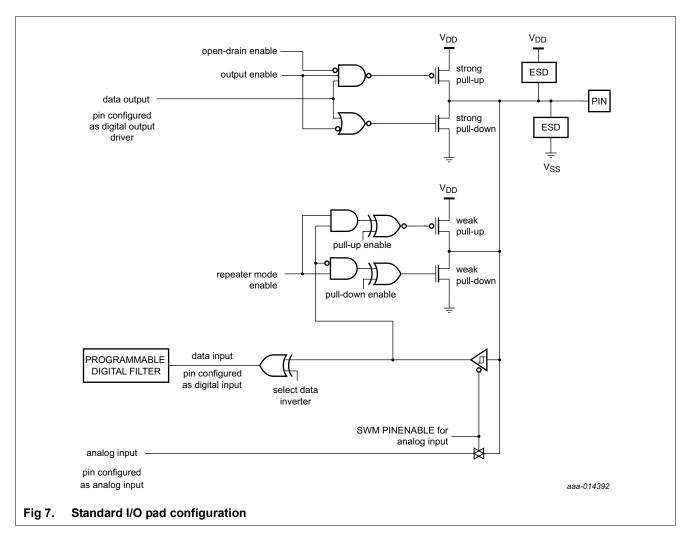

- Digital input: Repeater mode enabled/disabled.

- Digital input: Programmable input digital filter selectable on all pins.

- Analog input: Selected through the switch matrix.

# 8.9 Switch Matrix (SWM)

The switch matrix controls the function of each digital or mixed analog/digital pin in a highly flexible way by allowing to connect many functions like the USART, SPI, SCT, and I2C functions to any pin that is not power or ground. These functions are called movable functions and are listed in <u>Table 4</u>.

Functions that need specialized pads like the oscillator pins XTALIN and XTALOUT can be enabled or disabled through the switch matrix. These functions are called fixed-pin functions and cannot move to other pins. The fixed-pin functions are listed in <u>Table 3</u>. If a fixed-pin function is disabled, any other movable function can be assigned to this pin.

# 8.10 Fast General-Purpose parallel I/O (GPIO)

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Multiple outputs can be set or cleared in one write operation.

LPC82x use accelerated GPIO functions:

- GPIO registers are on the ARM Cortex-M0+ IO bus for fastest possible single-cycle I/O timing, allowing GPIO toggling with rates of up to 15 MHz.

- An entire port value can be written in one instruction.

- Mask, set, and clear operations are supported for the entire port.

All GPIO port pins are fixed-pin functions that are enabled or disabled on the pins by the switch matrix. Therefore each GPIO port pin is assigned to one specific pin and cannot be moved to another pin. Except for pins SWDIO/PIO0\_2, SWCLK/PIO0\_3, and RESET/PIO0\_5, the switch matrix enables the GPIO port pin function by default.

## 8.10.1 Features

- Bit level port registers allow a single instruction to set and clear any number of bits in one write operation.

- Direction control of individual bits.

- All I/O default to GPIO inputs with internal pull-up resistors enabled after reset except for the I<sup>2</sup>C-bus true open-drain pins PIO0\_10 and PIO0\_11.

- Pull-up/pull-down configuration, repeater, and open-drain modes can be programmed through the IOCON block for each GPIO pin (see Figure 7).

- Direction (input/output) can be set and cleared individually.

- Pin direction bits can be toggled.

## 8.11 Pin interrupt/pattern match engine

The pin interrupt block configures up to eight pins from all digital pins for providing eight external interrupts connected to the NVIC.

The pattern match engine can be used, with software, to create complex state machines based on pin inputs.

Any digital pin, independently of the function selected through the switch matrix, can be configured through the SYSCON block as input to the pin interrupt or pattern match engine. The registers that control the pin interrupt or pattern match engine are on the IO+ bus for fast single-cycle access.

## 8.11.1 Features

- Pin interrupts

- Up to eight pins can be selected from all digital pins as edge- or level-sensitive interrupt requests. Each request creates a separate interrupt in the NVIC.

- Edge-sensitive interrupt pins can interrupt on rising or falling edges or both.

- Level-sensitive interrupt pins can be HIGH- or LOW-active.

- Four inputs. Each input is configurable through an input multiplexer to use one of four external pins (connected through the switch matrix) or one of four internal sources. The maximum input signal frequency is 25 MHz.

- Six outputs. Connected to pins through the switch matrix.

- Counter/timer features:

- Each SCTimer is configurable as two 16-bit counters or one 32-bit counter.

- Counters can be clocked by the system clock or selected input.

- Configurable as up counters or up-down counters.

- Configurable number of match and capture registers. Up to eight match and capture registers total.

- Upon match create the following events: interrupt; stop, limit, halt the timer or change counting direction; toggle outputs.

- Counter value can be loaded into capture register triggered by a match or input/output toggle.

- PWM features:

- Counters can be used with match registers to toggle outputs and create time-proportioned PWM signals.

- Up to six single-edge or dual-edge PWM outputs with independent duty cycle and common PWM cycle length.

- Event creation features:

- The following conditions define an event: a counter match condition, an input (or output) condition such as a rising or falling edge or level, a combination of match and/or input/output condition.

- Selected events can limit, halt, start, or stop a counter or change its direction.

- Events trigger state changes, output toggles, interrupts, and DMA transactions.

- Match register 0 can be used as an automatic limit.

- In bidirectional mode, events can be enabled based on the count direction.

- Match events can be held until another qualifying event occurs.

- State control features:

- A state is defined by events that can happen in the state while the counter is running.

- A state changes into another state as a result of an event.

- Each event can be assigned to one or more states.

- State variable allows sequencing across multiple counter cycles.

- One SCTimer match output can be selected as ADC hardware trigger input.

## 8.16.2 SCTimer/PWM input MUX (INPUT MUX)

Each input of the SCTimer/PWM is connected to a programmable multiplexer which allows to connect one of multiple internal or external sources to the input. The available sources are the same for each SCTimer/PWM input and can be selected from four pins configured through the switch matrix, the ADC threshold compare interrupt, the comparator output, and the ARM core signals ARM\_TXEV and DEBUG\_HALTED.

# 8.17 Multi-Rate Timer (MRT)

The Multi-Rate Timer (MRT) provides a repetitive interrupt timer with four channels. Each channel can be programmed with an independent time interval, and each channel operates independently from the other channels.

## 8.17.1 Features

- 31-bit interrupt timer

- · Four channels independently counting down from individually set values

- Bus stall, repeat and one-shot interrupt modes

# 8.18 Windowed WatchDog Timer (WWDT)

The watchdog timer resets the controller if software fails to service the watchdog timer periodically within a programmable time window.

## 8.18.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The WatchDog Clock (WDCLK) is generated by the dedicated watchdog oscillator (WDOSC).

# 8.19 Self-Wake-up Timer (WKT)

The self-wake-up timer is a 32-bit, loadable down counter. Writing any non-zero value to this timer automatically enables the counter and launches a count-down sequence. When the counter is used as a wake-up timer, this write can occur prior to entering a reduced power mode.

## 8.19.1 Features

- 32-bit loadable down counter. Counter starts automatically when a count value is loaded. Time-out generates an interrupt/wake up request.

- The WKT resides in a separate, always-on power domain.

- The WKT supports three clock sources: an external clock on the WKTCLKIN pin, the low-power oscillator, and the IRC. The low-power oscillator is located in the always-on power domain, so it can be used as the clock source in Deep power-down mode.

- Voltage ladder source voltage is selectable from an external pin or the main 3.3 V supply voltage rail.

- Voltage ladder can be separately powered down for applications only requiring the comparator function.

- Interrupt output is connected to NVIC.

- Comparator level output is connected to output pin ACMP\_O.

- One comparator output is internally collected to the ADC trigger input multiplexer.

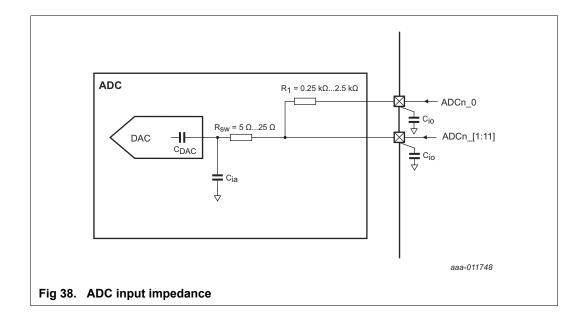

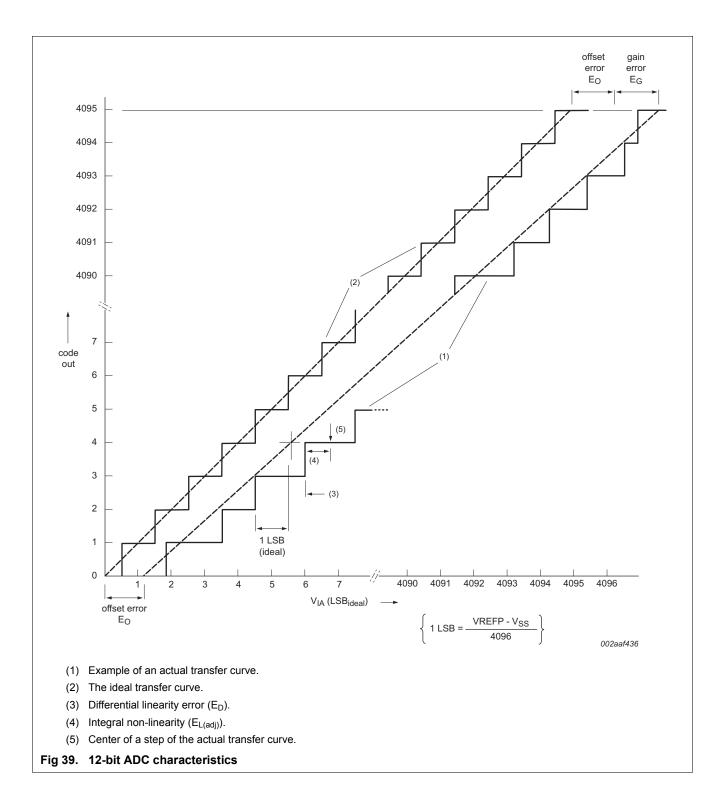

# 8.21 Analog-to-Digital Converter (ADC)

The ADC supports a resolution of 12 bit and fast conversion rates of up to 1.2 MSamples/s. Sequences of analog-to-digital conversions can be triggered by multiple sources. Possible trigger sources are the pin triggers, the SCT output SCT\_OUT3, the analog comparator output, and the ARM TXEV.

The ADC includes a hardware threshold compare function with zero-crossing detection.

**Remark:** For best performance, select VREFP and VREFN at the same voltage levels as  $V_{DD}$  and  $V_{SS}$ . When selecting VREFP and VREFN different from VDD and VSS, ensure that the voltage midpoints are the same:

$(VREFP-VREFN)/2 + VREFN = V_{DD}/2$

## 8.21.1 Features

- 12-bit successive approximation analog to digital converter.

- 12-bit conversion rate of up to 1.2 MSamples/s.

- Two configurable conversion sequences with independent triggers.

- Optional automatic high/low threshold comparison and zero-crossing detection.

- Power-down mode and low-power operating mode.

- Measurement range VREFN to VREFP (not to exceed V<sub>DD</sub> voltage level).

- Burst conversion mode for single or multiple inputs.

- Hardware calibration mode.

PC82x

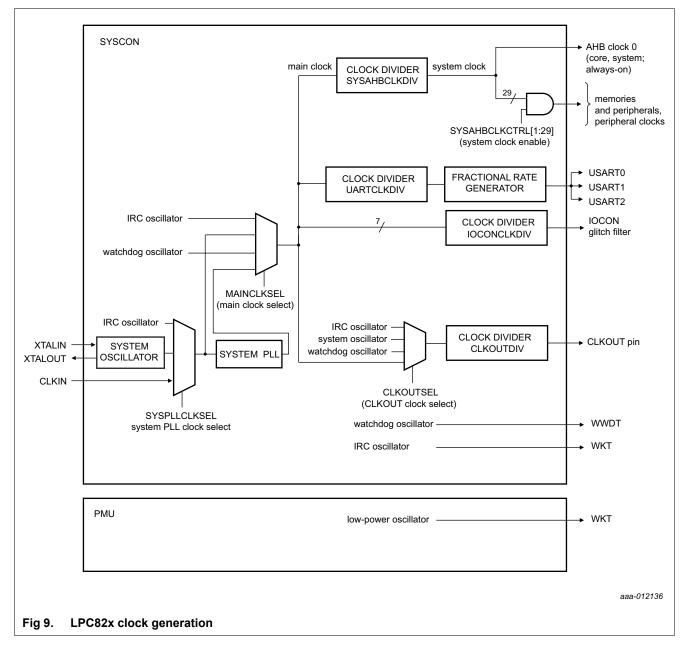

8.22 Clocking and power control

## 8.22.1 Crystal and internal oscillators

The LPC82x include four independent oscillators:

- 1. The crystal oscillator (SysOsc) operating at frequencies between 1 MHz and 25 MHz.

- 2. The internal RC Oscillator (IRC) with a fixed frequency of 12 MHz.

- 3. The internal low-power, low-frequency Oscillator with a nominal frequency of 10 kHz with 40% accuracy for use with the self-wake-up timer.

- 4. The dedicated Watchdog Oscillator (WDOsc) with a programmable nominal frequency between 9.4 kHz and 2.3 MHz with 40% accuracy.

LPC82x

When entering Deep power-down mode, an external pull-up resistor is required on the WAKEUP pin to hold it HIGH. Pull the RESET pin HIGH to prevent it from floating while in Deep power-down mode.

## 8.23 System control

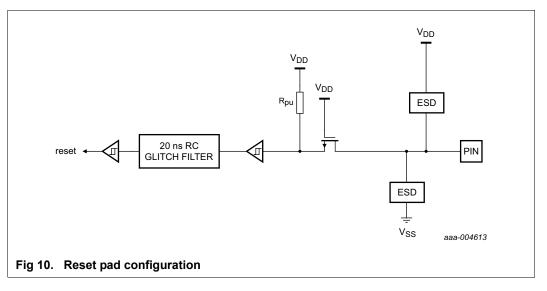

## 8.23.1 Reset

Reset has four sources on the LPC82x: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip reset by any source, once the operating voltage attains a usable level, starts the IRC and initializes the flash controller.

A LOW-going pulse as short as 50 ns resets the part.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the boot block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

## 8.23.2 Brownout detection

The LPC82x includes up to four levels for monitoring the voltage on the V<sub>DD</sub> pin. If this voltage falls below one of the selected levels, the BOD asserts an interrupt signal to the NVIC. This signal can be enabled for interrupt in the Interrupt Enable Register in the NVIC to cause a CPU interrupt. Alternatively, software can monitor the signal by reading a dedicated status register. Four threshold levels can be selected to cause a forced reset of the chip.

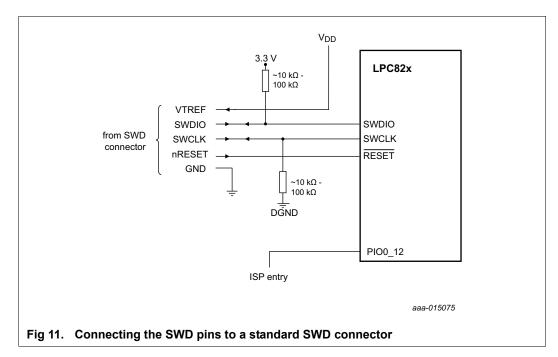

# 8.24 Emulation and debugging

Debug functions are integrated into the ARM Cortex-M0+. Serial wire debug functions are supported in addition to a standard JTAG boundary scan. The ARM Cortex-M0+ is configured to support up to four breakpoints and two watch points.

The Micro Trace Buffer is implemented on the LPC82x.

The RESET pin selects between the JTAG boundary scan (RESET = LOW) and the ARM SWD debug (RESET = HIGH). The ARM SWD debug port is disabled while the LPC82x is in reset. The JTAG boundary scan pins are selected by hardware when the part is in boundary scan mode on pins PIO0\_0 to PIO0\_3 (see <u>Table 3</u>).

To perform boundary scan testing, follow these steps:

- 1. Erase any user code residing in flash.

- 2. Power up the part with the  $\overline{\text{RESET}}$  pin pulled HIGH externally.

- 3. Wait for at least 250  $\mu$ s.

- 4. Pull the RESET pin LOW externally.

- 5. Perform boundary scan operations.

- 6. Once the boundary scan operations are completed, assert the TRST pin to enable the SWD debug mode, and release the RESET pin (pull HIGH).

**Remark:** The JTAG interface cannot be used for debug purposes.

LPC82x

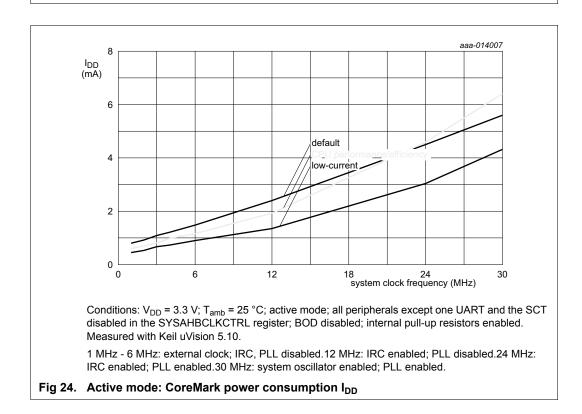

#### aaa-014006 2.5 coremark score ((iterations/s)/MHz) 2 default 1.5 low-current 1 0.5 0 0 6 12 24 30 18 system clock frequency (MHz) Conditions: V<sub>DD</sub> = 3.3 V; T<sub>amb</sub> = 25 °C; active mode; all peripherals except one UART and the SCT disabled in the SYSAHBCLKCTRL register; BOD disabled; internal pull-up resistors enabled. Measured with Keil uVision 5.10. 1 MHz - 6 MHz: external clock; IRC, PLL disabled.12 MHz: IRC enabled; PLL disabled. 24 MHz: IRC enabled; PLL enabled.30 MHz: system oscillator enabled; PLL enabled.

# 11.5 CoreMark data

Fig 23. CoreMark score

# **12.** Dynamic characteristics

# 12.1 Power-up ramp conditions

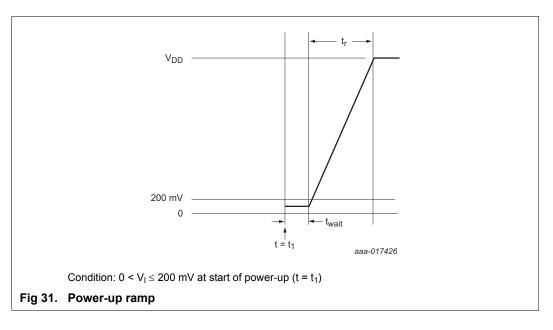

### Table 11. Power-up characteristics

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C; \ 1.8 \ V \le V_{DD} \le 3.6 \ V$

| Symbol            | Parameter     | Conditions                                      |           | Min | Тур | Max | Unit |

|-------------------|---------------|-------------------------------------------------|-----------|-----|-----|-----|------|

| tr                | rise time     | at t = $t_1$ : 0 < V <sub>I</sub> $\leq$ 200 mV | [1][3]    | 0   | -   | 500 | ms   |

| t <sub>wait</sub> | wait time     |                                                 | [1][2][3] | 12  | -   | -   | μS   |

| VI                | input voltage | at t = $t_1$ on pin $V_{DD}$                    | [3]       | 0   | -   | 200 | mV   |

[1] See Figure 31.

[2] The wait time specifies the time the power supply must be at levels below 200 mV before ramping up. See the LPC82x errata sheet.

[3] Based on characterization, not tested in production.

## 12.2 Flash/EEPROM memory

#### Table 12. Flash characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +105  $\text{}^{\circ}\text{C}$ . Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter | Conditions |     | Min   | Тур    | Max | Unit   |

|-------------------|-----------|------------|-----|-------|--------|-----|--------|

| N <sub>endu</sub> | endurance |            | [1] | 10000 | 100000 | -   | cycles |

| Symbol              | Parameter      |           | Conditions                                        | Min  | Max | Unit |

|---------------------|----------------|-----------|---------------------------------------------------|------|-----|------|

| t <sub>LOW</sub>    | LOW period of  |           | Standard-mode                                     | 4.7  | -   | μS   |

|                     | the SCL clock  |           | Fast-mode                                         | 1.3  | -   | μs   |

|                     |                |           | Fast-mode Plus; on<br>pins PIO0_10 and<br>PIO0_11 | 0.5  | -   | μs   |

| t <sub>HIGH</sub>   | HIGH period of |           | Standard-mode                                     | 4.0  | -   | μS   |

|                     | the SCL clock  |           | Fast-mode                                         | 0.6  | -   | μs   |

|                     |                |           | Fast-mode Plus; on<br>pins PIO0_10 and<br>PIO0_11 | 0.26 | -   | μs   |

| t <sub>HD;DAT</sub> | data hold time | [3][4][8] | Standard-mode                                     | 0    | -   | μS   |

|                     |                |           | Fast-mode                                         | 0    | -   | μS   |

|                     |                |           | Fast-mode Plus; on<br>pins PIO0_10 and<br>PIO0_11 | 0    | -   | μs   |

| t <sub>SU;DAT</sub> | data set-up    | [9][10]   | Standard-mode                                     | 250  | -   | ns   |

|                     | time           |           | Fast-mode                                         | 100  | -   | ns   |

|                     |                |           | Fast-mode Plus; on<br>pins PIO0_10 and<br>PIO0_11 | 50   | -   | ns   |

#### Table 19. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

$T_{amb} = -40 \ ^{\circ}C$  to +105  $^{\circ}C$ ; values guaranteed by design.<sup>[2]</sup>

[1] See the I<sup>2</sup>C-bus specification *UM10204* for details.

- [2] Parameters are valid over operating temperature range unless otherwise specified.

- [3] t<sub>HD:DAT</sub> is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [4] A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- [5] C<sub>b</sub> = total capacitance of one bus line in pF.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum  $t_{HD;DAT}$  could be 3.45  $\mu$ s and 0.9  $\mu$ s for Standard-mode and Fast-mode but must be less than the maximum of  $t_{VD;DAT}$  or  $t_{VD;ACK}$  by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] t<sub>SU;DAT</sub> is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode l<sup>2</sup>C-bus device can be used in a Standard-mode l<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT}$  = 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode l<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

| Table 25. | Comparator | characteristics | continued |

|-----------|------------|-----------------|-----------|

|-----------|------------|-----------------|-----------|

$T_{amb} = -40$  °C to +105 °C unless noted otherwise;  $V_{DD} = 1.8$  V to 3.6 V.

| Symbol           | Parameter          | Parameter Conditions                                                                         |                  | Min | Тур | Max | Unit |

|------------------|--------------------|----------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| t <sub>PD</sub>  | propagation delay  | HIGH to LOW; $V_{DD}$ = 3.0 V; $T_{amb}$ = 105 °C                                            |                  |     |     |     |      |

|                  |                    | V <sub>IC</sub> = 0.1 V; 100 mV overdrive input                                              | <u>[1][2][4]</u> | -   | 140 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 0.1 V; rail-to-rail input                                                  | [1][2]           | -   | 190 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 1.5 V; 100 mV overdrive input                                              | [1][2][4]        | -   | 130 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 1.5 V; rail-to-rail input                                                  | [1][2]           | -   | 120 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 2.9 V; 100 mV overdrive input                                              | [1][2][4]        | -   | 220 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 2.9 V; rail-to-rail input                                                  | [1][2]           | -   | 80  | -   | ns   |

| t <sub>PD</sub>  | propagation delay  | LOW to HIGH; $V_{DD}$ = 3.0 V; $T_{amb}$ = 105 °C                                            |                  |     |     |     |      |

|                  |                    | $V_{IC}$ = 0.1 V; 100 mV overdrive input                                                     | [1][2][4]        | -   | 240 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 0.1 V; rail-to-rail input                                                  | [1][2]           | -   | 60  | -   | ns   |

|                  |                    | V <sub>IC</sub> = 1.5 V; 100 mV overdrive input                                              | [1][2][4]        | -   | 160 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 1.5 V; rail-to-rail input                                                  | [1][2]           | -   | 150 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 2.9 V; 100 mV overdrive input                                              | [1][2][4]        | -   | 150 | -   | ns   |

|                  |                    | V <sub>IC</sub> = 2.9 V; rail-to-rail input                                                  | [1][2]           | -   | 260 | -   | ns   |

| V <sub>hys</sub> | hysteresis voltage | positive hysteresis; $V_{DD}$ = 3.0 V;<br>$V_{IC}$ = 1.5 V; $T_{amb}$ = 105 °C; settings:    | <u>[3]</u>       | -   |     | -   |      |

|                  |                    | 5 mV                                                                                         |                  |     | 6   |     | mV   |

|                  |                    | 10 mV                                                                                        |                  | -   | 11  | -   | mV   |

|                  |                    | 20 mV                                                                                        |                  | -   | 23  | -   | mV   |

| V <sub>hys</sub> | hysteresis voltage | negative hysteresis; $V_{DD} = 3.0 V$ ;<br>$V_{IC} = 1.5 V$ ; $T_{amb} = 105 °C$ ; settings: | [1][3]           |     |     |     |      |

|                  |                    | 5 mV                                                                                         |                  | -   | 10  | -   | mV   |

|                  |                    | 10 mV                                                                                        |                  | -   | 15  | -   | mV   |

|                  |                    | 20 mV                                                                                        |                  | -   | 27  | -   | mV   |

| R <sub>lad</sub> | ladder resistance  | -                                                                                            |                  | -   | 1   | -   | MΩ   |

[1] C<sub>L</sub> = 10 pF

[2] Characterized on typical samples, not tested in production.

[3] Input hysteresis is relative to the reference input channel and is software programmable.

[4] 100 mV overdrive corresponds to a square wave from 50 mV below the reference ( $V_{IC}$ ) to 50 mV above the reference.

#### Table 26. Comparator voltage ladder dynamic characteristics

$T_{amb} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C; \ V_{DD} = 1.8 \ V \ to \ 3.6 \ V.$

| Symbol             | Parameter                 | Conditions                               |            | Min | Тур | Max | Unit |

|--------------------|---------------------------|------------------------------------------|------------|-----|-----|-----|------|

| t <sub>s(pu)</sub> | power-up settling<br>time | to 99% of voltage<br>ladder output value | <u>[1]</u> | -   | 17  | -   | μS   |

| t <sub>s(sw)</sub> | switching settling time   | to 99% of voltage ladder output value    | <u>[1]</u> | -   | 18  | -   | μS   |

[1] Characterized on typical samples, not tested in production.

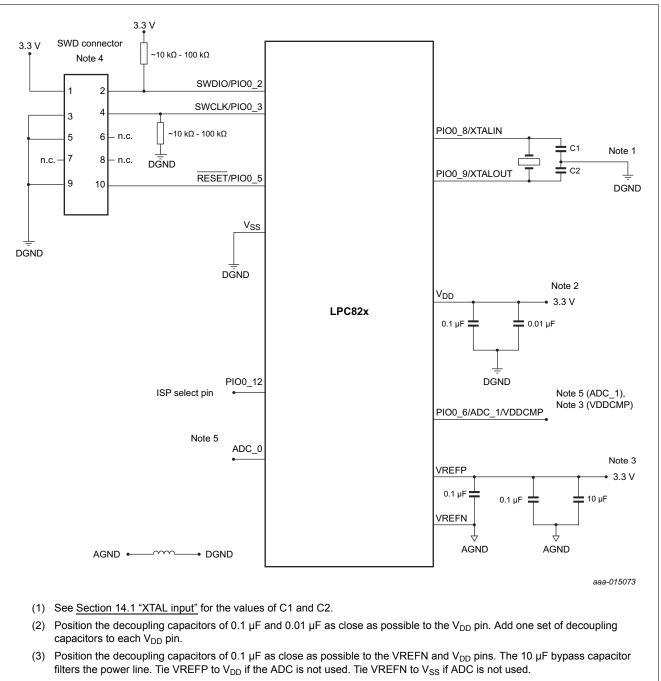

PC8

- (4) Uses the ARM 10-pin interface for SWD.

- (5) When measuring signals of low frequency, use a low-pass filter to remove noise and to improve ADC performance. Also see Ref. 4.

Fig 43. Power, clock, and debug connections

# 14.4 Termination of unused pins

<u>Table 30</u> shows how to terminate pins that are **not** used in the application. In many cases, unused pins may should be connected externally or configured correctly by software to minimize the overall power consumption of the part.

Unused pins with GPIO function should be configured as outputs set to LOW with their internal pull-up disabled. To configure a GPIO pin as output and drive it LOW, select the GPIO function in the IOCON register, select output in the GPIO DIR register, and write a 0 to the GPIO PORT register for that pin. Disable the pull-up in the pin's IOCON register.

In addition, it is recommended to configure all GPIO pins that are not bonded out on smaller packages as outputs driven LOW with their internal pull-up disabled.

| Pin                            | Default<br>state <u>[1]</u> | Recommended termination of unused pins                                                                                                                                                                      |

|--------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET/PIO0_5                   | I; PU                       | In an application that does not use the RESET pin or its GPIO function, the termination of this pin depends on whether Deep power-down mode is used:                                                        |

|                                |                             | • Deep power-down used: Connect an external pull-up resistor and keep pin in default state (input, pull-up enabled) during all other power modes.                                                           |

|                                |                             | <ul> <li>Deep power-down not used and no external pull-up connected: can be left<br/>unconnected if internal pull-up is disabled and pin is driven LOW and<br/>configured as output by software.</li> </ul> |

| all PIOn_m (not<br>open-drain) | I; PU                       | Can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software.                                                                                                      |

| PIOn_m (I2C open-drain)        | IA                          | Can be left unconnected if driven LOW and configured as GPIO output by software.                                                                                                                            |

| VREFP                          | -                           | Tie to VDD.                                                                                                                                                                                                 |

| VREFN                          | -                           | Tie to VSS.                                                                                                                                                                                                 |

Table 30.

Termination of unused pins

[1] I = Input, O = Output, IA = Inactive (no pull-up/pull-down enabled), F = floating, PU = Pull-Up.

# 14.5 Pin states in different power modes

| Table 31. | Pin states | in different power modes |

|-----------|------------|--------------------------|

|-----------|------------|--------------------------|

| Pin                                            | Active                         | Sleep                          | Deep-sleep/Power-<br>down | Deep power-down                                                                                                                                          |

|------------------------------------------------|--------------------------------|--------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIOn_m pins (not<br>I2C)                       | As configured in th enabled.   | e IOCON <sup>[1]</sup> . Defau | Floating.                 |                                                                                                                                                          |

| PIO0_4, PIO0_5<br>(open-drain<br>I2C-bus pins) | As configured in th            | e IOCON <u>[1]</u> .           |                           | Floating.                                                                                                                                                |

| RESET                                          | Reset function ena<br>enabled. | ıbled. Default: inpu           | ıt, internal pull-up      | Reset function disabled; floating; if the part<br>is in deep power-down mode, the RESET<br>pin needs an external pull-up to reduce<br>power consumption. |

| PIO0_16/<br>WAKEUP                             | As configured in th            | e IOCON <sup>[1]</sup> . WAKE  | EUP function inactive.    | Wake-up function enabled; can be disabled by software.                                                                                                   |

[1] Default and programmed pin states are retained in sleep, deep-sleep, and power-down modes.

LPC82x

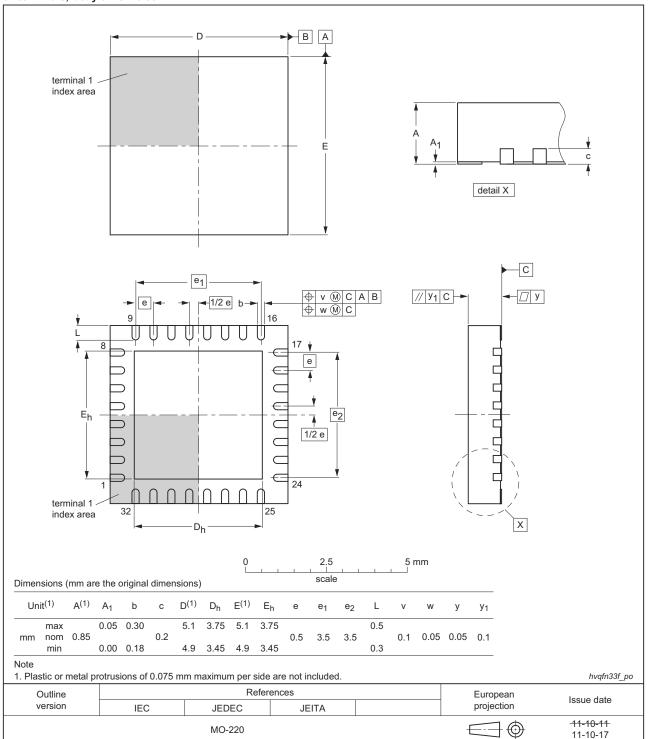

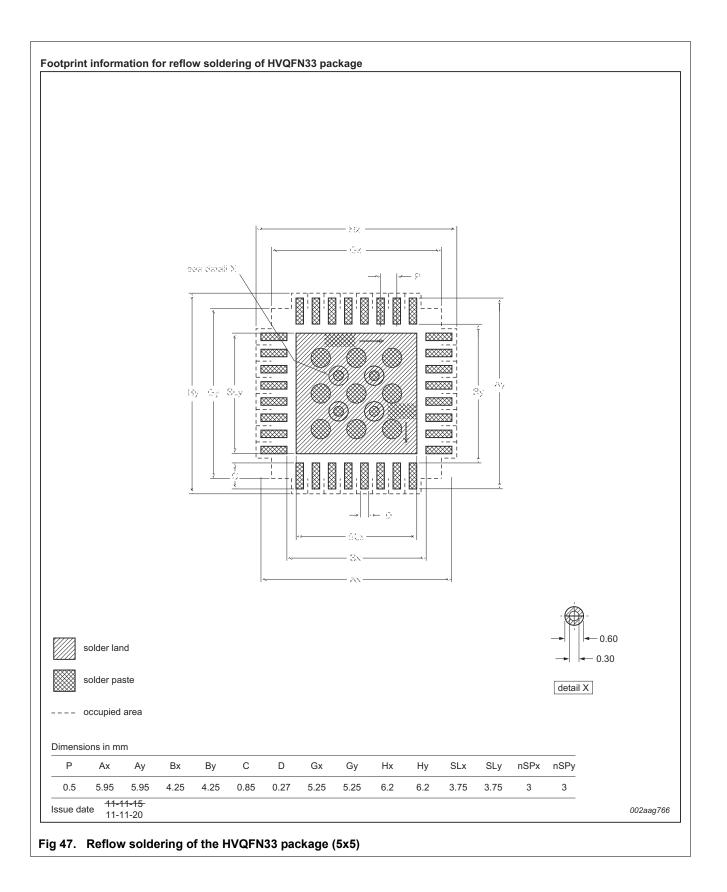

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 x 5 x 0.85 mm

### Fig 45. Package outline (HVQFN33 5x5)

LPC82x

© NXP Semiconductors N.V. 2018. All rights reserved.

LPC82x

All information provided in this document is subject to legal disclaimers.