Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 010                      |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LCD, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 68                                                                               |

| Program Memory Size        | 48KB (48K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 6K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

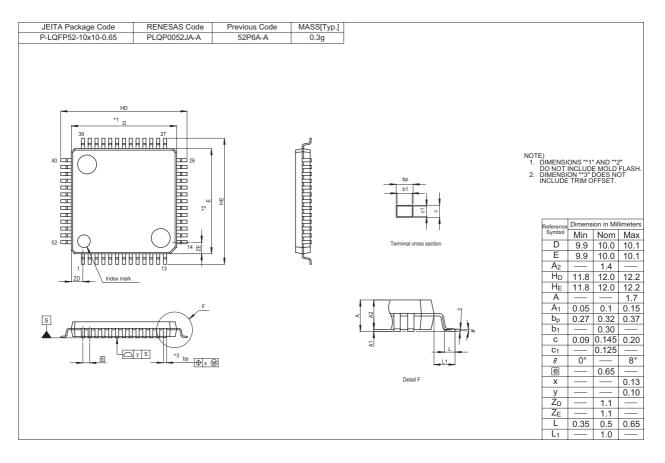

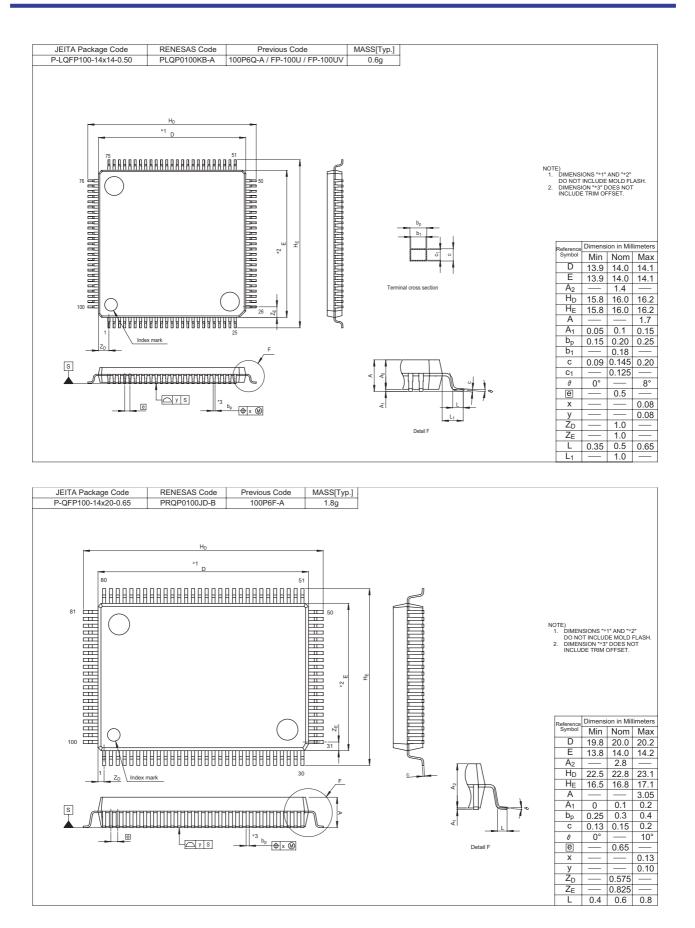

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f2l387cnfp-30 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                 | Function       | Specificati                                                                                      | on                                 |  |  |  |  |

|----------------------|----------------|--------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| Timer                | Timer RA       | 8 bits × 1 (with 8-bit prescaler)                                                                |                                    |  |  |  |  |

|                      |                | Timer mode (period timer), pulse output m                                                        |                                    |  |  |  |  |

|                      |                | period), event counter mode, pulse width measurement mode,                                       |                                    |  |  |  |  |

|                      | T DD           | pulse period measurement mode                                                                    |                                    |  |  |  |  |

|                      | Timer RB       | 8 bits x 1 (with 8-bit prescaler)<br>Timer mode (period timer), programmable                     | wayoform apporation mode (PW/M     |  |  |  |  |

|                      |                | output), programmable one-shot generation                                                        |                                    |  |  |  |  |

|                      |                | shot generation mode                                                                             | in mode, programmable wait one-    |  |  |  |  |

|                      | Timer RC       | 16 bits × 1 (with 4 capture/compare registers                                                    | 3                                  |  |  |  |  |

|                      |                | Timer mode (input capture function, output                                                       | t compare function), PWM mode      |  |  |  |  |

|                      |                | (output: 3 pins), PWM2 mode (PWM output: 1 pin)                                                  |                                    |  |  |  |  |

|                      | Timer RD       | 16 bits x 2 (with 4 capture/compare registers                                                    |                                    |  |  |  |  |

|                      |                | Timer mode (input capture function, output                                                       |                                    |  |  |  |  |

|                      |                | (output: 6 pins), reset synchronous PWM n                                                        |                                    |  |  |  |  |

|                      |                | 6 pins, sawtooth wave modulation), compl                                                         |                                    |  |  |  |  |

|                      |                | waveform output: 6 pins, triangular wave r                                                       | nodulation), PWM3 mode (PWM        |  |  |  |  |

|                      |                | output with fixed period: 2 pins)                                                                |                                    |  |  |  |  |

|                      | Timer RE       | 8 bits × 1                                                                                       |                                    |  |  |  |  |

|                      |                | Real-time clock mode (counting of seconds, minutes, hours, days of week),                        |                                    |  |  |  |  |

|                      | Timer RG       | output compare mode<br>16 bits x 1                                                               |                                    |  |  |  |  |

|                      |                | Phase-counting mode,                                                                             |                                    |  |  |  |  |

|                      |                | timer mode (output compare function, input capture function),                                    |                                    |  |  |  |  |

|                      |                | PWM mode (output: 1 pin)                                                                         |                                    |  |  |  |  |

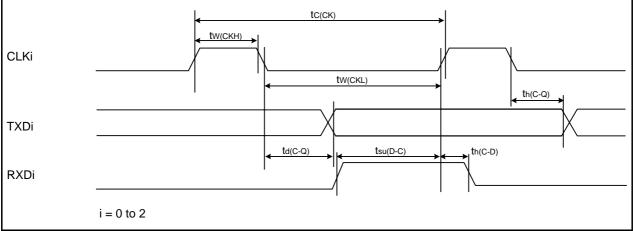

| Serial               | UART0, UART1   | Clock synchronous serial I/O/UART × 2 char                                                       | nnels                              |  |  |  |  |

| Interface            | UART2          | Clock synchronous serial I/O/UART, I <sup>2</sup> C mod<br>multiprocessor communication function | de (l <sup>2</sup> C-bus),         |  |  |  |  |

| Synchronous          | Sorial         |                                                                                                  |                                    |  |  |  |  |

|                      | ion Unit (SSU) | 1 (shared with I <sup>2</sup> C-bus)                                                             |                                    |  |  |  |  |

| I <sup>2</sup> C bus |                | 1 (shared with SSU)                                                                              |                                    |  |  |  |  |

| LIN Module           |                | Hardware LIN: 1 channel (timer RA, UART0 used)                                                   |                                    |  |  |  |  |

| A/D                  | R8C/L35C Group |                                                                                                  |                                    |  |  |  |  |

| Converter            | 100/2000 01000 | 10-bit resolution × 10 channels, including sample and hold function, with sweep mode             |                                    |  |  |  |  |

|                      | R8C/L36C Group | 10-bit resolution × 10 channels, including sample and hold function, with sweep                  |                                    |  |  |  |  |

|                      |                | mode                                                                                             |                                    |  |  |  |  |

|                      | R8C/L38C Group | 10-bit resolution × 16 channels, including sa mode                                               | mple and hold function, with sweep |  |  |  |  |

|                      | R8C/L3AC Group | 10-bit resolution × 20 channels, including sa                                                    | mple and hold function, with sweep |  |  |  |  |

|                      |                | mode                                                                                             |                                    |  |  |  |  |

| D/A Converte         | er             | 8-bit resolution × 2 circuits                                                                    |                                    |  |  |  |  |

| Comparator I         |                | 2 circuits                                                                                       |                                    |  |  |  |  |

| LCD Drive            | R8C/L35C Group | Common output: Max. 4 pins                                                                       | Bias: 1/2, 1/3                     |  |  |  |  |

| Control              |                | Segment output: Max. 24 pins                                                                     | Duty: static, 1/2, 1/3, 1/4        |  |  |  |  |

| Circuit              | R8C/L36C Group | Common output: Max. 8 pins                                                                       |                                    |  |  |  |  |

|                      |                | Segment output: Max. 32 pins <sup>(1)</sup>                                                      |                                    |  |  |  |  |

|                      | R8C/L38C Group | Common output: Max. 8 pins                                                                       | Bias: 1/2, 1/3, 1/4                |  |  |  |  |

|                      |                | Segment output: Max. 48 pins <sup>(1)</sup>                                                      | Duty: static, 1/2, 1/3, 1/4, 1/8   |  |  |  |  |

|                      | R8C/L3AC Group | Common output: Max. 8 pins                                                                       |                                    |  |  |  |  |

|                      |                | Segment output: Max. 56 pins <sup>(1)</sup>                                                      |                                    |  |  |  |  |

|                      |                | Voltage multiplier and dedicated regulator in                                                    | tearated                           |  |  |  |  |

|                      |                | voltage multiplier and dedicated regulator in                                                    | legialeu                           |  |  |  |  |

**Specifications (2)** Table 1.5

Note: 1. This applies when four pins are selected for common output.

| Item                          | Specification                                                                    |

|-------------------------------|----------------------------------------------------------------------------------|

| Flash Memory                  | <ul> <li>Programming and erasure voltage: VCC = 2.7 to 5.5 V</li> </ul>          |

|                               | <ul> <li>Programming and erasure endurance: 10,000 times (data flash)</li> </ul> |

|                               | 1,000 times (program ROM)                                                        |

|                               | <ul> <li>Program security: ROM code protect, ID code check</li> </ul>            |

|                               | On-chip debug function                                                           |

|                               | On-board flash rewrite function                                                  |

|                               | <ul> <li>Background operation (BGO) function</li> </ul>                          |

| Operating Frequency/          | f(XIN) = 20 MHz (VCC = 2.7 to 5.5 V)                                             |

| Supply Voltage                | f(XIN) = 5 MHz (VCC = 1.8 to 5.5 V)                                              |

| Current Consumption           | Typ. 7 mA (VCC = 5.0 V, f(XIN) = 20 MHz)                                         |

|                               | Typ. 3.6 mA (VCC = 3.0 V, f(XIN) = 10 MHz)                                       |

|                               | Typ. 3.5 μA (VCC = 3.0 V, wait mode (f(XCIN) = 32 kHz))                          |

|                               | Typ. 2 µA (VCC = 3.0 V, stop mode)                                               |

|                               | Typ. 0.02 $\mu$ A (VCC = 3.0 V, power-off mode)                                  |

| Operating Ambient Temperature | -20 to 85°C (N version)                                                          |

|                               | -40 to 85°C (D version) <sup>(1)</sup>                                           |

**Specifications (3)** Table 1.6

Note: 1. Specify the D version if D version functions are to be used.

| Item                                           | Pin Name                                                                                                                                                                                                     | I/O Type | Description                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

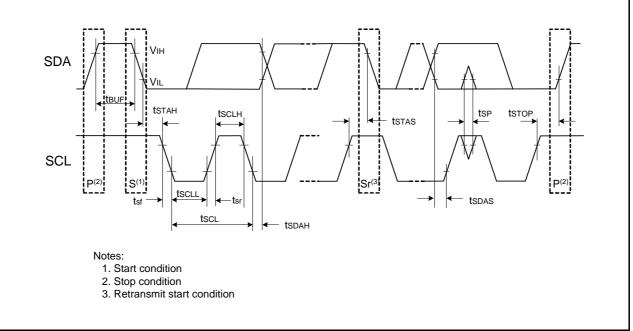

| I <sup>2</sup> C bus                           | SCL                                                                                                                                                                                                          | I/O      | Clock I/O pin                                                                                                                                                                                                                                                                                                            |

|                                                | SDA                                                                                                                                                                                                          | I/O      | Data I/O pin                                                                                                                                                                                                                                                                                                             |

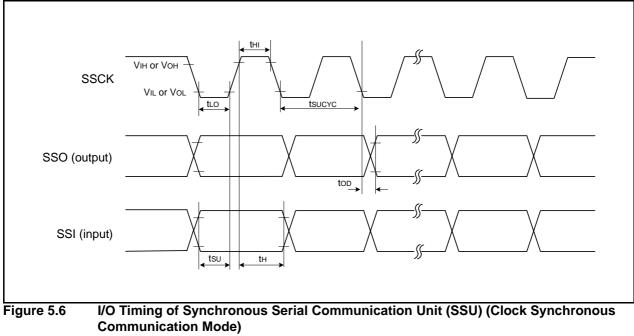

| SSU                                            | SSI                                                                                                                                                                                                          | I/O      | Data I/O pin                                                                                                                                                                                                                                                                                                             |

|                                                | SCS                                                                                                                                                                                                          | I/O      | Chip-select signal I/O pin                                                                                                                                                                                                                                                                                               |

|                                                | SSCK                                                                                                                                                                                                         | I/O      | Clock I/O pin                                                                                                                                                                                                                                                                                                            |

|                                                | SSO                                                                                                                                                                                                          | I/O      | Data I/O pin                                                                                                                                                                                                                                                                                                             |

| Reference voltage input                        | VREF                                                                                                                                                                                                         | I        | Reference voltage input pin for the A/D converter and the D/A converter                                                                                                                                                                                                                                                  |

| A/D converter                                  | AN0 to AN11                                                                                                                                                                                                  | I        | A/D converter analog input pins                                                                                                                                                                                                                                                                                          |

|                                                | ADTRG                                                                                                                                                                                                        | I        | A/D external trigger input pin                                                                                                                                                                                                                                                                                           |

| D/A converter                                  | DA0, DA1                                                                                                                                                                                                     | 0        | D/A converter output pins                                                                                                                                                                                                                                                                                                |

| Comparator B                                   | IVCMP1, IVCMP3                                                                                                                                                                                               | I        | Comparator B analog voltage input pins                                                                                                                                                                                                                                                                                   |

|                                                | IVREF1, IVREF3                                                                                                                                                                                               | I        | Comparator B reference voltage input pins                                                                                                                                                                                                                                                                                |

| I/O ports                                      | P0_0 to P0_7,<br>P1_0 to P1_7,<br>P2_0 to P2_7,<br>P3_0 to P3_7,<br>P4_0 to P4_7,<br>P5_0, P5_3,<br>P6_0 to P6_7<br>P7_0 to P7_7,<br>P10_0 to P10_7,<br>P11_0 to P11_7,<br>P12_0 to P12_3,<br>P13_0 to P13_7 | I/O      | CMOS I/O ports. Each port has an I/O select direction<br>register, allowing each pin in the port to be directed for input<br>or output individually.<br>Any port set to input can be set to use a pull-up resistor or not<br>by a program.<br>Ports P10_0 to P10_7 and P11_0 to P11_7 can be used as<br>LED drive ports. |

| Segment output                                 | SEG0 to SEG55                                                                                                                                                                                                | 0        | LCD segment output pins                                                                                                                                                                                                                                                                                                  |

| Common output                                  | COM0 to COM7                                                                                                                                                                                                 | 0        | LCD common output pins                                                                                                                                                                                                                                                                                                   |

| Voltage multiplier<br>capacity connect<br>pins | CL1, CL2                                                                                                                                                                                                     | 0        | Connect pins for the LCD control voltage multiplier                                                                                                                                                                                                                                                                      |

| LCD power supply                               | VL1                                                                                                                                                                                                          | I/O      | Apply the voltage: $0 \le VL1 \le VL2 \le VL3 \le VL4$ .                                                                                                                                                                                                                                                                 |

|                                                | VL2 to VL4                                                                                                                                                                                                   | I        | VL1 can be used as the reference potential input or output pin when setting the voltage multiplier.                                                                                                                                                                                                                      |

| Table 1.15 | Pin Functions for R8C/L3AC Group (2) |

|------------|--------------------------------------|

|------------|--------------------------------------|

I: Input O: Output I/O: Input and output

Note:

1. Contact the oscillator manufacturer for oscillation characteristics.

#### 2.1 Data Registers (R0, R1, R2, and R3)

R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.

#### 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32-bit address register (A1A0).

#### 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

#### 2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register that indicates the starting address of an interrupt vector table.

#### 2.5 Program Counter (PC)

PC is 20 bits wide and indicates the address of the next instruction to be executed.

## 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointers (SP), USP and ISP, are each 16 bits wide. The U flag of FLG is used to switch between USP and ISP.

#### 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

#### 2.8 Flag Register (FLG)

FLG is an 11-bit register indicating the CPU state.

#### 2.8.1 Carry Flag (C)

The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.

#### 2.8.2 Debug Flag (D)

The D flag is for debugging only. Set it to 0.

## 2.8.3 Zero Flag (Z)

The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.

#### 2.8.4 Sign Flag (S)

The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.

#### 2.8.5 Register Bank Select Flag (B)

Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.

#### 2.8.6 Overflow Flag (O)

The O flag is set to 1 when an operation results in an overflow; otherwise to 0.

## 2.8.7 Interrupt Enable Flag (I)

The I flag enables maskable interrupts.

Interrupts are disabled when the I flag is set to 0, and are enabled when the I flag is set to 1. The I flag is set to 0 when an interrupt request is acknowledged.

## 2.8.8 Stack Pointer Select Flag (U)

ISP is selected when the U flag is set to 0; USP is selected when the U flag is set to 1. The U flag is set to 0 when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.

## 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is 3 bits wide and assigns processor interrupt priority levels from level 0 to level 7. If a requested interrupt has higher priority than IPL, the interrupt is enabled.

#### 2.8.10 Reserved Bit

If necessary, set to 0. When read, the content is undefined.

| Address                                                              | Register                                                       | Symbol           | After Reset      |

|----------------------------------------------------------------------|----------------------------------------------------------------|------------------|------------------|

| 0080h                                                                | DTC Activation Control Register                                | DTCTL            | 00h              |

| 0081h                                                                |                                                                |                  |                  |

| 0082h                                                                |                                                                |                  |                  |

| 0083h                                                                |                                                                |                  |                  |

| 0084h                                                                |                                                                |                  |                  |

| 0085h                                                                |                                                                |                  |                  |

| 0085h                                                                |                                                                |                  |                  |

|                                                                      |                                                                |                  |                  |

| 0087h                                                                |                                                                |                  |                  |

| 0088h                                                                | DTC Activation Enable Register 0                               | DTCEN0           | 00h              |

| 0089h                                                                | DTC Activation Enable Register 1                               | DTCEN1           | 00h              |

| 008Ah                                                                | DTC Activation Enable Register 2                               | DTCEN2           | 00h              |

| 008Bh                                                                | DTC Activation Enable Register 3                               | DTCEN3           | 00h              |

| 008Ch                                                                | DTC Activation Enable Register 4                               | DTCEN4           | 00h              |

| 008Dh                                                                | DTC Activation Enable Register 5                               | DTCEN5           | 00h              |

| 008Eh                                                                | DTC Activation Enable Register 6                               | DTCEN6           | 00h              |

|                                                                      | DTC Activation Enable Register o                               | DICENO           | 0011             |

| 008Fh                                                                |                                                                |                  |                  |

| 0090h                                                                |                                                                |                  |                  |

| 0091h                                                                |                                                                |                  |                  |

| 0092h                                                                |                                                                |                  |                  |

| 0093h                                                                |                                                                |                  |                  |

| 0094h                                                                |                                                                | İ                |                  |

| 0095h                                                                |                                                                |                  |                  |

| 0096h                                                                |                                                                |                  |                  |

| 0096h                                                                |                                                                |                  |                  |

|                                                                      |                                                                |                  |                  |

| 0098h                                                                |                                                                |                  |                  |

| 0099h                                                                |                                                                |                  |                  |

| 009Ah                                                                |                                                                |                  |                  |

| 009Bh                                                                |                                                                |                  |                  |

| 009Ch                                                                |                                                                |                  |                  |

| 009Dh                                                                |                                                                |                  |                  |

| 009Eh                                                                |                                                                |                  |                  |

| 009Fh                                                                |                                                                |                  |                  |

|                                                                      | LIADTO Transmit/Dessitys Made Desister                         | U0MR             | 00h              |

| 00A0h                                                                | UARTO Transmit/Receive Mode Register                           |                  | 00h              |

| 00A1h                                                                | UART0 Bit Rate Register                                        | U0BRG            | XXh              |

| 00A2h                                                                | UART0 Transmit Buffer Register                                 | U0TB             | XXh              |

| 00A3h                                                                |                                                                |                  | XXh              |

| 00A4h                                                                | UART0 Transmit/Receive Control Register 0                      | U0C0             | 00001000b        |

| 00A5h                                                                | UART0 Transmit/Receive Control Register 1                      | U0C1             | 00000010b        |

| 00A6h                                                                | UART0 Receive Buffer Register                                  | UORB             | XXh              |

| 00A7h                                                                |                                                                |                  | XXh              |

| 00A8h                                                                | UART2 Transmit/Receive Mode Register                           | U2MR             | 00h              |

|                                                                      |                                                                |                  |                  |

| 00A9h                                                                | UART2 Bit Rate Register                                        | U2BRG            | XXh              |

| 00AAh                                                                | UART2 Transmit Buffer Register                                 | U2TB             | XXh              |

| 00ABh                                                                |                                                                |                  | XXh              |

| 00ACh                                                                | UART2 Transmit/Receive Control Register 0                      | U2C0             | 00001000b        |

| 00ADh                                                                | UART2 Transmit/Receive Control Register 1                      | U2C1             | 00000010b        |

| 00AEh                                                                | UART2 Receive Buffer Register                                  | U2RB             | XXh              |

| 00AFh                                                                | Ĭ                                                              | -                | XXh              |

| 00B0h                                                                | UART2 Digital Filter Function Select Register                  | URXDF            | 00h              |

| 00B0h                                                                |                                                                | 010,01           |                  |

|                                                                      |                                                                |                  |                  |

| 00B2h                                                                |                                                                |                  |                  |

| 00B3h                                                                |                                                                |                  |                  |

| 00B4h                                                                |                                                                |                  |                  |

| 00B5h                                                                |                                                                |                  |                  |

|                                                                      |                                                                |                  |                  |

| 00B6h                                                                |                                                                |                  |                  |

|                                                                      |                                                                |                  |                  |

| 00B6h<br>00B7h                                                       |                                                                |                  |                  |

| 00B6h<br>00B7h<br>00B8h                                              |                                                                |                  |                  |

| 00B6h<br>00B7h<br>00B8h<br>00B9h                                     |                                                                |                  |                  |

| 00B6h<br>00B7h<br>00B8h<br>00B9h<br>00BAh                            |                                                                |                  | 0.01             |

| 00B6h<br>00B7h<br>00B8h<br>00B9h<br>00BAh<br>00BBh                   | UART2 Special Mode Register 5                                  | U2SMR5           | 00h              |

| 00B6h<br>00B7h<br>00B8h<br>00B9h<br>00BAh<br>00BBh<br>00BCh          | UART2 Special Mode Register 4                                  | U2SMR4           | 00h              |

| 00B6h<br>00B7h<br>00B8h<br>00B9h<br>00BAh<br>00BBh<br>00BCh<br>00BDh | UART2 Special Mode Register 4<br>UART2 Special Mode Register 3 | U2SMR4<br>U2SMR3 | 00h<br>000X0X0Xb |

| 00B6h<br>00B7h<br>00B8h<br>00B9h<br>00BAh<br>00BBh<br>00BCh          | UART2 Special Mode Register 4                                  | U2SMR4           | 00h              |

#### SFR Information (3)<sup>(1)</sup> Table 4.3

X: Undefined Note: 1. Blank spaces are reserved. No access is allowed.

| Address | Register                                          | Symbol | After Reset |

|---------|---------------------------------------------------|--------|-------------|

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area DTC Transfer Vector Area |        | XXh<br>XXh  |

|         |                                                   |        |             |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          |        | XXh         |

|         | DTC Transfer Vector Area                          | DTODO  | XXh         |

|         | DTC Control Data 0                                | DTCD0  | XXh         |

| 2C41h   |                                                   |        | XXh         |

| 2C42h   |                                                   |        | XXh         |

| 2C43h   |                                                   |        | XXh         |

| 2C44h   |                                                   |        | XXh         |

| 2C45h   |                                                   |        | XXh         |

| 2C46h   |                                                   |        | XXh         |

| 2C47h   |                                                   | 5705/  | XXh         |

|         | DTC Control Data 1                                | DTCD1  | XXh         |

| 2C49h   |                                                   |        | XXh         |

| 2C4Ah   |                                                   |        | XXh         |

| 2C4Bh   |                                                   |        | XXh         |

| 2C4Ch   |                                                   |        | XXh         |

| 2C4Dh   |                                                   |        | XXh         |

| 2C4Eh   |                                                   |        | XXh         |

| 2C4Fh   |                                                   |        | XXh         |

|         | DTC Control Data 2                                | DTCD2  | XXh         |

| 2C51h   |                                                   |        | XXh         |

| 2C52h   |                                                   |        | XXh         |

| 2C53h   |                                                   |        | XXh         |

| 2C54h   |                                                   |        | XXh         |

| 2C55h   |                                                   |        | XXh         |

| 2C56h   |                                                   |        | XXh         |

| 2C57h   |                                                   |        | XXh         |

|         | DTC Control Data 3                                | DTCD3  | XXh         |

| 2C59h   |                                                   |        | XXh         |

| 2C5Ah   |                                                   |        | XXh         |

| 2C5Bh   |                                                   |        | XXh         |

| 2C5Ch   |                                                   |        | XXh         |

| 2C5Dh   |                                                   |        | XXh         |

| 2C5Eh   |                                                   |        | XXh         |

| 2C5Fh   |                                                   |        | XXh         |

|         | DTC Control Data 4                                | DTCD4  | XXh         |

| 2C61h   |                                                   |        | XXh         |

| 2C62h   |                                                   |        | XXh         |

| 2C63h   |                                                   |        | XXh         |

| 2C64h   |                                                   |        | XXh         |

| 2C65h   |                                                   |        | XXh         |

| 2C66h   |                                                   |        | XXh         |

| 2C67h   |                                                   |        | XXh         |

|         | DTC Control Data 5                                | DTCD5  | XXh         |

| 2C69h   |                                                   |        | XXh         |

| 2C6Ah   |                                                   |        | XXh         |

| 2C6Bh   |                                                   |        | XXh         |

| 2C6Ch   |                                                   |        | XXh         |

| 2C6Dh   |                                                   |        | XXh         |

| 2C6Eh   |                                                   |        | XXh         |

| 2002    |                                                   |        | XXh         |

#### SFR Information (13)<sup>(1)</sup> Table 4.13

X: Undefined Note: 1. Blank spaces are reserved. No access is allowed.

| Address        | Register            | Symbol  | After Reset |

|----------------|---------------------|---------|-------------|

| 2C70h          | DTC Control Data 6  | DTCD6   | XXh         |

| 2C71h          |                     |         | XXh         |

| 2C72h          |                     |         | XXh         |

| 2C73h          | -                   |         | XXh         |

|                |                     |         |             |

| 2C74h          |                     |         | XXh         |

| 2C75h          |                     |         | XXh         |

| 2C76h          |                     |         | XXh         |

| 2C77h          |                     |         | XXh         |

| 2C78h          | DTC Control Data 7  | DTCD7   | XXh         |

|                |                     | DICDI   |             |

| 2C79h          |                     |         | XXh         |

| 2C7Ah          |                     |         | XXh         |

| 2C7Bh          |                     |         | XXh         |

| 2C7Ch          |                     |         | XXh         |

| 2C7Dh          |                     |         | XXh         |

| 207Eh          | -                   |         | XXh         |

|                |                     |         |             |

| 2C7Fh          |                     |         | XXh         |

| 2C80h          | DTC Control Data 8  | DTCD8   | XXh         |

| 2C81h          |                     |         | XXh         |

| 2C82h          | 1                   |         | XXh         |

| 2C83h          | 1                   |         | XXh         |

| 2C83h          | 4                   |         |             |

|                | 4                   |         | XXh         |

| 2C85h          | 1                   |         | XXh         |

| 2C86h          |                     |         | XXh         |

| 2C87h          | 7                   |         | XXh         |

| 2C88h          | DTC Control Data 9  | DTCD9   | XXh         |

| 2C89h          |                     | 51050   | XXh         |

|                |                     |         |             |

| 2C8Ah          |                     |         | XXh         |

| 2C8Bh          |                     |         | XXh         |

| 2C8Ch          |                     |         | XXh         |

| 2C8Dh          |                     |         | XXh         |

| 2C8Eh          |                     |         | XXh         |

|                |                     |         |             |

| 2C8Fh          |                     |         | XXh         |

| 2C90h          | DTC Control Data 10 | DTCD10  | XXh         |

| 2C91h          |                     |         | XXh         |

| 2C92h          |                     |         | XXh         |

| 2C93h          |                     |         | XXh         |

| 2C94h          | 4                   |         | XXh         |

|                |                     |         |             |

| 2C95h          |                     |         | XXh         |

| 2C96h          |                     |         | XXh         |

| 2C97h          |                     |         | XXh         |

| 2C98h          | DTC Control Data 11 | DTCD11  | XXh         |

| 2C99h          |                     | 510511  | XXh         |

|                | 4                   |         |             |

| 2C9Ah          | 4                   |         | XXh         |

| 2C9Bh          |                     |         | XXh         |

| 2C9Ch          |                     |         | XXh         |

| 2C9Dh          | 1                   |         | XXh         |

| 2C9Eh          | 1                   |         | XXh         |

|                | 4                   |         |             |

| 2C9Fh          |                     | D700 (0 | XXh         |

| 2CA0h          | DTC Control Data 12 | DTCD12  | XXh         |

| 2CA1h          |                     |         | XXh         |

| 2CA2h          | 7                   |         | XXh         |

| 2CA3h          | 1                   |         | XXh         |

| 2CA4h          | 4                   |         | XXh         |

|                | 4                   |         |             |

| 2CA5h          | 4                   |         | XXh         |

| 2CA6h          |                     |         | XXh         |

| 2CA7h          | 7                   |         | XXh         |

| 2CA8h          | DTC Control Data 13 | DTCD13  | XXh         |

| 2CA9h          |                     | 510510  | XXh         |

|                | 4                   |         |             |

| 2CAAh          | 4                   |         | XXh         |

| 2CABh          |                     |         | XXh         |

| 2CACh          |                     |         | XXh         |

| 2CADh          | 1                   |         | XXh         |

|                | -                   |         | XXh         |

| 2(CAEh         |                     |         |             |

| 2CAEh<br>2CAFh | -                   |         | XXh         |

SFR Information (14)<sup>(1)</sup> Table 4.14

X: Undefined Note: 1. Blank spaces are reserved. No access is allowed.

# Table 5.4D/A Converter Characteristics<br/>(Vcc/AVcc = Vref = 2.7 to 5.5 V and Topr = -20 to 85°C (N version) / -40 to 85°C<br/>(D version), unless otherwise specified.)

| Symbol Parameter | Doromotor                     | Conditions | Standard |      |      | Unit |

|------------------|-------------------------------|------------|----------|------|------|------|

|                  | Falameter                     | Conditions | Min.     | Тур. | Max. | Unit |

| —                | Resolution                    |            |          |      | 8    | Bit  |

| —                | Absolute accuracy             |            | —        | _    | 2.5  | LSB  |

| tsu              | Setup time                    |            | —        | _    | 3    | μs   |

| Ro               | Output resistor               |            | —        | 6    | —    | kΩ   |

| IVref            | Reference power input current | (Note 1)   | _        | _    | 1.5  | mA   |

Note:

1. This applies when one D/A converter is used and the value of the DAi register (i = 0 or 1) for the unused D/A converter is 00h. The resistor ladder of the A/D converter is not included.

#### Table 5.5 Comparator B Characteristics

# (Vcc = 2.7 to 5.5 V and T<sub>opr</sub> = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol | Parameter                              | Condition          |      | Unit |           |      |

|--------|----------------------------------------|--------------------|------|------|-----------|------|

| Symbol | Falametei                              | Condition          | Min. | Тур. | Max.      | Unit |

| Vref   | IVREF1, IVREF3 input reference voltage |                    | 0    | _    | Vcc - 1.4 | V    |

| Vi     | IVCMP1, IVCMP3 input voltage           |                    | -0.3 | —    | Vcc + 0.3 | V    |

| —      | Offset                                 |                    | —    | 5    | 100       | mV   |

| td     | Comparator output delay time (1)       | VI = Vref ± 100 mV | —    | 0.1  | —         | μS   |

| ICMP   | Comparator operating current           | Vcc = 5.0 V        | —    | 17.5 | —         | μΑ   |

Note:

1. When the digital filter is disabled.

#### Table 5.7 Flash Memory (Data flash Block A to Block D) Characteristics (Vcc = 2.7 to 5.5 V and Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Cumbal               | Parameter                                                              | Conditions                  |            | Unit |                             |       |

|----------------------|------------------------------------------------------------------------|-----------------------------|------------|------|-----------------------------|-------|

| Symbol               | Parameter                                                              | Conditions                  | Min.       | Тур. | Max.                        | Unit  |

| _                    | Program/erase endurance (1)                                            |                             | 10,000 (2) | —    | —                           | times |

| _                    | Byte program time<br>(program/erase endurance ≤ 1,000 times)           |                             | —          | 160  | 1500                        | μS    |

| _                    | Byte program time<br>(program/erase endurance > 1,000 times)           |                             | _          | 300  | 1500                        | μS    |

| _                    | Block erase time<br>(program/erase endurance ≤ 1,000 times)            |                             | —          | 0.2  | 1                           | S     |

| _                    | Block erase time<br>(program/erase endurance > 1,000 times)            |                             | —          | 0.3  | 1                           | S     |

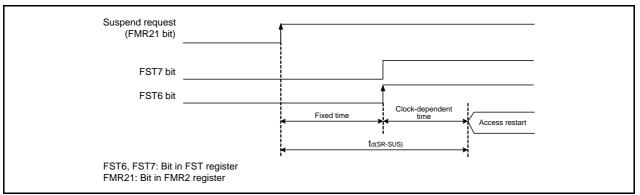

| td(SR-SUS)           | Time delay from suspend request until suspend                          |                             | —          | _    | 5 + CPU clock<br>× 3 cycles | ms    |

| _                    | Interval from erase start/restart until<br>following suspend request   |                             | 0          |      | —                           | ms    |

| _                    | Time from suspend until erase restart                                  |                             | _          | _    | 30+CPU clock<br>× 1 cycle   | μS    |

| td(CMDRST-<br>READY) | Time from when command is forcibly terminated until reading is enabled |                             | —          | _    | 30+CPU clock<br>× 1 cycle   | μS    |

| _                    | Program, erase voltage                                                 |                             | 2.7        |      | 5.5                         | V     |

| _                    | Read voltage                                                           |                             | 1.8        | _    | 5.5                         | V     |

| _                    | Program, erase temperature                                             |                             | -20 (6)    | _    | 85                          | °C    |

| _                    | Data hold time <sup>(7)</sup>                                          | Ambient temperature = 55 °C | 20         | _    | —                           | year  |

Notes:

1. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

2. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential 3. addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. In addition, averaging the erasure endurance between blocks A to D can further reduce the actual erasure endurance. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

4. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

5. Customers desiring program/erase failure rate information should contact their Renesas technical support representative. 6.

- -40°C for D version.

- 7. The data hold time includes time that the power supply is off or the clock is not supplied.

| Symbol  | Do                     | rameter                                                                                                                                                                                                                                                                                                                                                                                           | Condition               | S         | tandard |      | Unit |

|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|---------|------|------|

| Symbol  | Fd                     | lameter                                                                                                                                                                                                                                                                                                                                                                                           | Condition               | Min.      | 71      |      | Unit |

| Vон     | Output "H" voltage     | Port P10, P11 (1)                                                                                                                                                                                                                                                                                                                                                                                 | юн = -5 mA              | Vcc - 0.5 | _       | Vcc  | V    |

|         |                        | Other pins                                                                                                                                                                                                                                                                                                                                                                                        | Юн = -1 mA              | Vcc - 0.5 |         | Vcc  | V    |

|         |                        | XOUT                                                                                                                                                                                                                                                                                                                                                                                              | Юн = -200 μА            | 1.0       | _       | —    | V    |

| Vol     | Output "L" voltage     | Port P10, P11 (1)                                                                                                                                                                                                                                                                                                                                                                                 | IOL = 5 mA              | —         | -       | 0.5  | V    |

|         |                        | Other pins                                                                                                                                                                                                                                                                                                                                                                                        | IOL = 1 mA              | —         |         | 0.5  | V    |

|         |                        | XOUT                                                                                                                                                                                                                                                                                                                                                                                              | ΙΟL = 200 μΑ            | —         | _       | 0.5  | V    |

| VT+-VT- | Hysteresis             | INTO, INT1, INT2,<br>INT3, INT4, INT5,<br>INT6, INT7,<br>KI0, KI1, KI2, KI3, KI4,<br>KI5, KI6, KI7,<br>TRAIO,<br>TRCIOA, TRCIOB,<br>TRCIOC, TRCIOD,<br>TRDIOA0, TRDIOB0,<br>TRDIOC0, TRDIOD0,<br>TRDIOC1, TRDIOD1,<br>TRDIOC1, TRDIOD1,<br>TRDIOC1, TRDIOD1,<br>TRCTRG, TRCCLK,<br>TRGCLKA, TRGCLKB,<br>TRGIOA, TRGIOB,<br>ADTRG,<br>RXD0, RXD1, RXD2,<br>CLK0, CLK1, CLK2,<br>SSI, SCL, SDA, SSO |                         | 0.05      | 0.4     |      | V    |

|         |                        | RESET, WKUP0                                                                                                                                                                                                                                                                                                                                                                                      |                         | 0.1       | 0.8     | —    | V    |

| Ін      | Input "H" current      |                                                                                                                                                                                                                                                                                                                                                                                                   | VI = 3.0 V, Vcc = 3.0 V | —         | -       | 5.0  | μA   |

| lı∟     | Input "L" current      |                                                                                                                                                                                                                                                                                                                                                                                                   | VI = 0 V, Vcc = 3.0 V   | —         | _       | -5.0 | μA   |

| Rpullup | Pull-up resistance     | T                                                                                                                                                                                                                                                                                                                                                                                                 | VI = 0 V, Vcc = 3.0 V   | 30        | 100     | 170  | kΩ   |

| Rfxin   | Feedback<br>resistance | XIN                                                                                                                                                                                                                                                                                                                                                                                               |                         | —         | 0.3     | —    | MΩ   |

| Rfxcin  | Feedback<br>resistance | XCIN                                                                                                                                                                                                                                                                                                                                                                                              |                         | —         | 14      | —    | MΩ   |

| Vram    | RAM hold voltage       |                                                                                                                                                                                                                                                                                                                                                                                                   | During stop mode        | 1.8       | —       | —    | V    |

# Table 5.19DC Characteristics (3) $[2.7 V \le Vcc < 4.0 V]$ <br/>(Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

Note:

1. This applies when the drive capacity of the output transistor is set to High by registers P10DRR and P11DRR. When the drive capacity is set to Low, the value of any other pin applies.

|        |                                  | • •                                            |                     |            | •                     |              |                     | 0                                                                        |                                                                                                                                                                                                 |      | -           |      | <u> </u> |

|--------|----------------------------------|------------------------------------------------|---------------------|------------|-----------------------|--------------|---------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|------|----------|

|        |                                  |                                                | Osci                | llation    | On-C                  | hip          |                     | Condition                                                                |                                                                                                                                                                                                 | 5    | Standa      | ira  |          |

| Symbol | Parameter                        |                                                | Circuit<br>XIN XCIN |            | Oscilla<br>High-Speed |              | CPU<br>Clock        | Low-Power-<br>Consumption<br>Setting                                     | Other                                                                                                                                                                                           |      | Typ.<br>(3) | Max. | Un       |

| 00     | Power                            | High-                                          | (2)<br>20           | Off        | (fOCO-F)<br>Off       | Speed<br>125 | No                  |                                                                          |                                                                                                                                                                                                 |      | 7.0         | 14.5 | m/       |

|        | supply<br>current <sup>(1)</sup> | speed<br>clock                                 | MHz<br>10           | Off        | Off                   | kHz<br>125   | division<br>No      |                                                                          |                                                                                                                                                                                                 |      | 3.6         | 10   | m        |

|        |                                  | mode                                           | MHz<br>20           | Off        | Off                   | kHz<br>125   | division<br>Divide- |                                                                          |                                                                                                                                                                                                 | -    | 3.0         |      | m        |

|        |                                  |                                                | MHz                 | _          | -                     | kHz          | by-8                |                                                                          |                                                                                                                                                                                                 |      |             | _    |          |

|        |                                  |                                                | 10<br>MHz           | Off        | Off                   | 125<br>kHz   | Divide-<br>by-8     | _                                                                        |                                                                                                                                                                                                 |      | 1.5         | -    | m        |

|        |                                  | High-<br>speed                                 | Off                 | Off        | 20 MHz                | 125<br>kHz   | No<br>division      | _                                                                        |                                                                                                                                                                                                 | _    | 7.0         | 14.5 | m        |

|        |                                  | on-chip<br>oscillator                          | Off                 | Off        | 20 MHz                | 125<br>kHz   | Divide-<br>by-8     |                                                                          |                                                                                                                                                                                                 | -    | 3.0         | -    | m        |

|        |                                  | mode                                           | Off                 | Off        | 10 MHz                | 125<br>kHz   | No<br>division      | _                                                                        |                                                                                                                                                                                                 | -    | 4.0         | -    | m        |

|        |                                  |                                                | Off                 | Off        | 10 MHz                | 125<br>kHz   | Divide-<br>by-8     | _                                                                        |                                                                                                                                                                                                 | -    | 1.7         | -    | m        |

|        |                                  |                                                | Off                 | Off        | 4 MHz                 | 125<br>kHz   | Divide-<br>by-16    | MSTIIC = 1<br>MSTTRD = 1<br>MSTTRC = 1<br>MSTTRG = 1                     |                                                                                                                                                                                                 | -    | 1           | -    | m        |