Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LCD, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 68                                                                               |

| Program Memory Size        | 96KB (96K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 10K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f2l38acnfa-v0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | r        |          |          |          |          |          |          |          | -        |          |          |          |          |          |          |          |          |          |          |          |              |          |          |          | -        |          |          |          |          |          |              |              |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------------|--------------|

| _            |          |          |          |          | SC C     |          |          |          |          |          |          |          |          | Grou     | •        |          |          |          |          |          |              | Grou     |          |          |          |          |          |          | C C      |          | •            |              |

| Programmable |          | Т        | otal     | : 41     | I/O      | ) pin    | IS       |          |          | Т        | otal     | : 52     | I/C      | ) pin    | S        |          |          | Т        | otal     | : 68     | I/O          | ) pin    | IS       |          |          | Т        | otal     | : 88     | I/O      | pin      | s            |              |

| I/O Port     | bit<br>7 | bit<br>6 | bit<br>5 | bit<br>4 | bit<br>3 | bit<br>2 | bit<br>1 | bit<br>0 | bit<br>7 | bit<br>6 | bit<br>5 | bit<br>4 | bit<br>3 | bit<br>2 | bit<br>1 | bit<br>0 | bit<br>7 | bit<br>6 | bit<br>5 | bit<br>4 | bit<br>3     | bit<br>2 | bit<br>1 | bit<br>0 | bit<br>7 | bit<br>6 | bit<br>5 | bit<br>4 | bit<br>3 | bit<br>2 | bit<br>1     | bit<br>0     |

| P0           | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P1           | -        | Ι        | Ι        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | Ι        | -        | -        | Ι        | -        | Ι        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P2           | ~        | ~        | ~        | ~        | -        | -        | -        | -        | ~        | ~        | ~        | ~        | -        | -        | Ι        | -        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P3           | -        | 1        | 1        | -        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | $\checkmark$ | ~            |

| P4           | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | $\checkmark$ | ~            |

| P5           | -        | 1        | 1        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | 1        | -        | -        | 1        | -        | 1        | 1            | -        | -        | -        | -        | -        | -        | I        | ~        | ~        | $\checkmark$ | ~            |

| P6           | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P7           | ~        | ~        | ~        | ~        | -        | -        | -        | -        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | $\checkmark$ | ~            |

| P10          | -        | Ι        | Ι        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | Ι        | -        | -        | Ι        | -        | Ι        | Ι            | -        | -        | -        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P11          | -        | -        | -        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~            | ~            |

| P12          | -        | -        | -        | -        | ~        | ~        | ~        | ~        | -        | -        | -        | -        | ~        | ~        | ~        | ~        | -        | 1        | -        | -        | ~            | ~        | ~        | ~        | -        | -        | -        | -        | ~        | ~        | ~            | ~            |

| P13          | -        | -        | -        | -        | ~        | ~        | ~        | ~        | -        | -        | -        | -        | ~        | ~        | ~        | ~        | -        | 1        | -        | -        | $\checkmark$ | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | ~        | $\checkmark$ | $\checkmark$ |

### Table 1.2 Programmable I/O Ports Provided for Each Group

Notes:

1. The symbol " $\checkmark$ " indicates a programmable I/O port.

2. The symbol "-" indicates the settings should be made as follows:

- Set 1 to the corresponding bits in the PDi (i = 1 to 3, 5 to 7, and 10 to 13) register.

- Set 0 to the corresponding bits in the Pi (i = 1 to 3, 5 to 7, and 10 to 13) register.

- Set 0 to the corresponding bits in the P10DRR or P11DRR register.

### Table 1.3 LCD Display Function Pins Provided for Each Group

|          |           |           |           | 00        |                | о <b>р</b> . | ~,        |           |           |           | •••       |           | • • •     |           | 400           |           |           |           |           |           | ~ ~       |            |           |           |           |           |           |           |           |           |                |           |

|----------|-----------|-----------|-----------|-----------|----------------|--------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------------|-----------|

| Shared   |           | •         |           |           | Gro            | •            |           |           |           | _         |           | 6C        |           | •         |               |           |           | ~         |           | 8C        |           | •          |           |           |           | •         |           |           | Gro       |           |                |           |

| I/O Port |           |           |           |           | itput<br>tput: |              |           |           |           |           |           |           | •         |           | ax. 8<br>x. 3 |           |           |           |           |           | •         | : Ma<br>Ma |           |           |           |           |           |           |           |           | ax. 8<br>ax. 5 |           |

|          |           |           |           |           |                |              |           |           |           |           |           |           |           |           |               |           |           | _         |           |           | _         |            |           |           |           |           |           |           | <u> </u>  |           |                |           |

| P0       | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3       | SEG<br>2     | SEG<br>1  | SEG<br>0  | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1      | SEG<br>0  | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2   | SEG<br>1  | SEG<br>0  | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1       | SEG<br>0  |

| P1       | -         | -         | -         | -         | -              | -            | -         | -         | -         | -         | -         | -         | -         | -         | -             | -         | -         | -         | -         | -         | SEG<br>11 | SEG<br>10  | SEG<br>9  | SEG<br>8  | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9       | SEG<br>8  |

| P2       | SEG<br>23 | SEG<br>22 | SEG<br>21 | SEG<br>20 | -              | -            | -         | -         | SEG<br>23 | SEG<br>22 | SEG<br>21 | SEG<br>20 | -         | -         | -             | -         | SEG<br>23 | SEG<br>22 | SEG<br>21 | SEG<br>20 | SEG<br>19 | SEG<br>18  | SEG<br>17 | SEG<br>16 | SEG<br>23 | SEG<br>22 | SEG<br>21 | SEG<br>20 | SEG<br>19 | SEG<br>18 | SEG<br>17      | SEG<br>16 |

| P3       | -         | -         | -         | -         | SEG<br>27      | SEG<br>26    | SEG<br>25 | SEG<br>24 | SEG<br>31 | SEG<br>30 | SEG<br>29 | SEG<br>28 | SEG<br>27 | SEG<br>26 | SEG<br>25     | SEG<br>24 | SEG<br>31 | SEG<br>30 | SEG<br>29 | SEG<br>28 | SEG<br>27 | SEG<br>26  | SEG<br>25 | SEG<br>24 | SEG<br>31 | SEG<br>30 | SEG<br>29 | SEG<br>28 | SEG<br>27 | SEG<br>26 | SEG<br>25      | SEG<br>24 |

| P4       | SEG<br>39 | SEG<br>38 | SEG<br>37 | SEG<br>36 | SEG<br>35      | SEG<br>34    | SEG<br>33 | SEG<br>32 | SEG<br>39 | SEG<br>38 | SEG<br>37 | SEG<br>36 | SEG<br>35 | SEG<br>34 | SEG<br>33     | SEG<br>32 | SEG<br>39 | SEG<br>38 | SEG<br>37 | SEG<br>36 | SEG<br>35 | SEG<br>34  | SEG<br>33 | SEG<br>32 | SEG<br>39 | SEG<br>38 | SEG<br>37 | SEG<br>36 | SEG<br>35 | SEG<br>34 | SEG<br>33      | SEG<br>32 |

| P5       | -         | -         | -         | -         | -              | -            | -         | -         | -         | -         | -         | -         | -         | -         | -             | -         | -         | -         | -         | -         | -         | -          | -         | -         | -         | -         | -         | -         | SEG<br>43 | SEG<br>42 | SEG<br>41      | SEG<br>40 |

| P6       | -         | -         | -         | -         | -              | -            | -         | -         | -         | -         | -         | -         | -         | -         | -             | -         | SEG<br>51 | SEG<br>50 | SEG<br>49 | SEG<br>48 | SEG<br>47 | SEG<br>46  | SEG<br>45 | SEG<br>44 | SEG<br>51 | SEG<br>50 | SEG<br>49 | SEG<br>48 | SEG<br>47 | SEG<br>46 | SEG<br>45      | SEG<br>44 |

| P7       | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | -              | -            | -         | -         | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | SEG<br>55 | SEG<br>54 | SEG<br>53     | SEG<br>52 | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | SEG<br>55 | SEG<br>54  | SEG<br>53 | SEG<br>52 | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | SEG<br>55 | SEG<br>54 | SEG<br>53      | SEG<br>52 |

| P12      | -         | -         | I         | -         | CL2            | CL1          | -         | -         | -         | I         | I         | -         | CL2       | CL1       | I             | -         | -         | I         | -         | I         | CL2       | CL1        | I         | I         | -         | -         | -         | -         | CL2       | CL1       | -              | -         |

| -        |           |           |           | V         | L1             |              |           |           |           |           |           | V         | L1        |           |               |           |           |           |           | VI        | _1        |            |           |           |           |           |           | VI        | _1        |           |                |           |

| -        |           |           |           | V         | L2             |              |           |           |           |           |           | V         | _2        |           |               |           |           |           |           | VI        | _2        |            |           |           |           |           |           | VI        | L2        |           |                |           |

| _        |           |           |           | -         | _              |              |           |           |           |           |           | V         | _3        |           |               |           |           |           |           | VI        | _3        |            |           |           |           |           |           | VI        | ∟3        |           |                |           |

|          |           |           |           | V         | L4             |              |           |           |           |           |           | V         | _4        |           |               |           |           |           |           | VI        | _4        |            |           |           |           |           |           | VI        | L4        |           |                |           |

Notes:

1. The symbol "-" indicates there is no LCD display function. Set the corresponding bits in registers LSE1 to LSE3, LSE5 to LSE7 to 0 for these pins.

2. SEG52 to SEG55 can be used as COM7 to COM4.

The R8C/L35C Group does not have pins SEG52 to SEG55, so 1/8 duty cannot be selected.

3. The R8C/L35C Group does not have the VL3 pin, so 1/4 bias cannot be selected. When the internal voltage multiplier is used, 1/2 bias cannot also be selected.

| 1. Overview |

|-------------|

|-------------|

Current of Apr 2011

|              |             | -           |              |              |           |

|--------------|-------------|-------------|--------------|--------------|-----------|

| Part No.     | Internal RC | M Capacity  | Internal RAM | Package Type | Remarks   |

| Fait NO.     | Program ROM | Data Flash  | Capacity     | Fackage Type | Remarks   |

| R5F2L387CNFP | 48 Kbytes   | 1 Kbyte × 4 | 6 Kbytes     | PLQP0080KB-A | N Version |

| R5F2L387CNFA | 48 Kbytes   | 1 Kbyte × 4 | 6 Kbytes     | PLQP0080JA-A |           |

| R5F2L388CNFP | 64 Kbytes   | 1 Kbyte × 4 | 8 Kbytes     | PLQP0080KB-A |           |

| R5F2L388CNFA | 64 Kbytes   | 1 Kbyte × 4 | 8 Kbytes     | PLQP0080JA-A |           |

| R5F2L38ACNFP | 96 Kbytes   | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080KB-A |           |

| R5F2L38ACNFA | 96 Kbytes   | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080JA-A |           |

| R5F2L38CCNFP | 128 Kbytes  | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080KB-A |           |

| R5F2L38CCNFA | 128 Kbytes  | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080JA-A |           |

| R5F2L387CDFP | 48 Kbytes   | 1 Kbyte × 4 | 6 Kbytes     | PLQP0080KB-A | D Version |

| R5F2L387CDFA | 48 Kbytes   | 1 Kbyte × 4 | 6 Kbytes     | PLQP0080JA-A |           |

| R5F2L388CDFP | 64 Kbytes   | 1 Kbyte × 4 | 8 Kbytes     | PLQP0080KB-A |           |

| R5F2L388CDFA | 64 Kbytes   | 1 Kbyte × 4 | 8 Kbytes     | PLQP0080JA-A |           |

| R5F2L38ACDFP | 96 Kbytes   | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080KB-A |           |

| R5F2L38ACDFA | 96 Kbytes   | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080JA-A | 1         |

| R5F2L38CCDFP | 128 Kbytes  | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080KB-A | 1         |

| R5F2L38CCDFA | 128 Kbytes  | 1 Kbyte × 4 | 10 Kbytes    | PLQP0080JA-A | 1         |

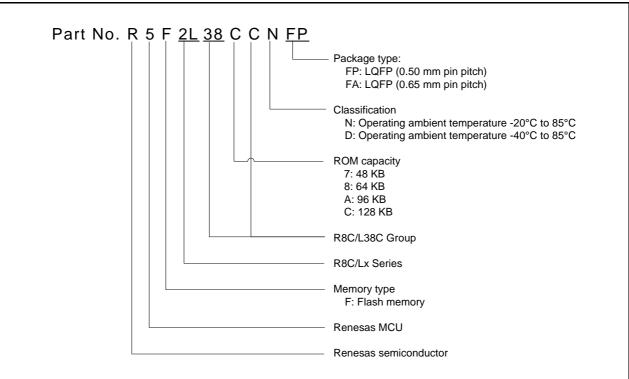

Figure 1.3 Correspondence of Part No., with Memory Size and Package of R8C/L38C Group

| L3B         L3B         L3B         L3B         L3B         Pin         Pin         Pin         Interrupt         Timer         Iserial         SSU         Pic Dot Dot Struct B         Concerner, or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Р       | in Num | nber |      |       |                |                    | I/O       | Pin Functions | for Per | ipheral | Modules        |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------|------|-------|----------------|--------------------|-----------|---------------|---------|---------|----------------|---------------------------------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | L38C   | L36C | L35C |       | Port           | Interrupt          | Timer     |               | SSU     |         | D/A Converter, | LCD drive<br>control<br>circuit |

| 3 [5]         2         63         1         P13_1         TXD0         AN1/DA1           4 [6]         3         64         2         P13_0         AN0/DA0         AN0/DA0           5 [7]         4         1         3         WKUP6         AN0/DA0         AN0/DA0           6 [8]         5         2         4         VREF         An0/DA0         AN0/DA0           7 [9]         6         3         5         MODE         An0/DA0         An0/DA0           9[10]         7         4         6         XCIN         An0/DA0         An0/DA0           9[11]         8         5         7         XCOUT         An0/DA0         An0/DA0           10 [12]         9         6         8         RESET         AN0/DA0         An0/DA0           11[13]         10         7         9         XOUT         P12_0         An0/C         An0/C           14 [16]         13         10         12         AVCC         ANCC         An0/C         An0/C           16 [18]         15         12         P11_7         (INT5)         TRAO         An0/DA0           19 [21]         18         15         14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 [3]   | 80     | 61   | 51   |       | P13_3          |                    |           | CLK0          |         |         |                |                                 |

| 4 [6]       3       64       2       P13_0       AN0DA0         5 [7]       4       1       3       WRUP5       AN0DA0       AN0DA0         6 [8]       5       2       4       VREF       AnonA       AnonA         7 [9]       6       3       5       MODE       AnonA       AnonA         8 [10]       7       4       6       XCN       AnonA       AnonA         9 [11]       8       5       7       XCOUT       AnonA       AnonA         10 [12]       9       6       8       RESET       AnonA       AnonA         11 [13]       10       7       9       XOUT       P12_0       AnonA       AnonA         13 [16]       12       9       11       XIN       P12_0       AnonA       AnonA         14 [16]       13       10       12       VCC       AnonA       AnonA       AnonA         15 [17]       14       11       P11_7       (INT7)       TREO       AnonA       AnonA         16 [18]       15       12       P11_6       (INT4)       TRAIO       AnonA       AnonA         19 [21]       18       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 [4]   | 1      | 62   | 52   |       | P13_2          |                    |           | RXD0          |         |         | AN2            |                                 |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 [5]   | 2      | 63   | 1    |       | P13_1          |                    |           | TXD0          |         |         | AN1/DA1        |                                 |

| 618         5         2         4         VREP                                                                                                                    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4 [6]   | 3      | 64   | 2    |       | P13_0          |                    |           |               |         |         | AN0/DA0        |                                 |

| 7 [9]         6         3         5         MODE         Image: constraint of the second                             | 5 [7]   | 4      | 1    | 3    | WKUP0 |                |                    |           |               |         |         |                |                                 |

| 8 [10]         7         4         6         XCIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |        |      |      |       |                |                    |           |               |         |         |                |                                 |

| 9 [11]         8         5         7         XCOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |        |      |      |       |                |                    |           |               |         |         |                |                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |        |      |      |       |                |                    |           |               |         |         |                |                                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        |      |      |       |                |                    |           |               |         |         |                |                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |        |      |      |       | <b>D</b> ( a ( |                    |           |               |         |         |                |                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 [13] | 10     | 1    | 9    |       | P12_1          |                    |           |               |         |         |                |                                 |

| 14         16         12         VCC/<br>AVCC         VCC/<br>AVCC         VCC/<br>AVCC         VCC/<br>(INT7)         TRE0         Image: Constraint of the state of the                                            | 12 [14] | 11     | 8    | 10   |       |                |                    |           |               |         |         |                |                                 |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13 [15] | 12     | 9    | 11   |       | P12_0          |                    |           |               |         |         |                |                                 |

| 16 [18]         15         12         P11_6         (INT5)         TRB0         Image: Constraint of the state                                      | 14 [16] | 13     | 10   | 12   |       |                |                    |           |               |         |         |                |                                 |

| 17 [19]       16       13       P11_5       (INT5)       TRAO       Image: constraint of the state of                                               | 15 [17] | 14     | 11   |      |       | P11_7          | (INT7)             | TREO      |               |         |         | (ADTRG)        |                                 |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16 [18] | 15     | 12   |      |       | P11_6          | (INT6)             | TRBO      |               |         |         |                |                                 |

| 19 [21]         18         15         14         P11_3         (INT3)         (CTS2/RTS2)         SCS         IVCMP3           20 [22]         19         16         15         P11_2         (INT2)         (RXD2/SCL2/<br>TXD2/SDA2)         SSO         SDA         IVREF3           21 [23]         20         17         16         P11_1         (INT1)         (RXD2/SCL2/<br>TXD2/SDA2)         SSI         IVCMP1           22 [24]         21         18         17         P11_0         (INT0)         (CLK2)         SSK         SCL         IVREF1           23 [25]         2         P10_7         (KI6)         (TRDIOC1)         2         2         2         2         1         RXD2/SCL2/<br>TXD2/SDA2)         SSI         IVCMP1           24 [26]         2         P10_7         (KI7)         (TRDIOC1)         2         2         2         1         2         2         1         2         2         2         1         2         2         2         1         2         2         1         1         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2 <td>17 [19]</td> <td>16</td> <td>13</td> <td></td> <td></td> <td>P11_5</td> <td>(INT5)</td> <td>TRAO</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 [19] | 16     | 13   |      |       | P11_5          | (INT5)             | TRAO      |               |         |         |                |                                 |

| 20 [22]         19         16         15         P11_2         (iNTe)         (RXD2/SCL2/<br>TXD2/SDA2)         SSO         SDA         IVREF3           21 [23]         20         17         16         P11_1         (iNT1)         (RXD2/SCL2/<br>TXD2/SDA2)         SSI         IVREF3           22 [24]         21         18         17         P11_0         (iNT0)         (CLK2)         SSK         SCL         IVREF1           23 [25]         2         P10_7         (KI7)         (TRDIOD1)         2         2         2         SSC         SCL         IVREF1           24 [26]         2         P10_5         (KI5)         (TRDIOD1)         2         2         2         2         2         10         P10_5         (KI7)         100011         2         2         2         2         2         2         10         P10_5         (KI3)         100011         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 [20] | 17     | 14   | 13   |       | P11_4          | (INT4)             | TRAIO     | (RXD0)        |         |         |                |                                 |

| 20 [22]       19       16       15       P11_2       (INT2)       TXD2/SDA2       SS0       SDA       INREF3         21 [23]       20       17       16       P11_1       (INT1)       (RXD2/SCL2/<br>TXD2/SDA2)       SSI       IVCMP1         22 [24]       21       18       17       P10_0       (INT0)       (CLK2)       SSK       SCL       IVREF1         23 [25]       I       P10_7       (KI7)       (TRDIOD1)       Image: Similar Simila                                                                                                                                                                                                                                                                                                                                                          | 19 [21] | 18     | 15   | 14   |       | P11_3          | (INT3)             |           |               | SCS     |         | IVCMP3         |                                 |

| 21 [23]       20       17       16       P11_1       (INT1)       TXD2/SDA2)       SS1       IVCMP1         22 [24]       21       18       17       P11_0       (INT0)       (CLK2)       SSCK       SCL       IVREF1         23 [25]       2       2       P10_7       (Ki7)       (TRDIOD1)       2       2       2         24 [26]       2       P10_6       (Ki6)       (TRDIOC1)       2       2       2         25 [27]       2       P10_5       (Ki5)       (TRDIOB1)       2       2       2         26 [28]       2       P10_4       (Ki4)       (TRDIOA1)       2       2       2         27 [29]       2       P10_2       (Ki3)       (TRDIOA0)       2       2       2         28 [30]       2       P10_1       (Ki1)       (TRDIOB0)       2       2       2         30 [32]       2       P10_0       (Ki0)       (TRDIOA0/<br>TRDCLK)       2       2       2       2         31 [33]       22       19       18       P7_7       2       2       2       2         31 [33]       24       21       20       P7_5       2       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20 [22] | 19     | 16   | 15   |       | P11_2          | (INT2)             |           | TXD2/SDA2)    | SSO     | SDA     | IVREF3         |                                 |

| 23 [25]       Image: Constraint of the const | 21 [23] | 20     | 17   | 16   |       | P11_1          | (INT1)             |           |               | SSI     |         | IVCMP1         |                                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 [24] | 21     | 18   | 17   |       | P11_0          | (INT0)             |           | (CLK2)        | SSCK    | SCL     | IVREF1         |                                 |

| $25 [27]$ $1$ $P10_5$ $(\overline{KI5})$ $(TRDIOB1)$ $1$ $1$ $26 [28]$ $1$ $P10_4$ $(\overline{KI4})$ $(TRDIOA1)$ $1$ $1$ $27 [29]$ $1$ $P10_3$ $(\overline{KI3})$ $(TRDIOD0)$ $1$ $1$ $28 [30]$ $1$ $P10_2$ $(\overline{KI2})$ $(TRDIOC0)$ $1$ $1$ $29 [31]$ $1$ $P10_1$ $(\overline{KI1})$ $(TRDIOA0/TRDICK)$ $1$ $1$ $30 [32]$ $1$ $P10_0$ $(\overline{KI0})$ $(TRDIOA0/TRDICK)$ $1$ $1$ $31 [33]$ $22$ $19$ $18$ $P7_7$ $1$ $0$ $0$ $31 [33]$ $22$ $19$ $18$ $P7_7$ $0$ $0$ $0$ $31 [33]$ $22$ $19$ $P7_76$ $0$ $0$ $0$ $0$ $33 [35]$ $24$ $21$ $20$ $P7_75$ $0$ $0$ $0$ $34 [36]$ $25$ $22$ $21$ $P7_74$ $0$ $0$ $0$ $35 [37]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 [25] |        |      |      |       | P10_7          | ( <del>KI7</del> ) | (TRDIOD1) |               |         |         |                |                                 |

| 26 [28]       P10_4       (Ki3)       (TRDIOA1)       Image: constraint of the state of the st                            | 24 [26] |        |      |      |       | P10_6          | ( <del>Kl6</del> ) | (TRDIOC1) |               |         |         |                |                                 |

| 27 [29]       P10_3       (KI3)       (TRDIOD0)       P10_2         28 [30]       P10_2       (KI2)       (TRDIOC0)       P10_2         29 [31]       P10_1       (KI1)       (TRDIOB0)       P10_3         30 [32]       P10_0       (KI0)       (TRDIOA0/<br>TRDIOA0/<br>TRDICLK)       P10_0       COM         31 [33]       22       19       18       P7_7       COM       COM         32 [34]       23       20       19       P7_6       COM       COM         33 [35]       24       21       20       P7_5       COM       COM         34 [36]       25       22       21       P7_4       COM       SEG       SEG         35 [37]       26       23       P7_3       SEG       SEG       SEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25 [27] |        |      |      |       | P10_5          | ( <del>KI5</del> ) | (TRDIOB1) |               |         |         |                |                                 |

| 28 [30]       P10_2       (Ki2)       (TRDIOCO)       P10_2         29 [31]       P10_1       (KI1)       (TRDIOBO)       P10_3         30 [32]       P10_0       (KI0)       (TRDIOAO/<br>TRDIOAO/<br>TRDICLK)       P10_0       (COM<br>TRDICAO/<br>TRDICLK)         31 [33]       22       19       18       P7_7       COM       COM         32 [34]       23       20       19       P7_6       COM       COM         33 [35]       24       21       20       P7_5       COM       COM         34 [36]       25       22       21       P7_4       COM       COM         35 [37]       26       23       P7_3       SEG       SEG       SEG         26 [38]       27       24       P7_2       P7_3       SEG       SEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 [28] |        |      |      |       | P10_4          | ( <del>KI4</del> ) | (TRDIOA1) |               |         |         |                |                                 |

| 29 [31]       P10_1       (KI)       (TRDIOB0)       P10_1         30 [32]       P10_0       (KI)       (TRDIOA0/<br>TRDCLK)       COM         31 [33]       22       19       18       P7_7       COM         32 [34]       23       20       19       P7_6       COM         33 [35]       24       21       20       P7_5       COM         34 [36]       25       22       21       P7_4       COM         35 [37]       26       23       P7_3       SEG       SEG         36 [38]       27       24       P7_2       SEG       SEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27 [29] |        |      |      |       | P10_3          | (KI3)              | (TRDIOD0) |               |         |         |                |                                 |

| 30 [32]       P10_0       (KI0)       (TRDIOA0/<br>TRDCLK)       COM         31 [33]       22       19       18       P7_7       COM         32 [34]       23       20       19       P7_6       COM         33 [35]       24       21       20       P7_5       COM         34 [36]       25       22       21       P7_4       COM         35 [37]       26       23       P7_3       SEG       COM         36 [38]       27       24       P7_2       P7_3       SEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 [30] |        |      |      |       | P10_2          | (KI2)              | (TRDIOC0) |               |         |         |                |                                 |

| 30 [32]       -       -       P10_0       (Kl0)       TRDCLK)       -       -       COM         31 [33]       22       19       18       P7_7       -       -       COM         32 [34]       23       20       19       P7_6       -       -       COM         33 [35]       24       21       20       P7_5       -       COM         34 [36]       25       22       21       P7_4       -       COM         35 [37]       26       23       P7_3       -       SEG       COM         36 [38]       27       24       P7_2       P7_3       SEG       SEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29 [31] |        |      |      |       | P10_1          | (KI1)              |           |               |         |         |                |                                 |