Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

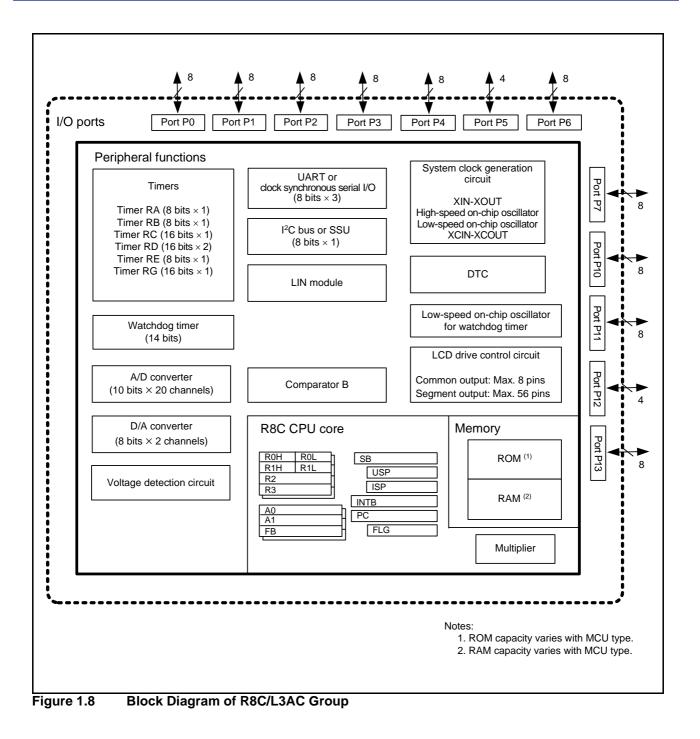

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LCD, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 88                                                                               |

| Program Memory Size        | 48KB (48K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 6K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 20x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

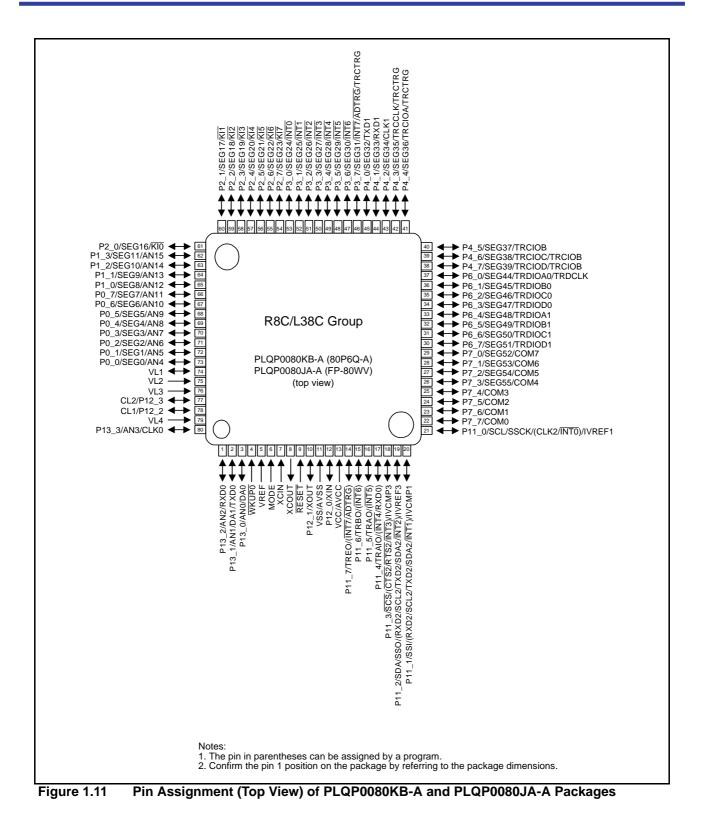

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f2l3a7cnfp-30 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                          | Specification                                                                    |

|-------------------------------|----------------------------------------------------------------------------------|

| Flash Memory                  | <ul> <li>Programming and erasure voltage: VCC = 2.7 to 5.5 V</li> </ul>          |

|                               | <ul> <li>Programming and erasure endurance: 10,000 times (data flash)</li> </ul> |

|                               | 1,000 times (program ROM)                                                        |

|                               | <ul> <li>Program security: ROM code protect, ID code check</li> </ul>            |

|                               | On-chip debug function                                                           |

|                               | On-board flash rewrite function                                                  |

|                               | <ul> <li>Background operation (BGO) function</li> </ul>                          |

| Operating Frequency/          | f(XIN) = 20 MHz (VCC = 2.7 to 5.5 V)                                             |

| Supply Voltage                | f(XIN) = 5 MHz (VCC = 1.8 to 5.5 V)                                              |

| Current Consumption           | Typ. 7 mA (VCC = 5.0 V, f(XIN) = 20 MHz)                                         |

|                               | Typ. 3.6 mA (VCC = 3.0 V, f(XIN) = 10 MHz)                                       |

|                               | Typ. 3.5 μA (VCC = 3.0 V, wait mode (f(XCIN) = 32 kHz))                          |

|                               | Typ. 2 µA (VCC = 3.0 V, stop mode)                                               |

|                               | Typ. 0.02 $\mu$ A (VCC = 3.0 V, power-off mode)                                  |

| Operating Ambient Temperature | -20 to 85°C (N version)                                                          |

|                               | -40 to 85°C (D version) <sup>(1)</sup>                                           |

**Specifications (3)** Table 1.6

Note: 1. Specify the D version if D version functions are to be used.

| LSAC         Desc         LSAC         Pin         Port         Interrupt         Timer         Serial<br>Interace         SSU         Pic<br>Us         Diversity         Control<br>Comparisor B         Control B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P        | in Nun | nber |      |          |          | İ           | I/O     | Pin Functions | for Per | ipheral | Modules             |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|------|----------|----------|-------------|---------|---------------|---------|---------|---------------------|-----------|

| (Note 2)         Image         Image         Image         Image         Image         SSD         Low         Controverted,<br>Comparator B         Controverted,<br>Comparator B         Controverted,<br>Comparator B         Controverted,<br>SEG49           40 (42)         31         -         P6.6         TRDIOCI         -         -         BE         SEG49           42 (44)         33         -         P6.6         TRDIOCI         -         -         SEG47           42 (44)         3         -         P6.2         TRDIOCI         -         -         SEG47           42 (44)         3         -         P6.2         TRDIOCIO         -         -         SEG47           44 (48)         37         -         -         P6.2         TRDIOCIO         -         -         SEG47           45 (14)         3         -         -         P6.2         TRCIOCIO         -         -         SEG47           16 (15)         -         P6.7         TRCIOCIO         -         -         SEG47           17 (2016)         18         38         27         24         P4.4         TRCIOCIO         -         -         -         SEG39           515 (51)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 1      | 1    | 1050 | Control  | Dent     |             |         |               | 1       |         |                     | LCD drive |

| Image: Constraint of the second of |          | L380   | L36C | L35C | Pin      | Pon      | Interrupt   | Timer   |               | SSU     |         | D/A Converter,      | control   |

| 4143         32         b         PR5.5         TRDOB1         b         b         SEG48           4343         34         -         PR5.3         TRDOON         -         -         SEG48           43461         35         -         PR5.3         TRDOON         -         SEG46           41461         35         -         PR5.1         TRDOKO         -         SEG46           41697         36         -         PR5.2         TRDOKO         -         SEG46           46(48)         37         -         PS5.2         -         -         SEG41           47(49)         -         PS5.2         -         -         -         SEG43           48(50)         -         PS5.2         -         -         -         SEG43           51(51         -         PS5.2         -         -         -         SEG39           51(51         41         30         25         P4.4         TRCIOD/<br>TRCIOB         -         -         SEG36           51(51         41         30         25         P4.4         TRCIOK/<br>TRCIAG         -         SEG37           54(58)         43         32 <t< td=""><td>(Note 2)</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>interface</td><td></td><td>bus</td><td>Comparator B</td><td>circuit</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (Note 2) |        |      |      |          |          |             |         | interface     |         | bus     | Comparator B        | circuit   |

| 42 [44]         33         b         PE6.4         TRDIOAL         D         D         SEGAF           44 [46]         35         -         PE6.2         TRDIODO         -         -         SEGAF           44 [46]         35         -         PE6.1         TRDIOAD         -         D         SEGAF           46 [46]         37         -         -         PE6.1         TRDIOAD         -         D         SEGAF           47 [40]         -         -         PE5.1         -         PE5.2         -         -         SEGAF           48 [50]         -         -         P5.1         -         -         SEGAF           49 [51]         -         -         P5.1         -         -         SEGAF           51 [51]         38         27         22         P4.7         TRCIOB         -         D         SEGAF           51 [51]         39         28         23         P4.6         TRCIOB         -         D         SEGAF           51 [51]         30         22         P4.4         TRCIOB         -         D         SEGAF           51 [51]         41         30         25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 31     |      |      |          |          |             |         |               |         |         |                     |           |

| 43 (46)         34          P6.3         TRDOOD           SEG47           44 (46)         35          P6_1         TRDOK0          SEG45           45 (47)         36          P6_1         TRDOK0          SEG45           46 (43)           P6_0         TRDOK0          SEG47           47 (43)           P6_5           SEG47           47 (43)           P6_0         TRDOK0          SEG47           51 (51)           P6_0         TRCIOC/          SEG47           51 (51)           P6_0         TRCIOC/           SEG39           52 (54)         39         28         23         P4_6         TRCIOC/           SEG36           53 (55)         41         30         25         P4_3         TRCIOR/           SEG36           56 (53)         43         32         27         P4_2         TRCIOR/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 32     |      |      |          |          |             |         |               |         |         |                     |           |

| 44 461         35         P6.2         TRD/OC0         P6.2         TRD/OC0         P6.2         TRD/OR0         SEC46           46 (48)         37         P6.1         TRD/OR0         P6.1         TRD/OR0         SEC43           47 (40)         P6.2         P6.3         P6.1         TRD/OR0         P6.2         SEC43           48 (50)         P6.2         P5.3         P5.2         P6.1         P6.2         P5.2         P6.2         P6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| Image: state of the state         |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 46 [48]         37         Pe.0         TRDOAN<br>TRDCA         Pe.0         SEG44           47 [49]         Pe.3         Pe.3         Pe.3         Pe.3         Pe.4         SEG43           48 [50]         Pe.7         Pe.7         Pe.7         SEG43         SEG43           50 [52]         Pe.7         Pe.7         TRCIOB         SEG43         SEG43           51 [53]         38         27         22         Pe.7         TRCIOB         SEG39           52 [54]         39         28         23         Pe.4.5         TRCIOB         SEG39           53 [55]         42         31         26         Pe.4.4         TRCIOC/<br>TRCIOB         SEG34         SEG35           54 [56]         41         30         25         Pe.4.4         TRCICK/<br>TRCICK         SEG34         SEG35           57 [57]         42         31         26         Pe.3.0         TRCTKG         SEG35           58 [60]         45         34         29         Pe.0         TRCTKG         SEG32           58 [61]         43         32         P3.7         INT7         TRCTKG         ADTRG           59 [61]         43         38         P3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 46         46         47         40         4         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40         40 </td <td>45 [47]</td> <td>36</td> <td></td> <td></td> <td></td> <td>P6_1</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>SEG45</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 [47]  | 36     |      |      |          | P6_1     |             |         |               |         |         |                     | SEG45     |

| Hat [G0]       L       L       PP5_2       L       L       PS24       L       SEG41         49 [51]       L       PS_0       L       PS_0       L       SEG41         51 [53]       38       27       22       P4_7       TRCIOD/<br>TRCIOB       SEG39         52 [54]       39       28       23       P4_6       TRCIOD/<br>TRCIOB       L       SEG39         53 [55]       40       29       24       P4_5       TRCIOB       L       SEG39         54 [56]       41       30       25       P4_4       TRCIRG       L       SEG36         56 [57]       42       31       26       P4_3       TRCIRG       L       SEG36         56 [58]       43       32       27       P4_2       CLK1       SEG33       SEG34         57 [59]       44       33       28       P4_1       RXD1       SEG33       SEG33         58 [60]       45       34       29       P4_0       RXD1       SEG34       SEG34         60 [61]       46       35       P3_6       INT6       ADTRG       SEG34         60 [62]       47       36       P3_6       INT6 <td< td=""><td></td><td>37</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 37     |      |      |          |          |             |         |               |         |         |                     |           |

| 49 (51)       -       -       P5_1       -       P5_0       -       SEG41         50 [52]       -       -       P4_0       TRCIOD/<br>TRCIOB       -       SEG39         51 [53]       38       27       22       P4_6       TRCIOD/<br>TRCIOB       -       SEG39         52 [54]       39       28       23       P4_6       TRCIOC/<br>TRCIOB       -       SEG37         54 [56]       41       30       25       P4_4       TRCIOA/<br>TRCIAG       SEG36       SEG36         55 [57]       42       31       26       P4_3       TRCICAK<br>TRCIAG       SEG36       SEG36         57 [59]       44       33       28       P4_1       RXD1       SEG33       SEG33         58 [60]       45       34       29       P4_0       TRCIAG       XDTRG       SEG31         59 [61]       46       35       P3_7       INT7       TRCTRG       XDTRG       SEG39         61 [63]       48       37       P3_6       INT6       SEG39       SEG39       SEG39         61 [64]       51       40       31       P3_2       INT7       CLK1       SEG32         62 [64]       49       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 50 [52]         D         P5_0         TRCIDD         TRCIDD         SEG40           51 [53]         38         27         22         P4_7         TRCIDB         SEG39           52 [54]         39         28         23         P4_6         TRCIDB         SEG39           53 [55]         40         29         24         P4_5         TRCIDB         SEG37           54 [56]         41         30         25         P4_4         TRCIDM         SEG36           55 [57]         42         31         26         P4_3         TRCIDK         SEG34           56 [58]         43         32         27         P4_2         CLK1         SEG34           57 [59]         44         33         28         P4_1         RXD1         SEG34           59 [61]         46         35         P3_7         INT7         TRCTRG         MADRG         SEG31           60 [62]         47         36         P3_6         INT6         NADRG         SEG36           61 [63]         48         37         Image: P3_4         INT4         Image: P3_4         Image: P3_4           65 [7]         52         41         32         P3_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 51         38         27         22         P4_7         TRCIOD<br>TRCIOB         SEG39           52         54         39         28         23         P4_6         TRCIOB         SEG38           53         54         60         29         24         P4_6         TRCIOB         SEG37           54         56         41         30         25         P4_4         TRCIOR<br>TRCIAG         SEG37           54         55         77         42         31         26         P4_3         TRCIAG         SEG36           55         577         42         31         26         P4_2         CLK1         SEG35           58         60         45         34         29         P4_0         TXD1         SEG32           59         61         46         35         P3_7         INT7         TRCTRG         XD1         SEG32           60         62         47         36         P3_6         INT6         ZD1         SEG32           61         63         48         37         P3_5         INT5         ZD1         SEG32           61         61         31         P3_2         INT2         ZD1 <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 51       38       27       22       P4_6       TRCIOB       C       SE339         52       40       29       24       P4_6       TRCIOB       C       SE339         54       56       41       30       25       P4_4       TRCIOB       C       SE339         54       56       41       30       25       P4_4       TRCIOB       C       SE339         55       57       42       31       26       P4_4       TRCIOB       C       SE339         56       56       33       32       27       P4_2       CLK1       SE334         57       57       44       33       28       P4_1       RXCING       SE334         59       61       46       35       P3_7       INT7       TRCTRG       M       ADTRG       SE33         60       62       47       36       P3_7       INT6       RCTRG       M       ADTRG       SE33         61631       48       37       C       P3_6       INT6       C       ADTRG       SE33         61631       49       38       C       P3_1       INT4       C       C       SE33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 [52]  |        |      |      |          | P5_0     |             | TRAIAR  |               |         |         |                     | SEG40     |

| b2 (sh)         33         28         23         P4_5         TRCIOB         Composition         SEG37           53 (s6)         40         29         24         P4_5         TRCIOB         Composition         SEG37           54 (s6)         41         30         25         P4_4         TRCIOM         Composition         SEG36           55 (s7)         42         31         26         P4_2         TRCTRG         CLK1         SEG33           65 (s1)         43         32         27         P4_2         CLK1         SEG33           58 (s0)         45         34         29         P4_0         TRCTRG         RXD1         SEG33           59 (s1)         46         35         C         P3_7         INT7         TRCTRG         ADTRG         SEG31           60 (s2)         47         36         C         P3_6         INT6         C         ADTRG         SEG31           61 (s1)         48         37         C         P3_5         INT5         C         C         ADTRG         SEG32           62 (s4)         49         38         C         P3_4         INT4         C         C         SEG22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 [53]  | 38     | 27   | 22   |          | P4_7     |             | TRCIOB  |               |         |         |                     | SEG39     |

| 53 [56]       40       29       24       P4_5       TRCIOB       Image: Constraint of the                                                              | 52 [54]  | 39     | 28   | 23   |          | P4_6     |             |         |               |         |         |                     | SEG38     |

| 54 [56]         41         30         25         P4_4         TRCION<br>TRCING         M         SEG36           55 [57]         42         31         26         P4_3         TRCCLK/<br>TRCTRG          SEG35           56 [58]         43         32         27         P4_2          CLK1         SEG34           57 [59]         44         33         28         P4_1         RD1         SEG33           58 [60]         45         34         29         P4.0         TXD1         SEG33           59 [61]         46         35         P3_7         INT7         TRCTRG         ADTRG         SEG31           60 [62]         47         36         P3_7         INT5         ADTRG         SEG30           61 [63]         48         37         P3_5         INT5         ADTRG         SEG28           63 [65]         50         39         30         P3_3         INT3         ADTRG         SEG28           63 [65]         50         39         30         P3_3         INT3         ADTRG         SEG26           66 [68]         54         43         34         P2_7         Ki7         ADTRG         SEG21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53 [55]  | 40     | 29   | 24   |          | P4_5     |             |         |               |         |         | 1                   | SEG37     |

| 55 [57]       42       31       26       P4_3       TRCLK/<br>TRCTRG       CLK1       SEG34         56 [58]       43       32       27       P4_2       CLK1       SEG34         57 [59]       44       33       28       P4_1       RD1       SEG33         58 [60]       45       34       29       P4_0       TXD1       SEG33         58 [61]       46       35       P3_7       INT7       TRCTRG       ADTRG       SEG31         60 [62]       47       36       P3_6       INT6       ADTRG       SEG31         61 [63]       48       37       P3_5       INT5       A       ADTRG       SEG32         62 [64]       49       38       P3_4       INT4       A       A       SEG26         63 [65]       50       39       30       P3_3       INT3       A       SEG26         64 [66]       51       40       31       P3_2       INT2       A       A       SEG26         65 [67]       52       41       32       P3_1       INT7       A       A       SEG26         66 [68]       53       42       33       P2_6       Ki6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 41     | 30   | 25   |          |          |             | TRCIOA/ |               |         |         |                     | SEG36     |

| 66 [58]       43       32       27       P4_2       CLK1       SEG34 $57$ [59]       44       33       28       P4_1       RXD1       SEG33         58 [60]       45       34       29       P4_0       TXD1       SEG33         59 [61]       46       35       P3_7       INT7       TRCTRG       IXD1       SEG32         59 [61]       46       35       P3_6       INT6       IXD1       SEG33         60 [62]       47       36       P3_6       INT6       IXD1       SEG33         61 [63]       48       37       P3_5       INT5       IXD1       SEG29         62 [64]       49       38       P3_4       INT4       IXD1       SEG26         63 [65]       50       39       30       P3_3       INT3       IXD1       SEG26         64 [66]       51       40       31       P3_2       INT2       IXD1       SEG26         65 [67]       52       41       32       P3_1       INT1       IXD1       SEG22         66 [68]       53       42       33       P2_7       Ki7       IXD       SEG20         67 [69]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 [57]  | 42     | 31   | 26   | <u> </u> | P4_3     |             | TRCCLK/ |               |         |         |                     | SEG35     |

| 57 [59]       44       33       28 $P4_{-1}^{-1}$ RXD1       SEG33         58 [60]       45       34       29 $P4_{-0}^{-1}$ TXCTRG       ADTRG       SEG32         59 [61]       46       35       P3_6       INT7       TRCTRG       INT6       SEG30         60 [62]       47       36       P3_6       INT6       SEG30       SEG30         61 [63]       48       37       P3_6       INT6       SEG30       SEG30         62 [64]       49       38       P3_3       INT3       SEG20       SEG27         62 [64]       51       40       31       P3_2       INT4       SEG26       SEG27         64 [66]       51       40       31       P3_2       INT3       SEG26       SEG26         66 [67]       52       41       32       P3_1       INT1       SEG26       SEG24         67 [69]       54       43       34       P2_7       Ki7       SEG27       SEG29         68 [70]       55       44       35       P2_6       Ki6       SEG27       SEG27         70 [72]       57       46       37       P2_2       Ki2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56 [58]  | 43     | 32   | 27   |          | P4_2     |             |         | CLK1          |         |         |                     | SEG34     |

| 58 [60]         45         34         29         P4_0         TXD1         SEG32           59 [61]         46         35         P3_7         INT7         TRCTRG         INT6         INT6         SEG31           60 [62]         47         36         P3_6         INT6         INT6         SEG30           61 [63]         48         37         P3_5         INT5         INT6         SEG29           62 [64]         49         38         P3_4         INT6         INT6         SEG29           63 [65]         50         39         30         P3_3         INT3         INT6         INT6         SEG27           64 [66]         51         40         31         P3_2         INT2         INT6         SEG26           65 [67]         52         41         32         P3_1         INT6         SEG26           66 [68]         53         42         33         P3_0         INT6         SEG23           66 [70]         55         44         35         P2_6         Kif6         SEG20           69 [71]         56         45         36         P2_2.6         Kif6         SEG20         SEG20           <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 59 [61]       46       35       P3_7       INT7       TRCTRG       ADTRG       SEG31         60 [62]       47       36       P3_6       INT6        SEG30       SEG30         61 [63]       48       37       P3_5       INT6        SEG30       SEG30         62 [64]       49       38       P3_4       INT4        SEG28       SEG28         63 [65]       50       39       30       P3_3       INT3        SEG27         64 [66]       51       40       31       P3_2       INT2        SEG26         65 [67]       52       41       32       P3_1       INT1         SEG25         66 [68]       53       42       33       P3_0       INT0        SEG23         68 [70]       55       44       35       P2_6       Ki6        SEG20         70 [72]       57       46       37       P2_4       Ki4         SEG30         71 [73]       58        P2_2       Ki2        SEG40       SEG41         71 [73]       58        P2_2,0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 45     | 34   |      |          | P4_0     |             |         | TXD1          |         |         |                     |           |

| 61 [63]       48       37       Image: constraint of the second secon                                    |          | 46     | 35   |      |          |          | INT7        | TRCTRG  |               |         |         | ADTRG               |           |

| 61 [63]       48       37       L       P3_5 $\overline{INT5}$ L       L       SEG29         62 [64]       49       38       P3_4 $\overline{INT4}$ L       L       SEG28         63 [65]       50       39       30       P3_3 $\overline{INT3}$ L       L       SEG27         64 [66]       51       40       31       P3_2 $\overline{INT2}$ L       L       SEG26         65 [67]       52       41       32       P3_1 $\overline{INT1}$ L       L       SEG26         66 [68]       53       42       33       P3_0 $\overline{INT0}$ L       L       SEG26         66 [69]       54       43       34       P2_7 $\overline{Ki7}$ L       L       SEG26         66 [69]       54       43       34       P2_7 $\overline{Ki7}$ L       L       SEG27         68 [70]       55       44       35       P2_6 $\overline{Ki6}$ L       L       SEG29         69 [71]       56       45       36       P2_5 $\overline{Ki5}$ L       L       SEG29         71 [73]       58       Z       2       P2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 [62]  | 47     | 36   |      |          | P3_6     | INT6        |         |               |         |         |                     | SEG30     |

| 63 [65]       50       39       30       P3_3 $\overline{INT3}$ Image: Market Ma                                                                   | 61 [63]  | 48     | 37   |      |          | P3_5     |             |         |               |         |         |                     | SEG29     |

| 64 [66]       51       40       31 $P3_2$ $\overline{INT2}$ $INT2$ $INT0$ $IINT0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62 [64]  | 49     | 38   |      |          | P3_4     | INT4        |         |               |         |         |                     | SEG28     |

| 65 [67]       52       41       32       P3_1       INT1       Image: constraint of the second seco                                                              | 63 [65]  | 50     | 39   | 30   |          | P3_3     | INT3        |         |               |         |         |                     |           |

| 66 [68]       53       42       33       P3_0       INTO       INTO       SEG24         67 [69]       54       43       34       P2_7       KI7       INTO       SEG23         68 [70]       55       44       35       P2_6       KI6       Into       SEG22         69 [71]       56       45       36       P2_5       KI5       Into       Into       SEG21         70 [72]       57       46       37       P2_4       KI4       Into       Into       SEG20         71 [73]       58       Into       P2_3       KI3       Into       Into       SEG10         72 [74]       59       Into       P2_2       KI2       Into       Into       SEG18         73 [75]       60       Into       P2_0       KI0       Into       Into       SEG18         74 [76]       61       Into       P1_6       Into       Into       SEG18         76 [77]       Into       P1_6       Into       Into       SEG18         76 [78]       Into       P1_6       Into       Into       SEG13         78 [80]       Into       P1_4       Into       Into       Into                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64 [66]  | 51     | 40   | 31   |          | P3_2     | INT2        |         |               |         |         |                     | SEG26     |

| $67$ [69]544334 $P2_{-7}$ $\overline{K17}$ $\overline{K10}$ $K1$                                      |          | 52     | 41   | 32   |          |          | INT1        |         |               |         |         |                     |           |

| 68 [70]       55       44       35       P2_6       Kin       Kin       Kin       Kin       Kin         69 [71]       56       45       36       P2_5       Kis       Kis       SEG21         70 [72]       57       46       37       P2_4       Kis       Kis       SEG20         71 [73]       58       Image: Constraint of the second se                                                                                                                                                                                                                                                                                                                       |          | 53     | 42   | 33   |          |          | <b>INTO</b> |         |               |         |         |                     |           |

| 69 [71]       56       45       36       P2_5       KI5       Image: constraint of the second secon                                                              |          |        |      |      |          |          | KI7         |         |               |         |         |                     |           |

| 70 [72]       57       46       37       P2_4       Kla       All       SEG20         71 [73]       58       Image: Constraint of the stress of                                                                                                                    |          | 55     |      |      |          |          | KI6         |         |               |         |         |                     |           |

| 71 [73]       58       P2_3       KI3       SEG19         72 [74]       59       P2_2       KI2       SEG18         73 [75]       60       P2_1       KI1       SEG17         74 [76]       61       P2_0       KI0       SEG16         75 [77]       P2_0       KI0       SEG16         75 [77]       P1_7       SEG16       SEG14         77 [79]       P1_6       SEG12         78 [80]       P1_4       SEG1         80 [82]       63       P1_1         81 [83]       64       P1_0         91_0       P1_0       AN13         82 [84]       65       P1_07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| $72 [74]$ $59$ $P2_2$ $\overline{Kl2}$ $Rectar Rectar Rect$                                                            |          |        | 46   | 37   |          | _        |             |         |               |         |         |                     |           |

| $73 [75]$ $60$ $P2_{-1}$ $\overline{Kl1}$ SEG17 $74 [76]$ $61$ $P2_{-0}$ $\overline{Kl0}$ SEG16 $75 [77]$ $P1_{-7}$ $P1_{-7}$ SEG16 $76 [78]$ $P1_{-6}$ $P1_{-6}$ $SEG14$ $77 [79]$ $P1_{-5}$ $P1_{-6}$ $SEG13$ $78 [80]$ $P1_{-4}$ $SEG12$ $SEG12$ $79 [81]$ $62$ $P1_{-13}$ $AN15$ $SEG11$ $80 [82]$ $63$ $P1_{-1}$ $AN14$ $SEG10$ $81 [83]$ $64$ $P1_{-1}$ $AN13$ $SEG9$ $82 [84]$ $65$ $P1_{-0}$ $AN11$ $AN11$ $SEG1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 74 [76]       61       P2_0       KI0       SEG16         75 [77]       P1_7       SEG15         76 [78]       P1_6       SEG14         77 [79]       P1_5       SEG13         78 [80]       P1_4       SEG12         79 [81]       62       P1_2       AN15         80 [82]       63       P1_2       AN14         81 [83]       64       P1_0       AN12         83 [85]       66       47       38       P0_7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 75 [77]       P1_7       SEG15         76 [78]       P1_6       SEG14         77 [79]       P1_5       SEG13         78 [80]       P1_4       SEG12         79 [81]       62       P1_3       AN15         80 [82]       63       P1_1       AN14         81 [83]       64       P1_0       AN13         82 [84]       65       P1_0       AN11 (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |        |      |      |          |          |             |         |               |         |         |                     |           |

| 76 [78]       P1_6       SEG14         77 [79]       P1_5       SEG13         78 [80]       P1_4       SEG12         79 [81]       62       P1_3       AN15         80 [82]       63       P1_2       AN14         81 [83]       64       P1_0       AN13         82 [84]       65       P1_0       AN12         83 [85]       66       47       38       P0_7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 61     |      |      |          |          | KI0         |         |               |         |         |                     |           |

| 77 [79]         P1_5         SEG13           78 [80]         P1_4         SEG12           79 [81]         62         P1_3         AN15         SEG11           80 [82]         63         P1_2         AN14         SEG10           81 [83]         64         P1_1         AN13         SEG9           82 [84]         65         P1_0         AN12         SEG8           83 [85]         66         47         38         P0_7         AN11 (3)         SEG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |        |      |      |          | _        |             |         |               |         |         |                     |           |

| 78 [80]         P1_4         SEG12           79 [81]         62         P1_3         AN15         SEG11           80 [82]         63         P1_2         AN14         SEG10           81 [83]         64         P1_1         AN13         SEG9           82 [84]         65         P1_0         AN12         SEG8           83 [85]         66         47         38         P0_7         AN11 (3)         SEG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |        |      |      |          | _        |             |         |               |         |         |                     |           |

| 79 [81]         62         P1_3         AN15         SEG11           80 [82]         63         P1_2         AN14         SEG10           81 [83]         64         P1_1         AN13         SEG9           82 [84]         65         P1_0         AN12         SEG8           83 [85]         66         47         38         P0_7         AN11 (3)         SEG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |        |      |      |          | _        |             |         |               |         |         |                     |           |

| 80 [82]         63         P1_2         AN14         SEG10           81 [83]         64         P1_1         AN13         SEG9           82 [84]         65         P1_0         AN12         SEG8           83 [85]         66         47         38         P0_7         AN11 (3)         SEG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 62     |      |      |          | _        |             |         |               | +       |         | AN15                |           |