Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 75MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | DMA, WDT                                                             |

| Number of I/O              | 40                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-LQFP                                                              |

| Supplier Device Package    | 48-LQFP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv10z32vlf7 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol           | Description                                                               | Min.                  | Max.                   | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|------------------------|------|

| V <sub>DD</sub>  | Digital supply voltage                                                    | -0.3                  | 3.8                    | V    |

| I <sub>DD</sub>  | Digital supply current                                                    | —                     | 120                    | mA   |

| V <sub>IO</sub>  | Digital pin input voltage (except open drain pins)                        | -0.3                  | VDD + 0.3 <sup>1</sup> | V    |

|                  | Open drain pins (PTC6 and PTC7)                                           | -0.3                  | 5.5                    | V    |

| Ι <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                     | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3  | V    |

1. Maximum value of  $V_{\text{IO}}$  (except open drain pins) must be 3.8 V.

# 2 General

Electromagnetic compatibility (EMC) performance depends on the environment in which the MCU resides. Board design and layout, circuit topology choices, location, characteristics of external components, and MCU software operation play a significant role in EMC performance.

See the following applications notes available on freescale.com for guidelines on optimizing EMC performance.

- AN2321: Designing for Board Level Electromagnetic Compatibility

- AN1050: Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

- AN1263: Designing for Electromagnetic Compatibility with Single-Chip Microcontrollers

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

# 2.1 AC electrical characteristics

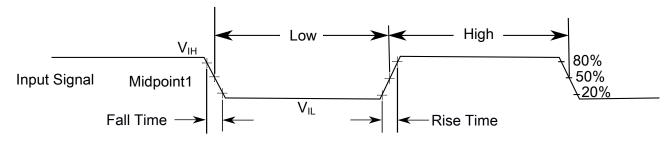

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  + ( $V_{IH}$  -  $V_{IL}$ ) / 2

### Figure 2. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume:

- 1. output pins

- have  $C_L=30$  pF loads,

- are slew rate disabled, and

- are normal drive strength

# 2.2 Nonswitching electrical specifications

### 2.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol             | Description                                                                               | Min.                 | Max.                 | Unit | Notes |

|--------------------|-------------------------------------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                                                            | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>   | Analog supply voltage                                                                     | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$ | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                 | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                 | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>    | Input high voltage                                                                        |                      |                      |      |       |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                              | $0.7 \times V_{DD}$  | —                    | V    |       |

|                    | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                             | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>    | Input low voltage                                                                         |                      |                      |      |       |

|                    | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                               | _                    | $0.35 \times V_{DD}$ | V    |       |

|                    | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                             | -                    | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>   | Input hysteresis                                                                          | $0.06 \times V_{DD}$ |                      | V    |       |

| I <sub>ICIO</sub>  | Pin negative DC injection current—single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> –0.3V | -5                   | _                    | mA   | 1     |

| Symbol              | Description                                                                                                                                                                                       | Min. | Max. | Unit | Notes |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>ICcont</sub> | Contiguous pin DC injection current—regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins<br>• Negative current injection | -25  | _    | mA   |       |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                    | 1.2  | _    | V    |       |

### Table 1. Voltage and current operating requirements (continued)

1. All I/O pins are internally clamped to  $V_{SS}$  through an ESD protection diode. There is no diode connection to  $V_{DD}$ . If  $V_{IN}$  greater than  $V_{IO\_MIN}$  (=  $V_{SS}$ -0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed, then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R = ( $V_{IO\_MIN} - V_{IN}$ )/ $I_{ICIO}$ .

### 2.2.2 LVD and POR operating requirements Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>   | Falling V <sub>DD</sub> POR detect voltage                  | 0.8  | 1.1  | 1.5  | V    |       |

| V <sub>LVDH</sub>  | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| $V_{LVW1H}$        | <ul> <li>Level 1 falling (LVWV=00)</li> </ul>               | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV=10)</li> </ul>               | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range   | _    | ±60  | _    | mV   |       |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    |       |

|                    | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| $V_{LVW1L}$        | Level 1 falling (LVWV=00)                                   | 1.74 | 1.80 | 1.86 | V    |       |

| V <sub>LVW2L</sub> | Level 2 falling (LVWV=01)                                   | 1.84 | 1.90 | 1.96 | V    |       |

| V <sub>LVW3L</sub> | <ul> <li>Level 3 falling (LVWV=10)</li> </ul>               | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$        | Level 4 falling (LVWV=11)                                   | 2.04 | 2.10 | 2.16 | V    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range    | -    | ±40  | -    | mV   |       |

| $V_{BG}$           | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   |       |

1. Rising thresholds are falling threshold + hysteresis voltage

8

| Symbol               | Description                                                                          | Min. | Тур.       | Max.       | Unit | Notes                                         |

|----------------------|--------------------------------------------------------------------------------------|------|------------|------------|------|-----------------------------------------------|

|                      | • at 3.0 V 50 MHz (25 MHz Bus)                                                       | —    | 5          | 6.3        | mA   |                                               |

|                      | • at 1.8 V 75 MHz (25 MHz Bus)                                                       | _    | 6.5        | 7.8        | mA   |                                               |

|                      | • at 3.0 V 75 MHz (25 MHz Bus)                                                       | —    | 6.5        | 7.5        | mA   |                                               |

| I <sub>DD_RUN</sub>  | Run mode current — all peripheral clocks enabled, code executing from flash          |      |            |            |      | Target IDD                                    |

|                      | • at 1.8 V 50 MHz                                                                    | _    | 7.1        | 8.2        | mA   |                                               |

|                      | • at 3.0 V 50 MHz                                                                    | _    | 7.1        | 8          | mA   |                                               |

|                      | • at 1.8 V 75 MHz                                                                    | _    | 9.4        | 10.9       | mA   |                                               |

|                      | • at 3.0 V 75 MHz                                                                    | _    | 9.4        | 10.6       | mA   |                                               |

| I <sub>DD_WAIT</sub> | Wait mode high frequency 75 MHz current at 3.0 V — all peripheral clocks disabled    |      | 4          | 5.2        | mA   | -                                             |

| I <sub>DD_WAIT</sub> | Wait mode reduced frequency 50 MHz current at 3.0 V — all peripheral clocks disabled | _    | 3.4        | 4.7        | mA   | _                                             |

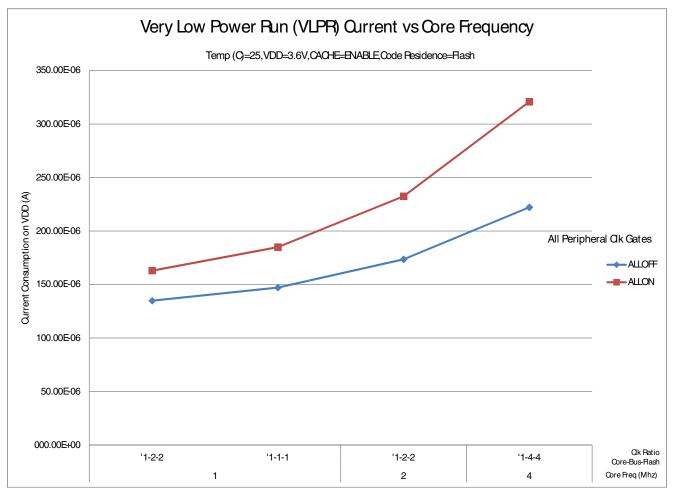

| I <sub>DD_VLPR</sub> | Very-Low-Power Run mode current 4 MHz at 3.0 V — all peripheral clocks disabled      | _    | 215        | 437        | μA   | 4 MHz<br>CPU<br>speed, 1<br>MHz bus<br>speed. |

| DD_VLPR              | Very-Low-Power Run mode current 4 MHz at 3.0 V — all peripheral clocks enabled       | _    | 313        | 570        | μA   | 4 MHz<br>CPU<br>speed, 1<br>MHz bus<br>speed. |

| DD_VLPW              | Very-Low-Power Wait mode current at 3.0 V — all peripheral clocks disabled           | _    | 149        | 303        | μA   | 4 MHz<br>CPU<br>speed, 1<br>MHz bus<br>speed. |

| DD_VLPW              | Very-Low-Power Wait mode current at 3.0 V — all peripheral clocks enabled            | _    | 244        | 347        | μΑ   | 4 MHz<br>CPU<br>speed, 1<br>MHz bus<br>speed. |

| I <sub>DD_STOP</sub> | Stop mode current at 3.0 V<br>• -40 °C to 25 °C                                      |      | 248        | 280        |      | _                                             |

|                      | • at 50 °C                                                                           |      | 248<br>261 | 280<br>315 |      |                                               |

|                      | • at 70 °C                                                                           |      |            |            | μA   |                                               |

|                      | • at 85 °C                                                                           |      | 278<br>307 | 333<br>435 |      |                                               |

|                      | • at 105 °C                                                                          |      | 307<br>381 | 435<br>510 |      |                                               |

| I <sub>DD_VLPS</sub> | Very-Low-Power Stop mode current at 3.0 V<br>• -40 °C to 25 °C                       |      |            | 510        |      | -                                             |

|                      |                                                                                      | _    | 2.2        | 4.3        |      |                                               |

|                      | • at 50 °C                                                                           | _    | 4.2        | 9.9        |      |                                               |

| Table 5. | Power consumption operating behaviors (continued) |

|----------|---------------------------------------------------|

|----------|---------------------------------------------------|

| Symbol                    | Description                                                                                                                                                                                                                                                    |     | ٦   | Tempera | ature (°C | )   |     | Un |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|----|

|                           |                                                                                                                                                                                                                                                                | -40 | 25  | 50      | 70        | 85  | 105 |    |

| I <sub>IREFSTEN4MHz</sub> | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled.                                                                                                                                               | 56  | 56  | 56      | 56        | 56  | 56  | μA |

| IIREFSTEN32KHz            | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.                                                                                                                                                 | 52  | 52  | 52      | 52        | 52  | 52  | μA |

| I <sub>EREFSTEN4MHz</sub> | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                                                                                                                     | 206 | 228 | 237     | 245       | 251 | 258 | u/ |

| IEREFSTEN32KHZ            | External 32 kHz crystal clock adder by<br>means of the OSC0_CR[EREFSTEN<br>and EREFSTEN] bits. Measured by<br>entering all modes with the crystal<br>enabled.                                                                                                  | 440 | 490 | 540     | 560       | 570 | 580 |    |

|                           | VLLS1                                                                                                                                                                                                                                                          | 440 | 490 | 540     | 560       | 570 | 580 | n/ |

|                           | VLLS3                                                                                                                                                                                                                                                          | 510 | 560 | 560     | 560       | 610 | 680 |    |

|                           | VLPS                                                                                                                                                                                                                                                           | 510 | 560 | 560     | 560       | 610 | 680 |    |

|                           | STOP                                                                                                                                                                                                                                                           |     |     |         |           |     |     |    |

| I <sub>CMP</sub>          | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and<br>a single external input for compare.<br>Includes 6-bit DAC power<br>consumption.                                                           | 22  | 22  | 22      | 22        | 22  | 22  | μ  |

| I <sub>UART</sub>         | UART peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source<br>waiting for RX data at 115200 baud<br>rate. Includes selected clock source<br>power consumption.<br>MCGIRCLK (4 MHz internal reference<br>clock) | 66  | 66  | 66      | 66        | 66  | 66  | μι |

|                           | OSCERCLK (4 MHz external crystal)                                                                                                                                                                                                                              | 214 | 237 | 246     | 254       | 260 | 268 |    |

| I <sub>SPI</sub>          | SPI peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source<br>waiting for RX data at 115200 baud<br>rate. Includes selected clock source<br>power consumption.                                                  | 66  | 66  | 66      | 66        | 66  | 66  | μ  |

|                           | MCGIRCLK (4 MHz internal reference<br>clock)                                                                                                                                                                                                                   |     |     |         |           |     |     | μ, |

|                           | OSCERCLK (4 MHz external crystal)                                                                                                                                                                                                                              | 214 | 237 | 246     | 254       | 260 | 268 |    |

| I <sub>I2C</sub>          | I2C peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source                                                                                                                                                      |     |     |         |           |     |     |    |

| Table 6.         Low power mode peripheral adders — typical value | alue |

|-------------------------------------------------------------------|------|

|-------------------------------------------------------------------|------|

Figure 4. VLPR mode current vs. core frequency

### 2.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors

| Symbol              | Description                        | Frequency<br>band<br>(MHz) | Тур. | Unit | Notes |

|---------------------|------------------------------------|----------------------------|------|------|-------|

| V <sub>RE1</sub>    | Radiated emissions voltage, band 1 | 0.15–50                    | 15   | dBµV | 1, 2  |

| V <sub>RE2</sub>    | Radiated emissions voltage, band 2 | 50–150                     | 17   | dBµV |       |

| V <sub>RE3</sub>    | Radiated emissions voltage, band 3 | 150–500                    | 12   | dBµV |       |

| V <sub>RE4</sub>    | Radiated emissions voltage, band 4 | 500-1000                   | 4    | dBµV |       |

| V <sub>RE_IEC</sub> | IEC level                          | 0.15–1000                  | М    | —    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code.

#### Peripheral operating requirements and behaviors

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# 3 Peripheral operating requirements and behaviors

### 3.1 Core modules

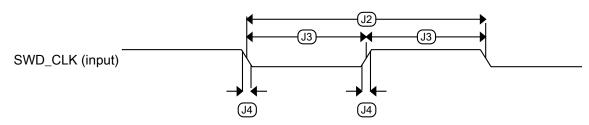

### 3.1.1 SWD Electricals

Table 13. SWD full voltage range electricals

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

|        | Operating voltage                               | 1.71 | 3.6  | V    |

| J1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 25   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 |      | ns   |

| J3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 20   | _    | ns   |

| J4     | SWD_CLK rise and fall times                     |      | 3    | ns   |

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | —    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 0    | —    | ns   |

| J11    | SWD_CLK high to SWD_DIO data valid              | _    | 32   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z                  | 5    |      | ns   |

Figure 5. Serial wire clock input timing

- The resulting system clock frequencies must not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature must be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification is based on standard deviation (RMS) of period or frequency.

- 8. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or there is a change from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

### 3.3.2 Oscillator electrical specifications

### 3.3.2.1 Oscillator DC electrical specifications Table 15. Oscillator DC electrical specifications

| Symbol             | Description                                                    | Min. | Тур. | Max. | Unit | Notes |

|--------------------|----------------------------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                                 | 1.71 | —    | 3.6  | V    |       |

| I <sub>DDOSC</sub> | Supply current — low-power mode (HGO=0)                        |      |      |      |      | 1     |

|                    | • 32 kHz                                                       | —    | 500  | _    | nA   |       |

|                    | • 4 MHz                                                        | _    | 200  | _    | μA   |       |

|                    | • 8 MHz                                                        | _    | 300  | _    | μA   |       |

|                    | • 16 MHz                                                       | _    | 950  | _    | μA   |       |

|                    | • 24 MHz                                                       | _    | 1.2  | _    | mA   |       |

|                    | • 32 MHz                                                       | _    | 1.5  | _    | mA   |       |

| IDDOSC             | Supply current — high gain mode (HGO=1)                        |      |      |      |      | 1     |

|                    | • 4 MHz                                                        | _    | 500  | _    | μA   |       |

|                    | • 8 MHz                                                        | _    | 600  | _    | μA   |       |

|                    | • 16 MHz                                                       | _    | 2.5  | _    | mA   |       |

|                    | • 24 MHz                                                       | _    | 3    | _    | mA   |       |

|                    | • 32 MHz                                                       | _    | 4    | _    | mA   |       |

| C <sub>x</sub>     | EXTAL load capacitance                                         |      |      | _    |      | 2, 3  |

| Cy                 | XTAL load capacitance                                          |      |      | —    |      | 2, 3  |

| R <sub>F</sub>     | Feedback resistor — low-frequency, low-power mode (HGO=0)      |      |      |      | MΩ   | 2, 4  |

|                    | Feedback resistor — low-frequency, high-gain mode (HGO=1)      | _    | 10   | —    | MΩ   |       |

|                    | Feedback resistor — high-frequency, low-<br>power mode (HGO=0) |      | _    | _    | MΩ   |       |

|                    | Feedback resistor — high-frequency, high-gain mode (HGO=1)     | _    | 1    | _    | MΩ   |       |

| Symbol           | Description                                                                                  | Min. | Тур. | Max. | Unit | Notes |

|------------------|----------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>cst</sub> | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                       | _    | 1000 | —    | ms   | 3, 4  |

|                  | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                       | _    | 250  |      | ms   |       |

|                  | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0) | _    | 0.6  | _    | ms   |       |

|                  | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1) | _    | 1    | _    | ms   |       |

Table 16.

Oscillator frequency specifications (continued)

- 1. Other frequency limits may apply when external clock is being used as a reference for the FLL.

- 2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- 4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

### NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

### 3.4 Memories and memory interfaces

### 3.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 3.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                | Description                        | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time | —    | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | _    | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time        | _    | 52   | 452  | ms   | 1     |

Table 17.

NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

# NP

#### **ADC electrical specifications**

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

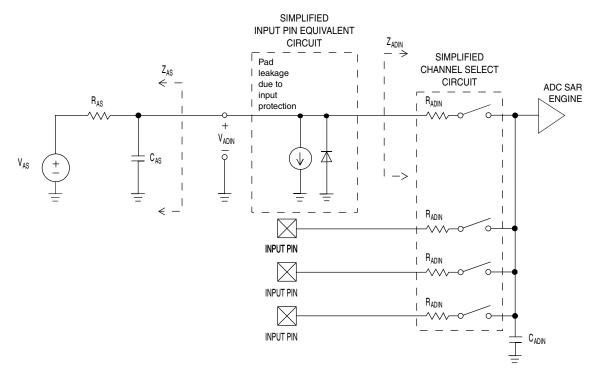

- This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8 Ω analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.</li>

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 7. ADC input impedance equivalency diagram

### 3.6.1.2 16-bit ADC electrical characteristics

| Symbol               | Description                         | Conditions <sup>1</sup> .                                                      | Min.         | Typ. <sup>2</sup> | Max.       | Unit              | Notes                                        |

|----------------------|-------------------------------------|--------------------------------------------------------------------------------|--------------|-------------------|------------|-------------------|----------------------------------------------|

| I <sub>DDA_ADC</sub> | Supply current                      |                                                                                | 0.215        | _                 | 1.7        | mA                | 3                                            |

| f <sub>adack</sub>   | ADC<br>asynchronous<br>clock source | <ul> <li>ADLPC = 1, ADHSC =<br/>0</li> <li>ADLPC = 1, ADHSC =</li> </ul>       | 1.2<br>2.4   | 2.4<br>4.0        | 3.9<br>6.1 | MHz               | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub> |

|                      | CIOCK SOURCE                        | <ul> <li>ADLPC = 0, ADHSC =<br/>0</li> <li>ADLPC = 0, ADHSC =<br/>1</li> </ul> | 3.0<br>4.4   | 5.2<br>6.2        | 7.3<br>9.5 | MHz<br>MHz<br>MHz |                                              |

|                      | Sample Time                         | See Reference Manual chapte                                                    | r for sample | times             |            | 1                 | 1                                            |

Table continues on the next page ...

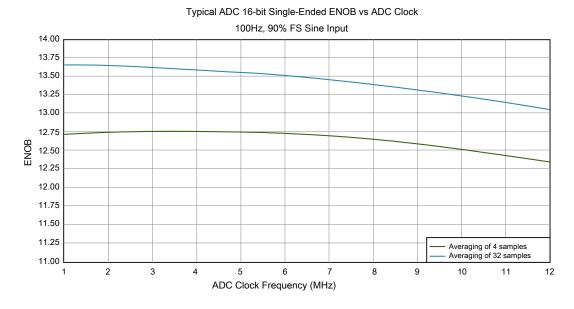

Figure 9. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 23. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                               | Min.                  | Тур. | Max.            | Unit |

|--------------------|-----------------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>    | Supply voltage                                            | 1.71                  |      | 3.6             | V    |

| I <sub>DDHS</sub>  | Supply current, high-speed mode (EN = 1, PMODE = 1)       | —                     | _    | 200             | μA   |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN = 1, PMODE = 0)        | —                     | _    | 20              | μA   |

| V <sub>AIN</sub>   | Analog input voltage                                      | V <sub>SS</sub>       | —    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                               | —                     |      | 20              | mV   |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>                 |                       |      |                 |      |

|                    | • CR0[HYSTCTR] = 00                                       | —                     | 5    | _               | mV   |

|                    | • CR0[HYSTCTR] = 01                                       | —                     | 10   | _               | mV   |

|                    | • CR0[HYSTCTR] = 10                                       | —                     | 20   | _               | mV   |

|                    | • CR0[HYSTCTR] = 11                                       | —                     | 30   | _               | mV   |

| V <sub>CMPOh</sub> | Output high                                               | V <sub>DD</sub> – 0.5 |      |                 | V    |

| V <sub>CMPOI</sub> | Output low                                                | —                     | _    | 0.5             | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN = 1,<br>PMODE = 1) | 20                    | 35   | 200             | ns   |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN = 1,<br>PMODE = 0)  | 80                    | 100  | 600             | ns   |

|                    | Analog comparator initialization delay <sup>2</sup>       | —                     | _    | 40              | μs   |

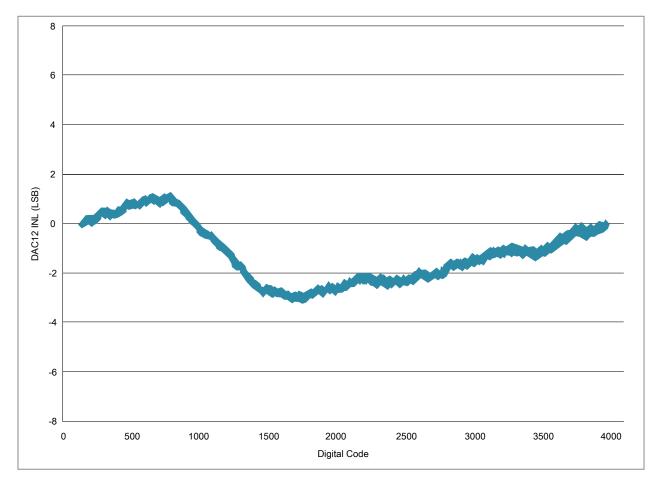

Figure 12. Typical INL error vs. digital code

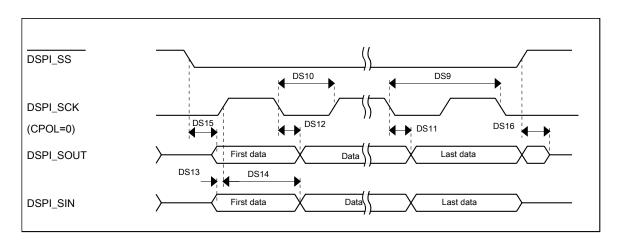

### 3.8.1 DSPI switching specifications (limited voltage range)

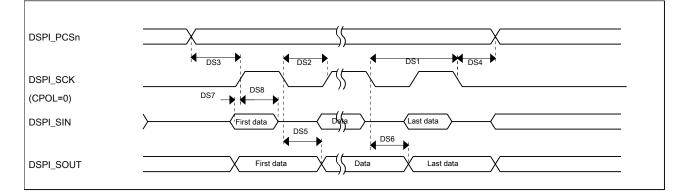

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                      | Unit | Notes |

|-----|-------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                   | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation              | —                             | 25                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 2 x t <sub>BUS</sub>          | —                         | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 8.5                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -2                            | —                         | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 17                            | —                         | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | —                         | ns   |       |

| Table 26. | Master mode DS | PI timing (limited | voltage range) |

|-----------|----------------|--------------------|----------------|

|-----------|----------------|--------------------|----------------|

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 14. DSPI classic SPI timing — master mode

### Table 27. Slave mode DSPI timing (limited voltage range)

| Num | Description            | Min. | Max. | Unit |

|-----|------------------------|------|------|------|

|     | Operating voltage      | 2.7  | 3.6  | V    |

|     | Frequency of operation |      | 12.5 | MHz  |

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | _                         | 21                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | —                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 15                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | —                         | 15                        | ns   |

Table 27. Slave mode DSPI timing (limited voltage range) (continued)

Figure 15. DSPI classic SPI timing — slave mode

### 3.8.2 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                   | Min.                      | Max.                     | Unit | Notes |

|-----|-------------------------------|---------------------------|--------------------------|------|-------|

|     | Operating voltage             | 1.71                      | 3.6                      | V    | 1     |

|     | Frequency of operation        | —                         | 12.5                     | MHz  |       |

| DS1 | DSPI_SCK output cycle time    | 4 x t <sub>BUS</sub>      | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |       |

Table 28. Master mode DSPI timing (full voltage range)

#### Pinout

| 48<br>LQFP | 32<br>QFN | 32<br>LQFP | Pin Name | Default                              | ALT0                                 | ALT1              | ALT2               | ALT3            | ALT4       | ALT5            | ALT6            | ALT7               |

|------------|-----------|------------|----------|--------------------------------------|--------------------------------------|-------------------|--------------------|-----------------|------------|-----------------|-----------------|--------------------|

| 15         | 10        | 10         | PTE24    | DISABLED                             |                                      | PTE24             |                    | FTM0_CH0        |            | I2C0_SCL        | EWM_OUT_b       |                    |

| 16         | 11        | 11         | PTE25    | DISABLED                             |                                      | PTE25             |                    | FTM0_CH1        |            | I2C0_SDA        | EWM_IN          |                    |

| 17         | 12        | 12         | PTA0     | SWD_CLK                              |                                      | PTA0              | UARTO_<br>CTS_b    | FTM0_CH5        |            |                 |                 | SWD_CLK            |

| 18         | 13        | 13         | PTA1     | DISABLED                             |                                      | PTA1              | UART0_RX           | FTM2_CH0        | CMP0_OUT   | FTM2_QD_<br>PHA | FTM1_CH1        |                    |

| 19         | 14        | 14         | PTA2     | DISABLED                             |                                      | PTA2              | UART0_TX           | FTM2_CH1        | CMP1_OUT   | FTM2_QD_<br>PHB | FTM1_CH0        |                    |

| 20         | 15        | 15         | PTA3     | SWD_DIO                              |                                      | PTA3              | UART0_<br>RTS_b    | FTM0_CH0        | FTM2_FLT0  | EWM_OUT_b       |                 | SWD_DIO            |

| 21         | 16        | 16         | PTA4     | NMI_b                                |                                      | PTA4/<br>LLWU_P3  |                    | FTM0_CH1        |            | FTM0_FLT3       |                 | NMI_b              |

| 22         | -         | -          | VDD      | VDD                                  | VDD                                  |                   |                    |                 |            |                 |                 |                    |

| 23         | -         | _          | VSS      | VSS                                  | VSS                                  |                   |                    |                 |            |                 |                 |                    |

| 24         | 17        | 17         | PTA18    | EXTAL0                               | EXTAL0                               | PTA18             |                    | FTM0_FLT2       | FTM_CLKIN0 |                 |                 |                    |

| 25         | 18        | 18         | PTA19    | XTAL0                                | XTAL0                                | PTA19             | FTM0_FLT0          | FTM1_FLT0       | FTM_CLKIN1 |                 | LPTMR0_<br>ALT1 |                    |

| 26         | 19        | 19         | PTA20    | RESET_b                              |                                      | PTA20             |                    |                 |            |                 |                 | RESET_b            |

| 27         | 20        | 20         | PTB0     | ADC0_SE8/<br>ADC1_SE8                | ADC0_SE8/<br>ADC1_SE8                | PTB0/<br>LLWU_P5  | I2C0_SCL           | FTM1_CH0        |            |                 | FTM1_QD_<br>PHA | UART0_RX           |

| 28         | 21        | 21         | PTB1     | ADC0_SE9/<br>ADC1_SE9                | ADC0_SE9/<br>ADC1_SE9                | PTB1              | I2C0_SDA           | FTM1_CH1        | FTM0_FLT2  | EWM_IN          | FTM1_QD_<br>PHB | UART0_TX           |

| 29         | -         | -          | PTB2     | ADC0_SE10/<br>ADC1_SE10/<br>ADC1_DM2 | ADC0_SE10/<br>ADC1_SE10/<br>ADC1_DM2 | PTB2              | I2C0_SCL           | UARTO_<br>RTS_b | FTM0_FLT1  |                 | FTM0_FLT3       |                    |

| 30         | -         | -          | PTB3     | ADC1_SE2/<br>ADC1_DP2                | ADC1_SE2/<br>ADC1_DP2                | PTB3              | I2C0_SDA           | UART0_<br>CTS_b |            |                 | FTM0_FLT0       |                    |

| 31         | -         | -          | PTB16    | DISABLED                             |                                      | PTB16             |                    | UART0_RX        | FTM_CLKIN2 |                 | EWM_IN          |                    |

| 32         | -         | -          | PTB17    | DISABLED                             |                                      | PTB17             |                    | UART0_TX        | FTM_CLKIN1 |                 | EWM_OUT_b       |                    |

| 33         | -         | -          | PTC0     | ADC1_SE11                            | ADC1_SE11                            | PTC0              | SPI0_PCS4          | PDB0_<br>EXTRG  |            | CMP0_OUT        | FTM0_FLT0       | SPI0_PCS0/<br>SS_b |

| 34         | 22        | 22         | PTC1     | ADC1_SE3                             | ADC1_SE3                             | PTC1/<br>LLWU_P6  | SPI0_PCS3          | UART1_<br>RTS_b | FTM0_CH0   | FTM2_CH0        |                 |                    |

| 35         | 23        | 23         | PTC2     | ADC0_SE11/<br>CMP1_IN0               | ADC0_SE11/<br>CMP1_IN0               | PTC2              | SPI0_PCS2          | UART1_<br>CTS_b | FTM0_CH1   | FTM2_CH1        |                 |                    |

| 36         | 24        | 24         | PTC3     | CMP1_IN1                             | CMP1_IN1                             | PTC3/<br>LLWU_P7  | SPI0_PCS1          | UART1_RX        | FTM0_CH2   | CLKOUT          |                 |                    |

| 37         | 25        | 25         | PTC4     | DISABLED                             |                                      | PTC4/<br>LLWU_P8  | SPI0_PCS0/<br>SS_b | UART1_TX        | FTM0_CH3   |                 | CMP1_OUT        |                    |

| 38         | 26        | 26         | PTC5     | DISABLED                             |                                      | PTC5/<br>LLWU_P9  | SPI0_SCK           | LPTMR0_<br>ALT2 |            |                 | CMP0_OUT        | FTM0_CH2           |

| 39         | 27        | 27         | PTC6     | CMP0_IN0                             | CMP0_IN0                             | PTC6/<br>LLWU_P10 | SPI0_SOUT          | PDB0_<br>EXTRG  |            | UART0_RX        |                 | I2C0_SCL           |

| 40         | 28        | 28         | PTC7     | CMP0_IN1                             | CMP0_IN1                             | PTC7              | SPI0_SIN           |                 |            | UART0_TX        |                 | I2C0_SDA           |

| 48<br>LQFP | 32<br>QFN | 32<br>LQFP | Pin Name | Default  | ALT0     | ALT1              | ALT2               | ALT3            | ALT4     | ALT5     | ALT6      | ALT7     |

|------------|-----------|------------|----------|----------|----------|-------------------|--------------------|-----------------|----------|----------|-----------|----------|

| 41         | -         | _          | PTD0     | DISABLED |          | PTD0/<br>LLWU_P12 | SPI0_PCS0/<br>SS_b | UART0_<br>CTS_b | FTM0_CH0 | UART1_RX |           |          |

| 42         | _         | -          | PTD1     | ADC0_SE2 | ADC0_SE2 | PTD1              | SPI0_SCK           | UART0_<br>RTS_b | FTM0_CH1 | UART1_TX |           |          |

| 43         | -         | -          | PTD2     | DISABLED |          | PTD2/<br>LLWU_P13 | SPI0_SOUT          | UART0_RX        | FTM0_CH2 |          |           | I2C0_SCL |

| 44         | -         | -          | PTD3     | DISABLED |          | PTD3              | SPI0_SIN           | UART0_TX        | FTM0_CH3 |          |           | I2C0_SDA |

| 45         | 29        | 29         | PTD4     | DISABLED |          | PTD4/<br>LLWU_P14 | SPI0_PCS1          | UART0_<br>RTS_b | FTM0_CH4 | FTM2_CH0 | EWM_IN    |          |

| 46         | 30        | 30         | PTD5     | ADC0_SE3 | ADC0_SE3 | PTD5              | SPI0_PCS2          | UART0_<br>CTS_b | FTM0_CH5 | FTM2_CH1 | EWM_OUT_b |          |

| 47         | 31        | 31         | PTD6     | ADC1_SE6 | ADC1_SE6 | PTD6/<br>LLWU_P15 | SPI0_PCS3          | UART0_RX        | FTM0_CH0 | FTM1_CH0 | FTM0_FLT0 |          |

| 48         | 32        | 32         | PTD7     | DISABLED |          | PTD7              |                    | UART0_TX        | FTM0_CH1 | FTM1_CH1 | FTM0_FLT1 |          |

# 5.2 KV10 Pinouts

The following figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

# 8.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 8.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 8.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

# 8.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

# 8.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

### 8.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

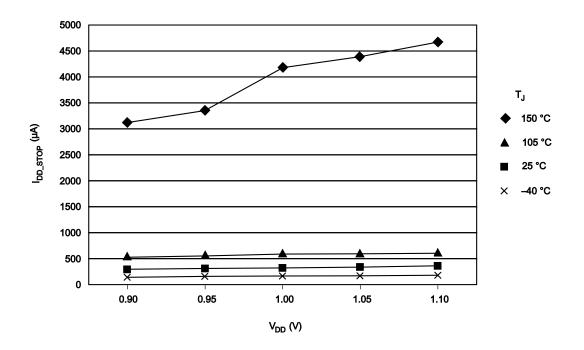

# 8.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

**Revision history**

# 8.9 Typical Value Conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | Э°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 9 Revision history

The following table provides a revision history for this document.

| Rev. No. | Date    | Substantial Changes                                                                                                                                     |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 02/2014 | Initial public release                                                                                                                                  |

| 4        | 02/2015 | <ul> <li>Updated the section "Power consumption operating behaviors"</li> <li>Added a note below the "Thermal operating requirements" table.</li> </ul> |

Table 30. Revision history

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, Freescale logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2014-2015 Freescale Semiconductor, Inc.

Document Number KV10P48M75 Revision 4, 02/2015