Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| )etails                  |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

|                          | Obselvts                                                                       |

| roduct Status            | Obsolete                                                                       |

| Core Processor           | F <sup>2</sup> MC-16FX                                                         |

| Core Size                | 16-Bit                                                                         |

| peed                     | 56MHz                                                                          |

| onnectivity              | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SCI, UART/USART                     |

| eripherals               | DMA, LVD, LVR, POR, PWM, WDT                                                   |

| umber of I/O             | 82                                                                             |

| rogram Memory Size       | 416KB (416K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| AM Size                  | 16K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| ata Converters           | A/D 24x10b                                                                     |

| scillator Type           | Internal                                                                       |

| perating Temperature     | -40°C ~ 105°C (TA)                                                             |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 100-BQFP                                                                       |

| ipplier Device Package   | 100-PQFP (14x20)                                                               |

| ırchase URL              | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f347rscpqc-gse2 |

#### **■ PIN CIRCUIT TYPE**

### Pin circuit types

| Pin Circuit ty | ypoo               | _ |           |                    |

|----------------|--------------------|---|-----------|--------------------|

| FPT-10         | 0P-M20             |   | FPT-10    | 0P-M22             |

| Pin no.        | Circuit<br>type *1 |   | Pin no.   | Circuit<br>type *1 |

| 1-10           | Н                  |   | 1-12      | Н                  |

| 11,12          | B*2                |   | 13, 14    | B*2                |

| 11,12          | H *3               |   | 13, 14    | H*3                |

| 13,14          | Supply             |   | 15,16     | Supply             |

| 15             | F                  |   | 17        | F                  |

| 16,17          | Н                  |   | 18,19     | Н                  |

| 18-21          | N                  |   | 20-23     | N                  |

| 22-29          | I                  |   | 24-31     | I                  |

| 30             | Supply             |   | 32        | Supply             |

| 31-32          | G                  |   | 33-34     | G                  |

| 33             | Supply             |   | 35        | Supply             |

| 34 to 41       | I                  |   | 36 to 43  | I                  |

| 42             | Supply             |   | 44        | Supply             |

| 43 to 48       | I                  |   | 45 to 50  | I                  |

| 49 to 51       | С                  |   | 51 to 53  | С                  |

| 52             | E                  |   | 54        | E                  |

| 53 to 54       | I                  |   | 55 to 56  | I                  |

| 55 to 62       | Н                  |   | 57 to 64  | Н                  |

| 63, 64         | Supply             |   | 65, 66    | Supply             |

| 65 to 87       | Н                  |   | 67 to 89  | Н                  |

| 88,89          | Supply             |   | 90, 91    | Supply             |

| 90, 91         | А                  |   | 92, 93    | А                  |

| 92-100         | Н                  |   | 94 to 100 | Н                  |

<sup>\*1:</sup> Please refer to "■ I/O CIRCUIT TYPE" for details on the I/O circuit types

<sup>\*2:</sup> Devices with suffix "W"

<sup>\*3:</sup> Devices without suffix "W"

## ■ I/O CIRCUIT TYPE

| Туре | Circuit                                | Remarks                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

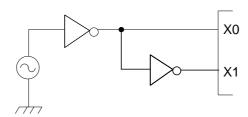

| A    | X1 R  MRFBE  R  X0  FCI or osc disable | <ul> <li>High-speed oscillation circuit:</li> <li>Programmable between oscillation mode (external crystal or resonator connected to X0/X1 pins) and Fast external Clock Input (FCI) mode (external clock connected to X0 pin)</li> <li>Programmable feedback resistor = approx. 2 * 0.5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled or in FCI mode</li> </ul> |

| В    | X1A Xout  SRFBE Osc disable            | Low-speed oscillation circuit: • Programmable feedback resistor = approx. 2 * 5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled                                                                                                                                                                                                                                   |

| С    | R<br>Hysteresis<br>inputs              | Mask ROM and EVA device:     CMOS Hysteresis input pin     Flash device:     CMOS input pin                                                                                                                                                                                                                                                                                                       |

| E    | Pull-up Resistor  Hysteresis inputs    | <ul> <li>CMOS Hysteresis input pin</li> <li>Pull-up resistor value: approx. 50 kΩ</li> </ul>                                                                                                                                                                                                                                                                                                      |

|                                              |                           | MB96F346Y<br>MB96F346R<br>MB96F346A | MB96F347Y<br>MB96F347R<br>MB96F347A |          |

|----------------------------------------------|---------------------------|-------------------------------------|-------------------------------------|----------|

| Alternative mode<br>CPU address              | Flash memory mode address | Flash size<br>288kByte              | Flash size<br>416kByte              |          |

| FF:FFFFH                                     | 3F:FFFFн                  | S39 - 64K                           | S39 - 64K                           |          |

| FF:0000h<br>FE:FFFFh                         | 3F:0000н<br>3E:FFFFн      | 1                                   |                                     |          |

| FE:0000н                                     | 3E:0000н                  | S38 - 64K                           | S38 - 64K                           |          |

| FD:FFFFH                                     | 3D:FFFFH                  | S37 - 64K                           | S37 - 64K                           |          |

| FD:0000 <sub>H</sub>                         | 3D:0000 <sub>H</sub>      | 337 - 64K                           | 537 - 64N                           | Flash    |

| FC:FFFFH                                     | 3C:FFFFн                  | S36 - 64K                           | S36 - 64K                           | riasii i |

| FC:0000 <sub>H</sub>                         | 3С:0000н                  | 030 041                             |                                     |          |

| FB:FFFF <sub>H</sub>                         | 3B:FFFFн                  |                                     | S35 - 64K                           |          |

| FB:0000н                                     | 3В:0000н                  | _  _                                |                                     |          |

| FA:FFFF <sub>H</sub>                         | 3A:FFFF <sub>H</sub>      |                                     | S34 - 64K                           |          |

| FA:0000H<br>F9:FFFFH                         | 3A:0000н<br>39:FFFFн      |                                     |                                     |          |

| F9:ГГГГН<br>F9:0000н                         | 39:0000н                  |                                     |                                     |          |

| F8:FFFFH                                     | 38:FFFFн                  |                                     | <del></del>                         |          |

| F8:0000 <sub>H</sub>                         | 38:0000н                  |                                     |                                     |          |

| F7:FFFFH                                     | 37:FFFF <sub>H</sub>      | -i                                  |                                     |          |

| F7:0000 <sub>H</sub>                         | 37:0000н                  |                                     |                                     |          |

| F6:FFFF                                      | 36:FFFFн                  | i i                                 |                                     |          |

| F6:0000 <sub>H</sub>                         | 36:0000н                  |                                     |                                     |          |

| F5:FFFF <sub>H</sub>                         | 35:FFFFн                  | i i                                 |                                     |          |

| F5:0000н                                     | 35:0000н                  | External bus                        |                                     |          |

| F4:FFFF <sub>H</sub>                         | 34:FFFFн                  | External bas                        |                                     |          |

| F4:0000H                                     | 34:0000н                  | _!                                  | External bus                        |          |

| F3:FFFF <sub>H</sub>                         | 33:FFFF <sub>H</sub>      |                                     |                                     |          |

| F3:0000н<br>F2:FFFFн                         | 33:0000н<br>32:FFFFн      |                                     |                                     |          |

| F2:0000H                                     | 32:0000н                  |                                     |                                     |          |

| F1:FFFFH                                     | 31:FFFF <sub>H</sub>      |                                     |                                     |          |

| F1:0000 <sub>H</sub>                         | 31:0000н                  |                                     |                                     |          |

| F0:FFFFH                                     | 30:FFFFн                  | 1                                   |                                     |          |

| F0:0000 <sub>H</sub>                         | 30:0000н                  |                                     |                                     |          |

| E0:FFFF <sub>H</sub>                         |                           |                                     |                                     |          |

| Е0:0000н                                     |                           |                                     |                                     |          |

| DF:FFFFH                                     |                           | Reserved                            | Reserved                            |          |

| DF:8000 <sub>H</sub><br>DF:7FFF <sub>H</sub> | 1F:7FFFн                  |                                     |                                     | $\neg$   |

| DF:7FFFн<br>DF:6000н                         | 1F:7FFFн<br>1F:6000н      | SA3 - 8K                            | SA3 - 8K                            |          |

| DF:5000H                                     | 1F:5FFFн                  | L 040 0K                            | 040 01/                             |          |

| DF:4000H                                     | 1F:4000н                  | SA2 - 8K                            | SA2 - 8K                            |          |

| DF:3FFFH                                     | 1F:3FFFн                  | SA1 - 8K                            | SA1 - 8K                            | Flash /  |

| DF:2000 <sub>H</sub>                         | 1F:2000 <sub>H</sub>      | SAI-BK                              | J SAI-BK                            |          |

| DF:1FFF <sub>H</sub>                         | 1F:1FFFH                  | SA0 - 8K *1                         | SA0 - 8K *1                         |          |

| DF:0000 <sub>H</sub>                         | 1F:0000 <sub>H</sub>      | SAU-ON                              | J SAU-ON '                          |          |

| DE:FFFF <sub>H</sub>                         |                           | Reserved                            | Reserved                            | _        |

| DE:0000 <sub>H</sub>                         |                           |                                     |                                     |          |

## I/O map MB96(F)34x (2 of 30)

| Address | Register                                                  | Abbreviation<br>8-bit access | Abbreviation 16-bit access | Access |  |

|---------|-----------------------------------------------------------|------------------------------|----------------------------|--------|--|

| 000026н | FRT1 - Control status register of free-running timer Low  | TCCSL1                       | TCCS1                      | R/W    |  |

| 000027н | FRT1 - Control status register of free-running timer High | TCCSH1                       |                            | R/W    |  |

| 000028н | OCU0 - Output Compare Control Status                      | OCS0                         |                            | R/W    |  |

| 000029н | OCU1 - Output Compare Control Status                      | OCS1                         |                            | R/W    |  |

| 00002Ан | OCU0 - Compare Register                                   |                              | OCCP0                      | R/W    |  |

| 00002Вн | OCU0 - Compare Register                                   |                              |                            | R/W    |  |

| 00002Сн | OCU1 - Compare Register                                   |                              | OCCP1                      | R/W    |  |

| 00002Dн | OCU1 - Compare Register                                   |                              |                            | R/W    |  |

| 00002Ен | OCU2 - Output Compare Control Status                      | OCS2                         |                            | R/W    |  |

| 00002Fн | OCU3 - Output Compare Control Status                      | OCS3                         |                            | R/W    |  |

| 000030н | OCU2 - Compare Register                                   |                              | OCCP2                      | R/W    |  |

| 000031н | OCU2 - Compare Register                                   |                              |                            | R/W    |  |

| 000032н | OCU3 - Compare Register                                   |                              | OCCP3                      | R/W    |  |

| 000033н | OCU3 - Compare Register                                   |                              |                            | R/W    |  |

| 000034н | OCU4 - Output Compare Control Status                      | OCS4                         |                            | R/W    |  |

| 000035н | OCU5 - Output Compare Control Status                      | OCS5                         |                            | R/W    |  |

| 000036н | OCU4 - Compare Register                                   |                              | OCCP4                      | R/W    |  |

| 000037н | OCU4 - Compare Register                                   |                              |                            | R/W    |  |

| 000038н | OCU5 - Compare Register                                   |                              | OCCP5                      | R/W    |  |

| 000039н | OCU5 - Compare Register                                   |                              |                            | R/W    |  |

| 00003Ан | OCU6 - Output Compare Control Status                      | OCS6                         |                            | R/W    |  |

| 00003Вн | OCU7 - Output Compare Control Status                      | OCS7                         |                            | R/W    |  |

| 00003Сн | OCU6 - Compare Register                                   |                              | OCCP6                      | R/W    |  |

| 00003Dн | OCU6 - Compare Register                                   |                              |                            | R/W    |  |

| 00003Ен | OCU7 - Compare Register                                   |                              | OCCP7                      | R/W    |  |

| 00003Fн | OCU7 - Compare Register                                   |                              |                            | R/W    |  |

| 000040н | ICU0/ICU1 - Control Status Register                       | ICS01                        |                            | R/W    |  |

| 000041н | ICU0/ICU1 - Edge register                                 | ICE01                        |                            | R/W    |  |

| 000042н | ICU0 - Capture Register Low                               | IPCPL0                       | IPCP0                      | R      |  |

## I/O map MB96(F)34x (7 of 30)

| Address | Register                                   | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------|--------------------------------------------|------------------------------|-------------------------------|--------|

| 0000АВн | PPG5 - Control status register High        | PCNH5                        |                               | R/W    |

| 0000АСн | I2C0 - Bus Status Register                 | IBSR0                        |                               | R      |

| 0000АДн | I2C0 - Bus Control Register                | IBCR0                        |                               | R/W    |

| 0000АЕн | I2C0 - Ten bit Slave address Register Low  | ITBAL0                       | ITBA0                         | R/W    |

| 0000АГн | I2C0 - Ten bit Slave address Register High | ITBAH0                       |                               | R/W    |

| 0000В0н | I2C0 - Ten bit Address mask Register Low   | ITMKL0                       | ITMK0                         | R/W    |

| 0000В1н | I2C0 - Ten bit Address mask Register High  | ITMKH0                       |                               | R/W    |

| 0000В2н | I2C0 - Seven bit Slave address Register    | ISBA0                        |                               | R/W    |

| 0000ВЗн | I2C0 - Seven bit Address mask Register     | ISMK0                        |                               | R/W    |

| 0000В4н | I2C0 - Data Register                       | IDAR0                        |                               | R/W    |

| 0000В5н | I2C0 - Clock Control Register              | ICCR0                        |                               | R/W    |

| 0000В6н | I2C1 - Bus Status Register                 | IBSR1                        |                               | R      |

| 0000В7н | I2C1 - Bus Control Register                | IBCR1                        |                               | R/W    |

| 0000В8н | I2C1 - Ten bit Slave address Register Low  | ITBAL1                       | ITBA1                         | R/W    |

| 0000В9н | I2C1 - Ten bit Slave address Register High | ITBAH1                       |                               | R/W    |

| 0000ВАн | I2C1 - Ten bit Address mask Register Low   | ITMKL1                       | ITMK1                         | R/W    |

| 0000ВВн | I2C1 - Ten bit Address mask Register High  | ITMKH1                       |                               | R/W    |

| 0000ВСн | I2C1 - Seven bit Slave address Register    | ISBA1                        |                               | R/W    |

| 0000ВДн | I2C1 - Seven bit Address mask Register     | ISMK1                        |                               | R/W    |

| 0000ВЕн | I2C1 - Data Register                       | IDAR1                        |                               | R/W    |

| 0000ВГн | I2C1 - Clock Control Register              | ICCR1                        |                               | R/W    |

| 0000С0н | USART0 - Serial Mode Register              | SMR0                         |                               | R/W    |

| 0000С1н | USART0 - Serial Control Register           | SCR0                         |                               | R/W    |

| 0000С2н | USART0 - TX Register                       | TDR0                         |                               | W      |

| 0000С2н | USART0 - RX Register                       | RDR0                         |                               | R      |

| 0000СЗн | USART0 - Serial Status                     | SSR0                         |                               | R/W    |

| 0000С4н | USART0 - Control/Com. Register             | ECCR0                        |                               | R/W    |

| 0000С5н | USART0 - Ext. Status Register              | ESCR0                        |                               | R/W    |

| 0000С6н | USART0 - Baud Rate Generator Register Low  | BGRL0                        | BGR0                          | R/W    |

| 0000С7н | USART0 - Baud Rate Generator Register High | BGRH0                        |                               | R/W    |

### I/O map MB96(F)34x (8 of 30)

| Address | Register                                    | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------|---------------------------------------------|------------------------------|-------------------------------|--------|

| 0000С8н | USART0 - Extended Serial Interrupt Register | ESIR0                        |                               | R/W    |

| 0000С9н | Reserved                                    |                              |                               | -      |

| 0000САн | USART1 - Serial Mode Register               | SMR1                         |                               | R/W    |

| 0000СВн | USART1 - Serial Control Register            | SCR1                         |                               | R/W    |

| 0000ССн | USART1 - TX Register                        | TDR1                         |                               | W      |

| 0000ССн | USART1 - RX Register                        | RDR1                         |                               | R      |

| 0000СDн | USART1 - Serial Status                      | SSR1                         |                               | R/W    |

| 0000СЕн | USART1 - Control/Com. Register              | ECCR1                        |                               | R/W    |

| 0000СFн | USART1 - Ext. Status Register               | ESCR1                        |                               | R/W    |

| 0000D0н | USART1 - Baud Rate Generator Register Low   | BGRL1                        | BGR1                          | R/W    |

| 0000D1н | USART1 - Baud Rate Generator Register High  | BGRH1                        |                               | R/W    |

| 0000D2н | USART1 - Extended Serial Interrupt Register | ESIR1                        |                               | R/W    |

| 0000Д3н | Reserved                                    |                              |                               | -      |

| 0000Д4н | USART2 - Serial Mode Register               | SMR2                         |                               | R/W    |

| 0000D5н | USART2 - Serial Control Register            | SCR2                         |                               | R/W    |

| 0000Д6н | USART2 - TX Register                        | TDR2                         |                               | W      |

| 0000Д6н | USART2 - RX Register                        | RDR2                         |                               | R      |

| 0000D7н | USART2 - Serial Status                      | SSR2                         |                               | R/W    |

| 0000D8н | USART2 - Control/Com. Register              | ECCR2                        |                               | R/W    |

| 0000D9н | USART2 - Ext. Status Register               | ESCR2                        |                               | R/W    |

| 0000Дн  | USART2 - Baud Rate Generator Register Low   | BGRL2                        | BGR2                          | R/W    |

| 0000ДВн | USART2 - Baud Rate Generator Register High  | BGRH2                        |                               | R/W    |

| 0000DСн | USART2 - Extended Serial Interrupt Register | ESIR2                        |                               | R/W    |

| 0000DDн | Reserved                                    |                              |                               | -      |

| 0000ДЕн | USART3 - Serial Mode Register               | SMR3                         |                               | R/W    |

| 0000DFн | USART3 - Serial Control Register            | SCR3                         |                               | R/W    |

| 0000Е0н | USART3 - TX Register                        | TDR3                         |                               | W      |

| 0000Е0н | USART3 - RX Register                        | RDR3                         |                               | R      |

| 0000Е1н | USART3 - Serial Status                      | SSR3                         |                               | R/W    |

| 0000Е2н | USART3 - Control/Com. Register              | ECCR3                        |                               | R/W    |

## I/O map MB96(F)34x (29 of 30)

| Address             | Register                                         | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|--------------------------------------------------|------------------------------|-------------------------------|--------|

| 000840н             | CAN1 - IF2 Command request register Low          | IF2CREQL1                    | IF2CREQ1                      | R/W    |

| 000841н             | CAN1 - IF2 Command request register High         | IF2CREQH1                    |                               | R/W    |

| 000842н             | CAN1 - IF2 Command Mask register Low             | IF2CMSKL1                    | IF2CMSK1                      | R/W    |

| 000843н             | CAN1 - IF2 Command Mask register High (reserved) | IF2CMSKH1                    |                               | R      |

| 000844н             | CAN1 - IF2 Mask 1 Register Low                   | IF2MSK1L1                    | IF2MSK11                      | R/W    |

| 000845н             | CAN1 - IF2 Mask 1 Register High                  | IF2MSK1H1                    |                               | R/W    |

| 000846н             | CAN1 - IF2 Mask 2 Register Low                   | IF2MSK2L1                    | IF2MSK21                      | R/W    |

| 000847н             | CAN1 - IF2 Mask 2 Register High                  | IF2MSK2H1                    |                               | R/W    |

| 000848н             | CAN1 - IF2 Arbitration 1 Register Low            | IF2ARB1L1                    | IF2ARB11                      | R/W    |

| 000849н             | CAN1 - IF2 Arbitration 1 Register High           | IF2ARB1H1                    |                               | R/W    |

| 00084Ан             | CAN1 - IF2 Arbitration 2 Register Low            | IF2ARB2L1                    | IF2ARB21                      | R/W    |

| 00084Вн             | CAN1 - IF2 Arbitration 2 Register High           | IF2ARB2H1                    |                               | R/W    |

| 00084Сн             | CAN1 - IF2 Message Control Register Low          | IF2MCTRL1                    | IF2MCTR1                      | R/W    |

| 00084Dн             | CAN1 - IF2 Message Control Register High         | IF2MCTRH1                    |                               | R/W    |

| 00084Ен             | CAN1 - IF2 Data A1 Low                           | IF2DTA1L1                    | IF2DTA11                      | R/W    |

| 00084Fн             | CAN1 - IF2 Data A1 High                          | IF2DTA1H1                    |                               | R/W    |

| 000850н             | CAN1 - IF2 Data A2 Low                           | IF2DTA2L1                    | IF2DTA21                      | R/W    |

| 000851н             | CAN1 - IF2 Data A2 High                          | IF2DTA2H1                    |                               | R/W    |

| 000852н             | CAN1 - IF2 Data B1 Low                           | IF2DTB1L1                    | IF2DTB11                      | R/W    |

| 000853н             | CAN1 - IF2 Data B1 High                          | IF2DTB1H1                    |                               | R/W    |

| 000854н             | CAN1 - IF2 Data B2 Low                           | IF2DTB2L1                    | IF2DTB21                      | R/W    |

| 000855н             | CAN1 - IF2 Data B2 High                          | IF2DTB2H1                    |                               | R/W    |

| 000856н-<br>00087Fн | Reserved                                         |                              |                               | -      |

| 000880н             | CAN1 - Transmission Request 1 Register Low       | TREQR1L1                     | TREQR11                       | R      |

| 000881н             | CAN1 - Transmission Request 1 Register High      | TREQR1H1                     |                               | R      |

| 000882н             | CAN1 - Transmission Request 2 Register Low       | TREQR2L1                     | TREQR21                       | R      |

| 000883н             | CAN1 - Transmission Request 2 Register High      | TREQR2H1                     |                               | R      |

| 000884н-<br>00088Fн | Reserved                                         |                              |                               | -      |

### **■ INTERRUPT VECTOR TABLE**

Interrupt vector table MB96(F)34x (1 of 4)

| Vector<br>number | Offset in vector table | Vector name | Cleared<br>by DMA | Index in ICR to program | Description            |

|------------------|------------------------|-------------|-------------------|-------------------------|------------------------|

| 0                | 3FСн                   | CALLV0      | No                | -                       |                        |

| 1                | 3F8н                   | CALLV1      | No                | -                       |                        |

| 2                | 3F4н                   | CALLV2      | No                | -                       |                        |

| 3                | 3F0н                   | CALLV3      | No                | -                       |                        |

| 4                | 3ЕСн                   | CALLV4      | No                | -                       |                        |

| 5                | 3Е8н                   | CALLV5      | No                | -                       |                        |

| 6                | 3Е4н                   | CALLV6      | No                | -                       |                        |

| 7                | 3Е0н                   | CALLV7      | No                | -                       |                        |

| 8                | 3DСн                   | RESET       | No                | -                       |                        |

| 9                | 3D8н                   | INT9        | No                | -                       |                        |

| 10               | 3D4н                   | EXCEPTION   | No                | -                       |                        |

| 11               | 3D0н                   | NMI         | No                | -                       | Non-Maskable Interrupt |

| 12               | 3ССн                   | DLY         | No                | 12                      | Delayed Interrupt      |

| 13               | 3С8н                   | RC_TIMER    | No                | 13                      | RC Timer               |

| 14               | 3С4н                   | MC_TIMER    | No                | 14                      | Main Clock Timer       |

| 15               | 3С0н                   | SC_TIMER    | No                | 15                      | Sub Clock Timer        |

| 16               | 3ВСн                   | RESERVED    | No                | 16                      | Reserved               |

| 17               | 3В8н                   | EXTINT0     | Yes               | 17                      | External Interrupt 0   |

| 18               | 3В4н                   | EXTINT1     | Yes               | 18                      | External Interrupt 1   |

| 19               | 3В0н                   | EXTINT2     | Yes               | 19                      | External Interrupt 2   |

| 20               | 3АСн                   | EXTINT3     | Yes               | 20                      | External Interrupt 3   |

| 21               | 3А8н                   | EXTINT4     | Yes               | 21                      | External Interrupt 4   |

| 22               | 3А4н                   | EXTINT5     | Yes               | 22                      | External Interrupt 5   |

| 23               | 3А0н                   | EXTINT6     | Yes               | 23                      | External Interrupt 6   |

| 24               | 39Сн                   | EXTINT7     | Yes               | 24                      | External Interrupt 7   |

| 25               | 398н                   | EXTINT8     | Yes               | 25                      | External Interrupt 8   |

| 26               | 394н                   | EXTINT9     | Yes               | 26                      | External Interrupt 9   |

| 27               | 390н                   | EXTINT10    | Yes               | 27                      | External Interrupt 10  |

## Interrupt vector table MB96(F)34x (4 of 4)

| Vector<br>number | Offset in vector ta- | Vector name | Cleared<br>by DMA | Index in<br>ICR to<br>program | Description                                     |

|------------------|----------------------|-------------|-------------------|-------------------------------|-------------------------------------------------|

| 83               | 2В0н                 | LINR2       | Yes               | 83                            | LIN USART 2 RX                                  |

| 84               | 2АСн                 | LINT2       | Yes               | 84                            | LIN USART 2 TX                                  |

| 85               | 2А8н                 | LINR3       | Yes               | 85                            | LIN USART 3 RX                                  |

| 86               | 2А4н                 | LINT3       | Yes               | 86                            | LIN USART 3 TX                                  |

| 87               | 2А0н                 | FLASH_A     | No                | 87                            | Flash memory A (only Flash devices)             |

| 88               | 29Сн                 | FLASH_B     | No                | 88                            | Flash memory B (only MB96F348T/H/C)             |

| 89               | 298н                 | LINR7       | Yes               | 89                            | LIN USART 7 RX                                  |

| 90               | 294н                 | LINT7       | Yes               | 90                            | LIN USART 7 TX                                  |

| 91               | 290н                 | LINR8       | Yes               | 91                            | LIN USART 8 RX                                  |

| 92               | 28Сн                 | LINT8       | Yes               | 92                            | LIN USART 8 TX                                  |

| 93               | 288н                 | LINR9       | Yes               | 93                            | LIN USART 9 RX                                  |

| 94               | 284н                 | LINT9       | Yes               | 94                            | LIN USART 9 TX                                  |

| 95               | 280н                 | RTC0        | No                | 95                            | Real Timer Clock                                |

| 96               | 27Сн                 | CAL0        | No                | 96                            | Clock Calibration Unit                          |

| 97               | 278н                 | DFLASH_A    | Yes               | 97                            | Data Flash A<br>(only MB96F345Dyy, MB96F345Fyy) |

#### 2. Opposite phase external clock

• When using an opposite phase external clock, X1 (X1A) must be supplied with a clock signal which has the opposite phase to the X0 (X0A) pins.

#### 4. Unused sub clock signal

If the pins X0A and X1A are not connected to an oscillator, a pull-down resistor must be connected on the X0A pin and the X1A pin must be left open.

#### 5. Notes on PLL clock mode operation

If the PLL clock mode is selected and no external oscillator is operating or no external clock is supplied, the microcontroller attempts to work with the free oscillating PLL. Performance of this operation, however, cannot be guaranteed.

#### 6. Power supply pins (Vcc/Vss)

It is required that all Vcc-level as well as all Vss-level power supply pins are at the same potential. If there is more than one Vcc or Vss level, the device may operate incorrectly or be damaged even within the guaranteed operating range.

Vcc and Vss must be connected to the device from the power supply with lowest possible impedance.

As a measure against power supply noise, it is required to connect a bypass capacitor of about 0.1  $\mu$ F between Vcc and Vss as close as possible to Vcc and Vss pins.

#### 7. Crystal oscillator and ceramic resonator circuit

Noise at X0, X1 pins or X0A, X1A pins might cause abnormal operation. It is required to provide bypass capacitors with shortest possible distance to X0, X1 pins and X0A, X1A pins, crystal oscillator (or ceramic resonator) and ground lines, and, to the utmost effort, that the lines of oscillation circuit do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0, X1 pins and X0A, X1A pins with a ground area for stabilizing the operation.

It is highly recommended to evaluate the quartz/MCU or resonator/MCU system at the quartz or resonator manufacturer, especially when using low-Q resonators at higher frequencies.

#### 8. Turn on sequence of power supply to A/D converter and analog inputs

It is required to turn the A/D converter power supply (AVcc, AVRH, AVRL) and analog inputs (ANn) on after turning the digital power supply (Vcc) on.

It is also required to turn the digital power off after turning the A/D converter supply and analog inputs off. In this case, the voltage must not exceed AVRH or AVcc (turning the analog and digital power supplies simultaneously on or off is acceptable).

#### 9. Pin handling when not using the A/D converter

It is required to connect the unused pins of the A/D converter as AVcc = Vcc, AVss = AVRH = AVRL = Vss.

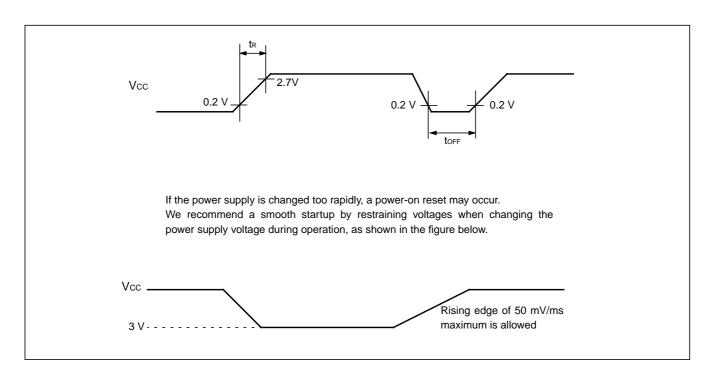

#### 10. Notes on Power-on

To prevent malfunction of the internal voltage regulator, supply voltage profile while turning the power supply on should be slower than  $50\mu s$  from  $0.2\ V$  to  $2.7\ V$ .

$(T_A = -40$ °C to 125°C,  $V_{CC} = AV_{CC} = 3.0$ V to 5.5V,  $V_{SS} = AV_{SS} = 0$ V)

| Doromotor          | Cymbal           | Din                     | Condition                       |       | Value |       | Unit  | Domorko                     |   |             |   |  |     |             |

|--------------------|------------------|-------------------------|---------------------------------|-------|-------|-------|-------|-----------------------------|---|-------------|---|--|-----|-------------|

| Parameter          | Symbol           | Pin                     | Condition                       | Min   | Тур   | Max   | Unit  | Remarks                     |   |             |   |  |     |             |

| Output H voltage   |                  |                         | 4.5V ≤ Vcc ≤ 5.5V               |       |       |       |       |                             |   |             |   |  |     |             |

|                    | V <sub>OH2</sub> | Normal                  | Iон = -2mA                      | Vcc - |       |       | V     | Driving strength set to 2mA |   |             |   |  |     |             |

|                    | V OH2            | outputs                 | 3.0V ≤ Vcc < 4.5V               | 0.5   | 0.5   | 0.5   | -     | -                           | V | (PODR:OD=1) |   |  |     |             |

|                    |                  |                         | Iон = -1.6mA                    |       |       |       |       |                             |   |             | , |  |     |             |

|                    |                  |                         | 4.5V ≤ Vcc ≤ 5.5V               |       |       |       |       |                             |   |             |   |  |     |             |

|                    | V <sub>OH5</sub> | Normal                  | Iон = -5mA                      | Vcc - |       |       | V     | Driving strength set to 5mA |   |             |   |  |     |             |

|                    | V OH5            | outputs                 | 3.0V ≤ Vcc < 4.5V               | 0.5   | -     | -   - | V     | (PODR:OD=0)                 |   |             |   |  |     |             |

|                    |                  |                         | Iон = -3mA                      |       |       |       |       | ,                           |   |             |   |  |     |             |

|                    |                  |                         | 4.5V ≤ Vcc ≤ 5.5V               |       |       |       | V     |                             |   |             |   |  |     |             |

|                    | Vонз             | 3mA out-<br>puts        | Iон = -3mA                      | Vcc - |       |       |       | I/O circuit type "N"        |   |             |   |  |     |             |

|                    | V OH3            |                         | 3.0V ≤ Vcc < 4.5V               | 0.5   | -     |       |       | 70 circuit type 11          |   |             |   |  |     |             |

|                    |                  |                         | Iон = -2mA                      |       |       |       |       |                             |   |             |   |  |     |             |

| Output L voltage   | Vois             | V <sub>OL2</sub> Normal | 4.5V ≤ Vcc ≤ 5.5V               | -     |       |       |       |                             |   |             |   |  |     |             |

|                    |                  |                         | IoL = +2mA                      |       | _     | - 0.4 | V     | Driving strength set to 2mA |   |             |   |  |     |             |

|                    | V OL2            | outputs                 | 3.0V ≤ Vcc < 4.5V               |       |       | - 0.4 |       |                             |   | 0.4         |   |  | 0.4 | (PODR:OD=1) |

|                    |                  |                         | IoL = +1.6mA                    |       |       |       |       |                             |   |             |   |  |     |             |

|                    |                  |                         | 4.5V ≤ Vcc ≤ 5.5V               |       |       |       |       |                             |   |             |   |  |     |             |

|                    | V <sub>OL5</sub> | Normal                  | IoL = +5mA                      | _     | _     | 0.4   | V     | Driving strength set to 5mA |   |             |   |  |     |             |

|                    | V OLS            | outputs                 | 3.0V ≤ Vcc < 4.5V               | _     | _     | 0.4   | \ \ \ | (PODR:OD=0)                 |   |             |   |  |     |             |

|                    |                  |                         | IoL = +3mA                      |       |       |       |       |                             |   |             |   |  |     |             |

|                    | V <sub>OL3</sub> | 3mA out-                | 3.0V ≤ Vcc ≤ 5.5V               | _     | _     | 0.4   | V     | I/O circuit type "N"        |   |             |   |  |     |             |

|                    | V OLS            | puts                    | IoL = +3mA                      |       |       | 0.4   | •     | "O on our type 14           |   |             |   |  |     |             |

|                    |                  |                         | Vss < Vı < Vcc                  |       |       |       |       |                             |   |             |   |  |     |             |

| Input leak current | Iı∟              | Pnn_m                   | AVss, AVRL < Vı <<br>AVcc, AVRH | -1    | -     | +1    | μΑ    | Single port pin             |   |             |   |  |     |             |

| Dull up resistance | Rup              | Pnn_m,                  | $Vcc = 3.3V \pm 10\%$           | 40    | 100   | 160   | kΩ    |                             |   |             |   |  |     |             |

| Pull-up resistance | <b>K</b> UP      | RSTX                    | $Vcc = 5.0V \pm 10\%$           | 25    | 50    | 100   | kΩ    |                             |   |             |   |  |     |             |

$(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, \text{ Vcc} = \text{AVcc} = 3.0 \text{V to } 5.5 \text{V}, \text{ Vss} = \text{AVss} = 0 \text{V})$

| Doromotor                   | Cumbal | Condition (at T <sub>A</sub> )                                                                                    |        | Value |      |        | Remarks              |  |

|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------|--------|-------|------|--------|----------------------|--|

| Parameter                   | Symbol |                                                                                                                   |        | Тур   | Max  | Unit   | Remarks              |  |

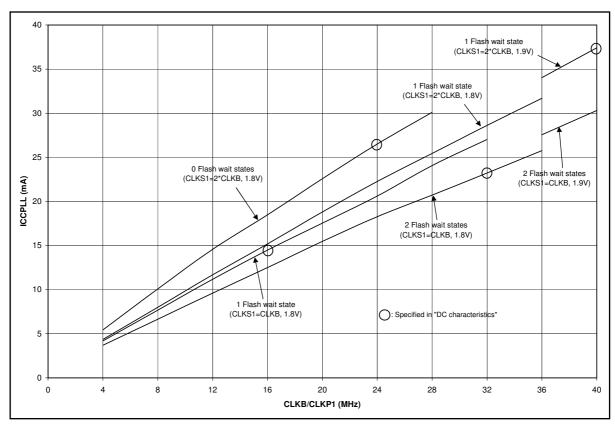

|                             |        |                                                                                                                   | +25°C  | 8     | 11   | mA     | MB96345/346          |  |

|                             |        |                                                                                                                   | +125°C | 8.5   | 13   | 1111/4 | WID90343/340         |  |

|                             |        | PLL Run mode with CLKS1/2 = CLKB =                                                                                | +25°C  | 15    | 20   | mA     | MB96F345             |  |

|                             |        | CLKP1 = 16MHz,<br>CLKP2 = 8MHz                                                                                    | +125°C | 16    | 23   | IIIA   | NID901 343           |  |

|                             |        | 1 Flash/ROM wait state                                                                                            | +25°C  | 17    | 22   | mA     | MB96F346/F347/F348Y/ |  |

|                             |        | (CLKRC and CLKSC stopped)                                                                                         | +125°C | 18.5  | 25.5 | IIIA   | R/Ayy                |  |

|                             |        |                                                                                                                   | +25°C  | 16    | 21   | mA     | MB96F348T/H/CyB/C    |  |

|                             |        |                                                                                                                   | +125°C | 17.5  | 24.5 | IIIA   | WIB90F3401/H/Cyb/C   |  |

|                             |        |                                                                                                                   | +25°C  | 14    | 18   | mA     | MB96345/346          |  |

|                             | Іссріі | PLL Run mode with CLKS1/2 = CLKB = CLKP1 = 32MHz, CLKP2 = 16MHz 2 Flash/ROM wait states (CLKRC and CLKSC stopped) | +125°C | 14.5  | 20   | IIIA   | WID90343/340         |  |

|                             |        |                                                                                                                   | +25°C  | 23.5  | 29.5 | mA     | MD06F24F             |  |

| Power supply current in Run |        |                                                                                                                   | +125°C | 25    | 32.5 |        | MB96F345             |  |

| modes*                      |        |                                                                                                                   | +25°C  | 26    | 32   | mA     | MB96F346/F347/F348Y/ |  |

|                             |        |                                                                                                                   | +125°C | 28    | 36   | IIIA   | R/Ayy                |  |

|                             |        |                                                                                                                   | +25°C  | 25    | 31   | mA     | MB96F348T/H/CyB/C    |  |

|                             |        |                                                                                                                   | +125°C | 27    | 35   | 1111/4 | WID90F3401/11/Cyb/C  |  |

|                             |        |                                                                                                                   | +25°C  | 13    | 17   | mA     | MB96345/346          |  |

|                             |        |                                                                                                                   | +125°C | 13.5  | 19   | 1111/4 | WID90343/340         |  |

|                             |        | PLL Run mode with CLKS1/2 = 48MHz,                                                                                | +25°C  | 27    | 39   | mΛ     | MB96F345             |  |

|                             |        | CLKB = CLKP1/2 = 24MHz                                                                                            | +125°C | 29    | 42   | mA     | WID90F343            |  |

|                             |        | 0 Flash/ROM wait states                                                                                           | +25°C  | 31    | 43   | m ^    | MB96F346/F347/F348Y/ |  |

|                             |        | (CLKRC and CLKSC stopped)                                                                                         | +125°C | 33    | 47   | mA     | R/Ayy                |  |

|                             |        | ,                                                                                                                 | +25°C  | 30    | 42   | m^     | MB96F348T/H/CyB/C    |  |

|                             |        |                                                                                                                   | +125°C | 32    | 46   | mA     | IVIDSUF3401/FI/CYD/C |  |

## **Internal Clock timing**

$(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, \text{ Vcc} = \text{AVcc} = 3.0 \text{V to } 5.5 \text{V}, \text{ Vss} = \text{AVss} = 0 \text{V})$

|                                                                                  |                | Core Voltage Settings |     |      |     |      |                   |  |

|----------------------------------------------------------------------------------|----------------|-----------------------|-----|------|-----|------|-------------------|--|

| Parameter                                                                        | Symbol         | 1.8V                  |     | 1.9V |     | Unit | Remarks           |  |

|                                                                                  |                | Min                   | Max | Min  | Max |      |                   |  |

| Internal System clock frequency (CLKS1 and CLKS2)                                | fclks1, fclks2 | 0                     | 92  | 0    | 96  | MHz  | Others than below |  |

|                                                                                  |                | 0                     | 86  | 0    | 96  | MHz  | MB96F348T/H/CxB/C |  |

|                                                                                  |                | 0                     | 72  | 0    | 80  | MHz  | MB96F345          |  |

|                                                                                  |                | 0                     | 68  | 0    | 74  | MHz  | MB96F34xY/R/Axx   |  |

| Internal CPU clock frequency (CLKB), internal peripheral clock frequency (CLKP1) | fськв, fськр1  | 0                     | 52  | 0    | 56  | MHz  | Others than below |  |

|                                                                                  |                | 0                     | 36  | 0    | 40  | MHz  | MB96F345          |  |

| Internal peripheral clock frequency (CLKP2)                                      | fclkp2         | 0                     | 28  | 0    | 32  | MHz  | Others than below |  |

|                                                                                  |                | 0                     | 26  | 0    | 28  | MHz  | MB96F34xY/R/Axx   |  |

## **Power On Reset timing**

$(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, V_{CC} = AV_{CC} = 3.0V \text{ to } 5.5V, V_{SS} = AV_{SS} = 0V)$

| Parameter          | Symbol     | Pin | Value |     |     | Unit  | Remarks |  |

|--------------------|------------|-----|-------|-----|-----|-------|---------|--|

| rarameter          | Зуппоп     |     | Min   | Тур | Max | Offic | Nemarks |  |

| Power on rise time | <b>t</b> R | Vcc | 0.05  | -   | 30  | ms    |         |  |

| Power off time     | toff       | Vcc | 1     | -   | 1   | ms    |         |  |

(TA = -40 °C to +125 °C, Vcc = 3.0 to 4.5V, Vss = 0.0 V, IOdrive = 5mA, CL = 50pF)

| Parameter                                         | Sym-           | Pin                   | Conditions                         | Va           | Unit         | D    |                        |  |

|---------------------------------------------------|----------------|-----------------------|------------------------------------|--------------|--------------|------|------------------------|--|

| Parameter                                         | bol            | Pin                   | Conditions                         | Min          | Max          | Unit | Remarks                |  |

| Valid address<br>⇒ RDX↓time                       | tavrl          | RDX, A[23:16]         | EACL:ACE=0                         | 3tcyc/2 - 20 | _            | nc   |                        |  |

|                                                   |                |                       | EACL:ACE=1                         | 5tcyc/2 - 20 | _            | ns   |                        |  |

|                                                   | <b>t</b> advrl | RDX, AD[15:0]         | EACL:ACE=0                         | tcyc - 20    | _            | 20   |                        |  |

|                                                   |                |                       | EACL:ACE=1                         | 2tcyc - 20   | _            | ns   |                        |  |

| Valid address<br>⇒ Valid data input               | tavdv          | A[23:16],<br>AD[15:0] | EACL:ACE=0                         | _            | 3tcyc - 60   | ne   | w/o cycle<br>extension |  |

|                                                   |                |                       | EACL:ACE=1                         | _            | 4tcyc - 60   | ns   |                        |  |

|                                                   | <b>t</b> advdv | AD[15:0]              | EACL:ACE=0                         | _            | 5tcyc/2 - 60 |      | w/o cycle<br>extension |  |

|                                                   |                |                       | EACL:ACE=1                         | _            | 7tcyc/2 - 60 | ns   |                        |  |

| RDX pulse width                                   | <b>t</b> rlrh  | RDX                   | _                                  | 3tcyc/2 - 8  | _            | ns   | w/o cycle<br>extension |  |

| $RDX \downarrow \Rightarrow Valid \ data \ input$ | <b>t</b> RLDV  | RDX, AD[15:0]         | _                                  |              | 3tcyc/2 - 55 | ns   | w/o cycle<br>extension |  |

| $RDX \uparrow \Rightarrow Data hold time$         | <b>t</b> RHDX  | RDX, AD[15:0]         |                                    | 0            |              | ns   |                        |  |

| Address valid ⇒ Data hold time                    | taxdx          | A[23:16]              | _                                  | 0            | _            | ns   |                        |  |

| $RDX \uparrow \Rightarrow ALE \uparrow time$      | trhlh RD       | RDX, ALE              | EACL:STS=1 and EACL:ACE=1          | 3tcyc/2 – 15 |              |      |                        |  |

|                                                   |                |                       | other ECL:STS,<br>EACL:ACE setting | tcyc/2 - 15  | _            | ns   |                        |  |

| Valid address                                     | <b>t</b> avch  | A[23:16], ECLK        |                                    | tcyc - 20    | — ns         |      |                        |  |

| ⇒ ECLK ↑ time                                     | tadvch         | AD[15:0], ECLK        | _                                  | tcyc/2 - 20  | _            | 1115 |                        |  |

| $RDX \downarrow \Rightarrow ECLK \uparrow time$   | <b>t</b> RLCH  | RDX, ECLK             | _                                  | tcyc/2 - 15  | _            | ns   |                        |  |

| ALE $↓$ ⇒ RDX $↓$ time                            | <b>t</b> LLRL  | ALE, RDX              | EACL:STS=0                         | tcyc/2 - 15  | _            | nc   |                        |  |

|                                                   |                |                       | EACL:STS=1                         | <b>– 15</b>  | _            | ns   |                        |  |

| ECLK↑ ⇒ Valid data input                          | tchdv          | AD[15:0], ECLK        |                                    |              | tcyc - 55    | ns   |                        |  |

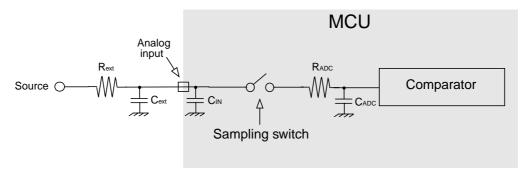

#### Accuracy and setting of the A/D Converter sampling time

If the external impedance is too high or the sampling time too short, the analog voltage charged to the internal sample and hold capacitor is insufficient, adversely affecting the A/D conversion precision.

To satisfy the A/D conversion precision, a sufficient sampling time must be selected. The required sampling time depends on the external driving impedance R<sub>ext</sub>, the board capacitance of the A/D converter input pin C<sub>ext</sub> and the AV<sub>cc</sub> voltage level. The following replacement model can be used for the calculation:

Rext: external driving impedance

$C_{\text{ext}}$ : capacitance of PCB at A/D converter input  $C_{\text{IN}}$ : capacitance of MCU input pin: 15pF (max)

Radc: resistance within MCU: 2.6k $\Omega$  (max) for  $4.5 V \le AV_{cc} \le 5.5 V$

$12k\Omega$  (max) for  $3.0V \le AV_{cc} < 4.5V$

CADC: sampling capacitance within MCU: 10pF (max)

The sampling time should be set to minimum " $7\tau$ ". The following approximation formula for the replacement model above can be used:

$$T_{\text{samp}} [min] = 7 \times (R_{\text{ext}} \times (C_{\text{ext}} + C_{\text{IN}}) + (R_{\text{ext}} + R_{\text{ADC}}) \times C_{\text{ADC}})$$

- Do not select a sampling time below the absolute minimum permitted value (0.5 $\mu$ s for 4.5V  $\leq$  AV $_{cc} \leq$  5.5V; 1.2  $\mu$ s for 3.0V  $\leq$  AV $_{cc} <$  4.5V).

- If the sampling time cannot be sufficient, connect a capacitor of about 0.1  $\mu$ F to the analog input pin. In this case the internal sampling capacitance C<sub>ADC</sub> will be charged out of this external capacitance.

- A big external driving impedance also adversely affects the A/D conversion precision due to the pin input leakage current I<sub>IL</sub> (static current before the sampling switch) or the analog input leakage current I<sub>AIN</sub> (total leakage current of pin input and comparator during sampling). The effect of the pin input leakage current I<sub>IL</sub> cannot be compensated by an external capacitor.

- The accuracy gets worse as |AVRH AVRL| becomes smaller.

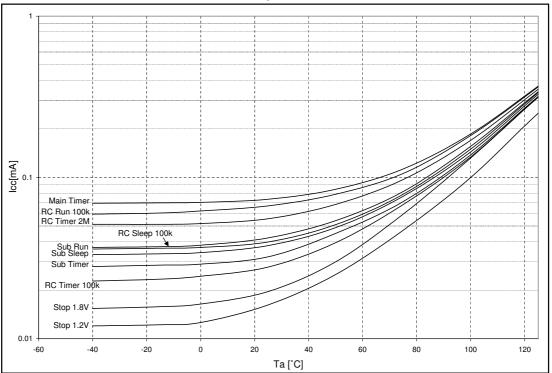

| Mode name     | Details                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

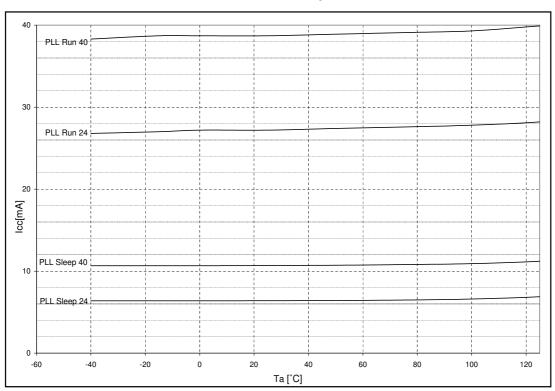

| PLL Sleep 48  | PLL Sleep mode current I <sub>CCSPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 96MHz  • f <sub>CLKP1</sub> = 48MHz  • f <sub>CLKP2</sub> = 24MHz  • Regulator in High Power Mode  • Core voltage at 1.9V (VRCR:HPM[1:0] = 11 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                |

| PLL Sleep 40  | PLL Sleep mode current I <sub>CCSPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 80MHz  • f <sub>CLKP1</sub> = 40MHz  • f <sub>CLKP2</sub> = 20MHz  • Regulator in High Power Mode  • Core voltage at 1.9V (VRCR:HPM[1:0] = 11 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                |

| PLL Sleep 36  | PLL Sleep mode current I <sub>CCSPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 72MHz  • f <sub>CLKP1</sub> = 36MHz  • f <sub>CLKP2</sub> = 18MHz  • Regulator in High Power Mode  • Core voltage at 1.9V (VRCR:HPM[1:0] = 11 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                |

| PLL Sleep 24  | PLL Sleep mode current I <sub>CCSPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 48MHz  • f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 24MHz  • Regulator in High Power Mode  • Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                         |

| Main Sleep    | Main Sleep mode current I <sub>CCSMAIN</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 4MHz  • Regulator in High Power Mode  • Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  • PLL, RC oscillator and Sub oscillator stopped                                                            |

| RC Sleep 2M   | RC Sleep mode current I <sub>CCSRCH</sub> with the following settings:  RC oscillator set to 2MHz (CKFCR:RCFS = 1)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 2MHz  Regulator in High Power Mode  Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped                         |

| RC Sleep 100k | RC Sleep mode current I <sub>CCSRCL</sub> with the following settings:  RC oscillator set to 100kHz (CKFCR:RCFS = 0)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 100kHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped |

| Mode name     | Details                                                                                                                                                                                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sub Sleep     | Sub Sleep mode current I <sub>CCSSUB</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 32kHz  • Regulator in Low Power Mode A (by hardware)  • Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  • PLL, RC oscillator and Main oscillator stopped |

| PLL Timer 48  | PLL Timer mode current I <sub>CCTPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 48MHz  • Regulator in High Power Mode  • Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                                  |

| Main Timer    | <ul> <li>Main Timer mode current I<sub>CCTMAIN</sub> with the following settings:</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 4MHz</li> <li>Regulator in Low Power Mode A (SMCR:LPMSS = 1)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, RC oscillator and Sub oscillator stopped</li> </ul> |

| RC Timer 2M   | RC Timer mode current I <sub>CCTRCH</sub> with the following settings:  RC oscillator set to 2MHz (CKFCR:RCFS = 1)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 2MHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped     |

| RC Timer 100k | RC Timer mode current I <sub>CCTRCL</sub> with the following settings:  RC oscillator set to 100kHz (CKFCR:RCFS = 0)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 100kHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped |

| Sub Timer     | Sub Timer mode current I <sub>CCTSUB</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 32kHz  • Regulator in Low Power Mode A (by hardware)  • Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  • PLL, RC oscillator and Main oscillator stopped                                           |

| Stop 1.8V     | Stop mode current I <sub>CCH</sub> with the following settings:  Regulator in Low Power Mode B (by hardware)  Core voltage at 1.8V (VRCR:LPMB[2:0] = 110 <sub>B</sub> )                                                                                                                                                            |

| Stop 1.2V     | Stop mode current I <sub>CCH</sub> with the following settings:  Regulator in Low Power Mode B (by hardware)  Core voltage at 1.2V (VRCR:LPMB[2:0] = 000 <sub>B</sub> )                                                                                                                                                            |

### MB96345/346 Low power mode currents

#### MB96F345 PLL Run and Sleep mode currents

### 2. Frequency dependency of power supply currents in PLL Run mode

The following diagrams show the current consumption of samples with typical wafer process parameters in PLL Run mode at different frequencies and Flash timing settings.

#### Measurement conditions:

- $V_{CC} = AV_{CC} = 5.0V$

- Ta = 25°C

- f<sub>CLKS1</sub> = f<sub>CLKB</sub> or f<sub>CLKS1</sub> = 2\*f<sub>CLKB</sub> as described in diagram

- f<sub>CLKS2</sub> = f<sub>CLKS1</sub>

- f<sub>CLKP1</sub> = f<sub>CLKB</sub>

- f<sub>CLKP2</sub> = f<sub>CLKB</sub>/2

- Core voltage at 1.8V (VRCR:HPM[1:0] = 10<sub>B</sub>) or 1.9V (VRCR:HPM[1:0] = 11<sub>B</sub>) as described in diagram

- Main clock = 4MHz external clock

- Flash memory timing settings:

- MTCRA=2128<sub>H</sub>/2208<sub>H</sub> (0 Flash wait states, f<sub>CLKS1</sub> = 2\*f<sub>CLKB</sub>)

- MTCRA=0239<sub>H</sub>/2129<sub>H</sub> (1 Flash wait state,  $f_{CLKS1} = f_{CLKB}$ )

- MTCRA= $4C09_H/6B09_H$  (1 Flash wait state,  $f_{CLKS1} = 2*f_{CLKB}$ )

- MTCRA=233A<sub>H</sub> (2 Flash wait states,  $f_{CLKS1} = f_{CLKB}$ )

- Average Flash access rate (number of read accesses to the Flash per CLKB clock cycle, no buffer hit):

- 0 Flash wait states: 0.5

- 1 Flash wait states: 0.33

- 2 Flash wait states: 0.25

#### MB96F345 PLL Run mode currents