Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga306-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: | DEVICE FEATURES FOR THE PIC24FJ128GA310 FAMILY: 80-PIN |

|------------|--------------------------------------------------------|

|            |                                                        |

| Features                                                               | PIC24FJ64GA308                                | PIC24FJ128GA308                                                                                   |  |  |

|------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| Operating Frequency                                                    | DC – 32 MHz                                   |                                                                                                   |  |  |

| Program Memory (bytes)                                                 | 64K                                           | 128K                                                                                              |  |  |

| Program Memory (instructions)                                          | 22,016                                        | 44,032                                                                                            |  |  |

| Data Memory (bytes)                                                    |                                               | 8K                                                                                                |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                         | 65                                            | (61/4)                                                                                            |  |  |

| I/O Ports                                                              | Ports A, B,                                   | C, D, E, F, G                                                                                     |  |  |

| Total I/O Pins                                                         |                                               | 69                                                                                                |  |  |

| Remappable Pins                                                        | 40 (31 I/Os                                   | , 9 input only)                                                                                   |  |  |

| Timers:                                                                |                                               |                                                                                                   |  |  |

| Total Number (16-bit)                                                  | !                                             | <sub>5</sub> (1)                                                                                  |  |  |

| 32-Bit (from paired 16-bit timers)                                     |                                               | 2                                                                                                 |  |  |

| Input Capture Channels                                                 | -                                             | 7 <sup>(1)</sup>                                                                                  |  |  |

| Output Compare/PWM Channels                                            |                                               | <sub>7</sub> (1)                                                                                  |  |  |

| Input Change Notification Interrupt                                    | 66                                            |                                                                                                   |  |  |

| Serial Communications:                                                 |                                               |                                                                                                   |  |  |

| UART                                                                   |                                               | 4(1)                                                                                              |  |  |

| SPI (3-wire/4-wire)                                                    | :                                             | 2 <sup>(1)</sup>                                                                                  |  |  |

| I <sup>2</sup> C™                                                      |                                               | 2                                                                                                 |  |  |

| Digital Signal Modulator                                               | Yes                                           |                                                                                                   |  |  |

| Parallel Communications (EPMP/PSP)                                     | Yes                                           |                                                                                                   |  |  |

| JTAG Boundary Scan                                                     | Yes                                           |                                                                                                   |  |  |

| 12/10-Bit Analog-to-Digital Converter<br>(ADC) Module (input channels) |                                               | 16                                                                                                |  |  |

| Analog Comparators                                                     |                                               | 3                                                                                                 |  |  |

| CTMU Interface                                                         | ``                                            | Yes                                                                                               |  |  |

| LCD Controller (available pixels)                                      | 368 (46 SI                                    | EG x 8 COM)                                                                                       |  |  |

| Resets (and Delays)                                                    | MCLR, WDT, Illegal Op<br>Hardware Traps, Conf | POR, BOR, RESET Instruction,<br>code, REPEAT Instruction,<br>iguration Word Mismatch<br>PLL Lock) |  |  |

| Instruction Set                                                        |                                               | le Addressing Mode Variations                                                                     |  |  |

| Packages                                                               | 80-Pin TQ                                     | FP and QFN                                                                                        |  |  |

Note 1: Peripherals are accessible through remappable pins.

# 2.4 Voltage Regulator Pin (VCAP)

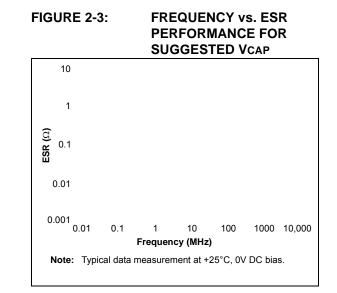

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the output voltage of the on-chip voltage regulator. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 32.0 "Electrical Characteristics"** for additional information.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

Refer to **Section 29.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

# TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### DC BIAS VOLTAGE vs. FIGURE 2-4: CAPACITANCE **CHARACTERISTICS** Change (%) 0 -10 16V Capacitor -20 -30 Capacitance -40 10V Capacitor -50 -60 -70 6.3V Capacitor

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V or 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

9 10 11 12 13

15 16

8

DC Bias Voltage (VDC)

# 2.5 ICSP Pins

2

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

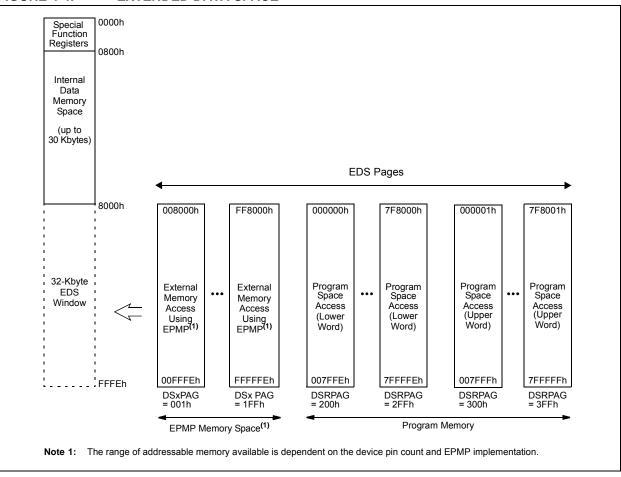

# 4.2.5 EXTENDED DATA SPACE (EDS)

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space, and any external memory through EPMP.

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.3.3 "Reading Data from Program Memory Using EDS".

Figure 4-4 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). The data addressing range of PIC24FJ128GA310 family devices depends on the version of the Enhanced Parallel Master Port implemented on a particular device; this is in turn a function of device pin count. Table 4-35 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to **"Enhanced Parallel Master Port (EPMP)"** (DS39730) in the *"dsPIC33/PIC24 Family Reference Manual"*.

| TABLE 4-35: | TOTAL ACCESSIBLE DATA |

|-------------|-----------------------|

|             | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGA310 | 8K              | Up to 16 MB                          |

| PIC24FJXXXGA308 | 8K              | Up to 64K                            |

| PIC24FJXXXGA306 | 8K              | Up to 64K                            |

**Note:** Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

### FIGURE 4-4: EXTENDED DATA SPACE

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, indicate the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test register, INTTREG, which displays the status of the interrupt controller. When an interrupt request occurs, it's associated vector number and the new Interrupt Priority Level are latched into INTTREG. This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors (such as when ISR remapping is used in bootloader applications) or to check if another interrupt is pending while in an ISR.

All interrupt registers are described in Register 8-1 through Register 8-44 in the succeeding pages.

#### **REGISTER 8-1:** SR: ALU STATUS REGISTER (IN CPU)

| U-0                               | U-0                   | U-0                   | U-0               | U-0              | U-0               | U-0              | R/W-0             |

|-----------------------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|-------------------|

| —                                 | —                     | —                     |                   | —                | —                 | _                | DC <sup>(1)</sup> |

| bit 15                            |                       |                       |                   |                  |                   |                  | bit 8             |

|                                   |                       |                       |                   |                  |                   |                  |                   |

| R/W-0                             | R/W-0                 | R/W-0                 | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0             |

| IPL2 <sup>(2,3)</sup>             | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup>  |

| bit 7                             |                       |                       |                   | •                |                   |                  | bit 0             |

|                                   |                       |                       |                   |                  |                   |                  |                   |

| Legend:                           |                       |                       |                   |                  |                   |                  |                   |

| R = Readable bit W = Writable bit |                       | bit                   | U = Unimpler      | mented bit, read | as '0'            |                  |                   |

|              |                |                                | · · · · · · · · · · · · · · · · · · · |                    |

|--------------|----------------|--------------------------------|---------------------------------------|--------------------|

| -n = Value a | at POR '       | 1' = Bit is set                | '0' = Bit is cleared                  | x = Bit is unknown |

|              |                |                                |                                       |                    |

| bit 15-9     | Unimplemente   | d: Read as '0'                 |                                       |                    |

| bit 7-5      | IPL<2:0>: CPU  | Interrupt Priority Lev         | /el Status bits <sup>(2,3)</sup>      |                    |

|              | 111 = CPU Inte | errupt Priority Level is       | s 7 (15); user interrupts are disa    | abled              |

|              | 110 = CPU Inte | errupt Priority Level is       | s 6 (14)                              |                    |

|              | 101 = CPU Inte | errupt Priority Level is       | s 5 (13)                              |                    |

|              |                | and the Date of the Law of the | - 4 (40)                              |                    |

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: See Register 3-1 for the description of the remaining bits (bits 8, 4, 3, 2, 1 and 0) that are not dedicated to interrupt control functions.

- 2: The IPLx bits are concatenated with the IPL3 (CORCON<3>) bit to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

| R/W-0         | R/W-0                                                                                              | R/W-0                            | R/W-0                 | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |

|---------------|----------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|-------------------|-----------------|-----------------|---------|--|--|

| U2TXIE        | U2RXIE                                                                                             | INT2IE <sup>(1)</sup>            | T5IE                  | T4IE              | OC4IE           | OC3IE           | DMA2IE  |  |  |

| bit 15        |                                                                                                    |                                  |                       |                   |                 |                 | bit 8   |  |  |

|               |                                                                                                    |                                  |                       |                   |                 |                 |         |  |  |

| U-0           | R/W-0                                                                                              | U-0                              | R/W-0                 | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |

| _             | IC7IE                                                                                              |                                  | INT1IE <sup>(1)</sup> | CNIE              | CMIE            | MI2C1IE         | SI2C1IE |  |  |

| bit 7         |                                                                                                    |                                  |                       |                   |                 |                 | bit (   |  |  |

| Legend:       |                                                                                                    |                                  |                       |                   |                 |                 |         |  |  |

| R = Readabl   | le bit                                                                                             | W = Writable                     | bit                   | U = Unimplen      | nented bit. rea | d as '0'        |         |  |  |

| -n = Value at | t POR                                                                                              | '1' = Bit is set                 |                       | '0' = Bit is clea |                 | x = Bit is unkn | iown    |  |  |

|               |                                                                                                    |                                  |                       |                   |                 |                 | -       |  |  |

| bit 15        | U2TXIE: UAF                                                                                        | RT2 Transmitte                   | Interrupt Enat        | ole bit           |                 |                 |         |  |  |

|               |                                                                                                    | request is enal                  | •                     |                   |                 |                 |         |  |  |

|               | 0 = Interrupt                                                                                      | request is not e                 | enabled               |                   |                 |                 |         |  |  |

| bit 14        |                                                                                                    | RT2 Receiver II                  | •                     | bit               |                 |                 |         |  |  |

|               |                                                                                                    | request is enal                  |                       |                   |                 |                 |         |  |  |

|               | •                                                                                                  | request is not o                 |                       |                   |                 |                 |         |  |  |

| bit 13        | INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup>                                             |                                  |                       |                   |                 |                 |         |  |  |

|               | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                  |                       |                   |                 |                 |         |  |  |

| bit 12        | T5IE: Timer5 Interrupt Enable bit                                                                  |                                  |                       |                   |                 |                 |         |  |  |

|               | 1 = Interrupt request is enabled                                                                   |                                  |                       |                   |                 |                 |         |  |  |

|               |                                                                                                    | request is not e                 |                       |                   |                 |                 |         |  |  |

| bit 11        | T4IE: Timer4                                                                                       | Interrupt Enab                   | le bit                |                   |                 |                 |         |  |  |

|               | 1 = Interrupt                                                                                      | request is enal                  | bled                  |                   |                 |                 |         |  |  |

|               | 0 = Interrupt                                                                                      | request is not e                 | enabled               |                   |                 |                 |         |  |  |

| bit 10        | OC4IE: Output Compare Channel 4 Interrupt Enable bit                                               |                                  |                       |                   |                 |                 |         |  |  |

|               | 1 = Interrupt request is enabled                                                                   |                                  |                       |                   |                 |                 |         |  |  |

|               | -                                                                                                  | request is not e                 |                       |                   |                 |                 |         |  |  |

| bit 9         | OC3IE: Output Compare Channel 3 Interrupt Enable bit                                               |                                  |                       |                   |                 |                 |         |  |  |

|               |                                                                                                    | request is enal request is not e |                       |                   |                 |                 |         |  |  |

| bit 8         | •                                                                                                  | •                                |                       | able hit          |                 |                 |         |  |  |

|               | DMA2IE: DMA Channel 2 Interrupt Flag Enable bit<br>1 = Interrupt request is enabled                |                                  |                       |                   |                 |                 |         |  |  |

|               |                                                                                                    | request is not e                 |                       |                   |                 |                 |         |  |  |

| bit 7         | Unimplemen                                                                                         | ted: Read as '                   | o'                    |                   |                 |                 |         |  |  |

| bit 6         | IC7IE: Input Capture Channel 7 Interrupt Enable bit                                                |                                  |                       |                   |                 |                 |         |  |  |

|               | 1 = Interrupt request is enabled                                                                   |                                  |                       |                   |                 |                 |         |  |  |

|               | 0 = Interrupt                                                                                      | request is not e                 | enabled               |                   |                 |                 |         |  |  |

| bit 5         | -                                                                                                  | ted: Read as '                   |                       |                   |                 |                 |         |  |  |

| bit 4         |                                                                                                    | rnal Interrupt 1                 |                       |                   |                 |                 |         |  |  |

|               |                                                                                                    | request is enal                  |                       |                   |                 |                 |         |  |  |

|               | 0 = Interrupt                                                                                      | request is not e                 | enabled               |                   |                 |                 |         |  |  |

pin. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

When the RTCC is enabled, it continues to operate with the same clock source (SOSC or LPRC) that was selected prior to entering VBAT mode. There is no provision to switch to a lower power clock source after the mode switch.

Since the loss of VDD is usually an unforeseen event, it is recommended that the contents of the Deep Sleep Semaphore registers be loaded with the data to be retained at an early point in code execution.

# 10.5.1 VBAT MODE WITH NO RTCC

By disabling RTCC operation during VBAT mode, power consumption is reduced to the lowest of all power-saving modes. In this mode, only the Deep Sleep Semaphore registers are maintained.

# 10.5.2 WAKE-UP FROM VBAT MODES

When VDD is restored to a device in VBAT mode, it automatically wakes. Wake-up occurs with a POR, after which the device starts executing code from the Reset vector. All SFRs, except the Deep Sleep Semaphores and RTCC registers are reset to their POR values. If the RTCC was not configured to run during VBAT mode, it will remain disabled and RTCC will not run. Wake-up timing is similar to that for a normal POR.

To differentiate a wake-up from VBAT mode from other POR states, check the VBAT status bit (RCON2<0>). If this bit is set while the device is starting to execute the code from Reset vector, it indicates that there has been an exit from VBAT mode. The application must clear the VBAT bit to ensure that future VBAT wake-up events are captured.

If a POR occurs without a power source connected to the VBAT pin, the VBPOR bit (RCON2<1>) is set. If this bit is set on a POR, it indicates that a battery needs to be connected to the VBAT pin.

In addition, if the VBAT power source falls below the level needed for Deep Sleep Semaphore operation while in VBAT mode (e.g., the battery has been drained), the VBPOR bit will be set. VBPOR is also set when the microcontroller is powered up the very first time, even if power is supplied to VBAT.

With VBPOR set, the user should clear it, and the next time, this bit will only set when VDD = 0 and the VBAT pin has gone below level VBTRST.

# 10.5.3 I/O PINS DURING VBAT MODES

All I/O pins should be maintained at Vss level; no I/O pins should be given VDD (refer to "**Absolute Maximum Ratings**" in **Section 32.0** "**Electrical Characteristics**") during VBAT mode. The only exceptions are the SOSCI and SOSCO pins, which maintain their states if the Secondary Oscillator is being used as the RTCC clock source. It is the user's responsibility to restore the I/O pins to their proper states, using the TRISx and LATx bits, once VDD has been restored.

# 10.5.4 SAVING CONTEXT DATA WITH THE DSGPRx REGISTERS

As with Deep Sleep mode, all SFRs are reset to their POR values after VDD has been restored. Only the Deep Sleep Semaphore registers are preserved. Applications which require critical data to be saved should save it in DSGPR0 and DSGPR1.

| Note: | If the VBAT mode is not used, the recommendation is to connect the VBAT pin to VDD and connect a $0.1 \mu$ F capacitor close to the VBAT pin to ground.                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | When the VBAT mode is used (connected to the battery), it is suggested to connect a 0.1 $\mu$ F capacitor from the VBAT pin to ground. The capacitor should be located very close to the VBAT pin. |

The BOR should be enabled for the reliable operation of the  $\ensuremath{\mathsf{VBAT}}$  .

# **REGISTER 11-5:** ANSE: PORTE ANALOG FUNCTION SELECTION REGISTER<sup>(1)</sup>

| U-0                                | U-0   | U-0    | U-0                                     | U-0 | U-0 | R/W-1                | U-0   |

|------------------------------------|-------|--------|-----------------------------------------|-----|-----|----------------------|-------|

| _                                  |       | —      |                                         |     |     | ANSE9 <sup>(2)</sup> | _     |

| bit 15                             |       |        |                                         |     |     |                      | bit 8 |

| R/W-1                              | R/W-1 | R/W-1  | R/W-1                                   | U-0 | U-0 | U-0                  | U-0   |

|                                    |       | E<7:4> |                                         | -   | _   | -                    | _     |

| bit 7                              |       |        |                                         |     |     |                      | bit 0 |

| Legend:                            |       |        |                                         |     |     |                      |       |

| R = Readable bit W = Writable bit  |       |        | U = Unimplemented bit, read as '0'      |     |     |                      |       |

| -n = Value at POR '1' = Bit is set |       |        | '0' = Bit is cleared x = Bit is unknown |     |     | own                  |       |

| bit 9   | ANSE9: Analog Function Selection bit <sup>(2)</sup>                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 8   | Unimplemented: Read as '0'                                                                                                                                   |

| bit 7-4 | ANSE<7:4>: Analog Function Selection bits <sup>(1)</sup>                                                                                                     |

|         | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                   |

# **Note 1:** This register is not available in 64-pin and 80-pin devices.

2: This bit is unimplemented on 64-pin devices. In 80-pin devices, this bit needs to be cleared to get digital functionality on RE9.

# REGISTER 11-6: ANSG: PORTG ANALOG FUNCTION SELECTION REGISTER

| U-0                                | U-0   | U-0            | U-0                                     | U-0          | U-0              | R/W-1            | R/W-1  |

|------------------------------------|-------|----------------|-----------------------------------------|--------------|------------------|------------------|--------|

| _                                  |       | —              | _                                       | —            | —                | ANSC             | 6<9:8> |

| bit 15                             |       |                |                                         |              |                  |                  | bit 8  |

|                                    |       |                |                                         |              |                  |                  |        |

| R/W-1                              | R/W-1 | U-0            | U-0                                     | U-0          | U-0              | U-0              | U-0    |

| ANSG<7:6>                          |       | —              | —                                       | —            | —                | —                | —      |

| bit 7                              |       |                |                                         |              |                  |                  | bit 0  |

|                                    |       |                |                                         |              |                  |                  |        |

| Legend:                            |       |                |                                         |              |                  |                  |        |

| R = Readable                       | e bit | W = Writable b | oit                                     | U = Unimplem | nented bit, read | l as '0'         |        |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unknown |              |                  | nown             |        |

| bit 15-10                          |       | ted: Read as ' | , 1                                     |              | areu             | x – dit is uliki | IUWII  |

| Dit 15-10 | Unimplemented: Read as "0"                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-6   | ANSG<9:6>: Analog Function Selection bits                                                                                                                    |

|           | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 5-0   | Unimplemented: Read as '0'                                                                                                                                   |

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Serial Peripheral Interface (SPI)" (DS39699) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

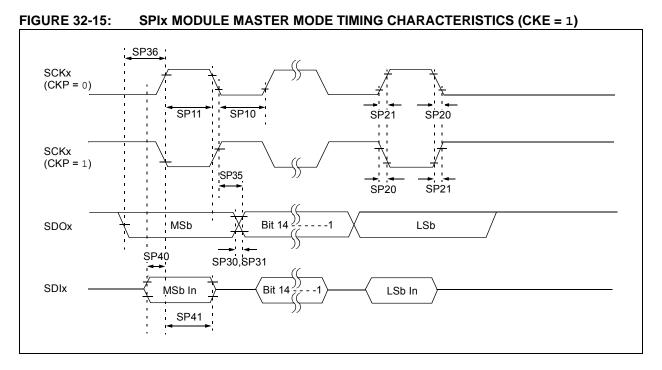

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces. All PIC24FJ128GA310 family devices include two SPI modules.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 16-1 and Figure 16-2.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 or SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the 2 SPI modules.

| REGISTER 16-1: | SPIxSTAT: SPIx STATUS AND CONTROL REGISTER |

|----------------|--------------------------------------------|

|----------------|--------------------------------------------|

| R/W-0                | U-0                                                                                                                                                                   | R/W-0                                   | U-0             | U-0                 | R-0, HSC         | R-0, HSC           | R-0, HSC     |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|---------------------|------------------|--------------------|--------------|--|--|

| SPIEN <sup>(1)</sup> |                                                                                                                                                                       | SPISIDL                                 | _               | _                   | SPIBEC2          | SPIBEC1            | SPIBEC0      |  |  |

| bit 15               |                                                                                                                                                                       |                                         |                 |                     |                  |                    | bit 8        |  |  |

|                      |                                                                                                                                                                       |                                         |                 |                     |                  |                    |              |  |  |

| R-0, HSC             | R/C-0, HS                                                                                                                                                             | R-0, HSC                                | R/W-0           | R/W-0               | R/W-0            | R-0, HSC           | R-0, HSC     |  |  |

| SRMPT                | SPIROV                                                                                                                                                                | SRXMPT                                  | SISEL2          | SISEL1              | SISEL0           | SPITBF             | SPIRBF       |  |  |

| bit 7                | ·                                                                                                                                                                     |                                         |                 | ·                   |                  | ·                  | bit (        |  |  |

|                      |                                                                                                                                                                       |                                         |                 |                     |                  |                    |              |  |  |

| Legend:              |                                                                                                                                                                       | C = Clearable                           | bit             | HS = Hardwa         | re Settable bit  |                    |              |  |  |

| R = Readable         | e bit                                                                                                                                                                 | W = Writable                            | bit             | U = Unimpler        | nented bit, read | d as '0'           |              |  |  |

| -n = Value at        | POR                                                                                                                                                                   | '1' = Bit is set                        |                 | '0' = Bit is cle    | ared             | x = Bit is unkr    | nown         |  |  |

| HSC = Hardw          | vare Settable/C                                                                                                                                                       | learable bit                            |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       |                                         |                 |                     |                  |                    |              |  |  |

| bit 15               | SPIEN: SPIX                                                                                                                                                           | Enable bit <sup>(1)</sup>               |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | module and co                           | nfigures SCKx   | , SDOx, SDIx a      | and SSx as ser   | ial port pins      |              |  |  |

|                      | 0 = Disables                                                                                                                                                          |                                         |                 |                     |                  |                    |              |  |  |

| bit 14               | -                                                                                                                                                                     | ted: Read as 'o                         |                 |                     |                  |                    |              |  |  |

| bit 13               | <b>SPISIDL:</b> SPIx Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode                                                          |                                         |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | iues module op<br>s module opera        |                 |                     | dle mode         |                    |              |  |  |

| bit 12-11            | Unimplemented: Read as '0'                                                                                                                                            |                                         |                 |                     |                  |                    |              |  |  |

| bit 10-8             | SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)                                                                                           |                                         |                 |                     |                  |                    |              |  |  |

|                      | Master mode:<br>Number of SPI transfers pending.                                                                                                                      |                                         |                 |                     |                  |                    |              |  |  |

|                      | <u>Slave mode:</u><br>Number of SF                                                                                                                                    | PI transfers unre                       | ead.            |                     |                  |                    |              |  |  |

| bit 7                | SRMPT: SPIX                                                                                                                                                           | Shift Register                          | (SPIxSR) Emp    | oty bit (valid in l | Enhanced Buff    | er mode)           |              |  |  |

|                      |                                                                                                                                                                       | ft register is em<br>ft register is not |                 | to send or rece     | eive             |                    |              |  |  |

| bit 6                |                                                                                                                                                                       | •                                       |                 |                     |                  |                    |              |  |  |

|                      | <b>SPIROV:</b> SPIx Receive Overflow Flag bit<br>1 = A new byte/word is completely received and discarded; the user software has not read the previous                |                                         |                 |                     |                  |                    |              |  |  |

|                      | data in the SPIxBUF register                                                                                                                                          |                                         |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | ow has occurre                          |                 |                     |                  |                    |              |  |  |

| bit 5                | SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)                                                                                                   |                                         |                 |                     |                  |                    |              |  |  |

|                      | <ul> <li>1 = Receive FIFO is empty</li> <li>0 = Receive FIFO is not empty</li> </ul>                                                                                  |                                         |                 |                     |                  |                    |              |  |  |

| bit 4-2              |                                                                                                                                                                       |                                         |                 | its (valid in Enh   | anced Buffer n   | node)              |              |  |  |

|                      | <b>SISEL&lt;2:0&gt;:</b> SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)<br>111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set) |                                         |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | •                                       |                 | •                   | ,                | TX FIFO is emp     | ty           |  |  |

|                      |                                                                                                                                                                       | pt when the las                         |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | pt when one da<br>pt when the SP        |                 |                     |                  | e TX FIFO has      | one open spo |  |  |

|                      |                                                                                                                                                                       | pt when the SF                          |                 |                     |                  |                    |              |  |  |

|                      |                                                                                                                                                                       | pt when data is                         |                 |                     |                  | s set)             |              |  |  |

|                      |                                                                                                                                                                       | •                                       | data in the red | ceive buffer is re  | ead; as a result | , the buffer is en | npty (SRXMP  |  |  |

|                      | bit is se                                                                                                                                                             | et)                                     |                 |                     |                  |                    |              |  |  |

| Note 1. If           | SPIEN = 1 the                                                                                                                                                         | se functions mu                         | et he assigned  | to available R      | Pn/RPIn nins h   | efore use. See     | Section 11   |  |  |

Note 1: If SPIEN = 1, these functions must be assigned to available RPn/RPIn pins before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

NOTES:

### REGISTER 20-9: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| Legend:R = Readable bitW = Writable bit |     |     | oit | U = Unimplem | ented bit, read | as '0' |        |

|-----------------------------------------|-----|-----|-----|--------------|-----------------|--------|--------|

| bit 7                                   |     |     |     |              |                 |        | bit 0  |

| —                                       | —   | —   |     |              | _               |        | PMPTTL |

| U-0                                     | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | R/W-0  |

|                                         |     |     |     |              |                 |        |        |

| bit 15                                  |     |     |     |              |                 |        | bit 8  |

| —                                       | —   | —   |     | _            | _               |        | —      |

| U-0                                     | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | U-0    |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 Unimplemented: Read as '0'

bit 0

- PMPTTL: EPMP Module TTL Input Buffer Select bit

- 1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

# 22.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

### 22.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 22-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 22-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |

|-------------|----------------------------|-------------|--|--|--|

| KIGPIK(I.0> | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |

| 11          | —                          | YEAR        |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 22-2).

By writing the ALRMVALH byte, the Alarm Pointer value, ALRMPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 22-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |

|---------|-----------------------------|--------------|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |

| 11      | —                           | —            |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

# 22.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL1<13>) must be set (see Example 22-1).

| Note: | To avoid accidental writes to the timer, it is<br>recommended that the RTCWREN bit<br>(RCFGCAL1<13>) is kept clear at any<br>other time. For the RTCWREN bit to be<br>set, there is only one instruction cycle time |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | window allowed between the 55h/AA sequence and the setting of RTCWREN; therefore, it is recommended that code follow the procedure in Example 22-1.                                                                 |

# 22.2.3 SELECTING RTCC CLOCK SOURCE

The clock source for the RTCC module can be selected using the RTCLK<1:0> bits in the RTCPWC register. When the bits are set to '00', the Secondary Oscillator (SOSC) is used as the reference clock and when the bits are '01', LPRC is used as the reference clock. When RTCLK<1:0> = 10 and 11, the external power line (50 Hz and 60 Hz) is used as the clock source.

### EXAMPLE 22-1: SETTING THE RTCWREN BIT

```

asm volatile("push w7");

asm volatile("push w8");

asm volatile("disi #5");

asm volatile("mov #0x55, w7");

asm volatile("mov w7, _NVMKEY");

asm volatile("mov #0xAA, w8");

asm volatile("mov w8, _NVMKEY");

asm volatile("bset _RCFGCAL1, #13"); //set the RTCWREN bit

asm volatile("pop w8");

asm volatile("pop w7");

```

# **REGISTER 22-1:** RCFGCAL: RTCC CALIBRATION/CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

```

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

01111111 = Maximum positive adjustment; adds 127 RTC clock pulses every 15 seconds

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

<li

```

- Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### REGISTER 24-6: AD1CHS: ADC1 SAMPLE SELECT REGISTER (CONTINUED)

- bit 7-5 **CH0NA<2:0>:** Sample A Channel 0 Negative Input Select bits Same definitions as for CHONB<2:0>.

- bit 4-0 **CH0SA<4:0>:** Sample A Channel 0 Positive Input Select bits Same definitions as for CHOSB<4:0>.

- Note 1: These input channels do not have corresponding memory-mapped result buffers.

- 2: These channels are implemented in 100-pin devices only.

### REGISTER 24-7: ANCFG: ADC BAND GAP REFERENCE CONFIGURATION REGISTER

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|

| —            | —   | —   | —   | —   | —   | —   | _   |

| bit 15 bit 8 |     |     |     |     |     |     |     |

|              |     |     |     |     |     |     |     |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0 |

|-------|-----|-----|-----|-----|--------|--------|-------|

| —     | —   | —   | —   | —   | VBG6EN | VBG2EN | VBGEN |

| bit 7 |     |     |     |     |        |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-3<br>bit 2 | Unimplemented: Read as '0'<br>VBG6EN: ADC Input VBG/6 Enable bit<br>1 = Band gap voltage, divided by six reference (VBG/6), is enabled                      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 0 = Band gap, divided by six reference (VBG/6), is disabled                                                                                                 |

| bit 1             | VBG2EN: ADC Input VBG/2 Enable bit                                                                                                                          |

|                   | <ul> <li>1 = Band gap voltage, divided by two reference (VBG/2), is enabled</li> <li>0 = Band gap, divided by two reference (VBG/2), is disabled</li> </ul> |

| bit 0             | VBGEN: ADC Input VBG Enable bit                                                                                                                             |

|                   | <ul> <li>1 = Band gap voltage reference (VBG) is enabled</li> <li>0 = Band gap reference (VBG) is disabled</li> </ul>                                       |

| Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| ADD                  | ADD f |                 | f = f + WREG                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C, DC, N, OV, Z          |

| ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + Iit5 + (C)                     | 1             | 1              | C, DC, N, OV, Z          |

| AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N, Z                     |

|                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N, Z                     |

|                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N, Z                     |

|                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N, Z                     |

|                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N, Z                     |

| ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N, Z                     |

|                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N, Z                     |

| BCLR                 | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1              | None                     |

| DODIC                | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1              | None                     |

| BRA                  | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)          | None                     |

|                      | BRA   | GE, Expr        | Branch if Greater than or Equal          | 1             | 1 (2)          | None                     |

|                      | BRA   | GEU, Expr       | Branch if Unsigned Greater than or Equal | 1             | 1 (2)          | None                     |

|                      | BRA   | GT, Expr        | Branch if Greater than                   | 1             | 1 (2)          | None                     |

|                      | BRA   | GTU, Expr       | Branch if Unsigned Greater than          | 1             | 1 (2)          | None                     |

|                      | BRA   | LE, Expr        | Branch if Less than or Equal             | 1             | 1 (2)          | None                     |

|                      | BRA   | LEU, Expr       | Branch if Unsigned Less than or Equal    | 1             | 1 (2)          | None                     |

|                      | BRA   | LT, Expr        | Branch if Less than                      | 1             | 1 (2)          | None                     |

|                      | BRA   |                 | Branch if Unsigned Less than             | 1             | 1 (2)          | None                     |

|                      | BRA   | LTU, Expr       | Branch if Negative                       | 1             |                | None                     |

|                      |       | N, Expr         | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                      | BRA   | NC, Expr        |                                          |               | 1 (2)          |                          |

|                      | BRA   | NN, Expr        | Branch if Not Negative                   | 1             | 1 (2)          | None<br>None             |

|                      | BRA   | NOV,Expr        | Branch if Not Overflow                   | 1             | 1 (2)          |                          |

|                      | BRA   | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                      | BRA   | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                      | BRA   | Expr            | Branch Unconditionally                   | 1             | 2              | None                     |

|                      | BRA   | Z,Expr          | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                      | BRA   | Wn              | Computed Branch                          | 1             | 2              | None                     |

| BSET                 | BSET  | f,#bit4         | Bit Set f                                | 1             | 1              | None                     |

|                      | BSET  | Ws,#bit4        | Bit Set Ws                               | 1             | 1              | None                     |

| BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |