Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga306t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

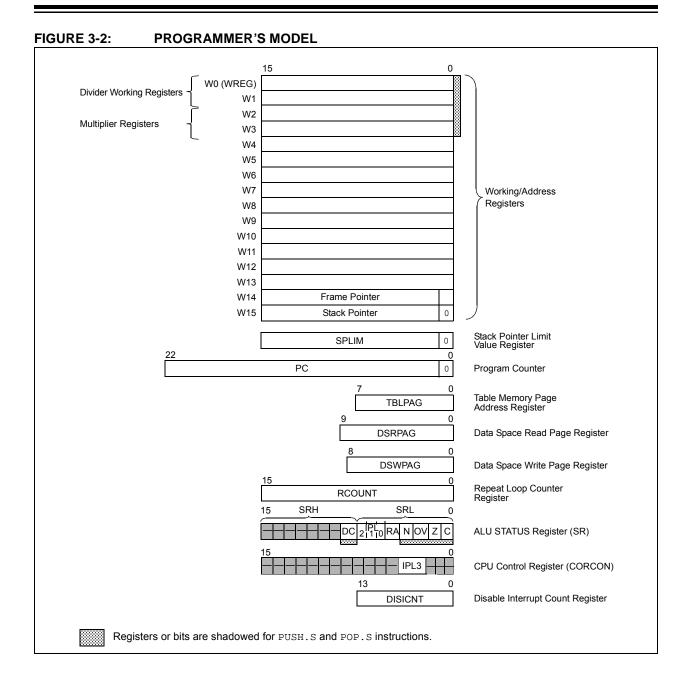

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space during code execution.

### 4.1 **Program Memory Space**

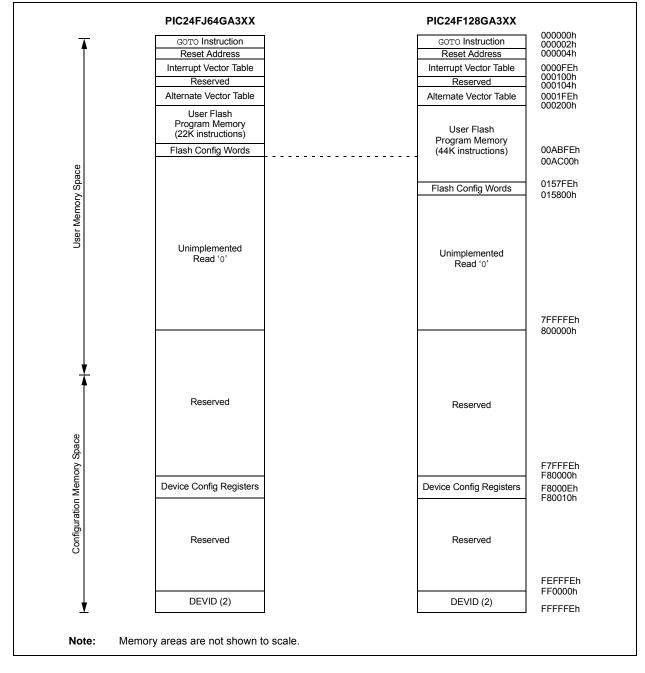

The program address memory space of the PIC24FJ128GA310 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.3** "Interfacing **Program and Data Memory Spaces**".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ128GA310 family of devices are shown in Figure 4-1.

#### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ128GA310 FAMILY DEVICES

#### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 **CNIE:** Input Change Notification Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

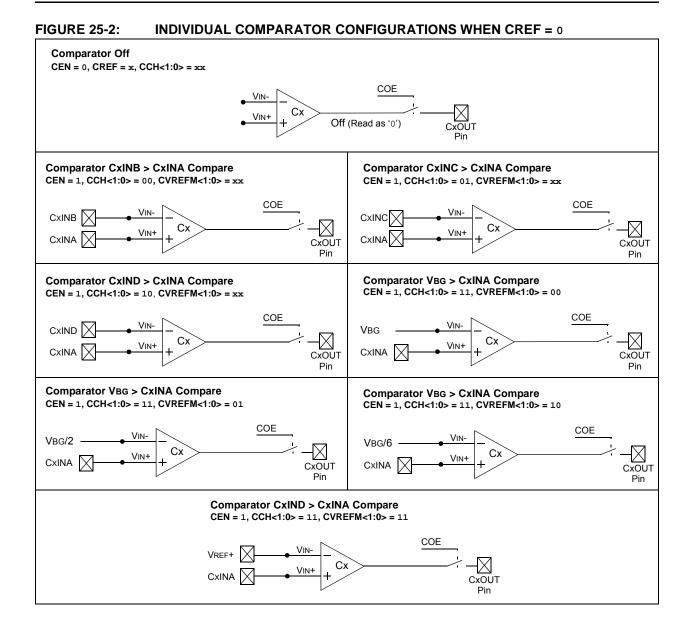

- bit 2 **CMIE:** Comparator Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 1 MI2C1IE: Master I2C1 Event Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 SI2C1IE: Slave I2C1 Event Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- Note 1: If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

#### REGISTER 8-31: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

|               |               |                                       |                   |                    | D/A/ 4           |                 |        |  |  |  |  |

|---------------|---------------|---------------------------------------|-------------------|--------------------|------------------|-----------------|--------|--|--|--|--|

| U-0           | R/W-1         | R/W-0                                 | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

|               | OC7IP2        | OC7IP1                                | OC7IP0            |                    | OC6IP2           | OC6IP1          | OC6IP0 |  |  |  |  |

| bit 15        |               |                                       |                   |                    |                  |                 | bit 8  |  |  |  |  |

|               |               | DAMO                                  | <b>D</b> /// 0    |                    |                  |                 |        |  |  |  |  |

| U-0           | R/W-1         | R/W-0                                 | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

| -             | OC5IP2        | OC5IP1                                | OC5IP0            | —                  | IC6IP2           | IC6IP1          | IC6IP0 |  |  |  |  |

| bit 7         |               |                                       |                   |                    |                  |                 | bit 0  |  |  |  |  |

| Legend:       |               |                                       |                   |                    |                  |                 |        |  |  |  |  |

| R = Readabl   | le hit        | W = Writable                          | hit               | U = Unimplen       | nented bit, read | 1 as '0'        |        |  |  |  |  |

| -n = Value at |               | '1' = Bit is set                      |                   | '0' = Bit is clea  |                  | x = Bit is unkr | nown   |  |  |  |  |

|               |               |                                       |                   |                    | area             |                 | IOWIT  |  |  |  |  |

| bit 15        | Unimplemen    | ted: Read as '                        | )'                |                    |                  |                 |        |  |  |  |  |

| bit 14-12     | -             |                                       |                   | Interrupt Priority | v bits           |                 |        |  |  |  |  |

|               |               | pt is Priority 7 (                    |                   |                    | ,                |                 |        |  |  |  |  |

|               | •             | , , , , , , , , , , , , , , , , , , , | 5 , ,             | 1,                 |                  |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | •             | 001 = Interrupt is Priority 1         |                   |                    |                  |                 |        |  |  |  |  |

|               |               | pt is Phonity 1<br>pt source is dis   | abled             |                    |                  |                 |        |  |  |  |  |

| bit 11        |               | ted: Read as '                        |                   |                    |                  |                 |        |  |  |  |  |

| bit 10-8      | •             |                                       |                   | Interrupt Priority | v hits           |                 |        |  |  |  |  |

|               |               | pt is Priority 7 (                    |                   |                    | , 510            |                 |        |  |  |  |  |

|               | •             | , , , , , , , , , , , , , , , , , , , |                   |                    |                  |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | •             | at is Daisaits 4                      |                   |                    |                  |                 |        |  |  |  |  |

|               | 001 = Interru | pt is Priority 1<br>pt source is dis  | abled             |                    |                  |                 |        |  |  |  |  |

| bit 7         | -             | ted: Read as '                        |                   |                    |                  |                 |        |  |  |  |  |

| bit 6-4       | -             |                                       |                   | Interrupt Priority | v hite           |                 |        |  |  |  |  |

|               |               | pt is Priority 7 (                    |                   | • •                | y 013            |                 |        |  |  |  |  |

|               | •             |                                       | inglicet priority | (interrupt)        |                  |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | •             | •                                     |                   |                    |                  |                 |        |  |  |  |  |

|               | 001 = Interru | pt is Priority 1<br>pt source is dis  | ahled             |                    |                  |                 |        |  |  |  |  |

| bit 3         | -             | ted: Read as '                        |                   |                    |                  |                 |        |  |  |  |  |

| bit 2-0       | -             |                                       |                   | rupt Priority bits | 3                |                 |        |  |  |  |  |

| Dit Z U       |               | pt is Priority 7 (                    |                   |                    | 5                |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | •             |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               | 001 = Interru | pt is Priority 1<br>pt source is dis  | ahlad             |                    |                  |                 |        |  |  |  |  |

|               |               |                                       |                   |                    |                  |                 |        |  |  |  |  |

|               |               |                                       |                   |                    |                  |                 |        |  |  |  |  |

REGISTER 8-36:

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 CRCIP2 CRCIP1 CRCIP0 U2ERIP1 U2ERIP0 U2ERIP2 \_ \_\_\_\_ bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U1ERIP2 U1ERIP1 U1ERIP0 \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 CRCIP<2:0>: CRC Generator Error Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 U2ERIP<2:0>: UART2 Error Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' bit 6-4 U1ERIP<2:0>: UART1 Error Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled Unimplemented: Read as '0' bit 3-0

**IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16**

| U-0              | R/W-1                                                                 | R/W-0                                                                       | R/W-0                                                 | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|

| _                | U3TXIP2                                                               | U3TXIP1                                                                     | U3TXIP0                                               | _                 | U3RXIP2          | U3RXIP1         | U3RXIP0 |  |  |  |

| bit 15           |                                                                       |                                                                             |                                                       |                   |                  |                 | bit 8   |  |  |  |

| U-0              | R/W-1                                                                 | R/W-0                                                                       | R/W-0                                                 | U-0               | U-0              | U-0             | U-0     |  |  |  |

| 0-0              | U3ERIP2                                                               | U3ERIP1                                                                     | U3ERIP0                                               | 0-0               | 0-0              | 0-0             | 0-0     |  |  |  |

| <br>bit 7        | U3ERIP2                                                               | USERIPI                                                                     | USERIPU                                               | _                 | _                | _               | bit (   |  |  |  |

|                  |                                                                       |                                                                             |                                                       |                   |                  |                 | bit (   |  |  |  |

| Legend:          |                                                                       |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

| R = Readab       | ole bit                                                               | W = Writable                                                                | bit                                                   | U = Unimplem      | nented bit, read | as '0'          |         |  |  |  |

| -n = Value a     | at POR                                                                | '1' = Bit is set                                                            |                                                       | '0' = Bit is clea | ared             | x = Bit is unkn | iown    |  |  |  |

|                  |                                                                       |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

| bit 15           | Unimplemen                                                            | ted: Read as '                                                              | )'                                                    |                   |                  |                 |         |  |  |  |

| bit 14-12        | U3TXIP<2:0>                                                           | : UART3 Trans                                                               | mitter Interrup                                       | ot Priority bits  |                  |                 |         |  |  |  |

|                  | <pre>111 = Interrupt is Priority 7 (highest priority interrupt)</pre> |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | •                                                                     |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  |                                                                       |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | 001 = Interru                                                         | ot is Priority 1                                                            |                                                       |                   |                  |                 |         |  |  |  |

|                  | 000 = Interru                                                         | ot source is dis                                                            | abled                                                 |                   |                  |                 |         |  |  |  |

| bit 11           | Unimplemen                                                            | ted: Read as '                                                              | )'                                                    |                   |                  |                 |         |  |  |  |

| bit 10-8         | U3RXIP<2:0>: UART3 Receiver Interrupt Priority bits                   |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | 111 = Interrupt is Priority 7 (highest priority interrupt)            |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | •                                                                     |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | •                                                                     |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1                                    |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | 001 = Interrup                                                        | ot is Priority 1                                                            |                                                       |                   |                  |                 |         |  |  |  |

|                  |                                                                       | ot is Priority 1<br>ot source is dis                                        | abled                                                 |                   |                  |                 |         |  |  |  |

| bit 7            | 000 = Interru                                                         |                                                                             |                                                       |                   |                  |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen                                           | ot source is dis                                                            | )'                                                    | rity bits         |                  |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                            | ot source is dis<br>ted: Read as '(                                         | )'<br>Interrupt Prior                                 |                   |                  |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                            | ot source is dis<br>ted: Read as '(<br>-: UART3 Error                       | )'<br>Interrupt Prior                                 |                   |                  |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                            | ot source is dis<br>ted: Read as '(<br>-: UART3 Error                       | )'<br>Interrupt Prior                                 |                   |                  |                 |         |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                            | ot source is dis<br>ted: Read as '(<br>:: UART3 Error<br>ot is Priority 7 ( | )'<br>Interrupt Prior                                 |                   |                  |                 |         |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>U3ERIP<2:0><br>111 = Interrup         | ot source is dis<br>ted: Read as '(<br>:: UART3 Error<br>ot is Priority 7 ( | <sub>)</sub> ,<br>Interrupt Prior<br>highest priority |                   |                  |                 |         |  |  |  |

#### REGISTER 8-39: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0                         | U-0                                                                         | U-0                                                                                                           | U-0                             | U-0                                     | U-0              | U-0     | U-0     |

|-----------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|------------------|---------|---------|

| _                           | —                                                                           | —                                                                                                             | —                               | —                                       | —                | —       | —       |

| bit 15                      |                                                                             |                                                                                                               |                                 |                                         | •                |         | bit 8   |

|                             |                                                                             |                                                                                                               |                                 |                                         |                  |         |         |

| U-0                         | R/W-1                                                                       | R/W-0                                                                                                         | R/W-0                           | U-0                                     | R/W-1            | R/W-0   | R/W-0   |

|                             | U4TXIP2                                                                     | U4TXIP1                                                                                                       | U4TXIP0                         |                                         | U4RXIP2          | U4RXIP1 | U4RXIP0 |

| bit 7                       |                                                                             |                                                                                                               |                                 |                                         |                  |         | bit (   |

| Legend:                     |                                                                             |                                                                                                               |                                 |                                         |                  |         |         |

| R = Readab                  | le bit                                                                      | W = Writable                                                                                                  | bit                             | U = Unimpler                            | nented bit, read | as '0'  |         |

| -n = Value a                | t POR                                                                       | '1' = Bit is set                                                                                              |                                 | '0' = Bit is cleared x = Bit is unknown |                  |         | iown    |

| bit 6-4<br>bit 3<br>bit 2-0 | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplement | : UART4 Trans<br>ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br>ted: Read as '<br>: UART4 Rece | highest priority<br>abled<br>)' | interrupt)                              |                  |         |         |

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers:

- OSCCON

- CLKDIV

- · OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The OSCTUN register (Register 9-3) allows the user to fine tune the FRC oscillator over a range of approximately  $\pm 1.5\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC oscillator by a fixed amount.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | egend: CO = Clearable Only bit SO = Settable Only bit |                        |                    |  |

|-------------------|-------------------------------------------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                      | U = Unimplemented bit, | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set                                      | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a Non-PLL Clock mode is selected.

## 9.5 Secondary Oscillator (SOSC)

#### 9.5.1 BASIC SOSC OPERATION

PIC24FJ128GA310 family devices do not have to set the SOSCEN bit to use the Secondary Oscillator. Any module requiring the SOSC (such as RTCC, Timer1 or DSWDT) will automatically turn on the SOSC when the clock signal is needed. The SOSC, however, has a long start-up time. To avoid delays for peripheral start-up, the SOSC can be manually started using the SOSCEN bit.

To use the Secondary Oscillator, the SOSCSEL bit (CW3<8>) must be set (= 1). Programming SOSCSEL (= 0) configures the SOSC pins for Digital mode, enabling digital input functionality on the pins.

#### 9.5.2 EXTERNAL (DIGITAL) CLOCK MODE (SCLKI)

The SOSC can also be configured to run from an external 32 kHz clock source, rather than the internal oscillator. In this mode, also referred to as Digital mode, the clock source provided on the SCLKI pin is used to clock any modules that are configured to use the Secondary Oscillator. In this mode, the crystal driving circuit is disabled and the SOSCEN bit (OSCCON<1>) has no effect.

#### 9.5.3 SOSC LAYOUT CONSIDERATIONS

The pinout limitations on low pin count devices, such as those in the PIC24FJ128GA310 family, may make the SOSC more susceptible to noise than other PIC24FJ devices. Unless proper care is taken in the design and layout of the SOSC circuit, this external noise may introduce inaccuracies into the oscillator's period.

Note: A typical 50K ESR (65K-70K Max) crystal is recommended for the reliable operation of the SOSC. The duty cycle of the SOSC output can be measured on the REFO pin and is recommended to be within ±15% from a 50% duty cycle. In general, the crystal circuit connections should be as short as possible. It is also good practice to surround the crystal circuit with a ground loop or ground plane. For more information on crystal circuit design, please refer to **"Oscillator"** (DS39700) in the *"dsPIC33/PIC24 Family Reference Manual"*. Additional information is also available in these Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PICmicro<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design" (DS00849).

### 9.6 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FJ128GA310 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT). Otherwise, if the POSCEN bit is also not set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

### 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

### 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits (see Register 11-1 through Register 11-6), which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

## 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. Refer to **Section 32.0 "Electrical Characteristics"** for more details.

### TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

### TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                         | Tolerated Input | Description                                                          |  |  |

|-------------------------------------|-----------------|----------------------------------------------------------------------|--|--|

| PORTA<15:14, 7:0> <sup>(1)</sup>    |                 |                                                                      |  |  |

| PORTB<15:7, 5:2>                    |                 |                                                                      |  |  |

| PORTC<3:1>(1)                       |                 |                                                                      |  |  |

| PORTD<15:8, 5:0>(1)                 | 5.5V            | Tolerates input levels above VDD; useful<br>for most standard logic. |  |  |

| PORTE<9:8, 4:0> <sup>(1)</sup>      |                 | ior most standard logic.                                             |  |  |

| PORTF<13:12, 8:0>(1)                |                 |                                                                      |  |  |

| PORTG<15:12, 9, 6:0> <sup>(1)</sup> |                 |                                                                      |  |  |

| PORTA<10:9> <sup>(1)</sup>          |                 |                                                                      |  |  |

| PORTB<6, 1:0>                       |                 |                                                                      |  |  |

| PORTC<15:12, 4> <sup>(1)</sup>      |                 |                                                                      |  |  |

| PORTD<7:6>                          | VDD             | Only VDD input levels are tolerated.                                 |  |  |

| PORTE<7:5>(1)                       |                 |                                                                      |  |  |

| PORTG<8:7>                          |                 |                                                                      |  |  |

**Note 1:** Not all of these pins are implemented on 64-pin or 80-pin devices. Refer to **Section 1.0 "Device Overview"** for a complete description of port pin implementation.

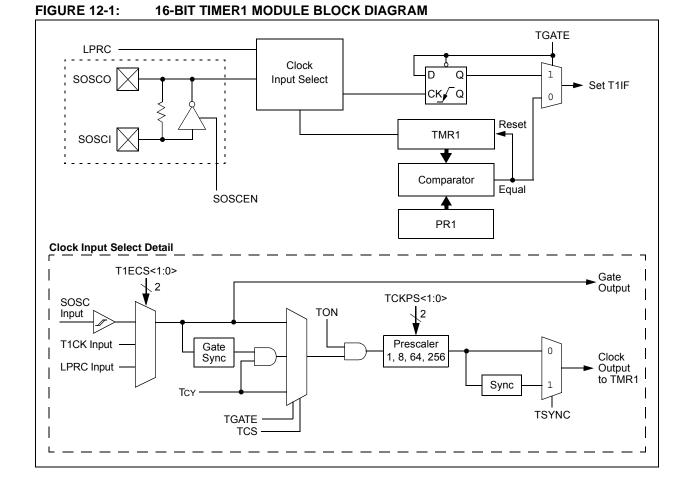

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Timers" (DS39704) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS, TECS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

© 2010-2014 Microchip Technology Inc.

## 13.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Timers" (DS39704) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two independent 16-bit timers with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- Single 32-bit synchronous counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- ADC Event Trigger (only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC event trigger. This trigger is implemented only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1; T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 or Timer5 interrupt flags. To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 or T45 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word (msw) of the value, while PR2 (or PR4) contains the least significant word (lsw).

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2> (or TMR<5:4>). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON (TxCON<15> = 1) bit.

| R/W-0            | U-0                                       | R/W-0                                                            | U-0                                                      | U-0               | U-0              | U-0            | U-0                  |

|------------------|-------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|-------------------|------------------|----------------|----------------------|

| MDEN             |                                           | MSIDL                                                            |                                                          |                   |                  | —              |                      |

| bit 15           |                                           | •                                                                |                                                          | ·                 | •                | •              | bit                  |

| U-0              | R/W-0                                     | R/W-0                                                            | R/W-0                                                    | U-0               | U-0              | U-0            | R/W-0                |

| _                | MDOE                                      | MDSLR                                                            | MDOPOL                                                   |                   | _                | _              | MDBIT <sup>(1)</sup> |

| bit 7            |                                           |                                                                  |                                                          |                   |                  |                | bit                  |

| Legend:          |                                           |                                                                  |                                                          |                   |                  |                |                      |

| R = Readab       | ole bit                                   | W = Writable                                                     | bit                                                      | U = Unimplem      | nented bit, read | l as '0'       |                      |

| -n = Value a     | t POR                                     | '1' = Bit is set                                                 | t                                                        | '0' = Bit is clea | ared             | x = Bit is unk | nown                 |

| bit 14<br>bit 13 | 0 = Modulato<br>Unimplemen<br>MSIDL: Mode | or module is dis<br>n <b>ted:</b> Read as '<br>ulator Stop in lo |                                                          | no output         |                  |                |                      |

|                  | 0 = Continue                              | es module oper                                                   | ation in Idle mo                                         |                   |                  |                |                      |

| bit 12-7         | -                                         | ted: Read as '                                                   |                                                          | 1. 1.9            |                  |                |                      |

| bit 6            | 1 = Modulate                              | or pin output is<br>or pin output is                             |                                                          |                   |                  |                |                      |

| bit 5            | 1 = MDOUT                                 | pin slew rate li                                                 | Rate Limiting b<br>miting is enable<br>miting is disable | ed                |                  |                |                      |

| bit 4            | 1 = Modulate                              | or output signal                                                 | t Polarity Select<br>is inverted<br>is not inverted      | t bit             |                  |                |                      |

| bit 3-1          |                                           | nted: Read as '                                                  |                                                          |                   |                  |                |                      |

| bit 0            | -                                         | ual Modulation                                                   |                                                          |                   |                  |                |                      |

|                  | 1 = Carrier is                            | s modulated                                                      | -                                                        |                   |                  |                |                      |

|                  |                                           | o modulato a                                                     |                                                          |                   |                  |                |                      |

### REGISTER 19-1: MDCON: MODULATOR CONTROL REGISTER

REGISTER 19-3:

#### R/W-x R/W-x R/W-x R/W-x U-0 R/W-x R/W-x R/W-x CH0<sup>(1)</sup> CH3(1) CH2<sup>(1)</sup> CH1<sup>(1)</sup> CHODIS CHPOL CHSYNC bit 15 bit 8 R/W-0 R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x U-0 CI 3<sup>(1)</sup> CI 2<sup>(1)</sup> CL1<sup>(1)</sup> CI 0<sup>(1)</sup> CLODIS CLPOL CLSYNC bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 CHODIS: Modulator High Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CH<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 14 CHPOL: Modulator High Carrier Polarity Select bit 1 = Selected high carrier signal is inverted 0 = Selected high carrier signal is not inverted bit 13 CHSYNC: Modulator High Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the high carrier before allowing a switch to the low carrier 0 = Modulator output is not synchronized to the high time carrier signal<sup>(1)</sup> bit 12 Unimplemented: Read as '0' bit 11-8 CH<3:0> Modulator Data High Carrier Selection bits<sup>(1)</sup> 1111 = Reserved . . . 1011 1010 = Output Compare/PWM Module 7 output 1001 = Output Compare/PWM Module 6 output 1000 = Output Compare/PWM Module 5 output 0111 = Output Compare/PWM Module 4 output 0110 = Output Compare/PWM Module 3 output 0101 = Output Compare/PWM Module 2 output 0100 = Output Compare/PWM Module 1 output 0011 = Reference clock (REFO) output 0010 = Input on MDCIN2 pin 0001 = Input on MDCIN1 pin 0000 = Vss bit 7 CLODIS: Modulator Low Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CL<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 6 CLPOL: Modulator Low Carrier Polarity Select bit 1 = Selected low carrier signal is inverted 0 = Selected low carrier signal is not inverted bit 5 **CLSYNC:** Modulator Low Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the low carrier before allowing a switch to the high carrier 0 = Modulator output is not synchronized to the low time carrier signal<sup>(1)</sup>bit 4 Unimplemented: Read as '0' CL<3:0> Modulator Data Low Carrier Selection bits<sup>(1)</sup> bit 3-0 Bit settings are identical to those for CH<3:0>.

MDCAR: MODULATOR CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| R/W-0        | R/W-0                       | R/W-0                                 | R/W-0          | R/W-0                 | R/W-0                 | R/W-0           | R/W-0   |

|--------------|-----------------------------|---------------------------------------|----------------|-----------------------|-----------------------|-----------------|---------|

| PWCEN        | PWCPOL                      | PWCPRE                                | PWSPRE         | RTCLK1 <sup>(2)</sup> | RTCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0 |

| bit 15       | ·                           |                                       |                |                       |                       |                 | bit 8   |

|              |                             |                                       |                |                       |                       |                 |         |

| U-0          | U-0                         | U-0                                   | U-0            | U-0                   | U-0                   | U-0             | U-0     |

|              | —                           |                                       | _              | —                     | —                     | —               |         |

| bit 7        |                             |                                       |                |                       |                       |                 | bit     |

| Legend:      |                             |                                       |                |                       |                       |                 |         |

| R = Readab   | le bit                      | W = Writable                          | bit            | U = Unimplem          | nented bit, read      | l as '0'        |         |

| -n = Value a | t POR                       | '1' = Bit is set                      |                | '0' = Bit is clea     | ared                  | x = Bit is unkr | nown    |

|              |                             |                                       |                |                       |                       |                 |         |

| bit 15       | PWCEN: Pow                  | ver Control Ena                       | ble bit        |                       |                       |                 |         |

|              |                             | ontrol is enable                      |                |                       |                       |                 |         |

|              |                             | ontrol is disable                     |                |                       |                       |                 |         |

| bit 14       |                             | ower Control Er                       |                |                       |                       |                 |         |

|              |                             | ontrol is enable<br>ontrol is disable |                |                       |                       |                 |         |

| bit 13       |                             | ower Control/St                       |                | ar hite               |                       |                 |         |

|              |                             |                                       | -              | y-2 of the sourc      | e RTCC clock          |                 |         |

|              |                             |                                       |                | y-1 of the source     |                       |                 |         |

| bit 12       | PWSPRE: Po                  | wer Control Sa                        | mple Prescale  | er bits               |                       |                 |         |

|              |                             |                                       |                | /-2 of the sourc      |                       |                 |         |

|              |                             | -                                     | -              | /-1 of the sourc      | e RTCC clock          |                 |         |

| bit 11-10    |                             | : RTCC Clock                          |                | bits <sup>(2)</sup>   |                       |                 |         |

|              |                             | l power line (60<br>l power line sou  |                |                       |                       |                 |         |

|              |                             | LPRC Oscillato                        |                |                       |                       |                 |         |

|              |                             | Secondary Os                          |                | )                     |                       |                 |         |

| bit 9-8      | RTCOUT<1:0                  | >: RTCC Outp                          | ut Source Sele | ect bits              |                       |                 |         |

|              | 11 = Power c                |                                       |                |                       |                       |                 |         |

|              | 10 = RTCC cl<br>01 = RTCC s |                                       |                |                       |                       |                 |         |

|              | 00 = RTCC a                 |                                       |                |                       |                       |                 |         |

| bit 7-0      |                             | ted: Read as '                        | )'             |                       |                       |                 |         |

|              | •                           |                                       |                |                       |                       |                 |         |

| Note 1: ⊤    | he RTCPWC reg               |                                       | rected by a PO |                       |                       |                 |         |

# REGISTER 22-2: RTCPWC: RTCC POWER CONTROL REGISTER<sup>(1)</sup>

2: When a new value is written to these register bits, the lower half of the MINSEC register should also be written to properly reset the clock prescalers in the RTCC.

#### REGISTER 29-5: DEVID: DEVICE ID REGISTER

| U-1       | U-1                        | U-1             | U-1               | U-1          | U-1        | U-1    | U-1    |  |  |

|-----------|----------------------------|-----------------|-------------------|--------------|------------|--------|--------|--|--|

| _         | —                          | —               | —                 | —            | —          | —      | —      |  |  |

| bit 23    |                            |                 |                   |              |            |        | bit 16 |  |  |

|           |                            |                 |                   |              |            |        |        |  |  |

| R         | R                          | R               | R                 | R            | R          | R      | R      |  |  |

| FAMID7    | FAMID6                     | FAMID5          | FAMID4            | FAMID3       | FAMID2     | FAMID1 | FAMID0 |  |  |

| bit 15    |                            |                 |                   |              |            |        | bit 8  |  |  |

|           |                            |                 |                   |              |            |        |        |  |  |

| R         | R                          | R               | R                 | R            | R          | R      | R      |  |  |

| DEV7      | DEV6                       | DEV5            | DEV4              | DEV3         | DEV2       | DEV1   | DEV0   |  |  |

| bit 7     |                            |                 |                   |              |            |        | bit 0  |  |  |

|           |                            |                 |                   |              |            |        |        |  |  |

| Legend: F | R = Readable bit           |                 |                   | U = Unimplem | nented bit |        |        |  |  |

|           |                            |                 |                   |              |            |        |        |  |  |

| bit 23-16 | Unimplemen                 | ted: Read as ': | 1'                |              |            |        |        |  |  |

| bit 15-8  | FAMID<7:0>:                | Device Family   | Identifier bits   |              |            |        |        |  |  |

|           | 0100 0110 =                | = PIC24FJ1280   | GA310 family      |              |            |        |        |  |  |

| bit 7-0   | DEV<7:0>: In               | dividual Device | e Identifier bits |              |            |        |        |  |  |

|           |                            | PIC24FJ64G      |                   |              |            |        |        |  |  |

|           |                            | PIC24FJ1280     |                   |              |            |        |        |  |  |

|           | 1100 0100 = PIC24FJ64GA308 |                 |                   |              |            |        |        |  |  |

- 1100 0100 = PIC24FJ04GA308 1100 0110 = PIC24FJ128GA308

- 1100 1000 = PIC24FJ64GA310

- 1100 1010 = PIC24FJ128GA310

### REGISTER 29-6: DEVREV: DEVICE REVISION REGISTER

| U-0       | U-0            | U-0 | U-0 | U-0          | U-0        | U-0 | U-0    |  |

|-----------|----------------|-----|-----|--------------|------------|-----|--------|--|

| —         | —              | —   | —   | —            | —          | _   | _      |  |

| bit 23    |                |     |     | •            |            |     | bit 16 |  |

|           |                |     |     |              |            |     |        |  |

| U-0       | U-0            | U-0 | U-0 | U-0          | U-0        | U-0 | U-0    |  |

|           | _              | —   | —   | —            | —          | —   | —      |  |

| bit 15    |                |     |     |              |            |     | bit 8  |  |

|           |                |     |     |              |            |     |        |  |

| U-0       | U-0            | U-0 | U-0 | R            | R          | R   | R      |  |

| —         | —              | —   | —   | REV<3:0>     |            |     |        |  |

| bit 7     |                |     |     |              |            |     | bit 0  |  |

|           |                |     |     |              |            |     |        |  |

| Legend: R | = Readable bit |     |     | U = Unimpler | mented bit |     |        |  |

|           |                |     |     |              |            |     | ,<br>, |  |

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Device revision identifier bits

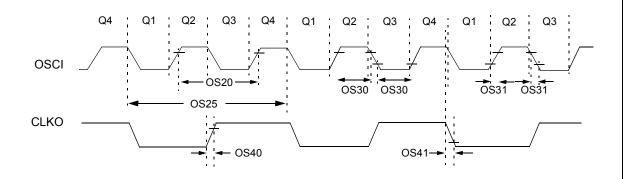

| TABLE 32-19: | EXTERNAL CLOCK TIMING REQUIREMENTS |

|--------------|------------------------------------|

|              |                                    |

| AC CH        | ARACTE        | RISTICS                                                                 | Standard Operating Conditions: 2V to 3.6V (unless otherwise stated) |                    |                                        |                                 |                                      |

|--------------|---------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------|----------------------------------------|---------------------------------|--------------------------------------|

|              |               |                                                                         | Operating temperature                                               |                    | $-40^{\circ}C \le TA \le +85^{\circ}C$ |                                 | for Industrial                       |

| Param<br>No. | Symbol        | Characteristic                                                          | Min                                                                 | Typ <sup>(1)</sup> | Max                                    | Units                           | Conditions                           |

| OS10         | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4                                                             |                    | 32<br>8                                | MHz<br>MHz                      | EC<br>ECPLL                          |

|              |               | Oscillator Frequency                                                    | 3.5<br>4<br>10<br>4<br>31                                           |                    | 10<br>8<br>32<br>8<br>33               | MHz<br>MHz<br>MHz<br>MHz<br>kHz | XT<br>XTPLL<br>HS<br>HSPLL<br>SOSC   |

| OS20         | Tosc          | Tosc = 1/Fosc                                                           |                                                                     | _                  | _                                      |                                 | See Parameter OS10 for<br>Fosc value |

| OS25         | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                                                                | _                  | DC                                     | ns                              |                                      |

| OS30         | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc                                                         | —                  | _                                      | ns                              | EC                                   |

| OS31         | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | —                                                                   | _                  | 20                                     | ns                              | EC                                   |

| OS40         | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | _                                                                   | 6                  | 10                                     | ns                              |                                      |

| OS41         | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | —                                                                   | 6                  | 10                                     | ns                              |                                      |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

#### TABLE 32-37: SPIX MODULE SLAVE MODE TIMING REQUIREMENTS (CKE = 1) (CONTINUED)

| AC CHARACTERISTICS |                      |                                       | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |            |

|--------------------|----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|

| Param<br>No.       | Symbol               | Characteristic                        | Min                                                                                                                                               | Тур <sup>(1)</sup> | Max | Units | Conditions |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                 | 1.5 Tcy + 40                                                                                                                                      | _                  | _   | ns    |            |

| SP60               | TssL2doV             | SDOx Data Output Valid after SSx Edge | —                                                                                                                                                 | _                  | 50  | ns    |            |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

**3:** Assumes 50 pF load on all SPIx pins.

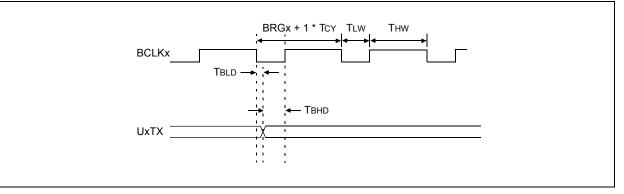

### FIGURE 32-18: UARTX BAUD RATE GENERATOR OUTPUT TIMING

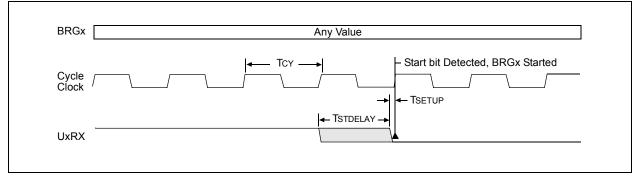

#### FIGURE 32-19: UARTX START BIT EDGE DETECTION

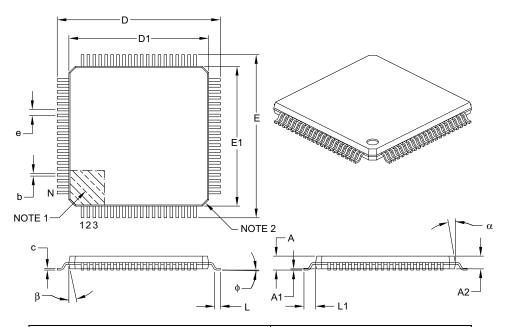

#### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS |      |  |  |

|--------------------------|------------------|-----------|-------------|------|--|--|

|                          | Dimension Limits | MIN       | NOM         | MAX  |  |  |

| Number of Leads          |                  |           | 80          |      |  |  |

| Lead Pitch               | е                |           | 0.50 BSC    |      |  |  |

| Overall Height           | А                | -         | -           | 1.20 |  |  |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |  |  |

| Standoff                 | A1               | 0.05      | -           | 0.15 |  |  |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |  |  |

| Footprint                | L1               | 1.00 REF  |             |      |  |  |

| Foot Angle               | ф                | 0°        | 3.5°        | 7°   |  |  |

| Overall Width            | E                |           | 14.00 BSC   |      |  |  |

| Overall Length           | D                | 14.00 BSC |             |      |  |  |

| Molded Package Width     | E1               | 12.00 BSC |             |      |  |  |

| Molded Package Length    | h D1 12.00 BSC   |           |             |      |  |  |

| Lead Thickness           | С                | 0.09      | -           | 0.20 |  |  |

| Lead Width               | b                | 0.17      | 0.22        | 0.27 |  |  |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |  |  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B