Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga308t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                                               | PIC24FJ64GA306                                                                                   | PIC24FJ128GA306                                    |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Operating Frequency                                                    | DC – 3                                                                                           | 2 MHz                                              |

| Program Memory (bytes)                                                 | 64K                                                                                              | 128K                                               |

| Program Memory (instructions)                                          | 22,016                                                                                           | 44,032                                             |

| Data Memory (bytes)                                                    | 8                                                                                                | K                                                  |

| Interrupt Sources (soft vectors/<br>NMI traps)                         | 65 (6                                                                                            | 61/4)                                              |

| I/O Ports                                                              | Ports B, C,                                                                                      | , D, E, F, G                                       |

| Total I/O Pins                                                         | 5                                                                                                | 3                                                  |

| Remappable Pins                                                        | 30 (29 I/Os,                                                                                     | 1 input only)                                      |

| Timers:                                                                |                                                                                                  |                                                    |

| Total Number (16-bit)                                                  | 50                                                                                               | (1)                                                |

| 32-Bit (from paired 16-bit timers)                                     | 2                                                                                                | 2                                                  |

| Input Capture Channels                                                 | 7(                                                                                               | (1)                                                |

| Output Compare/PWM Channels                                            | 7(                                                                                               | (1)                                                |

| Input Change Notification Interrupt                                    | 5                                                                                                | 2                                                  |

| Serial Communications:                                                 |                                                                                                  |                                                    |

| UART                                                                   | 40                                                                                               | (1)                                                |

| SPI (3-wire/4-wire)                                                    | 20                                                                                               | (1)                                                |

| I <sup>2</sup> C™                                                      | 2                                                                                                | 2                                                  |

| Digital Signal Modulator                                               | Ye                                                                                               | es                                                 |

| Parallel Communications (EPMP/PSP)                                     | Ye                                                                                               | es                                                 |

| JTAG Boundary Scan                                                     | Ye                                                                                               | es                                                 |

| 12/10-Bit Analog-to-Digital Converter<br>(ADC) Module (input channels) | 1                                                                                                | 6                                                  |

| Analog Comparators                                                     | 3                                                                                                | 3                                                  |

| CTMU Interface                                                         | Ye                                                                                               | es                                                 |

| LCD Controller (available pixels)                                      | 240 (30 SE                                                                                       | G x 8 COM)                                         |

| Resets (and Delays)                                                    | Core <u>POR,</u> VDD POR, VBAT P<br>MCLR, WDT, Illegal Opc<br>Hardware Traps, Config<br>(OST, Pl | ode, REPEAT Instruction,<br>juration Word Mismatch |

| Instruction Set                                                        | 76 Base Instructions, Multiple                                                                   | Addressing Mode Variations                         |

| Packages                                                               | 64-Pin TQF                                                                                       | P and QFN                                          |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ128GA310 FAMILY: 64-PIN

**Note 1:** Peripherals are accessible through remappable pins.

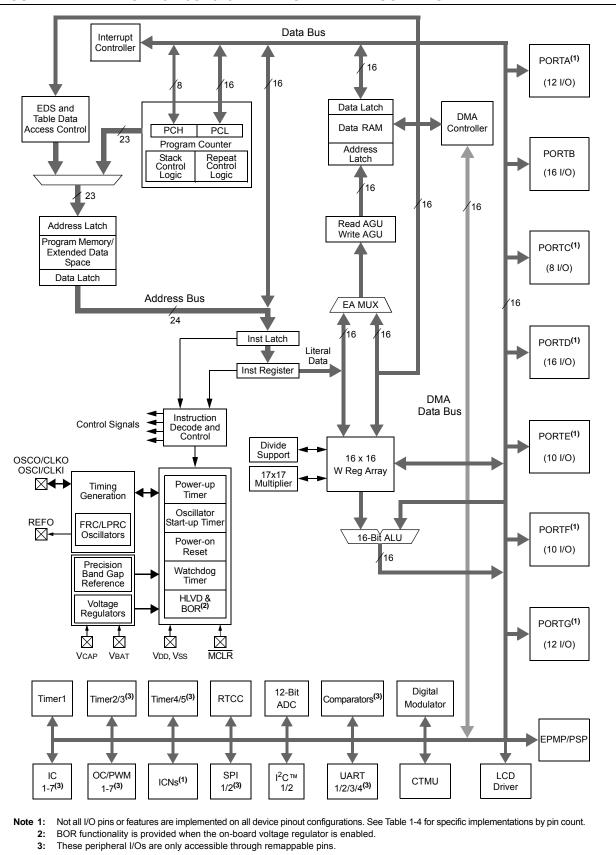

#### FIGURE 1-1: PIC24FJ128GA310 FAMILY GENERAL BLOCK DIAGRAM

### TABLE 4-10: UART REGISTER MAPS

| File Name      | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8                   | Bit 7          | Bit 6    | Bit 5   | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------------|------|----------|--------|----------|--------|--------|--------|---------|-------------------------|----------------|----------|---------|------------|---------|--------|--------|-------|---------------|

| U1MODE         | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0                    | WAKE           | LPBACK   | ABAUD   | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA          | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF   | TRMT                    | URXISEL1       | URXISEL0 | ADDEN   | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG        | 0224 | _        | —      | _        | —      | _      | _      |         |                         |                |          | UART1 T | ransmit Re | egister |        |        |       | xxxx          |

| U1RXREG        | 0226 | _        | _      | _        | —      | —      | —      |         |                         |                |          | UART1 F | Receive Re | gister  |        |        |       | 0000          |

| U1BRG          | 0228 |          |        |          |        |        |        | Baud Ra | te Generato             | or Prescaler F | Register |         |            |         |        |        |       | 0000          |

| U2MODE         | 0230 | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0                    | WAKE           | LPBACK   | ABAUD   | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA          | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF   | TRMT                    | URXISEL1       | URXISEL0 | ADDEN   | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG        | 0234 | _        | —      | _        | —      | _      | _      |         | UART2 Transmit Register |                |          |         |            | xxxx    |        |        |       |               |

| U2RXREG        | 0236 | _        | —      | _        | —      | _      | _      |         |                         |                |          | UART2 F | Receive Re | gister  |        |        |       | 0000          |

| U2BRG          | 0238 |          |        |          |        |        |        | Baud Ra | te Generato             | or Prescaler F | Register |         |            |         |        |        |       | 0000          |

| U3MODE         | 0250 | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0                    | WAKE           | LPBACK   | ABAUD   | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA          | 0252 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF   | TRMT                    | URXISEL1       | URXISEL0 | ADDEN   | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U3TXREG        | 0254 | _        | —      | _        | —      | _      | _      |         |                         |                |          | UART3 T | ransmit Re | egister |        |        |       | xxxx          |

| <b>U3RXREG</b> | 0256 | _        | —      | _        | —      | _      | _      |         |                         |                |          | UART3 F | Receive Re | gister  |        |        |       | 0000          |

| U3BRG          | 0258 |          |        |          |        |        |        | Baud Ra | te Generato             | or Prescaler F | Register |         |            |         |        |        |       | 0000          |

| U4MODE         | 02B0 | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0                    | WAKE           | LPBACK   | ABAUD   | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA          | 02B2 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF   | TRMT                    | URXISEL1       | URXISEL0 | ADDEN   | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U4TXREG        | 02B4 | _        | _      | _        | _      | _      | _      |         |                         |                |          | UART4 T | ransmit Re | egister |        |        |       | xxxx          |

| U4RXREG        | 02B6 | _        | _      | _        | _      | —      | _      | _       |                         |                |          | UART4 F | Receive Re | gister  |        |        |       | 0000          |

| U4BRG          | 02B8 |          |        |          |        |        |        | Baud Ra | te Generato             | or Prescaler F | Register |         |            |         |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-3: DMAINTX: DMA CHANNEL x INTERRUPT REGISTER

| R-0                     | U-0                                                  | R/W-0                             | R/W-0                 | R/W-0                  | R/W-0            | R/W-0            | R/W-0            |

|-------------------------|------------------------------------------------------|-----------------------------------|-----------------------|------------------------|------------------|------------------|------------------|

| DBUFWF <sup>(1)</sup>   |                                                      | CHSEL5                            | CHSEL4                | CHSEL3                 | CHSEL2           | CHSEL1           | CHSEL0           |

| bit 15                  |                                                      |                                   |                       |                        | L                |                  | bit 8            |

|                         |                                                      |                                   |                       |                        |                  |                  |                  |

| R/W-0                   | R/W-0                                                | R/W-0                             | R/W-0                 | R/W-0                  | U-0              | U-0              | R/W-0            |

| HIGHIF <sup>(1,2)</sup> | LOWIF <sup>(1,2)</sup>                               | DONEIF <sup>(1)</sup>             | HALFIF <sup>(1)</sup> | OVRUNIF <sup>(1)</sup> | —                |                  | HALFEN           |

| bit 7                   |                                                      |                                   |                       |                        |                  |                  | bit (            |

|                         |                                                      |                                   |                       |                        |                  |                  |                  |

| Legend:                 |                                                      |                                   |                       |                        |                  |                  |                  |

| R = Readable            |                                                      | W = Writable I                    | bit                   | -                      | nented bit, read |                  |                  |

| -n = Value at           | POR                                                  | '1' = Bit is set                  |                       | '0' = Bit is clea      | ared             | x = Bit is unkr  | nown             |

| L:1 4 F                 |                                                      | ffered Date Mr                    |                       |                        |                  |                  |                  |

| bit 15                  |                                                      | Iffered Data Wr                   | •                     | not boon writte        | n to the locati  | on analified in  |                  |

|                         |                                                      | Cx in Null Write                  |                       | not been writte        |                  | on specified in  | DIVIADSTX 0      |

|                         |                                                      |                                   |                       | e been written         | to the location  | on specified in  | DMADSTx o        |

|                         |                                                      | Cx in Null Write                  |                       |                        |                  |                  |                  |

| bit 14                  | -                                                    | ted: Read as '0                   |                       |                        |                  |                  |                  |

| bit 13-8                |                                                      | : DMA Channe                      |                       | tion bits              |                  |                  |                  |

|                         |                                                      | for a complete                    |                       | (1.0)                  |                  |                  |                  |

| bit 7                   |                                                      | High Address                      |                       |                        |                  |                  |                  |

|                         | 1 = The DMA<br>data RAN                              |                                   | ttempted to ac        | cess an addres         | s higher than D  | DMAH or the up   | per limit of the |

|                         |                                                      | •                                 | ot invoked the        | high address li        | mit interrupt    |                  |                  |

| bit 6                   |                                                      | Low Address L                     |                       | -                      |                  |                  |                  |

|                         |                                                      |                                   |                       | ccess the DMA          | SFR address      | lower than DM    | IAL, but above   |

|                         |                                                      | range (07FFh)                     |                       |                        |                  |                  |                  |

|                         |                                                      |                                   |                       | low address lir        | nit interrupt    |                  |                  |

| bit 5                   |                                                      | A Complete Op                     | eration Interru       | pt Flag bit            |                  |                  |                  |

|                         | $\frac{\text{If CHEN} = 1}{1 = \text{The previous}}$ | ious DMA sess                     | ion has ended         | with completion        | n                |                  |                  |

|                         |                                                      | ent DMA sessio                    |                       |                        | 1                |                  |                  |

|                         | <u>If CHEN = 0</u> :                                 |                                   |                       |                        |                  |                  |                  |

|                         |                                                      |                                   |                       | with completion        |                  |                  |                  |

|                         | -                                                    |                                   |                       | without comple         | etion            |                  |                  |

| bit 4                   |                                                      | A 50% Waterma                     |                       |                        |                  |                  |                  |

|                         |                                                      | Tx has reached<br>Tx has not reac |                       |                        |                  |                  |                  |

| bit 3                   |                                                      | MA Channel O                      |                       |                        |                  |                  |                  |

|                         |                                                      |                                   | •                     | s still completing     | the operation    | based on the p   | revious triaae   |

|                         |                                                      | run condition ha                  |                       |                        |                  |                  | 00               |

| bit 2-1                 | Unimplemen                                           | ted: Read as 'o                   | )'                    |                        |                  |                  |                  |

| bit 0                   | HALFEN: Ha                                           | Ifway Completio                   | on Watermark          | bit                    |                  |                  |                  |

|                         |                                                      |                                   |                       | x has reached i        |                  | nt and is at com | npletion         |

|                         | 0 = An interru                                       | upt is invoked o                  | nly at the com        | pletion of the tr      | ansfer           |                  |                  |

| Note 1: Se              | tting these flag                                     | s in software do                  | oes not genera        | ate an interrupt.      |                  |                  |                  |

|                         |                                                      |                                   |                       | or DMADSTx is          |                  | than DMAH o      | r less than      |

2: Testing for address limit violations (DMASRCx or DMADSTx is either greater than DMAH or less than DMAL) is NOT done before the actual access.

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Reset" (DS39712) in the "dsPIC33/PIC24 Family Reference Manual', . The information in this data sheet supersedes the information in the FRM.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). In addition, Reset events occurring while an extreme power-saving feature is in use (such as VBAT) will set one or more status bits in the RCON2 register (Register 7-2). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON registers should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

© 2010-2014 Microchip Technology Inc.

| U-0          | R/W-0          | R/W-0                            | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|----------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

|              | DMA4IF         | PMPIF                            | —                | OC7IF             | OC6IF           | OC5IF           | IC6IF  |

| bit 15       |                |                                  |                  |                   |                 |                 | bit 8  |

|              |                |                                  |                  |                   |                 |                 |        |

| R/W-0        | R/W-0          | R/W-0                            | R/W-0            | U-0               | U-0             | R/W-0           | R/W-0  |

| IC5IF        | IC4IF          | IC3IF                            | DMA3IF           | —                 | —               | SPI2IF          | SPF2IF |

| bit 7        |                |                                  |                  |                   |                 |                 | bit 0  |

| Legend:      |                |                                  |                  |                   |                 |                 |        |

| R = Readab   | le bit         | W = Writable                     | bit              | U = Unimpler      | nented bit, rea | d as '0'        |        |

| -n = Value a |                | '1' = Bit is set                 |                  | '0' = Bit is cle  |                 | x = Bit is unkr | nown   |

|              |                |                                  |                  |                   |                 |                 |        |

| bit 15       | Unimplemen     | ted: Read as '                   | כ'               |                   |                 |                 |        |

| bit 14       | DMA4IF: DM     | A Channel 4 In                   | terrupt Flag St  | atus bit          |                 |                 |        |

|              |                | request has oc                   |                  |                   |                 |                 |        |

|              | •              | request has no                   |                  |                   |                 |                 |        |

| bit 13       |                | lel Master Port                  |                  | Status bit        |                 |                 |        |

|              |                | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 12       | •              | ted: Read as '                   |                  |                   |                 |                 |        |

| bit 11       | -              |                                  |                  | pt Flag Status    | bit             |                 |        |

|              | •              | request has oc                   |                  |                   |                 |                 |        |

|              |                | request has no                   |                  |                   |                 |                 |        |

| bit 10       |                | •                                |                  | pt Flag Status    | bit             |                 |        |

|              |                | request has oc                   |                  |                   |                 |                 |        |

| hit O        | •              | request has no                   |                  | unt Flog Status   | h i t           |                 |        |

| bit 9        | •              | request has oc                   |                  | ipt Flag Status I | UIL             |                 |        |

|              |                | request has no                   |                  |                   |                 |                 |        |

| bit 8        | IC6IF: Input C | Capture Channe                   | el 6 Interrupt F | lag Status bit    |                 |                 |        |

|              |                | request has oc                   |                  |                   |                 |                 |        |

|              |                | request has no                   |                  |                   |                 |                 |        |

| bit 7        | •              | Capture Channe                   | •                | lag Status bit    |                 |                 |        |

|              |                | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 6        |                | Capture Channe                   |                  | lag Status bit    |                 |                 |        |

|              | -              | request has oc                   | -                |                   |                 |                 |        |

|              |                | request has no                   |                  |                   |                 |                 |        |

| bit 5        | IC3IF: Input C | Capture Channe                   | el 3 Interrupt F | lag Status bit    |                 |                 |        |

|              |                | request has oc                   |                  |                   |                 |                 |        |

| hit 1        | -              | request has no                   |                  | atus hit          |                 |                 |        |

| bit 4        |                | A Channel 3 In<br>request has oc |                  | atus dit          |                 |                 |        |

|              |                | request has no                   |                  |                   |                 |                 |        |

| bit 3-2      |                | ted: Read as '                   |                  |                   |                 |                 |        |

| bit 1        | SPI2IF: SPI2   | Event Interrup                   | t Flag Status b  | it                |                 |                 |        |

|              |                | request has oc                   |                  |                   |                 |                 |        |

|              | 0 = Interrupt  | request has no                   | t occurred       |                   |                 |                 |        |

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

#### REGISTER 8-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 2 OC1IE: Output Compare Channel 1 Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

#### REGISTER 8-19: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

| U-0           | U-0                            | U-0              | U-0             | U-0                                | U-0  | U-0             | U-0   |  |

|---------------|--------------------------------|------------------|-----------------|------------------------------------|------|-----------------|-------|--|

| —             | _                              | —                | —               | _                                  | —    | —               | —     |  |

| bit 15        |                                |                  |                 |                                    |      |                 | bit 8 |  |

|               |                                |                  |                 |                                    |      |                 |       |  |

| U-0           | U-0                            | U-0              | R/W-0           | U-0                                | U-0  | U-0             | U-0   |  |

| _             | —                              | —                | LCDIE           | _                                  | —    | —               | —     |  |

| bit 7         |                                |                  | •               |                                    | •    |                 | bit 0 |  |

|               |                                |                  |                 |                                    |      |                 |       |  |

| Legend:       |                                |                  |                 |                                    |      |                 |       |  |

| R = Readabl   | le bit                         | W = Writable     | bit             | U = Unimplemented bit, read as '0' |      |                 |       |  |

| -n = Value at | -n = Value at POR '1' = Bit is |                  |                 | '0' = Bit is clea                  | ared | x = Bit is unkr | iown  |  |

|               |                                |                  |                 |                                    |      |                 |       |  |

| bit 15-5      | Unimplemen                     | ted: Read as 'd  | D'              |                                    |      |                 |       |  |

| bit 4         | LCDIE: LCD                     | Controller Inter | rupt Enable bit | t                                  |      |                 |       |  |

|               |                                |                  |                 |                                    |      |                 |       |  |

|         | <ol> <li>1 = Interrupt request is enabled</li> </ol> |

|---------|------------------------------------------------------|

|         | 0 = Interrupt request is not enabled                 |

| bit 3-0 | Unimplemented: Read as '0'                           |

#### REGISTER 8-20: IEC7: INTERRUPT ENABLE CONTROL REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | _   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|--------|-----|-----|-----|-----|-------|

| —     | —   | JTAGIE | —   |     |     |     | —     |

| bit 7 |     |        |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5 JTAGIE: JTAG Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 4-0 Unimplemented: Read as '0'

## 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Output Compare with Dedicated Timer" (DS39723) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GA310 family all feature seven independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 31 user-selectable trigger/sync sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSELx bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-Bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs and the even module (OCy) provides the Most Significant 16 bits. Wraparounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more details on cascading, refer to **"Output Compare with Dedicated Timer"** (DS39723) in the *"dsPIC33/PIC24 Family Reference Manual"*.

## 17.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, ADC Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- · Both 100 kHz and 400 kHz bus specifications

- · Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 17-1.

### 17.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

### 17.2 Setting Baud Rate When Operating as a Bus Master

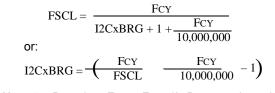

To compute the Baud Rate Generator reload value, use Equation 17-1.

#### EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1,2)</sup>

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

## 17.3 Slave Address Masking

The I2CxMSK register (Register 17-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '0000000' and '0100000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Demained Overlage Fact | Fair   | I2CxB     | RG Value      | A stud Fool |

|------------------------|--------|-----------|---------------|-------------|

| Required System Fsc∟   | FCY    | (Decimal) | (Hexadecimal) | Actual FscL |

| 100 kHz                | 16 MHz | 157       | 9D            | 100 kHz     |

| 100 kHz                | 8 MHz  | 78        | 4E            | 100 kHz     |

| 100 kHz                | 4 MHz  | 39        | 27            | 99 kHz      |

| 400 kHz                | 16 MHz | 37        | 25            | 404 kHz     |

| 400 kHz                | 8 MHz  | 18        | 12            | 404 kHz     |

| 400 kHz                | 4 MHz  | 9         | 9             | 385 kHz     |

| 400 kHz                | 2 MHz  | 4         | 4             | 385 kHz     |

| 1 MHz                  | 16 MHz | 13        | D             | 1.026 MHz   |

| 1 MHz                  | 8 MHz  | 6         | 6             | 1.026 MHz   |

| 1 MHz                  | 4 MHz  | 3         | 3             | 0.909 MHz   |

## **TABLE 17-1:** I2C<sup>™</sup> CLOCK RATES<sup>(1,2)</sup>

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

...

| TABLE 17-2: | I <sup>2</sup> C <sup>™</sup> RESERVED ADDRESSES <sup>(1)</sup> |  |

|-------------|-----------------------------------------------------------------|--|

|             |                                                                 |  |

| Slave Address | R/W Bit | Description                            |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|

| 000 000       | 0       | General Call Address <sup>(2)</sup>    |  |  |  |

| 0000 0000     | 1       | Start Byte                             |  |  |  |

| 0000 001      | x       | CBus Address                           |  |  |  |

| 0000 01x      | x       | Reserved                               |  |  |  |

| 0000 1xx      | x       | HS Mode Master Code                    |  |  |  |

| 1111 0xx      | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |

| 1111 1xx      | x       | Reserved                               |  |  |  |

Note 1: The address bits listed here will never cause an address match, independent of address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ACKDT: Acknowledge Data bit (when operating as I<sup>2</sup>C master; applicable during master receive)</li> <li>Value that will be transmitted when the software initiates an Acknowledge sequence.</li> <li>1 = Sends NACK during Acknowledge</li> <li>0 = Sends ACK during Acknowledge</li> </ul>                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master; applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                          |

|       | 1 = Enables Receive mode for I <sup>2</sup> C. Hardware is clear at the end of the eighth bit of the master receive data byte.                                                                                                                                                                                                                                       |

|       | 0 = Receive sequence is not in progress                                                                                                                                                                                                                                                                                                                              |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                    |

|       | 1 = Initiates Stop condition on the SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                                                                                                                                    |

|       | 0 = Stop condition is not in progress                                                                                                                                                                                                                                                                                                                                |

| bit 1 | RSEN: Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                |

|       | <ul> <li>1 = Initiates Repeated Start condition on the SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> </ul>                                                                                                                                                                                                        |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                                                                                                                                                      |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                          |

|       | 1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.                                                                                                                                                                                                                                                      |

|       | 0 = Start condition is not in progress                                                                                                                                                                                                                                                                                                                               |

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC     | R-0, HSC                                                                                                                                                                                                                        | U-0                                                                | U-0                                | U-0                          | R/C-0, HS                    | R-0, HSC            | R-0, HSC           |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------|------------------------------|------------------------------|---------------------|--------------------|--|--|--|

| ACKSTAT      | TRSTAT                                                                                                                                                                                                                          | _                                                                  | —                                  |                              | BCL                          | GCSTAT              | ADD10              |  |  |  |

| bit 15       |                                                                                                                                                                                                                                 |                                                                    |                                    |                              |                              |                     | bit 8              |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

| R/C-0, HS    | R/C-0, HS                                                                                                                                                                                                                       | R-0, HSC                                                           | R/C-0, HSC                         | R/C-0, HSC                   | R-0, HSC                     | R-0, HSC            | R-0, HSC           |  |  |  |

| IWCOL        | I2COV                                                                                                                                                                                                                           | D/A                                                                | Р                                  | S                            | R/W                          | RBF                 | TBF                |  |  |  |

| bit 7        |                                                                                                                                                                                                                                 |                                                                    |                                    |                              |                              |                     | bit 0              |  |  |  |

| Legend:      |                                                                                                                                                                                                                                 | C = Clearab                                                        | le hit                             | HS = Hardware                | Settable bit                 |                     |                    |  |  |  |

| R = Readab   | le hit                                                                                                                                                                                                                          | W = Writabl                                                        |                                    |                              | ented bit, read as           | ' <b>∩</b> '        |                    |  |  |  |

| -n = Value a |                                                                                                                                                                                                                                 | '1' = Bit is s                                                     |                                    | '0' = Bit is clear           |                              | x = Bit is unkno    | wn                 |  |  |  |

|              | ware Settable                                                                                                                                                                                                                   |                                                                    |                                    |                              | 04                           |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

| bit 15       | ACKSTAT:                                                                                                                                                                                                                        | Acknowledge                                                        | Status bit                         |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 | was detected                                                       |                                    |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 | as detected la                                                     |                                    | of Acknowledge.              |                              |                     |                    |  |  |  |

| bit 14       |                                                                                                                                                                                                                                 | ansmit Status                                                      |                                    | Acknowledge.                 |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    |                                    | icable to master             | transmit operation           | on.)                |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    | progress (8 b                      | its + ACK)                   |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    | ot in progress                     | er transmission:             | hardware is clear            | at the end of slav  | ve Acknowledge     |  |  |  |

| bit 13-11    |                                                                                                                                                                                                                                 | -                                                                  | -                                  |                              | nardware is clear            |                     | re Acknowledge.    |  |  |  |

| bit 10       | -                                                                                                                                                                                                                               | Unimplemented: Read as '0'<br>BCL: Master Bus Collision Detect bit |                                    |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 | 1 = A bus collision has been detected during a master operation    |                                    |                              |                              |                     |                    |  |  |  |

|              | 0 = No colli                                                                                                                                                                                                                    |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

| 1.1.0        |                                                                                                                                                                                                                                 |                                                                    | etection of a bi                   | us collision.                |                              |                     |                    |  |  |  |

| bit 9        | GCSTAT: General Call Status bit<br>1 = General call address was received                                                                                                                                                        |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    | s was received<br>s was not rece   |                              |                              |                     |                    |  |  |  |

|              | Hardware is                                                                                                                                                                                                                     | set when the                                                       | address mate                       | ches the general             | call address; ha             | rdware is clear a   | t Stop detection.  |  |  |  |

| bit 8        | ADD10: 10-                                                                                                                                                                                                                      | Bit Address S                                                      | Status bit                         |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 | ddress was r                                                       |                                    |                              |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 | ddress was r<br>set at the mat                                     |                                    | te of the matched            | d 10-bit address; h          | nardware is clear a | at Stop detection. |  |  |  |

| bit 7        |                                                                                                                                                                                                                                 | ite Collision E                                                    | -                                  |                              |                              |                     |                    |  |  |  |

|              | 1 = An atter                                                                                                                                                                                                                    | mpt to write t                                                     | o the I2CxTRI                      | N register failed            | because the I <sup>2</sup> C | module is busy      |                    |  |  |  |

|              | 0 = No colli                                                                                                                                                                                                                    |                                                                    | ourronoo of ur                     | ite te IOOVTON               | while husy (slear            | ad by coffwore)     |                    |  |  |  |

| bit 6        | Hardware is set at an occurrence of write to I2CxTRN while busy (cleared by software).<br>I2COV: Receive Overflow Flag bit                                                                                                      |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

| bit 0        |                                                                                                                                                                                                                                 |                                                                    | 0                                  | xRCV register is             | still holding the            | previous byte       |                    |  |  |  |

|              | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> <li>Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).</li> </ul> |                                                                    |                                    |                              |                              |                     |                    |  |  |  |

|              | _                                                                                                                                                                                                                               |                                                                    | -                                  |                              | 2CxRCV (cleared              | d by software).     |                    |  |  |  |

| bit 5        |                                                                                                                                                                                                                                 | •                                                                  |                                    | l as l <sup>2</sup> C slave) |                              |                     |                    |  |  |  |

|              |                                                                                                                                                                                                                                 |                                                                    | st byte receive<br>st byte receive | ed was data                  | address                      |                     |                    |  |  |  |

|              | Hardware is                                                                                                                                                                                                                     | clear at the                                                       | e device addr                      |                              | dware is set after           | er a transmissio    | n finishes or by   |  |  |  |

|              | reception of                                                                                                                                                                                                                    | a slave byte                                                       |                                    |                              |                              |                     |                    |  |  |  |

NOTES:

## 20.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Enhanced Parallel Master Port (EPMP)" (DS39730) in the "dsPIC33/PIC24 Family Reference Manual'. The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only), 8-bit (Master and Slave modes) or 16-bit (Master mode only) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each Chip Select, and then assigning each Chip Select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP.

Key features of the EPMP module are:

- Extended Data Space (EDS) Interface allows Direct Access from the CPU

- Up to 23 Programmable Address Lines

- Up to 2 Chip Select Lines

- Up to 2 Acknowledgment Lines (one per Chip Select)

- 4-Bit, 8-Bit or 16-Bit-Wide Data Bus

- Programmable Strobe Options (per Chip Select):

- Individual Read and Write Strobes or;

- Read/Write Strobe with Enable Strobe

- Programmable Address/Data Multiplexing

- Programmable Address Wait States

- · Programmable Data Wait States (per Chip Select)

- Programmable Polarity on Control Signals (per Chip Select)

- · Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address Support

- 4-Byte Deep Auto-Incrementing Buffer

### 20.1 Specific Package Variations

While all PIC24FJ128GA310 family devices implement the EPMP, I/O pin constraints place some limits on 16-Bit Master mode operations in some package types. This is reflected in the number of dedicated Chip Select pins implemented and the number of dedicated address lines that are available. The differences are summarized in Table 20-1. All available EPMP pin functions are summarized in Table 20-2.

For 64-pin devices, the dedicated Chip Select pins (PMCS1 and PMCS2) are not implemented. In addition, only 16 address lines (PMA<15:0>) are available. If required, PMA14 and PMA15 can be remapped to function as PMCS1 and PMCS2, respectively.

For 80-pin devices, the dedicated PMCS2 pin is not implemented. It also only implements 16 address lines (PMA<15:0>). If required, PMA15 can be remapped to function as PMCS2.

The memory space addressable by the device depends on the number of address lines available, as well as the number of Chip Select signals required for the application. Devices with lower pin counts are more affected by Chip Select requirements, as these take away address lines. Table 20-1 shows the maximum addressable range for each pin count.

| Device                    | Dedicated Chip Select |     | Address | Address Range (bytes) |      |      |

|---------------------------|-----------------------|-----|---------|-----------------------|------|------|

| Device                    | CS1                   | CS2 | Lines   | No CS                 | 1 CS | 2 CS |

| PIC24FJXXXGA306 (64-pin)  | _                     | —   | 16      | 64K                   | 32K  | 16K  |

| PIC24FJXXXGA308 (80-pin)  | Х                     | —   | 16      | 64K 32                |      | 32K  |

| PIC24FJXXXGA310 (100-pin) | Х                     | Х   | 23      |                       | 16M  |      |

#### TABLE 20-1: EPMP FEATURE DIFFERENCES BY DEVICE PIN COUNT

#### FIGURE 22-2: ALARM MASK SETTINGS

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month Day       | Hours | Minutes Seconds |