Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga310-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Features                                                               | PIC24FJ64GA310                                   | PIC24FJ128GA310                                                                                |

|------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------|

| Operating Frequency                                                    | DC – 3                                           | 32 MHz                                                                                         |

| Program Memory (bytes)                                                 | 64K                                              | 128K                                                                                           |

| Program Memory (instructions)                                          | 22,016                                           | 44,032                                                                                         |

| Data Memory (bytes)                                                    | 8                                                | ĸ                                                                                              |

| Interrupt Sources (soft vectors/NMI traps)                             | 66 (6                                            | 62/4)                                                                                          |

| I/O Ports                                                              | Ports A, B, 0                                    | C, D, E, F, G                                                                                  |

| Total I/O Pins                                                         | 8                                                | 35                                                                                             |

| Remappable Pins                                                        | 44 (32 I/Os, 1                                   | 12 input only)                                                                                 |

| Timers:                                                                | · · · · · ·                                      |                                                                                                |

| Total Number (16-bit)                                                  | 5(                                               | (1)                                                                                            |

| 32-Bit (from paired 16-bit timers)                                     | 2                                                | 2                                                                                              |

| Input Capture Channels                                                 | 7(                                               | (1)                                                                                            |

| Output Compare/PWM Channels                                            | 7(                                               | (1)                                                                                            |

| Input Change Notification Interrupt                                    | 8                                                | 32                                                                                             |

| Serial Communications:                                                 |                                                  |                                                                                                |

| UART                                                                   | 4                                                | (1)                                                                                            |

| SPI (3-wire/4-wire)                                                    | 20                                               | (1)                                                                                            |

| l <sup>2</sup> C™                                                      | 2                                                | 2                                                                                              |

| Digital Signal Modulator                                               | Ye                                               | es                                                                                             |

| Parallel Communications<br>(EPMP/PSP)                                  | Ye                                               | es                                                                                             |

| JTAG Boundary Scan                                                     | Ye                                               | es                                                                                             |

| 12/10-Bit Analog-to-Digital Converter<br>(ADC) Module (input channels) | 2                                                | 24                                                                                             |

| Analog Comparators                                                     | 3                                                | 3                                                                                              |

| CTMU Interface                                                         | Ye                                               | es                                                                                             |

| LCD Controller (available pixels)                                      | 480 (60 SE                                       | G x 8 COM)                                                                                     |

| Resets (and delays)                                                    | MCLR, WDT, Illegal Opc<br>Hardware Traps, Config | POR, BOR, RESET Instruction,<br>ode, REPEAT Instruction,<br>guration Word Mismatch<br>LL Lock) |

| Instruction Set                                                        | 76 Base Instructions, Multiple                   | e Addressing Mode Variations                                                                   |

| Packages                                                               | 100-Pin TQFP a                                   | Ind 121-Pin BGA                                                                                |

### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FJ128GA310 FAMILY: 100-PIN DEVICES

**Note 1:** Peripherals are accessible through remappable pins.

## TABLE 4-8: OUTPUT COMPARE REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8       | Bit 7        | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|---------|---------|---------|--------|-------------|--------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC7CON1   | 01CC | _      | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1      | ENFLT0       | OCFLT2       | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC7CON2   | 01CE | FLTMD  | FLTOUT | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32        | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC7RS     | 01D0 |        |        |          |         |         |         | 0      | utput Compa | are 7 Second | ary Register |        |          |          |          |          |          | 0000          |

| OC7R      | 01D2 |        |        |          |         |         |         |        | Output C    | Compare 7 Re | egister      |        |          |          |          |          |          | 0000          |

| OC7TMR    | 01D4 |        |        |          |         |         |         |        | Timer       | Value 7 Regi | ster         |        |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-9: I<sup>2</sup>C<sup>™</sup> REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                                                  | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------------------------------------------------------|-------|-------|-------|-----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | —       | —      | —       | _      | _      | —      | —                                                      | _     |       |       |           | 2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN   | 0202 | —       | _      | —       | —      | —      | -      | —                                                      | _     |       |       | I         | 2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1BRG   | 0204 | —       | _      | —       | —      | _      | _      | —                                                      |       |       |       | Baud Rate | e Generato  | r Register   |       |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                                                 | SMEN  | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                                                 | ADD10 | IWCOL | I2COV | D/A       | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | —       | _      | —       | —      | —      | -      | I2C1 Address Register 0                                |       |       |       |           |             | 0000         |       |       |       |               |

| I2C1MSK   | 020C | —       | _      | _       | _      | _      | _      | I2C1 Address Mask Register 0                           |       |       |       |           |             | 0000         |       |       |       |               |

| I2C2RCV   | 0210 | —       | _      | —       | —      | _      | _      | _                                                      | —     |       |       |           | 2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN   | 0212 | —       | _      | —       | —      | _      | _      | —                                                      | —     |       |       | I         | 2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2BRG   | 0214 | —       | _      | —       | —      | _      | _      | —                                                      |       |       |       | Baud Rate | e Generato  | r Register   |       |       |       | 0000          |

| I2C2CON   | 0216 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN 1 |       |       |       |           |             | 1000         |       |       |       |               |

| I2C2STAT  | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                                                 | ADD10 | IWCOL | I2COV | D/A       | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD   | 021A | —       | _      | —       | —      | —      | -      |                                                        |       |       |       | 2C2 Addre | ss Register |              |       |       |       | 0000          |

| I2C2MSK   | 021C | —       |        | _       | _      | _      |        |                                                        |       |       | I2C   | 2 Address | Mask Regis  | ster         |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-26: REAL-TIME CLOCK AND CALENDAR (RTCC) REGISTER MAP

|           |      |        |        |         |         |         | <u> </u> |               |             |           |           |       |       |       |       |       |       |               |

|-----------|------|--------|--------|---------|---------|---------|----------|---------------|-------------|-----------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10   | Bit 9         | Bit 8       | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| ALRMVAL   | 0620 |        |        |         |         |         | Alarm V  | alue Register | Window Bas  | ed on ALR | MPTR<1:0  | >     |       |       |       |       |       | xxxx          |

| ALCFGRPT  | 0622 | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0   | ALRMPTR1      | ALRMPTR0    | ARPT7     | ARPT6     | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL    | 0624 |        |        |         |         |         | RTCC     | Value Registe | r Window Ba | sed on RT | CPTR<1:0> |       |       |       |       |       |       | xxxx          |

| RCFGCAL   | 0626 | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE    | RTCPTR1       | RTCPTR0     | CAL7      | CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | Note 1        |

| RTCPWC    | 0628 | PWCEN  | PWCPOL | PWCPRE  | PWSPRE  | RTCLK1  | RTCLK0   | RTCOUT1       | RTCOUT0     |           | _         | _     | _     | _     | _     | _     | _     | Note 1        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The status of the RCFGCAL and RTCPWR registers on POR is '0000', and on other Resets, it is unchanged.

## TABLE 4-27: DATA SIGNAL MODULATOR (DSM) REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|--------|--------|-------|-------|-------|-------|---------------|

| MDCON     | 062A | MDEN   |        | MDSIDL | _      | _      | _      |       |       | —      | MDOE  | MDSLR  | MDOPOL | _     | _     |       | MDBIT | 0020          |

| MDSRC     | 062C | _      | —      | —      | _      | —      | _      | —     | _     | SODIS  | —     | —      | —      | MS3   | MS2   | MS1   | MS0   | 000x          |

| MDCAR     | 062E | CHODIS | CHPOL  | CHSYNC | _      | CH3    | CH2    | CH1   | CH0   | CLODIS | CLPOL | CLSYNC | —      | CL3   | CL2   | CL1   | CL0   | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-28: COMPARATORS REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT    | 0630 | CMIDL  | —      | _      | _      |        | C3EVT  | C2EVT   | C1EVT   | —      | _      | _     | —     |       | C3OUT | C2OUT | C10UT | 0000          |

| CVRCON    | 0632 | _      | _      | _      | _      | _      | CVREFP | CVREFM1 | CVREFM0 | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON    | 0634 | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON    | 0636 | CON    | COE    | CPOL   | -      |        | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | —     | CREF  | -     | —     | CCH1  | CCH0  | 0000          |

| CM3CON    | 0638 | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | —     | _     | CCH1  | CCH0  | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 8-27: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0           | R/W-1                | R/W-0                                      | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

|---------------|----------------------|--------------------------------------------|------------------|-------------------|------------------|-----------------|---------|

| _             | T4IP2                | T4IP1                                      | T4IP0            | —                 | OC4IP2           | OC4IP1          | OC4IP0  |

| bit 15        |                      |                                            |                  |                   |                  |                 | bit 8   |

|               |                      |                                            |                  |                   |                  |                 |         |

| U-0           | R/W-1                | R/W-0                                      | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

| —             | OC3IP2               | OC3IP1                                     | OC3IP0           | —                 | DMA2IP2          | DMA2IP1         | DMA2IP0 |

| bit 7         |                      |                                            |                  |                   |                  |                 | bit     |

|               |                      |                                            |                  |                   |                  |                 |         |

| Legend:       | - 1-:4               |                                            | L :4             |                   |                  | l = = (0)       |         |

| R = Readable  |                      | W = Writable                               |                  | -                 | mented bit, read |                 |         |

| -n = Value at | POR                  | '1' = Bit is set                           |                  | '0' = Bit is cle  | ared             | x = Bit is unkr | IOWN    |

| bit 15        | Unimplemen           | ted: Read as '                             | כי               |                   |                  |                 |         |

| bit 14-12     |                      | imer4 Interrupt                            |                  |                   |                  |                 |         |

|               |                      | pt is Priority 7 (                         | -                | interrupt)        |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               | 001 = Interru        | pt is Priority 1                           |                  |                   |                  |                 |         |

|               | 000 <b>= Interru</b> | pt source is dis                           | abled            |                   |                  |                 |         |

| bit 11        | Unimplemen           | ted: Read as '                             | כי               |                   |                  |                 |         |

| bit 10-8      |                      | Output Compa                               |                  | -                 | y bits           |                 |         |

|               | 111 = Interru        | pt is Priority 7 (                         | highest priority | interrupt)        |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               |                      | pt is Priority 1                           | ablad            |                   |                  |                 |         |

| bit 7         |                      | pt source is dis<br><b>ited:</b> Read as ' |                  |                   |                  |                 |         |

| bit 6-4       | -                    | : Output Compa                             |                  | Intorrunt Priorit | v bite           |                 |         |

| Dit 0-4       |                      | pt is Priority 7 (                         |                  | -                 | y bits           |                 |         |

|               | •                    | prior nonty / (                            |                  | interrupt)        |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               | •<br>001 - Interru   | pt is Priority 1                           |                  |                   |                  |                 |         |

|               |                      | pt source is dis                           | abled            |                   |                  |                 |         |

| bit 3         | Unimplemen           | ted: Read as '                             | כ'               |                   |                  |                 |         |

| bit 2-0       | DMA2IP<2:0           | >: DMA Chann                               | el 2 Interrupt F | riority bits      |                  |                 |         |

|               | 111 = Interru        | pt is Priority 7 (                         | highest priority | interrupt)        |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               |                      |                                            |                  |                   |                  |                 |         |

|               | •                    |                                            |                  |                   |                  |                 |         |

|               | •<br>001 = Interru   | pt is Priority 1                           |                  |                   |                  |                 |         |

## REGISTER 8-29: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | SPI2IP2 | SPI2IP1 | SPI2IP0 | —   | SPF2IP2 | SPF2IP1 | SPF2IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:      |            |                                                   |                       |                    |  |

|--------------|------------|---------------------------------------------------|-----------------------|--------------------|--|

| R = Readal   | ole bit    | W = Writable bit                                  | U = Unimplemented bit | , read as '0'      |  |

| -n = Value a | at POR     | '1' = Bit is set                                  | '0' = Bit is cleared  | x = Bit is unknown |  |

|              |            |                                                   |                       |                    |  |

| bit 15-7     | Unimplen   | nented: Read as '0'                               |                       |                    |  |

| bit 6-4      | SPI2IP<2   | :0>: SPI2 Event Interrupt Pr                      | iority bits           |                    |  |

|              | 111 = Inte | errupt is Priority 7 (highest p                   | riority interrupt)    |                    |  |

|              | •          |                                                   |                       |                    |  |

|              | •          |                                                   |                       |                    |  |

|              | •          | arrupt in Drigrity 1                              |                       |                    |  |

|              |            | errupt is Priority 1<br>errupt source is disabled |                       |                    |  |

| bit 3        | Unimplen   | nented: Read as '0'                               |                       |                    |  |

| bit 2-0      | SPF2IP<2   | ::0>: SPI2 Fault Interrupt Pr                     | iority bits           |                    |  |

|              | 111 = Inte | errupt is Priority 7 (highest p                   | riority interrupt)    |                    |  |

|              | •          |                                                   |                       |                    |  |

|              | •          |                                                   |                       |                    |  |

|              | •          |                                                   |                       |                    |  |

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0           | U-0                                        | U-0                                   | U-0     | U-0              | R/W-1            | R/W-0           | R/W-0   |

|---------------|--------------------------------------------|---------------------------------------|---------|------------------|------------------|-----------------|---------|

| —             | —                                          | —                                     | _       | —                | INT4IP2          | INT4IP1         | INT4IP0 |

| pit 15        |                                            |                                       |         |                  |                  |                 | bit 8   |

|               | D/// 4                                     | DAMA                                  | DAMO    |                  |                  |                 |         |

| U-0           | R/W-1                                      | R/W-0                                 | R/W-0   | U-0              | U-0              | U-0             | U-0     |

|               | INT3IP2                                    | INT3IP1                               | INT3IP0 | —                | —                | _               |         |

| oit 7         |                                            |                                       |         |                  |                  |                 | bit (   |

| Legend:       |                                            |                                       |         |                  |                  |                 |         |

| R = Readabl   | le bit                                     | W = Writable                          | bit     | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at | t POR                                      | '1' = Bit is set                      |         | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

|               | •<br>•<br>001 = Interrup<br>000 = Interrup | ot source is dis                      | abled   | interrupt)       |                  |                 |         |

| bit 7         | Unimplement                                | ted: Read as '                        | )'      |                  |                  |                 |         |

| bit 6-4       | 111 = Interrup<br>•<br>•                   | External Interr<br>ot is Priority 7 ( |         |                  |                  |                 |         |

|               | 001 = Interrup<br>000 = Interrup           | ot is Priority 1<br>ot source is dis  | abled   |                  |                  |                 |         |

## REGISTER 8-34: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

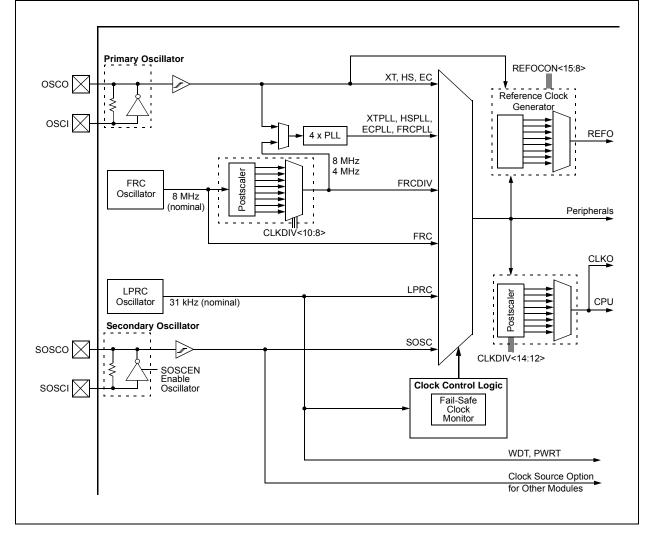

## 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Oscillator" (DS39700) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The oscillator system for PIC24FJ128GA310 family devices has the following features:

- A total of four external and internal oscillator options as clock sources, providing 11 different clock modes

- On-chip 4x PLL to boost internal operating frequency on select internal and external oscillator sources

- Software-controllable switching between various clock sources

- Software-controllable postscaler for selective clocking of CPU for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- A separate and independently configurable system clock output for synchronizing external hardware

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: PIC24FJ128GA310 FAMILY CLOCK DIAGRAM

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7  | CLKLOCK: Clock Selection Lock Enabled bit                                                |

|--------|------------------------------------------------------------------------------------------|

|        | If FSCM is Enabled (FCKSM1 = 1):                                                         |

|        | 1 = Clock and PLL selections are locked                                                  |

|        | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|        | If FSCM is Disabled (FCKSM1 = 0):                                                        |

|        | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6  | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                               |

|        | 1 = I/O lock is active                                                                   |

|        | 0 = I/O lock is not active                                                               |

| bit 5  | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                 |

|        | 1 = PLL module is in lock or PLL module start-up timer is satisfied                      |

|        | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled          |

| bit 4  | Unimplemented: Read as '0'                                                               |

| bit 3  | CF: Clock Fail Detect bit                                                                |

|        | 1 = FSCM has detected a clock failure                                                    |

|        | <ul><li>0 = No clock failure has been detected</li></ul>                                 |

| bit 2  | POSCEN: Primary Oscillator Sleep Enable bit                                              |

|        | 1 = Primary oscillator continues to operate during Sleep mode                            |

|        | 0 = Primary oscillator is disabled during Sleep mode                                     |

| bit 1  | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|        | 1 = Enables Secondary Oscillator                                                         |

|        | 0 = Disables Secondary Oscillator                                                        |

| bit 0  | OSWEN: Oscillator Switch Enable bit                                                      |

|        | 1 = Initiates an oscillator switch to a clock source specified by the NOSC<2:0> bits     |

|        | 0 = Oscillator switch is complete                                                        |

| Note 1 | Poppet values for those bits are determined by the ENOSCY Configuration bits             |

- **Note 1:** Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a Non-PLL Clock mode is selected.

| REGISTER 11-29: | <b>RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2</b> |

|-----------------|-------------------------------------------------------|

|-----------------|-------------------------------------------------------|

| —         —         RP5R5 <sup>(1)</sup> RP5R4 <sup>(1)</sup> RP5R3 <sup>(1)</sup> RP5R2 <sup>(1)</sup> RP5R1 <sup>(1)</sup> RI           bit 15 | R/W-0               |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| bit 15                                                                                                                                           | 95R0 <sup>(1)</sup> |

|                                                                                                                                                  | bit 8               |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RP4R5 | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

- RP5R<5:0>: RP5 Output Pin Mapping bits<sup>(1)</sup> bit 13-8

- Peripheral Output Number n is assigned to pin, RP5 (see Table 11-4 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP4R<5:0>:** RP4 Output Pin Mapping bits

- Peripheral Output Number n is assigned to pin, RP4 (see Table 11-4 for peripheral function numbers).

Note 1: These bits are unimplemented in 64-pin devices; read as '0'.

## **REGISTER 11-30: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | _   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP7R<5:0>: RP7 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP7 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP6R<5:0>: RP6 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP6 (see Table 11-4 for peripheral function numbers). |

| R/W-0        | U-0                                                                                                                                                             | R/W-0                               | U-0             | U-0              | U-0              | R/W-0           | R/W-0         |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|------------------|-----------------|---------------|--|--|

| TON          |                                                                                                                                                                 | TSIDL                               |                 | _                |                  | TIECS1          | TIECS0        |  |  |

| bit 15       |                                                                                                                                                                 |                                     |                 |                  |                  |                 | bit 8         |  |  |

| U-0          | R/W-0                                                                                                                                                           | R/W-0                               | R/W-0           | U-0              | R/W-0            | R/W-0           | U-0           |  |  |

|              | TGATE                                                                                                                                                           | TCKPS1                              | TCKPS0          | _                | TSYNC            | TCS             | _             |  |  |

| bit 7        |                                                                                                                                                                 |                                     |                 |                  |                  |                 | bit 0         |  |  |

| Legend:      |                                                                                                                                                                 |                                     |                 |                  |                  |                 |               |  |  |

| R = Readab   | le bit                                                                                                                                                          | W = Writable                        | bit             | U = Unimplen     | nented bit, read | d as '0'        |               |  |  |

| -n = Value a | t POR                                                                                                                                                           | '1' = Bit is set                    |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown          |  |  |

| bit 15       | <b>TON:</b> Timer1<br>1 = Starts 16<br>0 = Stops 16                                                                                                             | bit Timer1                          |                 |                  |                  |                 |               |  |  |

| bit 14       | Unimplemen                                                                                                                                                      | ted: Read as '                      | 0'              |                  |                  |                 |               |  |  |

| bit 13       | TSIDL: Time                                                                                                                                                     | r1 Stop in Idle M                   | /lode bit       |                  |                  |                 |               |  |  |

|              |                                                                                                                                                                 | nues module op<br>es module opera   |                 |                  | dle mode         |                 |               |  |  |

| bit 12-10    | Unimplemen                                                                                                                                                      | ted: Read as '                      | 0'              |                  |                  |                 |               |  |  |

| bit 9-8      | TIECS<1:0>: Timer1 Extended Clock Source Select bits (selected when TCS = 1)                                                                                    |                                     |                 |                  |                  |                 |               |  |  |

|              | <ul> <li>11 = Unimplemented, do not use</li> <li>10 = LPRC oscillator</li> <li>01 = T1CK external clock input</li> <li>00 = SOSC</li> </ul>                     |                                     |                 |                  |                  |                 |               |  |  |

| bit 7        | Unimplemen                                                                                                                                                      | ted: Read as '                      | 0'              |                  |                  |                 |               |  |  |

| bit 6        | TGATE: Time                                                                                                                                                     | er1 Gated Time                      | Accumulation    | Enable bit       |                  |                 |               |  |  |

|              | When TCS = 1:         This bit is ignored.         When TCS = 0:         1 = Gated time accumulation is enabled         0 = Gated time accumulation is disabled |                                     |                 |                  |                  |                 |               |  |  |

| bit 5-4      | <b>TCKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:256<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1                                             |                                     |                 |                  |                  |                 |               |  |  |

| bit 3        | Unimplemen                                                                                                                                                      | nted: Read as '                     | 0'              |                  |                  |                 |               |  |  |

| bit 2        |                                                                                                                                                                 | er1 External Clo                    | ock Input Sync  | hronization Sel  | ect bit          |                 |               |  |  |

|              |                                                                                                                                                                 | nizes external o<br>t synchronize e |                 | nput             |                  |                 |               |  |  |

|              | This bit is ign                                                                                                                                                 |                                     |                 |                  |                  |                 |               |  |  |

| bit 1        | TCS: Timer1                                                                                                                                                     | Clock Source S                      | Select bit      |                  |                  |                 |               |  |  |

|              |                                                                                                                                                                 | d clock is selec<br>clock (Fosc/2)  | ted by the time | er               |                  |                 |               |  |  |

| bit 0        | Unimplemen                                                                                                                                                      | ted: Read as '                      | 0'              |                  |                  |                 |               |  |  |

|              | hanging the val                                                                                                                                                 |                                     | hile the timer  | is running (TON  | l = 1) causes t  | he timer presca | le counter to |  |  |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup>

## 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs and the even module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

## 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every  $4^{th}$  or  $16^{th}$ ). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- 3. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired sync/trigger source.

- 5. Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source.

- 6. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG, and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8>) and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bits settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to set the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- **Note:** For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired Capture mode.

The module is ready to capture events when the time base and the sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

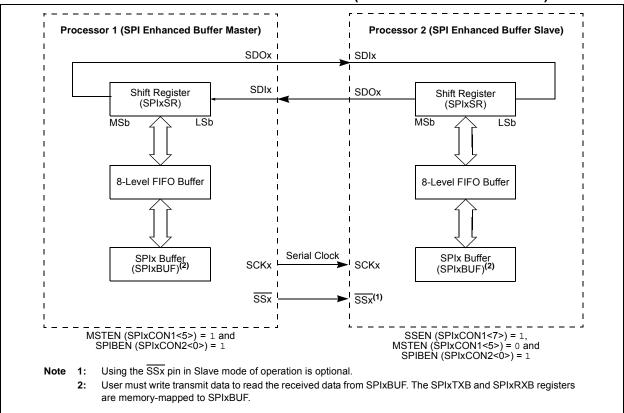

### FIGURE 16-4: SPIX MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

NOTES:

| R/W-0          | U-0                                                                            | R/W-0                                                                                          | R/W-0                                                | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|----------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------|------------------|-----------------|--------|--|--|--|

| CTMUEN         | —                                                                              | CTMUSIDL                                                                                       | TGEN                                                 | EDGEN            | EDGSEQEN         | IDISSEN         | CTTRIG |  |  |  |

| bit 15         |                                                                                |                                                                                                |                                                      |                  |                  |                 | bit 8  |  |  |  |

| U-0            | U-0                                                                            | U-0                                                                                            | U-0                                                  | U-0              | U-0              | U-0             | U-0    |  |  |  |

| _              | —                                                                              | —                                                                                              | _                                                    |                  | _                | _               | _      |  |  |  |

| bit 7          |                                                                                |                                                                                                |                                                      |                  |                  |                 | bit (  |  |  |  |

| Legend:        |                                                                                |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

| R = Readabl    | e bit                                                                          | W = Writable b                                                                                 | bit                                                  | U = Unimple      | mented bit, read | as '0'          |        |  |  |  |

| -n = Value at  | POR                                                                            | '1' = Bit is set                                                                               |                                                      | '0' = Bit is cle |                  | x = Bit is unkn | iown   |  |  |  |

|                |                                                                                |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

| bit 15         | CTMUEN: CT                                                                     | MU Enable bit                                                                                  |                                                      |                  |                  |                 |        |  |  |  |

|                | 1 = Module is enabled                                                          |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

|                | 0 = Module is                                                                  | s disabled                                                                                     |                                                      |                  |                  |                 |        |  |  |  |

| bit 14         | Unimplemen                                                                     | ted: Read as '0                                                                                | ,                                                    |                  |                  |                 |        |  |  |  |

| bit 13         | CTMUSIDL: CTMU Stop in Idle Mode bit                                           |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

|                |                                                                                | ues module opera                                                                               |                                                      |                  | dle mode         |                 |        |  |  |  |

| bit 12         | TGEN: Time Generation Enable bit                                               |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

|                |                                                                                | edge delay gen<br>edge delay gen                                                               |                                                      |                  |                  |                 |        |  |  |  |

| bit 11         | EDGEN: Edg                                                                     | e Enable bit                                                                                   |                                                      |                  |                  |                 |        |  |  |  |

|                | 1 = Edges are not blocked                                                      |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

|                | 0 = Edges are blocked                                                          |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

| bit 10         | EDGSEQEN: Edge Sequence Enable bit                                             |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

|                |                                                                                | vent must occur<br>sequence is ne                                                              |                                                      | 2 event can o    | ccur             |                 |        |  |  |  |

|                | IDISSEN: Analog Current Source Control bit                                     |                                                                                                |                                                      |                  |                  |                 |        |  |  |  |

| bit 9          | -                                                                              | -                                                                                              | urce Control b                                       | oit              |                  |                 |        |  |  |  |

| bit 9          | <b>IDISSEN:</b> Ana<br>1 = Analog c                                            | -                                                                                              | utput is groun                                       | ded              |                  |                 |        |  |  |  |

| bit 9<br>bit 8 | IDISSEN: Ana<br>1 = Analog ci<br>0 = Analog ci                                 | alog Current So<br>urrent source or                                                            | utput is ground<br>utput is not gro                  | ded              |                  |                 |        |  |  |  |

|                | IDISSEN: Ana<br>1 = Analog cu<br>0 = Analog cu<br>CTTRIG: CTM<br>1 = Trigger o | alog Current So<br>urrent source ou<br>urrent source ou<br>/IU Trigger Con<br>utput is enabled | utput is ground<br>utput is not gro<br>trol bit<br>I | ded              |                  |                 |        |  |  |  |

|                | IDISSEN: Ana<br>1 = Analog cu<br>0 = Analog cu<br>CTTRIG: CTM<br>1 = Trigger o | alog Current So<br>urrent source ou<br>urrent source ou<br>MU Trigger Con                      | utput is ground<br>utput is not gro<br>trol bit<br>I | ded              |                  |                 |        |  |  |  |

## REGISTER 27-1: CTMUCON1: CTMU CONTROL REGISTER 1

## 29.0 SPECIAL FEATURES

- **Note:** This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the following sections of the *"dsPIC33/PIC24 Family Reference Manual"*. The information in this data sheet supersedes the information in the FRMs.

- "Watchdog Timer (WDT)" (DS39697)

- "High-Level Device Integration" (DS39719)

- "Programming and Diagnostics" (DS39716)

PIC24FJ128GA310 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup>

- In-Circuit Emulation

## 29.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location, F80000h. A detailed explanation of the various bit functions is provided in Register 29-1 through Register 29-6.

Note that address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh) which can only be accessed using Table Reads and Table Writes.

### 29.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ128GA310 FAMILY DEVICES

In PIC24FJ128GA310 family devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the three words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 29-1. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among several locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The upper byte of all Flash Configuration Words in program memory should always be '0000 0000'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '0's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

## TABLE 29-1: FLASH CONFIGURATION WORD LOCATIONS FOR PIC24FJ128GA310 FAMILY DEVICES

| Device          | Configuration Word Addresses |        |        |        |  |  |

|-----------------|------------------------------|--------|--------|--------|--|--|

|                 | 1                            | 2      | 3      | 4      |  |  |

| PIC24FJ64GA3XX  | ABFEh                        | ABFCh  | ABFAh  | ABF8h  |  |  |

| PIC24FJ128GA3XX | 157FEh                       | 157FCh | 157FAh | 157F8h |  |  |

### 29.4.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes or reads in two ways. The primary protection method is the same as that of the RP registers – shadow registers contain a complimentary value which is constantly compared with the actual value.

To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. When the GCP bit is set, the source data for device configuration is also protected as a consequence. Even if General Segment protection is not enabled, the device configuration can be protected by using the appropriate code segment protection setting.

## 29.5 JTAG Interface

PIC24FJ128GA310 family devices implement a JTAG interface, which supports boundary scan device testing.

## 29.6 In-Circuit Serial Programming

PIC24FJ128GA310 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power (VDD), ground (VSS) and MCLR. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 29.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS and the PGECx/PGEDx pin pair designated by the ICSx Configuration bits. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

| DC CHARACTERISTICS |                        | Standard Operating Conditions: 2V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |                          |              |                                                |  |

|--------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|--------------|------------------------------------------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах                                                                                                                                            | Units | Operating<br>Temperature | Vdd          | Conditions                                     |  |

| Power-Dov          | vn Current (           | IPD)                                                                                                                                           |       |                          |              |                                                |  |

| DC60               |                        |                                                                                                                                                | μA    | -40°C                    | 2.0V         |                                                |  |

|                    | 3.7                    |                                                                                                                                                | μA    | +25°C                    |              |                                                |  |

|                    | 6.2                    |                                                                                                                                                | μA    | +60°C                    |              |                                                |  |

|                    | 13.6                   | 27.5                                                                                                                                           | μA    | +85°C                    |              |                                                |  |

|                    | _                      |                                                                                                                                                | μA    | -40°                     | 3.3V         | Sleep <sup>(2)</sup>                           |  |

|                    | 3.8                    |                                                                                                                                                | μA    | +25°C                    |              |                                                |  |

|                    | 6.3                    |                                                                                                                                                | μA    | +60°C                    |              |                                                |  |

|                    | 13.7                   | 28                                                                                                                                             | μA    | +85°C                    |              |                                                |  |

| DC61               | _                      |                                                                                                                                                | μA    | -40°                     | 2.0V         |                                                |  |

|                    | 0.33                   |                                                                                                                                                | μA    | +25°C                    |              | - Low-Voltage Sleep <sup>(3)</sup>             |  |

|                    | 2                      |                                                                                                                                                | μA    | +60°C                    |              |                                                |  |

|                    | 7.7                    | 14.5                                                                                                                                           | μA    | +85°C                    |              |                                                |  |

|                    | _                      |                                                                                                                                                | μΑ    | -40°                     | 3.3V         |                                                |  |

|                    | 0.34                   | _                                                                                                                                              | μΑ    | +25°C                    |              |                                                |  |

|                    | 2                      | _                                                                                                                                              | μA    | +60°C                    |              |                                                |  |

|                    | 7.9                    | 15                                                                                                                                             | μA    | +85°C                    |              |                                                |  |

| DC70               | _                      | _                                                                                                                                              | μA    | -40°                     | 2.0V<br>3.3V |                                                |  |