Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga310t-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 121-PIN DEVICES (CONTINUED)

| Pin | Function                                 | Pin | Function                                  |

|-----|------------------------------------------|-----|-------------------------------------------|

| J1  | AN3/C2INA/SEG4/CN5/RB3                   | K7  | AN14/RP14/SEG8/CTPLS/CTED5/PMA1/CN32/RB14 |

| J2  | AN2/C2INB/RP13/SEG5/CTCMP/CTED13/CN4/RB2 | K8  | VDD                                       |

| J3  | PGED2/AN7/ <b>RP7/</b> CN25/RB7          | K9  | RP5/SEG39/CN21/RD15                       |

| J4  | AVDD                                     | K10 | RP16/SEG12/CN71/RF3                       |

| J5  | AN11/PMA12/CN29/RB11                     | K11 | RP30/SEG40/CN70/RF2                       |

| J6  | TCK/CN34/RA1                             | L1  | PGEC2/AN6/RP6/LCDBIAS3/CN24/RB6           |

| J7  | AN12/SEG18/CTED2/PMA11/CN30/RB12         | L2  | VREF-/SEG36/PMA7/CN41/RA9                 |

| J8  | N/C                                      | L3  | AVss                                      |

| J9  | N/C                                      | L4  | AN9/RP9/COM6/SEG30/CN27/RB9               |

| J10 | RP15/SEG41/CN74/RF8                      | L5  | CVREF/AN10/COM5/SEG29/PMA13/CN28/RB10     |

| J11 | SDA1/SEG47/CN73/RG3                      | L6  | RP31/SEG54/CN76/RF13                      |

| K1  | PGEC1/CVREF-/AN1/RP1/SEG6/CTED12/CN3/RB1 | L7  | AN13/SEG19/CTED1/PMA10/CN31/RB13          |

| K2  | PGD1/CVREF+/AN0/RP0/SEG7/CN2/RB0         | L8  | AN15/RP29/SEG9/CTED6/REFO/PMA0/CN12/RB15  |

| K3  | VREF+/SEG37/PMA6/CN42/RA10               | L9  | RPI43/SEG38/CN20/RD14                     |

| K4  | AN8/RP8/COM7/SEG31/CN26/RB8              | L10 | RP10/SEG10/PMA9/CN17/RF4                  |

| K5  | N/C                                      | L11 | RP17/SEG11/PMA8/CN18/RF5                  |

| K6  | RPI32/SEG55/CTED7/PMA18/CN75/RF12        |     |                                           |

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select functions.

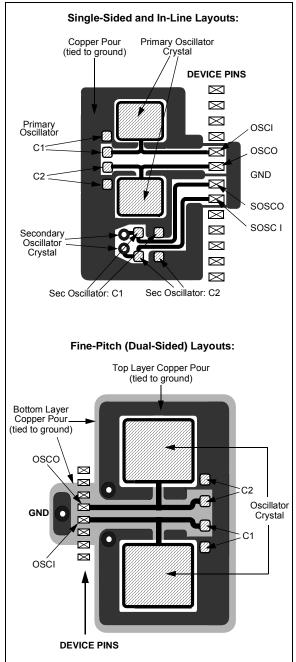

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### FIGURE 2-5:

### PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

### 3.2 CPU Control Registers

### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                                                                                      | U-0                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0               | U-0                | U-0                           | U-0              | R/W-0           |  |  |  |

|------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-------------------------------|------------------|-----------------|--|--|--|

| _                                                                                        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                 | —                  | _                             | —                | DC              |  |  |  |

| bit 15                                                                                   |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  | bit 8           |  |  |  |

|                                                                                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

| R/W-0 <sup>(1</sup>                                                                      |                     | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R-0               | R/W-0              | R/W-0                         | R/W-0,           | R/W-0           |  |  |  |

| IPL2 <sup>(2)</sup>                                                                      | IPL1 <sup>(2)</sup> | <sup>(2)</sup> IPL0 <sup>(2)</sup> RA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | Ν                  | OV                            | Z                | С               |  |  |  |

| bit 7                                                                                    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  | bit 0           |  |  |  |

|                                                                                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

| Legend:                                                                                  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

| R = Read                                                                                 | able bit            | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | oit               | U = Unimplem       | nented bit, read              | l as '0'         |                 |  |  |  |

| -n = Value                                                                               | e at POR            | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | '0' = Bit is clea  | ared                          | x = Bit is unki  | nown            |  |  |  |

|                                                                                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

| bit 15-9                                                                                 | Unimplemen          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )'                |                    |                               |                  |                 |  |  |  |

| bit 8                                                                                    | DC: ALU Hal         | f Carry/Borrow I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | oit               |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | out from the 4 <sup>th</sup> I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ow-order bit (f   | or byte-sized da   | ata) or 8 <sup>th</sup> low-o | order bit (for w | ord-sized data) |  |  |  |

|                                                                                          | of the res          | sult occurred<br>out from the 4 <sup>th</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | or oth low or     | lar hit of the rea |                               | d                |                 |  |  |  |

| hit 7 E                                                                                  | •                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               | eu               |                 |  |  |  |

| bit 7-5 <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | <ul> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>110 = CPU Interrupt Priority Level is 6 (14)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | 101 = CPU Interrupt Priority Level is 5 (14)101 = CPU Interrupt Priority Level is 5 (13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | 100 = CPU Interrupt Priority Level is 4 (12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | nterrupt Priority<br>nterrupt Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | Interrupt Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | )                  |                               |                  |                 |  |  |  |

|                                                                                          |                     | nterrupt Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                    |                               |                  |                 |  |  |  |

| bit 4                                                                                    | <b>RA:</b> REPEAT   | Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          |                     | loop is in progre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          | 0 = REPEAT          | loop is not in pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ogress            |                    |                               |                  |                 |  |  |  |

| bit 3                                                                                    | N: ALU Nega         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                    |                               |                  |                 |  |  |  |

|                                                                                          | 1 = Result w        | Ų                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (                 | · · - <b>)</b>     |                               |                  |                 |  |  |  |

| L:1 0                                                                                    |                     | as not negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (zero or positi   | ve)                |                               |                  |                 |  |  |  |