Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

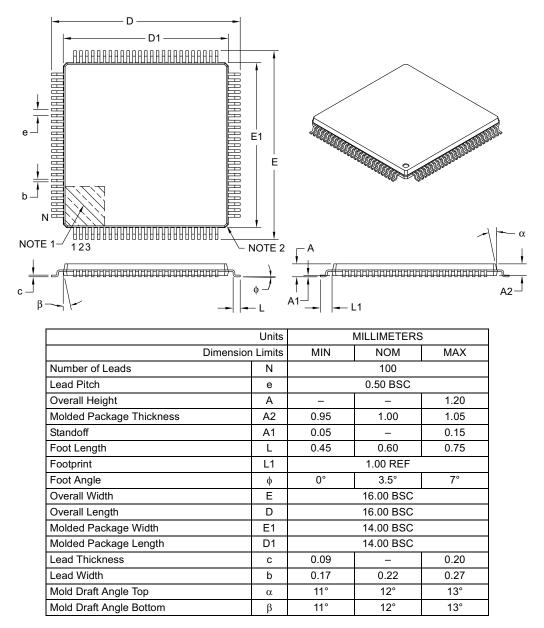

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga310t-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|------|--------|---------|---------|---------|--------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|---------|---------------|

| IPC16        | 00C4 | _      | CRCIP2  | CRCIP1  | CRCIP0  |        | U2ERIP2 | U2ERIP1 | U2ERIP0 | _     | U1ERIP2 | U1ERIP1 | U1ERIP0 | _       |         | _       | _       | 4440          |

| IPC18        | 00C8 | _      | _       | _       | _       | _      | _       | _       | _       | _     | _       | _       | _       | _       | HLVDIP2 | HLVDIP1 | HLVDIP0 | 0004          |

| IPC19        | 00CA | _      | _       | _       | _       | _      | _       | _       | _       | _     | CTMUIP2 | CTMUIP1 | CTMUIP0 | _       | _       | _       | _       | 0040          |

| IPC20        | 00CC | _      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2 | U3RXIP1 | U3RXIP0 | _     | U3ERIP2 | U3ERIP1 | U3ERIP0 | _       | _       | _       | _       | 4440          |

| IPC21        | 00CE | _      | U4ERIP2 | U4ERIP1 | U4ERIP0 |        |         | _       | _       |       | _       | _       | _       | _       |         |         | —       | 4000          |

| IPC22        | 00D0 | _      |         | _       |         |        |         | _       | _       |       | U4TXIP2 | U4TXIP1 | U4TXIP0 | _       | U4RXIP2 | U4RXIP1 | U4RXIP0 | 0044          |

| IPC25        | 00D6 | _      |         | _       |         |        |         | _       | _       |       | _       | _       | _       | _       | LCDIP2  | LCDIP1  | LCDIP0  | 0004          |

| IPC29        | 00DE | _      | _       | _       | _       | _      | _       | _       | _       |       | JTAGIP2 | JTAGIP1 | JTAGIP0 | _       | _       | _       | _       | 0040          |

| INTTREG      | 00E0 | CPUIRQ |         | VHOLD   |         | ILR3   | ILR2    | ILR1    | ILR0    |       | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-6: TIMER REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7        | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|---------------------------|--------|--------|--------|--------|--------------|--------------|--------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1      | 0100 |        |                           |        |        |        |        |              | Timer1 F     | Register     |              |        |        |       |       |       |       | 0000          |

| PR1       | 0102 |        | Timer1 Period Register    |        |        |        |        |              |              |              |              | FFFF   |        |       |       |       |       |               |

| T1CON     | 0104 | TON    | _                         | TSIDL  | _      | _      | _      | TIECS1       | TIECS0       | _            | TGATE        | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2      | 0106 |        |                           |        |        |        |        |              | Timer2 F     | Register     |              |        |        |       |       |       |       | 0000          |

| TMR3HLD   | 0108 |        |                           |        |        |        | Timer  | 3 Holding R  | egister (for | 32-bit time  | operations   | only)  |        |       |       |       |       | 0000          |

| TMR3      | 010A |        |                           |        |        |        |        |              | Timer3 F     | Register     |              |        |        |       |       |       |       | 0000          |

| PR2       | 010C |        | Timer2 Period Register FF |        |        |        |        |              |              |              | FFFF         |        |        |       |       |       |       |               |

| PR3       | 010E |        |                           |        |        |        |        |              | Timer3 Peri  | od Register  |              |        |        |       |       |       |       | FFFF          |

| T2CON     | 0110 | TON    | _                         | TSIDL  | _      | _      | _      | _            | _            | _            | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON     | 0112 | TON    | _                         | TSIDL  | _      | _      | _      | _            | _            | _            | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

| TMR4      | 0114 |        |                           |        |        |        |        |              | Timer4 F     | Register     |              |        |        |       |       |       |       | 0000          |

| TMR5HLD   | 0116 |        |                           |        |        |        | Tin    | ner5 Holding | g Register ( | or 32-bit op | perations or | nly)   |        |       |       |       |       | 0000          |

| TMR5      | 0118 |        |                           |        |        |        |        |              | Timer5 F     | Register     |              |        |        |       |       |       |       | 0000          |

| PR4       | 011A |        | Timer4 Period Register FF |        |        |        |        |              |              | FFFF         |              |        |        |       |       |       |       |               |

| PR5       | 011C |        | Timer5 Period Register FF |        |        |        |        |              |              | FFFF         |              |        |        |       |       |       |       |               |

| T4CON     | 011E | TON    |                           | TSIDL  |        | —      | —      | _            |              | _            | TGATE        | TCKPS1 | TCKPS0 | T45   | —     | TCS   | —     | 0000          |

| T5CON     | 0120 | TON    | _                         | TSIDL  | _      | _      | _      | _            | _            | _            | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-30: PERIPHERAL PIN SELECT REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14 | Bit 13                | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0     | 06C0 | _      | _      | RP1R5                 | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | —     | —     | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1     | 06C2 | _      | _      | RP3R5                 | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2     | 06C4 | —      | _      | RP5R5 <sup>(1)</sup>  | RP5R4 <sup>(1)</sup>  | RP5R3 <sup>(1)</sup>  | RP5R2 <sup>(1)</sup>  | RP5R1 <sup>(1)</sup>  | RP5R0 <sup>(1)</sup>  | _     | _     | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3     | 06C6 | —      | _      | RP7R5                 | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | _     | _     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4     | 06C8 | _      | _      | RP9R5                 | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | _     | _     | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5     | 06CA | _      | _      | RP11R5                | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | _     | _     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6     | 06CC | —      | _      | RP13R5                | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | _     | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 | 0000          |

| RPOR7     | 06CE | —      | _      | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> | _     | _     | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR8     | 06D0 | _      | _      | RP17R5                | RP17R4                | RP17R3                | RP17R2                | RP17R1                | RP17R0                | _     | _     | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 | 0000          |

| RPOR9     | 06D2 | —      | _      | RP19R5                | RP19R4                | RP19R3                | RP19R2                | RP19R1                | RP19R0                | _     | _     | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 | 0000          |

| RPOR10    | 06D4 | _      | _      | RP21R5                | RP21R4                | RP21R3                | RP21R2                | RP21R1                | RP21R0                | _     | _     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 | 0000          |

| RPOR11    | 06D6 | _      | _      | RP23R5                | RP23R4                | RP23R3                | RP23R2                | RP23R1                | RP23R0                | _     | _     | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 | 0000          |

| RPOR12    | 06D8 | _      | _      | RP25R5                | RP25R4                | RP25R3                | RP25R2                | RP25R1                | RP25R0                | _     | _     | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 | 0000          |

| RPOR13    | 06DA | _      | _      | RP27R5                | RP27R4                | RP27R3                | RP27R2                | RP27R1                | RP27R0                | _     | _     | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 | 0000          |

| RPOR14    | 06DC | —      | _      | RP29R5                | RP29R4                | RP29R3                | RP29R2                | RP29R1                | RP29R0                | _     | _     | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 | 0000          |

| RPOR15    | 06DE |        |        | RP31R5 <sup>(2)</sup> | RP31R4 <sup>(2)</sup> | RP31R3 <sup>(2)</sup> | RP31R2 <sup>(2)</sup> | RP31R1 <sup>(2)</sup> | RP31R0 <sup>(2)</sup> | _     |       | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 64-pin devices, read as '0'.

2: These bits are unimplemented in 64-pin and 80-pin devices, read as '0'.

#### TABLE 4-31: SYSTEM CONTROL (CLOCK AND RESET) REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|--------|--------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      | RETEN  | —      | DPSLP  | CM     | VREGS  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP  | IDLE   | BOR    | POR    | Note 1        |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | _     | CF     | POSCEN | SOSCEN | OSWEN  | Note 2        |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _      | _      | _     | _      | _      | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _      |        |       | TUN    | <5:0>  |        |        | 0000          |

| REFOCON   | 074E | ROEN   | _      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _      | _      | _     | _      | _      | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN |        | HLSIDL |        | _      |        |        | —      | VDIR    | BGVST  | IRVST  | _     | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 0000          |

| RCON2     | 0762 | _      | _      | _      |        | _      | _      | _      | _      | _       | _      |        | r     | VDDBOR | VDDPOR | VBPOR  | VBAT   | Note 1        |

Legend: — = unimplemented, read as '0'; r = reserved. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 7.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 9.0 "Oscillator Configuration" for more information.

| Flag Bit          | Setting Event                                     | Clearing Event                     |

|-------------------|---------------------------------------------------|------------------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                                |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                                |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                                |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                                |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                                |

| WDTO (RCON<4>)    | WDT Time-out                                      | CLRWDT, PWRSAV<br>Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #0 Instruction                             | POR                                |

| DPSLP (RCON<10>)  | PWRSAV #0 Instruction while DSEN bit is Set       | POR                                |

| IDLE (RCON<2>)    | PWRSAV #1 Instruction                             | POR                                |

| BOR (RCON<1>)     | POR, BOR                                          | —                                  |

| POR (RCON<0>)     | POR                                               | —                                  |

TABLE 7-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

## 7.1 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC<2:0> bits in Flash Configuration Word 2 (CW2) (see Table 7-2). The RCFGCAL and NVMCON registers are only affected by a POR.

## 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the system Reset signal, SYSRST, is released after the POR delay time expires.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The Fail-Safe Clock Monitor (FSCM) delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

# 7.3 Brown-out Reset (BOR)

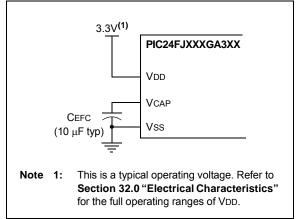

PIC24FJ128GA310 family devices implement a BOR circuit that provides the user with several configuration and power-saving options. The BOR is controlled by the BOREN (CW3<12>) Configuration bit.

When BOR is enabled, any drop of VDD below the BOR threshold results in a device BOR. Threshold levels are described in **Section 32.1** "**DC Characteristics**" (Parameter DC17).

## 7.4 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. Refer to **"Oscillator"** (DS39700) in the *"dsPIC33/PIC24 Family Reference Manual"* for further details.

#### TABLE 7-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant                 |

|------------|------------------------------------------|

| POR        | FNOSC<2:0> Configuration bits            |

| BOR        | (CW2<10:8>)                              |

| MCLR       |                                          |

| WDTO       | COSC2:0> Control bits<br>(OSCCON<14:12>) |

| SWR        | (00000114.122)                           |

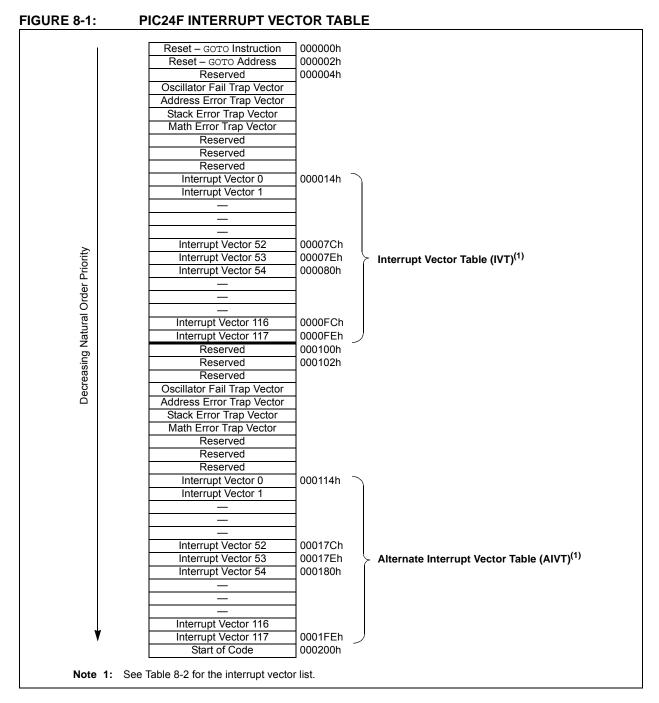

### TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

| U-0          | R/W-1                              | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|--------------|------------------------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|

| _            | IC5IP2                             | IC5IP1                               | IC5IP0           | _                 | IC4IP2           | IC4IP1          | IC4IP0  |  |  |  |

| oit 15       |                                    |                                      |                  |                   |                  |                 | bit 8   |  |  |  |

| U-0          | R/W-1                              | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|              | IC3IP2                             | IC3IP1                               | IC3IP0           |                   | DMA3IP2          | DMA3IP1         | DMA3IP0 |  |  |  |

| oit 7        |                                    |                                      |                  |                   |                  | 2               | bit C   |  |  |  |

| Legend:      |                                    |                                      |                  |                   |                  |                 |         |  |  |  |

| R = Readab   | le bit                             | W = Writable                         | bit              | U = Unimple       | mented bit, read | d as '0'        |         |  |  |  |

| -n = Value a | t POR                              | '1' = Bit is set                     |                  | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |  |  |

| bit 15       | Unimplemen                         | ted: Read as '                       | 0'               |                   |                  |                 |         |  |  |  |

| bit 14-12    | -                                  | Input Capture C                      |                  | rrupt Priority bi | ts               |                 |         |  |  |  |

|              | 111 = Interru                      | pt is Priority 7 (                   | highest priority | y interrupt)      |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | 001 = Interru                      |                                      |                  |                   |                  |                 |         |  |  |  |

|              | 000 = Interrupt source is disabled |                                      |                  |                   |                  |                 |         |  |  |  |

| bit 11       | -                                  | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |

| bit 10-8     |                                    | Input Capture C                      |                  |                   | ts               |                 |         |  |  |  |

|              | 111 = Interru                      | pt is Priority 7 (                   | highest priority | y interrupt)      |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | 001 = Interru                      | pt is Priority 1<br>pt source is dis | ablad            |                   |                  |                 |         |  |  |  |

| bit 7        |                                    | ited: Read as '                      |                  |                   |                  |                 |         |  |  |  |

| bit 6-4      | -                                  | Input Capture C                      |                  | rrupt Priority bi | te               |                 |         |  |  |  |

| DIL 0-4      |                                    | pt is Priority 7 (                   |                  |                   | 15               |                 |         |  |  |  |

|              | •                                  |                                      |                  | y meen apty       |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | •<br>001 = Interru                 | nt is Priority 1                     |                  |                   |                  |                 |         |  |  |  |

|              |                                    | pt source is dis                     | abled            |                   |                  |                 |         |  |  |  |

| bit 3        |                                    | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |

| bit 2-0      | DMA3IP<2:0                         | >: DMA Chann                         | el 3 Interrupt F | Priority bits     |                  |                 |         |  |  |  |

|              | 111 = Interru                      | pt is Priority 7 (                   | highest priority | y interrupt)      |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              |                                    |                                      |                  |                   |                  |                 |         |  |  |  |

|              | •                                  |                                      |                  |                   |                  |                 |         |  |  |  |

|              | •<br>001 = Interru                 | pt is Priority 1                     |                  |                   |                  |                 |         |  |  |  |

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "I/O Ports with Peripheral Pin Select (PPS)" (DS39711) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

All of the device pins (except VDD, VSS, MCLR and OSCI/CLKI) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger (ST) inputs for improved noise immunity.

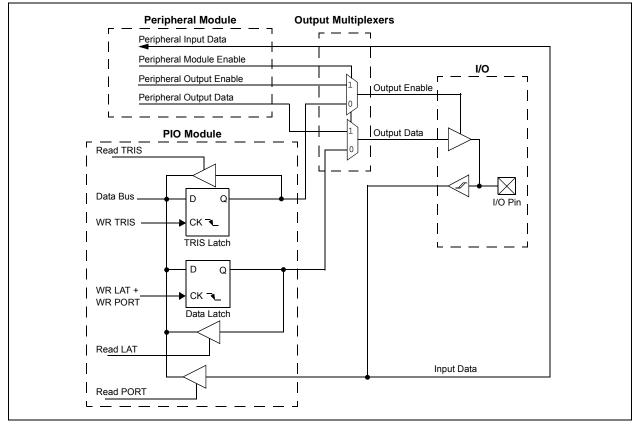

## 11.1 Parallel I/O (PIO) Ports

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/Os and one register associated with their operation as analog inputs. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch register (LATx), read the latch; writes to the latch, write the latch. Reads from the port (PORTx), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is regarded as a dedicated port because there is no other competing source of inputs. RC13 and RC14 can be input ports only; they cannot be configured as outputs.

### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

## 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits (see Register 11-1 through Register 11-6), which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

# 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. Refer to **Section 32.0 "Electrical Characteristics"** for more details.

## TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

## TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                         | Tolerated Input | Description                                                          |

|-------------------------------------|-----------------|----------------------------------------------------------------------|

| PORTA<15:14, 7:0> <sup>(1)</sup>    |                 |                                                                      |

| PORTB<15:7, 5:2>                    |                 |                                                                      |

| PORTC<3:1>(1)                       |                 |                                                                      |

| PORTD<15:8, 5:0>(1)                 | 5.5V            | Tolerates input levels above VDD; useful<br>for most standard logic. |

| PORTE<9:8, 4:0> <sup>(1)</sup>      |                 | ior most standard logic.                                             |

| PORTF<13:12, 8:0>(1)                |                 |                                                                      |

| PORTG<15:12, 9, 6:0> <sup>(1)</sup> |                 |                                                                      |

| PORTA<10:9> <sup>(1)</sup>          |                 |                                                                      |

| PORTB<6, 1:0>                       |                 |                                                                      |

| PORTC<15:12, 4> <sup>(1)</sup>      |                 |                                                                      |

| PORTD<7:6>                          | VDD             | Only VDD input levels are tolerated.                                 |

| PORTE<7:5>(1)                       |                 |                                                                      |

| PORTG<8:7>                          |                 |                                                                      |

**Note 1:** Not all of these pins are implemented on 64-pin or 80-pin devices. Refer to **Section 1.0 "Device Overview"** for a complete description of port pin implementation.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ128GA310 family devices support a larger number of remappable input only pins than remappable input/output pins. In this device family, there are up to 32 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31. Remappable input only pins are numbered above this range, from RPI32 to RPI43 (or the upper limit for that particular device).

See Table 1-4 for a summary of pinout options in each package offering.

## 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- $I^2C^{TM}$  (input and output)

- Change Notification inputs

- RTCC alarm output(s)

- EPMP signals (input and output)

- LCD signals

- · Analog inputs

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., OCx, UARTx transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs (e.g., USB on USB-enabled devices) will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin-selectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

### 11.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '111111' and all RPORx registers reset to '000000', all Peripheral Pin Select inputs are tied to Vss and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to  |

|-------|-------------------------------------------|

|       | RP63, RP63 need not exist on a device for |

|       | the registers to be reset to it.          |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing-critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in 'C', or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn/RPIn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use. Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation, and enabled as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration, or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a Peripheral Pin Select.

Example 11-3 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 11-3: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

|                                              | 1 011    |            |         |         |

|----------------------------------------------|----------|------------|---------|---------|

| // Unlock Regi                               | sters    |            |         |         |

| asm volatile(                                |          |            |         |         |

|                                              |          | #0x46,     | w2      |         |

|                                              | "MOV     | #0x57,     | w3      | \n"     |

|                                              | "MOV.b   | w2,        | [w1]    | \n"     |

|                                              | "MOV.b   | w3,        | [w1]    | \n"     |

|                                              | "BCLR (  | SCCON,#6") | ;       |         |

| // or use C30<br>//builtin_v                 |          |            | SN &    | 0xbf);  |

| // Configure I<br>// Assign T<br>RPINR18bit: | JIRX TO  | Pin RPO    | ble 11- | 2))     |

| // Assign W<br>RPINR18bit:                   |          |            |         |         |

| // Configure O<br>// Assign T<br>RPOR1bits.P | JITX To  | Pin RP2    | able 11 | I-4 )   |

| // Assign W<br>RPOR1bits.P                   |          |            |         |         |

| // Lock Regist                               | ers      |            |         |         |

| asm volatile                                 | ( "MOV   | #OSCCON,   | wl      | \n"     |

|                                              | "MOV     | #0x46,     | w2      | \n"     |

|                                              | "MOV     | #0x57,     | w3      | \n"     |

|                                              | "MOV.b   |            | [w1]    |         |

|                                              | "MOV.b   | w3,        | [w1]    | \n"     |

|                                              | "BSET    | OSCCON,    | #6"     | ;       |

| // or use C30                                | built-ir | macro:     |         |         |

| //builtin_w                                  |          |            | NTLO    | x 10) · |

| //DuiituiiW                                  | TTCE_OSC | CONT(OPCCO |         | A40//   |

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

|--------|-----------|-----|----------|----------|----------|----------|----------|

| ICTRIG | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |     |          |          |          |          | bit 0    |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC32: Cascade Two IC Modules Enable bit (32-bit operation)                                                                                                                                |

|          | <ul> <li>1 = ICx and ICy operate in cascade as a 32-bit module (this bit must be set in both modules)</li> <li>0 = ICx functions independently as a 16-bit module</li> </ul>              |

| bit 7    | ICTRIG: ICx Sync/Trigger Select bit                                                                                                                                                       |

|          | <ul> <li>1 = Trigger ICx from the source designated by the SYNCSELx bits</li> <li>0 = Synchronize ICx with the source designated by the SYNCSELx bits</li> </ul>                          |

| bit 6    | TRIGSTAT: Timer Trigger Status bit                                                                                                                                                        |

|          | <ul> <li>1 = Timer source has been triggered and is running (set in hardware, can be set in software)</li> <li>0 = Timer source has not been triggered and is being held clear</li> </ul> |

| bit 5    | Unimplemented: Read as '0'                                                                                                                                                                |

- Note 1: Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an IC module as its own trigger source, by selecting this mode.

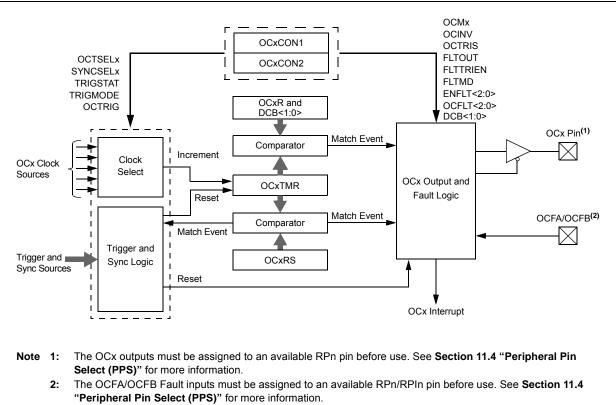

### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

## 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation (= 0xx).

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no sync/trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a trigger source event occurs.

| U-0                 | U-0                                   | U-0                                   | R/W-0                                 | R/W-0                                  | R/W-0                   | R/W-0              | R/W-0              |

|---------------------|---------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|-------------------------|--------------------|--------------------|

| _                   | _                                     | _                                     | DISSCK <sup>(1)</sup>                 | DISSDO <sup>(2)</sup>                  | MODE16                  | SMP                | CKE <sup>(3)</sup> |

| bit 15              |                                       |                                       |                                       |                                        |                         |                    | bit                |

| R/W-0               | R/W-0                                 | R/W-0                                 | R/W-0                                 | R/W-0                                  | R/W-0                   | R/W-0              | R/W-0              |

| SSEN <sup>(4)</sup> | -                                     | MSTEN                                 | SPRE2                                 | SPRE1                                  | SPRE0                   | PPRE1              | PPRE0              |

| bit 7               |                                       |                                       |                                       | -                                      |                         |                    | bit (              |

| Legend:             |                                       |                                       |                                       |                                        |                         |                    |                    |

| R = Reada           | ıble bit                              | W = Writable                          | bit                                   | U = Unimplem                           | ented bit, read         | as '0'             |                    |

| -n = Value          | at POR                                | '1' = Bit is set                      |                                       | '0' = Bit is clea                      | ared                    | x = Bit is unkn    | own                |

| bit 15-13           | Unimplomen                            | ted: Dood oo '                        | 0'                                    |                                        |                         |                    |                    |

| bit 12              | -                                     | ted: Read as '                        |                                       | modes only) <sup>(1)</sup>             |                         |                    |                    |

| DIL 12              | 1 = Internal S                        |                                       | abled; pin funct                      |                                        |                         |                    |                    |

| bit 11              |                                       | able SDOx Pin                         |                                       |                                        |                         |                    |                    |

|                     |                                       | n is not used by<br>n is controlled I |                                       | in functions as                        | I/O                     |                    |                    |

| bit 10              | -                                     |                                       | unication Sele                        | ct bit                                 |                         |                    |                    |

|                     | 1 = Commun                            | ication is word                       | -wide (16 bits)                       |                                        |                         |                    |                    |

| bit 9               | SMP: SPIx D                           | ata Input Samp                        | ble Phase bit                         |                                        |                         |                    |                    |

|                     |                                       | a is sampled a                        | t the end of dat<br>t the middle of ( | a output time<br>data output time      | 9                       |                    |                    |

|                     | Slave mode:                           |                                       | SPIx is used in                       | -                                      |                         |                    |                    |

| bit 8               | CKE: SPIx C                           | lock Edge Sele                        | ect bit <sup>(3)</sup>                |                                        |                         |                    |                    |

|                     |                                       |                                       |                                       | n from active cl<br>n from Idle cloc   |                         |                    |                    |

| bit 7               |                                       |                                       | (Slave mode) b                        | oit <sup>(4)</sup>                     |                         |                    |                    |

|                     |                                       | s used for Slav<br>s not used by t    |                                       | is controlled by                       | the port function       | on                 |                    |

| bit 6               | CKP: Clock F                          | Polarity Select I                     | bit                                   |                                        |                         |                    |                    |

|                     |                                       |                                       |                                       | ctive state is a<br>ctive state is a h |                         |                    |                    |

| bit 5               | MSTEN: Mas                            | ter Mode Enab                         | ole bit                               |                                        |                         |                    |                    |

|                     | 1 = Master m<br>0 = Slave mo          |                                       |                                       |                                        |                         |                    |                    |

|                     | If DISSCK = 0, S<br>Select (PPS)" for |                                       |                                       | available RPn                          | pin. See <b>Sectio</b>  | on 11.4 "Perip     | heral Pin          |

|                     | If DISSDO = 0, S<br>Select (PPS)" for |                                       |                                       | available RPn                          | pin. See <b>Secti</b>   | on 11.4 "Perip     | heral Pin          |

|                     | The CKE bit is no SPI modes (FRM      |                                       | ramed SPI mod                         | les. The user s                        | hould program           | this bit to '0' fo | r the Framed       |

|                     | If SSEN = 1, SSx<br>Select (PPS)" for |                                       |                                       | ilable RPn/PRI                         | n pin. See <b>Sec</b> t | tion 11.4 "Peri    | pheral Pin         |

## REGISTER 22-11: RTCCSWT: POWER CONTROL AND SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x       |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| PWCSAMP7(2) | PWCSAMP6(2) | PWCSAMP5(2) | PWCSAMP4(2) | PWCSAMP3(2) | PWCSAMP2(2) | PWCSAMP1(2) | PWCSAMP0(2) |

| bit 7       |             |             |             |             |             |             | bit 0       |

| Legend:           |                               |                                       |                    |

|-------------------|-------------------------------|---------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit,                | read as '0'        |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared                  | x = Bit is unknown |

|                   |                               | · · · · · · · · · · · · · · · · · · · |                    |

| bit 15-8 PWCST    | AB<7:0>: Power Control Stabil | ity Window Timer bits                 |                    |

|         | 11111111 = Stability Window is 255 TPWCCLK clock periods<br>11111110 = Stability Window is 254 TPWCCLK clock periods                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <br>00000001 = Stability Window is 1 TPWCCLK clock period<br>00000000 = No Stability Window; Sample Window starts when the alarm event triggers |

| bit 7-0 | PWCSAMP<7:0>: Power Control Sample Window Timer bits <sup>(2)</sup>                                                                             |

|         | 11111111 = Sample Window is always enabled, even when PWCEN = 0<br>11111110 = Sample Window is 254 TPWCCLK clock periods                        |

|         | <br>00000001 = Sample Window is 1 TPWCCLK clock period<br>00000000 = No Sample Window                                                           |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

2: The Sample Window always starts when the Stability Window timer expires, except when its initial value is 00h.

| R/W-0         | R/W-0                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                               | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|------------------|-----------------|--------|

| CH0NB2        | CH0NB1                                                                                                | CH0NB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CH0SB4                              | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |

| bit 15        | •                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     |                   |                  |                 | bit 8  |

|               |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     |                   |                  |                 |        |