Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

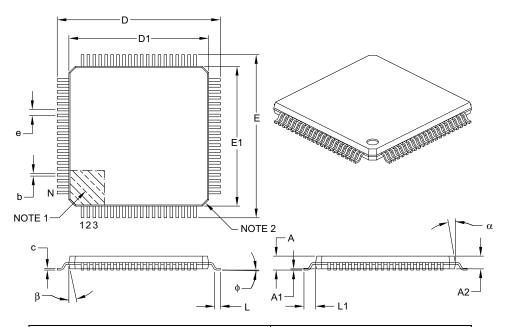

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga306-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0          | R/W-1              | R/W-0              | R/W-0             | U-0               | R/W-1            | R/W-0           | R/W-0   |

|--------------|--------------------|--------------------|-------------------|-------------------|------------------|-----------------|---------|

| —            | U2TXIP2            | U2TXIP1            | U2TXIP0           |                   | U2RXIP2          | U2RXIP1         | U2RXIP0 |

| bit 15       |                    |                    | I                 |                   |                  | L               | bit     |

|              |                    |                    |                   |                   |                  |                 |         |

| U-0          | R/W-1              | R/W-0              | R/W-0             | U-0               | R/W-1            | R/W-0           | R/W-0   |

| —            | INT2IP2            | INT2IP1            | INT2IP0           | —                 | T5IP2            | T5IP1           | T5IP0   |

| bit 7        |                    |                    |                   |                   |                  |                 | bit     |

|              |                    |                    |                   |                   |                  |                 |         |

| Legend:      | 1. 1.1             |                    | 1.10              |                   |                  |                 |         |

| R = Readab   |                    | W = Writable       |                   | -                 | nented bit, read |                 |         |

| -n = Value a | IT POR             | '1' = Bit is set   |                   | '0' = Bit is clea | ared             | x = Bit is unkr | iown    |

| bit 15       | Unimpleme          | nted: Read as '    | ı'                |                   |                  |                 |         |

| bit 14-12    | -                  | >: UART2 Trans     |                   | t Priority bite   |                  |                 |         |

| 511 14-12    |                    | pt is Priority 7 ( | •                 | •                 |                  |                 |         |

|              | •                  |                    | inglicer priority | interrupt)        |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              | •<br>001 – Intorru | pt is Priority 1   |                   |                   |                  |                 |         |

|              |                    | ipt source is dis  | abled             |                   |                  |                 |         |

| bit 11       |                    | nted: Read as '    |                   |                   |                  |                 |         |

| bit 10-8     | -                  | >: UART2 Rece      |                   | Priority bits     |                  |                 |         |

|              |                    | pt is Priority 7 ( | -                 | •                 |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              | 001 = Interru      | pt is Priority 1   |                   |                   |                  |                 |         |

|              | 000 = Interru      | pt source is dis   | abled             |                   |                  |                 |         |

| bit 7        | Unimplemer         | nted: Read as '    | כ'                |                   |                  |                 |         |

| bit 6-4      |                    | : External Interr  | • •               |                   |                  |                 |         |

|              | 111 = Interru      | pt is Priority 7 ( | highest priority  | interrupt)        |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              |                    | pt is Priority 1   |                   |                   |                  |                 |         |

|              |                    | pt source is dis   |                   |                   |                  |                 |         |

| bit 3        | -                  | nted: Read as '    |                   |                   |                  |                 |         |

| bit 2-0      |                    | Timer5 Interrupt   | -                 |                   |                  |                 |         |

|              | 111 = Interru      | pt is Priority 7(  | nignest priority  | interrupt)        |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              | •                  |                    |                   |                   |                  |                 |         |

|              |                    | pt is Priority 1   | ablad             |                   |                  |                 |         |

|              | uuu = merru        | pt source is dis   | auleu             |                   |                  |                 |         |

#### 10.6 Clock Frequency and Clock Switching

In Run and Idle modes, all PIC24FJ devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

#### 10.7 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.8 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers (XXXMD bits are in PMD1, PMD2, PMD3, PMD4, PMD6, PMD7 registers).

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as the PMD bits are used. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

#### 11.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ128GA310 family of devices implements a total of 35 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (20)

- Output Remappable Peripheral Registers (16)

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 11.4.4.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 11-7: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  |

|---------------|-------|------------------|--------|-----------------------------------------|--------|--------|--------|

| _             | —     | INT1R5           | INT1R4 | INT1R3                                  | INT1R2 | INT1R1 | INT1R0 |

| bit 15        |       |                  |        |                                         |        |        | bit 8  |

|               |       |                  |        |                                         |        |        |        |

| U-0           | U-0   | U-0              | U-0    | U-0                                     | U-0    | U-0    | U-0    |

| —             | —     | —                | —      | —                                       | —      | —      | —      |

| bit 7         |       |                  |        |                                         |        |        | bit 0  |

|               |       |                  |        |                                         |        |        |        |

| Legend:       |       |                  |        |                                         |        |        |        |

| R = Readable  | e bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        | nown   |        |

| bit 13-8 | INT1R<5:0>: Assign External Interrupt 1 (INT1) | to Corresponding RPn or RPIn Pin hits |

|----------|------------------------------------------------|---------------------------------------|

|          |                                                |                                       |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-8: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT3R5 | INT3R4 | INT3R3 | INT3R2 | INT3R1 | INT3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14Unimplemented: Read as '0'bit 13-8INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bitsbit 7-6Unimplemented: Read as '0'bit 5-0INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits

NOTES:

REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0      | U-0                            | R/W-0                                                               | R/W-1, HC                           | R/W-0                         | R/W-0                   | R/W-0            | R/W-0           |  |  |

|------------|--------------------------------|---------------------------------------------------------------------|-------------------------------------|-------------------------------|-------------------------|------------------|-----------------|--|--|

| I2CEN      | _                              | I2CSIDL                                                             | SCLREL                              | IPMIEN                        | A10M                    | DISSLW           | SMEN            |  |  |

| bit 15     | bit                            |                                                                     |                                     |                               |                         |                  |                 |  |  |

|            |                                |                                                                     |                                     |                               |                         |                  |                 |  |  |

| R/W-0      | R/W-0                          | R/W-0                                                               | R/W-0, HC                           | R/W-0, HC                     | R/W-0, HC               | R/W-0, HC        | R/W-0, HC       |  |  |

| GCEN       | STREN                          | ACKDT                                                               | ACKEN                               | RCEN                          | PEN                     | RSEN             | SEN             |  |  |

| bit 7      |                                |                                                                     |                                     |                               |                         |                  | bit C           |  |  |

| Legend:    |                                | HC - Hardwa                                                         | re Clearable bit                    |                               |                         |                  |                 |  |  |

| R = Reada  | ble bit                        | W = Writable                                                        |                                     |                               | ented bit, read         | as 'O'           |                 |  |  |

|            |                                |                                                                     | JIL                                 | -                             |                         |                  | 0.4/2           |  |  |

| -n = Value | atpor                          | '1' = Bit is set                                                    |                                     | '0' = Bit is clea             | ired                    | x = Bit is unkn  | own             |  |  |

| bit 15     | 12CEN: 12Cx E                  | Enable bit                                                          |                                     |                               |                         |                  |                 |  |  |

|            | 1 = Enables t                  | he I2Cx module                                                      | e and configure                     | s the SDAx and                | I SCLx pins as          | serial port pins |                 |  |  |

|            |                                |                                                                     | e; all l <sup>2</sup> C™ pins       |                               |                         |                  |                 |  |  |

| bit 14     | Unimplement                    | ted: Read as '0                                                     | ,                                   |                               |                         |                  |                 |  |  |

| bit 13     | I2CSIDL: I2C                   | x Stop in Idle M                                                    | ode bit                             |                               |                         |                  |                 |  |  |

|            |                                |                                                                     | eration when de<br>tion in Idle mod |                               | Idle mode               |                  |                 |  |  |

| bit 12     | SCLREL: SC                     | Lx Release Cor                                                      | ntrol bit (when o                   | perating as I <sup>2</sup> C  | slave)                  |                  |                 |  |  |

|            |                                | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch) |                                     |                               |                         |                  |                 |  |  |

|            | If STREN = 1:                  |                                                                     | write '0' to initi                  | ate stretch and               | write '1' to rele       | ase clock) Ha    | rdware is clear |  |  |

|            |                                |                                                                     | smission. Hard                      |                               |                         |                  |                 |  |  |

|            | If STREN = 0:                  |                                                                     |                                     |                               |                         |                  |                 |  |  |

|            | Bit is R/S (i.e. transmission. | , software may                                                      | only write '1' to                   | release clock)                | . Hardware is o         | clear at the beg | inning of slave |  |  |

| bit 11     | IPMIEN: Intell                 | igent Platform I                                                    | Management In                       | terface (IPMI) E              | Enable bit              |                  |                 |  |  |

|            | 1 = IPMI Sup<br>0 = IPMI mod   |                                                                     | abled; all addre                    | esses are Ackno               | owledged                |                  |                 |  |  |

| bit 10     | A10M: 10-Bit                   | Slave Addressi                                                      | ng bit                              |                               |                         |                  |                 |  |  |

|            | 1 = I2CxADD                    | is a 10-bit slav                                                    | e address                           |                               |                         |                  |                 |  |  |

|            | 0 = I2CxADD                    | is a 7-bit slave                                                    | address                             |                               |                         |                  |                 |  |  |

| bit 9      | DISSLW: Disa                   | able Slew Rate                                                      | Control bit                         |                               |                         |                  |                 |  |  |

|            |                                | control is disal                                                    |                                     |                               |                         |                  |                 |  |  |

| bit 8      | SMEN: SMBu                     | s Input Levels                                                      | oit                                 |                               |                         |                  |                 |  |  |

|            |                                | /O pin threshol<br>the SMBus inp                                    | ds compliant wi<br>ut thresholds    | th SMBus spec                 | ifications              |                  |                 |  |  |

| bit 7      | GCEN: Gener                    | al Call Enable                                                      | bit (when opera                     | ting as I <sup>2</sup> C slav | e)                      |                  |                 |  |  |

|            | 1 = Enables i<br>reception     | -                                                                   | a general call a                    | address is rece               | ived in the I2C         | xRSR (module     | is enabled for  |  |  |

|            |                                | all address is c                                                    | lisabled                            |                               |                         |                  |                 |  |  |

| bit 6      | STREN: SCL                     | k Clock Stretch                                                     | Enable bit (whe                     | en operating as               | I <sup>2</sup> C slave) |                  |                 |  |  |

|            |                                |                                                                     |                                     |                               |                         |                  |                 |  |  |

|            |                                | nction with the                                                     | SCLREL bit.<br>eive clock stretc    |                               |                         |                  |                 |  |  |

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC      | R-0, HSC                                                                                                                                                                        | U-0                             | U-0                            | U-0                                   | R/C-0, HS                    | R-0, HSC            | R-0, HSC            |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|---------------------------------------|------------------------------|---------------------|---------------------|--|--|--|--|

| ACKSTAT       | TRSTAT                                                                                                                                                                          |                                 |                                |                                       | BCL                          | GCSTAT              | ADD10               |  |  |  |  |

| bit 15        |                                                                                                                                                                                 |                                 |                                |                                       |                              |                     | bit 8               |  |  |  |  |

|               |                                                                                                                                                                                 |                                 |                                |                                       |                              |                     |                     |  |  |  |  |

| R/C-0, HS     | R/C-0, HS                                                                                                                                                                       | R-0, HSC                        | R/C-0, HSC                     | R/C-0, HSC                            | R-0, HSC                     | R-0, HSC            | R-0, HSC            |  |  |  |  |

| IWCOL         | I2COV                                                                                                                                                                           | D/Ā                             | Р                              | S                                     | R/W                          | RBF                 | TBF                 |  |  |  |  |

| bit 7         |                                                                                                                                                                                 |                                 |                                |                                       |                              |                     | bit 0               |  |  |  |  |

| Legend:       | Legend: C = Clearable bit HS = Hardware Settable bit                                                                                                                            |                                 |                                |                                       |                              |                     |                     |  |  |  |  |

| R = Readab    | ole bit                                                                                                                                                                         | W = Writabl                     |                                |                                       | nted bit, read as            | · 'O'               |                     |  |  |  |  |

| -n = Value a  |                                                                                                                                                                                 | '1' = Bit is s                  |                                | '0' = Bit is clear                    |                              | x = Bit is unkno    | wn                  |  |  |  |  |

|               | ware Settable                                                                                                                                                                   |                                 |                                |                                       |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 |                                |                                       |                              |                     |                     |  |  |  |  |

| bit 15        | ACKSTAT:                                                                                                                                                                        | Acknowledge                     | Status bit                     |                                       |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 | was detected                    |                                |                                       |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 | as detected la<br>set or cleare |                                | of Acknowledge.                       |                              |                     |                     |  |  |  |  |

| bit 14        |                                                                                                                                                                                 | ansmit Status                   |                                | , , , , , , , , , , , , , , , , , , , |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 |                                | icable to master                      | transmit operati             | on.)                |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 | progress (8 b                  | its + ACK)                            |                              |                     |                     |  |  |  |  |

|               | <ul> <li>0 = Master transmit is not in progress</li> <li>Hardware is set at the beginning of master transmission; hardware is clear at the end of slave Acknowledge.</li> </ul> |                                 |                                |                                       |                              |                     |                     |  |  |  |  |

| bit 13-11     |                                                                                                                                                                                 | ented: Read a                   | •                              |                                       |                              |                     | ie / loit ie wiedge |  |  |  |  |

| bit 10        | -                                                                                                                                                                               | er Bus Collisio                 |                                |                                       |                              |                     |                     |  |  |  |  |

|               | 1 = A bus c                                                                                                                                                                     | ollision has b                  | een detected                   | during a master                       | operation                    |                     |                     |  |  |  |  |

|               | 0 = No colli                                                                                                                                                                    |                                 | testion of a b                 |                                       |                              |                     |                     |  |  |  |  |

| bit 9         |                                                                                                                                                                                 | eneral Call S                   | etection of a bi               | us collision.                         |                              |                     |                     |  |  |  |  |

| DIL 9         |                                                                                                                                                                                 |                                 | s was received                 | 4                                     |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 | s was not rece                 |                                       |                              |                     |                     |  |  |  |  |

|               | Hardware is                                                                                                                                                                     | set when the                    | e address mate                 | ches the general                      | call address; ha             | rdware is clear a   | t Stop detection.   |  |  |  |  |

| bit 8         |                                                                                                                                                                                 | Bit Address S                   |                                |                                       |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 | ddress was r<br>ddress was r    |                                |                                       |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 |                                | te of the matched                     | 110-bit address; h           | nardware is clear a | at Stop detection.  |  |  |  |  |

| bit 7         |                                                                                                                                                                                 | ite Collision E                 | -                              |                                       |                              |                     | ·                   |  |  |  |  |

|               | 1 = An atter                                                                                                                                                                    | mpt to write t                  | o the I2CxTRI                  | N register failed                     | because the I <sup>2</sup> C | module is busy      |                     |  |  |  |  |

|               | 0 = No colli                                                                                                                                                                    |                                 | ourroppo of w                  | ite te IOOVTON                        | while husy (sloar            | ad by coffwore)     |                     |  |  |  |  |

| bit 6         |                                                                                                                                                                                 | eive Overflow                   |                                |                                       | while busy (clear            | ed by software).    |                     |  |  |  |  |

| bit 0         |                                                                                                                                                                                 |                                 | •                              | xRCV register is                      | still holding the            | previous byte       |                     |  |  |  |  |

|               | 0 = No over                                                                                                                                                                     | rflow                           |                                |                                       |                              |                     |                     |  |  |  |  |

| 6.4. <b>F</b> | _                                                                                                                                                                               |                                 | -                              |                                       | 2CxRCV (cleare               | d by software).     |                     |  |  |  |  |

| bit 5         |                                                                                                                                                                                 |                                 | then operating to byte receive | l as l <sup>2</sup> C slave)          |                              |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                 |                                 |                                | ed was data                           | address                      |                     |                     |  |  |  |  |

|               | Hardware is                                                                                                                                                                     | s clear at the                  | e device addr                  |                                       |                              | er a transmissio    | n finishes or by    |  |  |  |  |

|               | reception of                                                                                                                                                                    | a slave byte                    |                                |                                       |                              |                     |                     |  |  |  |  |

#### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "UART" (DS39708) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 15 bps to 1 Mbps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 18-1: UARTx SIMPLIFIED BLOCK DIAGRAM Baud Rate Generator IrDA® Hardware Flow Control UXRTS/BCLKx UARTx Receiver UARTx Receiver UARTx Transmitter VART Note: The UART inputs and outputs must all be assigned to available RPn/RPIn pins before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

REGISTER 19-3:

#### R/W-x R/W-x R/W-x R/W-x U-0 R/W-x R/W-x R/W-x CH0<sup>(1)</sup> CH3(1) CH2<sup>(1)</sup> CH1<sup>(1)</sup> CHODIS CHPOL CHSYNC bit 15 bit 8 R/W-0 R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x U-0 CI 3<sup>(1)</sup> CI 2<sup>(1)</sup> CL1<sup>(1)</sup> CI 0<sup>(1)</sup> CLODIS CLPOL CLSYNC bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 CHODIS: Modulator High Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CH<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 14 CHPOL: Modulator High Carrier Polarity Select bit 1 = Selected high carrier signal is inverted 0 = Selected high carrier signal is not inverted bit 13 CHSYNC: Modulator High Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the high carrier before allowing a switch to the low carrier 0 = Modulator output is not synchronized to the high time carrier signal<sup>(1)</sup> bit 12 Unimplemented: Read as '0' bit 11-8 CH<3:0> Modulator Data High Carrier Selection bits<sup>(1)</sup> 1111 = Reserved . . . 1011 1010 = Output Compare/PWM Module 7 output 1001 = Output Compare/PWM Module 6 output 1000 = Output Compare/PWM Module 5 output 0111 = Output Compare/PWM Module 4 output 0110 = Output Compare/PWM Module 3 output 0101 = Output Compare/PWM Module 2 output 0100 = Output Compare/PWM Module 1 output 0011 = Reference clock (REFO) output 0010 = Input on MDCIN2 pin 0001 = Input on MDCIN1 pin 0000 = Vss bit 7 CLODIS: Modulator Low Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CL<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 6 CLPOL: Modulator Low Carrier Polarity Select bit 1 = Selected low carrier signal is inverted 0 = Selected low carrier signal is not inverted bit 5 **CLSYNC:** Modulator Low Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the low carrier before allowing a switch to the high carrier 0 = Modulator output is not synchronized to the low time carrier signal<sup>(1)</sup>bit 4 Unimplemented: Read as '0' CL<3:0> Modulator Data Low Carrier Selection bits<sup>(1)</sup> bit 3-0 Bit settings are identical to those for CH<3:0>.

MDCAR: MODULATOR CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| R-0, HSC               | U-0                                                                                             | R/C-0, HS              | R/C-0, HS              | U-0                    | U-0                       | U-0                    | U-0                    |  |

|------------------------|-------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|---------------------------|------------------------|------------------------|--|

| BUSY                   | _                                                                                               | ERROR                  | TIMEOUT                |                        |                           |                        | _                      |  |

| bit 15                 |                                                                                                 |                        |                        |                        |                           |                        | bit 8                  |  |

|                        |                                                                                                 |                        |                        |                        |                           |                        |                        |  |

| R/W-0                  | R/W-0                                                                                           | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                     | R/W-0                  | R/W-0                  |  |

| RADDR23 <sup>(1)</sup> | RADDR22 <sup>(1)</sup>                                                                          | RADDR21 <sup>(1)</sup> | RADDR20 <sup>(1)</sup> | RADDR19 <sup>(1)</sup> | RADDR18 <sup>(1)</sup>    | RADDR17 <sup>(1)</sup> | RADDR16 <sup>(1)</sup> |  |

| bit 7                  |                                                                                                 |                        |                        |                        |                           |                        | bit 0                  |  |

|                        |                                                                                                 |                        |                        |                        |                           |                        |                        |  |

| Legend:                |                                                                                                 | HS = Hardward          | e Settable bit         | HSC = Hardwa           | are Settable/Cl           | earable bit            |                        |  |

| R = Readable           | bit                                                                                             | W = Writable I         | oit                    | U = Unimpleme          | ented, read as '          | 0'                     |                        |  |

| -n = Value at F        | POR                                                                                             | '1' = Bit is set       |                        | '0' = Bit is clea      | ared                      | x = Bit is unkn        | own                    |  |

| C = Clearable          | bit                                                                                             |                        |                        |                        |                           |                        |                        |  |

|                        |                                                                                                 |                        |                        |                        |                           |                        |                        |  |

| bit 15                 | BUSY: Busy b                                                                                    | oit (Master mod        | e only)                |                        |                           |                        |                        |  |

|                        | 1 = Port is bu                                                                                  | •                      |                        |                        |                           |                        |                        |  |

|                        | 0 = Port is no                                                                                  | ,                      |                        |                        |                           |                        |                        |  |

| bit 14                 | Unimplement                                                                                     | ted: Read as '0        | )'                     |                        |                           |                        |                        |  |

| bit 13                 | ERROR: Erro                                                                                     |                        |                        |                        |                           |                        |                        |  |

|                        |                                                                                                 | on error (illegal      |                        | as requested)          |                           |                        |                        |  |

| h:: 40                 |                                                                                                 | on completed s         | successfully           |                        |                           |                        |                        |  |

| bit 12                 | TIMEOUT: Tir                                                                                    |                        |                        |                        |                           |                        |                        |  |

|                        | <ul><li>1 = Transaction timed out</li><li>0 = Transaction completed successfully</li></ul>      |                        |                        |                        |                           |                        |                        |  |

| bit 11-8               |                                                                                                 |                        |                        |                        |                           |                        |                        |  |

| bit 7-0                | •                                                                                               |                        |                        | erved Address S        | Space bits <sup>(1)</sup> |                        |                        |  |

|                        | bit 7-0 RADDR<23:16>: Parallel Master Port Reserved Address Space bits <sup>(1)</sup>           |                        |                        |                        |                           |                        |                        |  |

| Note 1: If R           | Note 1: If RADDR<23:16> = 00000000, then the last EDS address for Chip Select 2 will be FFFFFh. |                        |                        |                        |                           |                        |                        |  |

#### REGISTER 20-2: PMCON2: EPMP CONTROL REGISTER 2

#### 22.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

#### 22.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 22-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 22-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |  |

|-------------|----------------------------|-------------|--|--|--|--|

| KIGPIK(I.0> | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |  |

| 11          | —                          | YEAR        |  |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 22-2).

By writing the ALRMVALH byte, the Alarm Pointer value, ALRMPTR<1:0> bits, decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 22-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |

| 11      | —                           | —            |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

#### 22.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL1<13>) must be set (see Example 22-1).

| Note: | To avoid accidental writes to the timer, it is<br>recommended that the RTCWREN bit<br>(RCFGCAL1<13>) is kept clear at any<br>other time. For the RTCWREN bit to be<br>set, there is only one instruction cycle time |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | window allowed between the 55h/AA sequence and the setting of RTCWREN; therefore, it is recommended that code follow the procedure in Example 22-1.                                                                 |

#### 22.2.3 SELECTING RTCC CLOCK SOURCE

The clock source for the RTCC module can be selected using the RTCLK<1:0> bits in the RTCPWC register. When the bits are set to '00', the Secondary Oscillator (SOSC) is used as the reference clock and when the bits are '01', LPRC is used as the reference clock. When RTCLK<1:0> = 10 and 11, the external power line (50 Hz and 60 Hz) is used as the clock source.

#### EXAMPLE 22-1: SETTING THE RTCWREN BIT

```

asm volatile("push w7");

asm volatile("push w8");

asm volatile("disi #5");

asm volatile("mov #0x55, w7");

asm volatile("mov w7, _NVMKEY");

asm volatile("mov #0xAA, w8");

asm volatile("mov w8, _NVMKEY");

asm volatile("bset _RCFGCAL1, #13"); //set the RTCWREN bit

asm volatile("pop w8");

asm volatile("pop w7");

```

#### 24.4 Control Registers

The 12-bit ADC is controlled through a total of 13 registers:

- AD1CON1 through AD1CON5 (Register 24-1 through Register 24-5)

- AD1CS (Register 24-6)

- AD1CHITH and AD1CHITL (Register 24-8 and Register 24-9)

- AD1CSSH and AD1CSSL (Register 24-10 and Register 24-11)

- AD1CTMENH and AD1CTMENL (Register 24-12 and Register 24-13)

- AD1DMBUF (not shown) The 16-bit conversion buffer for Extended Buffer mode

| DMABL<2:0> Buffer Size per<br>Channel (words) |     | Generated Offset<br>Address (lower 11 bits) | Available<br>Input<br>Channels | Allowable DMADST<br>Addresses |

|-----------------------------------------------|-----|---------------------------------------------|--------------------------------|-------------------------------|

| 000                                           | 1   | 000 00cc ccc0                               | 32                             | xxxx xxxx xx00 0000           |

| 001                                           | 2   | 000 0ccc ccn0                               | 32                             | xxxx xxxx x000 0000           |

| 010                                           | 4   | 000 cccc cnn0                               | 32                             | xxxx xxxx 0000 0000           |

| 011                                           | 8   | 00c cccc nnn0                               | 32                             | xxxx xxx0 0000 0000           |

| 100                                           | 16  | 0cc cccn nnn0                               | 32                             | xxxx xx00 0000 0000           |

| 101                                           | 32  | ccc ccnn nnn0                               | 32                             | xxxx x000 0000 0000           |

| 110                                           | 64  | ccc cnnn nnn0                               | 16                             | xxxx x000 0000 0000           |

| 111                                           | 128 | ccc nnnn nnn0                               | 8                              | xxxx x000 0000 0000           |

**Legend:** ccc = Channel number (three to five bits), n = Base buffer address (zero to seven bits),

x = User-definable range of DMADST for base address, 0 = Masked bits of DMADST for IA.

#### REGISTER 24-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

- bit 1 **SAMP:** ADC Sample Enable bit

- 1 = ADC Sample-and-Hold amplifiers are sampling

- 0 = ADC Sample-and-Hold amplifiers are holding

- bit 0 DONE: ADC Conversion Status bit

- 1 = ADC conversion cycle has completed

- 0 = ADC conversion has not started or is in progress

- Note 1: This bit is only available when extended DMA/buffer features are available (DMAEN = 1).

#### REGISTER 24-6: AD1CHS: ADC1 SAMPLE SELECT REGISTER (CONTINUED)

- bit 7-5 **CH0NA<2:0>:** Sample A Channel 0 Negative Input Select bits Same definitions as for CHONB<2:0>.

- bit 4-0 **CH0SA<4:0>:** Sample A Channel 0 Positive Input Select bits Same definitions as for CHOSB<4:0>.

- Note 1: These input channels do not have corresponding memory-mapped result buffers.

- 2: These channels are implemented in 100-pin devices only.

#### REGISTER 24-7: ANCFG: ADC BAND GAP REFERENCE CONFIGURATION REGISTER

| U-0      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|----------|-----|-----|-----|-----|-----|-----|-----|

| —        | —   | —   | —   | —   | —   | —   | _   |

| bit 15 b |     |     |     |     |     |     |     |

|          |     |     |     |     |     |     |     |

| U-0         | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0 |  |  |

|-------------|-----|-----|-----|-----|--------|--------|-------|--|--|

| —           | —   | —   | —   | —   | VBG6EN | VBG2EN | VBGEN |  |  |

| bit 7 bit 0 |     |     |     |     |        |        |       |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-3<br>bit 2 | <b>Unimplemented:</b> Read as '0'<br><b>VBG6EN:</b> ADC Input VBG/6 Enable bit<br>1 = Band gap voltage, divided by six reference (VBG/6), is enabled        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 0 = Band gap, divided by six reference (VBG/6), is disabled                                                                                                 |

| bit 1             | VBG2EN: ADC Input VBG/2 Enable bit                                                                                                                          |

|                   | <ul> <li>1 = Band gap voltage, divided by two reference (VBG/2), is enabled</li> <li>0 = Band gap, divided by two reference (VBG/2), is disabled</li> </ul> |

| bit 0             | VBGEN: ADC Input VBG Enable bit                                                                                                                             |

|                   | <ul> <li>1 = Band gap voltage reference (VBG) is enabled</li> <li>0 = Band gap reference (VBG) is disabled</li> </ul>                                       |

#### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic | Assembly Syntax PWRSAV #lit1 |                   | Description                                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|------------------------------|-------------------|--------------------------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               |                              |                   | Go into Sleep or Idle mode                             | 1             |                | WDTO, Sleep              |

| RCALL                | RCALL                        | Expr              | Relative Call                                          | 1             | 2              | None                     |

|                      | RCALL                        | Wn                | Computed Call                                          | 1             | 2              | None                     |

| REPEAT               | REPEAT                       | #lit14            | Repeat Next Instruction lit14 + 1 times                | 1             | 1              | None                     |

|                      | REPEAT                       | Wn                | Repeat Next Instruction (Wn) + 1 times                 | 1             | 1              | None                     |

| RESET                | RESET                        |                   | Software Device Reset                                  | 1             | 1              | None                     |

| RETFIE               | RETFIE                       |                   | Return from Interrupt                                  | 1             | 3 (2)          | None                     |

| RETLW                | RETLW                        | #lit10,Wn         | Return with Literal in Wn                              | 1             | 3 (2)          | None                     |

| RETURN               | RETURN                       |                   | Return from Subroutine                                 | 1             | 3 (2)          | None                     |

| RLC                  | RLC                          | f                 | f = Rotate Left through Carry f                        | 1             | 1              | C, N, Z                  |

|                      | RLC                          | f,WREG            | WREG = Rotate Left through Carry f                     | 1             | 1              | C, N, Z                  |

|                      | RLC                          | Ws,Wd             | Wd = Rotate Left through Carry Ws                      | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC                         | f                 | f = Rotate Left (No Carry) f                           | 1             | 1              | N, Z                     |

|                      | RLNC                         | f,WREG            | WREG = Rotate Left (No Carry) f                        | 1             | 1              | N, Z                     |

|                      | RLNC                         | Ws,Wd             | Wd = Rotate Left (No Carry) Ws                         | 1             | 1              | N, Z                     |

| RRC                  | RRC                          | f                 | f = Rotate Right through Carry f                       | 1             | 1              | C, N, Z                  |

|                      | RRC                          | f,WREG            | WREG = Rotate Right through Carry f                    | 1             | 1              | C, N, Z                  |

|                      | RRC                          | Ws,Wd             | Wd = Rotate Right through Carry Ws                     | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC                         | f                 | f = Rotate Right (No Carry) f                          | 1             | 1              | N, Z                     |

|                      | RRNC                         | f,WREG            | WREG = Rotate Right (No Carry) f                       | 1             | 1              | N, Z                     |

|                      | RRNC                         | Ws,Wd             | Wd = Rotate Right (No Carry) Ws                        | 1             | 1              | N, Z                     |

| SE                   | SE                           | Ws,Wnd            | Wnd = Sign-Extended Ws                                 | 1             | 1              | C, N, Z                  |

| SETM                 | SETM                         | f                 | f = FFFFh                                              | 1             | 1              | None                     |

|                      | SETM                         | WREG              | WREG = FFFFh                                           | 1             | 1              | None                     |

|                      | SETM                         | Ws                | Ws = FFFFh                                             | 1             | 1              | None                     |

| SL                   | SL                           | f                 | f = Left Shift f                                       | 1             | 1              | C, N, OV, Z              |

|                      | SL                           | f,WREG            | WREG = Left Shift f                                    | 1             | 1              | C, N, OV, Z              |

|                      | SL                           | Ws,Wd             | Wd = Left Shift Ws                                     | 1             | 1              | C, N, OV, Z              |

|                      | SL                           | Wb,Wns,Wnd        | Wnd = Left Shift Wb by Wns                             | 1             | 1              | N, Z                     |

|                      | SL                           | Wb,#lit5,Wnd      | Wnd = Left Shift Wb by lit5                            | 1             | 1              | N, Z                     |

| SUB                  | SUB                          | f                 | f = f – WREG                                           | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB                          | f,WREG            | WREG = f – WREG                                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB                          | #lit10,Wn         | Wn = Wn - lit10                                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB                          | Wb,Ws,Wd          | Wd = Wb – Ws                                           | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB                          | Wb,#lit5,Wd       | Wd = Wb – lit5                                         | 1             | 1              | C, DC, N, OV, 2          |

| SUBB                 | SUBB                         | f                 | $f = f - WREG - (\overline{C})$                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB                         | f,WREG            | WREG = $f - WREG - (\overline{C})$                     | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB                         | #lit10,Wn         | $Wn = Wn - lit10 - (\overline{C})$                     | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB                         | Wb,Ws,Wd          | $Wd = Wb - Ws - (\overline{C})$                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB                         | Wb,#lit5,Wd       | $Wd = Wb - lit5 - (\overline{C})$                      | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR                         | f                 | f = WREG – f                                           | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR                         | f,WREG            | WREG = WREG – f                                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR                         | Wb,Ws,Wd          | Wd = Ws – Wb                                           | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR                         | Wb,#lit5,Wd       | Wd = lit5 – Wb                                         | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR                        | f                 | $f = WREG - f - (\overline{C})$                        | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR                        | f,WREG            | WREG = WREG – f – $(\overline{C})$                     | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR                        |                   | $Wd = Ws - Wb - (\overline{C})$                        | 1             | 1              | C, DC, N, OV, Z          |

|                      |                              | Wb,Ws,Wd          | $Wd = WS - WD - (C)$ $Wd = lit5 - Wb - (\overline{C})$ | 1             | 1              |                          |

|                      | SUBBR                        | Wb,#lit5,Wd<br>Wn | Wd = Iit5 - Wb - (C)<br>Wn = Nibble Swap Wn            | 1             | 1              | C, DC, N, OV, Z<br>None  |

| SWAP                 | SWAP.b                       |                   |                                                        |               |                |                          |

NOTES:

#### 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FJ128GA310 family AC characteristics and timing parameters.

#### TABLE 32-17: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2V to 3.6V (unless otherwise stated)            |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial    |

|                    | Operating voltage VDD range as described in Section 32.1 "DC Characteristics". |

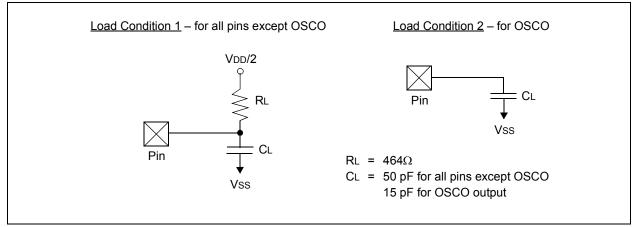

#### FIGURE 32-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 32-18: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosco  | OSCO/CLKO Pin         | _   | —                  | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | _   | —                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —                  | 400 | pF    | In l <sup>2</sup> C™ mode                                          |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.