Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

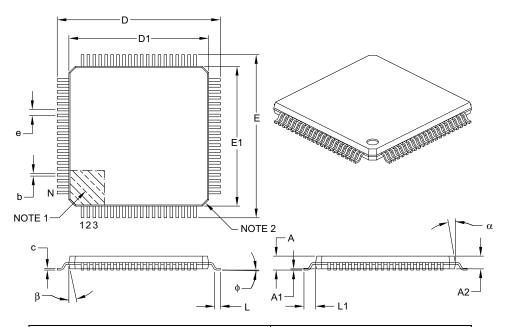

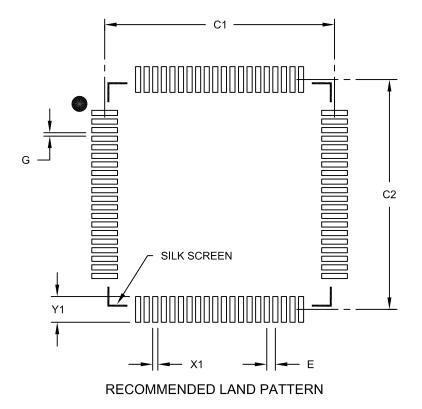

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga308t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TADLE 1-4: |                |                |                 |                |     |        |                    |  |  |

|------------|----------------|----------------|-----------------|----------------|-----|--------|--------------------|--|--|

| Pin        | Pi             | n Number/      | Grid Loca       | ter            |     | Input  |                    |  |  |

| Function   | 64-Pin<br>TQFP | 80-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O | Buffer | Description        |  |  |

| RB0        | 16             | 20             | 25              | K2             | I/O | ST     | PORTB Digital I/O. |  |  |

| RB1        | 15             | 19             | 24              | K1             | I/O | ST     |                    |  |  |

| RB2        | 14             | 18             | 23              | J2             | I/O | ST     |                    |  |  |

| RB3        | 13             | 17             | 22              | J1             | I/O | ST     |                    |  |  |

| RB4        | 12             | 16             | 21              | H2             | I/O | ST     |                    |  |  |

| RB5        | 11             | 15             | 20              | H1             | I/O | ST     |                    |  |  |

| RB6        | 17             | 21             | 26              | L1             | I/O | ST     |                    |  |  |

| RB7        | 18             | 22             | 27              | J3             | I/O | ST     |                    |  |  |

| RB8        | 21             | 27             | 32              | K4             | I/O | ST     |                    |  |  |

| RB9        | 22             | 28             | 33              | L4             | I/O | ST     |                    |  |  |

| RB10       | 23             | 29             | 34              | L5             | I/O | ST     |                    |  |  |

| RB11       | 24             | 30             | 35              | J5             | I/O | ST     |                    |  |  |

| RB12       | 27             | 33             | 41              | J7             | I/O | ST     |                    |  |  |

| RB13       | 28             | 34             | 42              | L7             | I/O | ST     |                    |  |  |

| RB14       | 29             | 35             | 43              | K7             | I/O | ST     |                    |  |  |

| RB15       | 30             | 36             | 44              | L8             | I/O | ST     |                    |  |  |

| RC1        | _              | 4              | 6               | D1             | I/O | ST     | PORTC Digital I/O. |  |  |

| RC2        | _              | _              | 7               | E4             | I/O | ST     |                    |  |  |

| RC3        | _              | 5              | 8               | E2             | I/O | ST     |                    |  |  |

| RC4        | _              | _              | 9               | E1             | I/O | ST     |                    |  |  |

| RC12       | 39             | 49             | 63              | F9             | I/O | ST     |                    |  |  |

| RC13       | 47             | 59             | 73              | C10            | I   | ST     |                    |  |  |

| RC14       | 48             | 60             | 74              | B11            | I   | ST     |                    |  |  |

| RC15       | 40             | 50             | 64              | F11            | I/O | ST     |                    |  |  |

| RD0        | 46             | 58             | 72              | D9             | I/O | ST     | PORTD Digital I/O. |  |  |

| RD1        | 49             | 61             | 76              | A11            | I/O | ST     |                    |  |  |

| RD2        | 50             | 62             | 77              | A10            | I/O | ST     |                    |  |  |

| RD3        | 51             | 63             | 78              | B9             | I/O | ST     | ]                  |  |  |

| RD4        | 52             | 66             | 81              | C8             | I/O | ST     | ]                  |  |  |

| RD5        | 53             | 67             | 82              | B8             | I/O | ST     |                    |  |  |

| RD6        | 54             | 68             | 83              | D7             | I/O | ST     | ]                  |  |  |

| RD7        | 55             | 69             | 84              | C7             | I/O | ST     | ]                  |  |  |

| RD8        | 42             | 54             | 68              | E9             | I/O | ST     | ]                  |  |  |

| RD9        | 43             | 55             | 69              | E10            | I/O | ST     |                    |  |  |

| RD10       | 44             | 56             | 70              | D11            | I/O | ST     | ]                  |  |  |

| RD11       | 45             | 57             | 71              | C11            | I/O | ST     | ]                  |  |  |

| RD12       | _              | 64             | 79              | A9             | I/O | ST     |                    |  |  |

| RD13       |                | 65             | 80              | D8             | I/O | ST     | ]                  |  |  |

| RD14       |                | 37             | 47              | L9             | I/O | ST     | ]                  |  |  |

| RD15       |                | 38             | 48              | K9             | I/O | ST     | ]                  |  |  |

#### PIC24FJ128GA310 FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

TTL = TTL input buffer Legend: ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

NOTES:

| U-0           | R/W-0                                                   | R/W-0                                                                                                                        | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |

|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|--------|--|--|--|

|               | DMA1IF                                                  | AD1IF                                                                                                                        | U1TXIF          | U1RXIF            | SPI1IF          | SPF1IF          | T3IF   |  |  |  |

| bit 15        |                                                         |                                                                                                                              |                 |                   |                 |                 | bit 8  |  |  |  |

| R/W-0         | R/W-0                                                   | R/W-0                                                                                                                        | R/W-0           | R/W-0             | R/W-0,          | R/W-0           | R/W-0  |  |  |  |

| T2IF          | OC2IF                                                   | IC2IF                                                                                                                        | DMA0IF          | T1IF              | OC1IF           | IC1IF           | INTOIF |  |  |  |

| bit 7         |                                                         |                                                                                                                              |                 |                   |                 |                 | bit 0  |  |  |  |

| Legend:       |                                                         |                                                                                                                              |                 |                   |                 |                 |        |  |  |  |

| R = Readabl   | e bit                                                   | W = Writable                                                                                                                 | bit             | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |

| -n = Value at | POR                                                     | '1' = Bit is set                                                                                                             |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |  |  |  |

| bit 15        | Unimplemen                                              | ted: Read as '                                                                                                               | )'              |                   |                 |                 |        |  |  |  |

| bit 14        | -                                                       | A Channel 1 In                                                                                                               |                 | atus bit          |                 |                 |        |  |  |  |

|               |                                                         | request has oc                                                                                                               |                 |                   |                 |                 |        |  |  |  |

|               | 0 = Interrupt                                           | request has no                                                                                                               | t occurred      |                   |                 |                 |        |  |  |  |

| bit 13        |                                                         |                                                                                                                              | •               | upt Flag Status   | bit             |                 |        |  |  |  |

|               |                                                         | request has oc                                                                                                               |                 |                   |                 |                 |        |  |  |  |

| bit 12        | -                                                       | request has no<br>RT1 Transmitter                                                                                            |                 | Status hit        |                 |                 |        |  |  |  |

|               |                                                         | request has oc                                                                                                               | 1 0             | Olatus bit        |                 |                 |        |  |  |  |

|               |                                                         | request has no                                                                                                               |                 |                   |                 |                 |        |  |  |  |

| bit 11        | <b>U1RXIF:</b> UART1 Receiver Interrupt Flag Status bit |                                                                                                                              |                 |                   |                 |                 |        |  |  |  |

|               |                                                         | request has oc<br>request has no                                                                                             |                 |                   |                 |                 |        |  |  |  |

| bit 10        | SPI1IF: SPI1                                            | Event Interrup                                                                                                               | Flag Status b   | it                |                 |                 |        |  |  |  |

|               |                                                         | request has oc<br>request has no                                                                                             |                 |                   |                 |                 |        |  |  |  |

| bit 9         | SPF1IF: SPI1                                            | I Fault Interrup                                                                                                             | Flag Status b   | it                |                 |                 |        |  |  |  |

|               |                                                         | request has oc<br>request has no                                                                                             |                 |                   |                 |                 |        |  |  |  |

| bit 8         | T3IF: Timer3                                            | Interrupt Flag                                                                                                               | Status bit      |                   |                 |                 |        |  |  |  |

|               | •                                                       | request has occ<br>request has not                                                                                           |                 |                   |                 |                 |        |  |  |  |

| bit 7         | T2IF: Timer2                                            | Interrupt Flag                                                                                                               | Status bit      |                   |                 |                 |        |  |  |  |

|               | •                                                       | request has oc<br>request has no                                                                                             |                 |                   |                 |                 |        |  |  |  |

| bit 6         | -                                                       | -                                                                                                                            |                 | ipt Flag Status I | oit             |                 |        |  |  |  |

|               | 1 = Interrupt                                           | request has occ                                                                                                              | curred          |                   |                 |                 |        |  |  |  |

| bit 5         | IC2IF: Input C                                          | <ul> <li>0 = Interrupt request has not occurred</li> <li>IC2IF: Input Capture Channel 2 Interrupt Flag Status bit</li> </ul> |                 |                   |                 |                 |        |  |  |  |

|               |                                                         | request has oc<br>request has no                                                                                             |                 |                   |                 |                 |        |  |  |  |

| bit 4         | DMA0IF: DM                                              | A Channel 0 In                                                                                                               | terrupt Flag St | atus bit          |                 |                 |        |  |  |  |

|               | 1 = Interrupt                                           | request has oc                                                                                                               | curred          |                   |                 |                 |        |  |  |  |

|               | -                                                       | request has no                                                                                                               |                 |                   |                 |                 |        |  |  |  |

| bit 3         | 1 = Interrupt                                           | Interrupt Flag<br>request has oc<br>request has no                                                                           | curred          |                   |                 |                 |        |  |  |  |

### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

### REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0         | U-0                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                | R/W-0             | R/W-0          | R/W-0             | R/W-0        |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------------------|--------------|--|--|--|--|

| ROEN          | 0-0                                                                                                                                                               | ROSSLP                                                                                                                                                                                                                                                                               | ROSEL                                                                                                                                                                                                | RODIV3            | RODIV2         | RODIV1            | RODIV0       |  |  |  |  |

| bit 15        |                                                                                                                                                                   | RUSSLF                                                                                                                                                                                                                                                                               | RUJEL                                                                                                                                                                                                | RODIV3            | RODIVZ         | RODIVI            | bit          |  |  |  |  |

|               |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                |                   |              |  |  |  |  |

| U-0           | U-0                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                  | U-0               | U-0            | U-0               | U-0          |  |  |  |  |

| <u> </u>      | —                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                    | —                 | —              | —                 | —            |  |  |  |  |

| bit 7         |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                |                   | bit          |  |  |  |  |

| Legend:       |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                |                   |              |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                             | W = Writable b                                                                                                                                                                                                                                                                       | bit                                                                                                                                                                                                  | U = Unimplem      | ented bit, rea | d as '0'          |              |  |  |  |  |

| -n = Value at | POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | '0' = Bit is clea | ared           | x = Bit is unkn   | iown         |  |  |  |  |

| bit 15        |                                                                                                                                                                   | ence Oscillator                                                                                                                                                                                                                                                                      | Output Enable                                                                                                                                                                                        | a hit             |                |                   |              |  |  |  |  |

|               | 1 = Reference                                                                                                                                                     | e oscillator is en<br>e oscillator is dis                                                                                                                                                                                                                                            | abled on the l                                                                                                                                                                                       |                   |                |                   |              |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                                                        | ted: Read as '0                                                                                                                                                                                                                                                                      | ,                                                                                                                                                                                                    |                   |                |                   |              |  |  |  |  |

| bit 13        | ROSSLP: Re                                                                                                                                                        | ference Oscillat                                                                                                                                                                                                                                                                     | or Output Sto                                                                                                                                                                                        | p in Sleep bit    |                |                   |              |  |  |  |  |

|               | <b>ROSSLP:</b> Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep                                                |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                |                   |              |  |  |  |  |

|               | 0 = Reference                                                                                                                                                     | e oscillator is dis                                                                                                                                                                                                                                                                  | sabled in Slee                                                                                                                                                                                       | р                 |                |                   |              |  |  |  |  |

| bit 12        |                                                                                                                                                                   | erence Oscillato                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |                   |                |                   |              |  |  |  |  |

|               |                                                                                                                                                                   | oscillator is used                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                      |                   |                |                   | enabled usin |  |  |  |  |

|               |                                                                                                                                                                   | C<2:0> bits; the<br>clock is used as                                                                                                                                                                                                                                                 |                                                                                                                                                                                                      |                   |                |                   | he device    |  |  |  |  |

| bit 11-8      | •                                                                                                                                                                 |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                | in switching of t |              |  |  |  |  |

|               |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                      | RODIV<3:0>: Reference Oscillator Divisor Select bits                                                                                                                                                 |                   |                |                   |              |  |  |  |  |

|               | 1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 16,384                                                                            |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                   |                |                   |              |  |  |  |  |

|               | 1110 = Base                                                                                                                                                       |                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                                                    | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base                                                                                                                                                       | clock value divi<br>clock value divi                                                                                                                                                                                                                                                 | ded by 16,384<br>ded by 8,192                                                                                                                                                                        | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base                                                                                                                                        | clock value divi<br>clock value divi<br>clock value divi                                                                                                                                                                                                                             | ded by 16,384<br>ded by 8,192<br>ded by 4,096                                                                                                                                                        | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base                                                                                                                         | clock value divi<br>clock value divi<br>clock value divi<br>clock value divi                                                                                                                                                                                                         | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048                                                                                                                                        | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base                                                                                                          | clock value divi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi                                                                                                                                                                                     | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024                                                                                                                        | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base                                                                                           | clock value divi<br>clock value divi<br>clock value divi<br>clock value divi                                                                                                                                                                                                         | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512                                                                                                          | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base                                                             | clock value divi<br>clock value divi                                                                                                                         | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 256<br>ded by 128                                                                              | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base                                                             | clock value divi<br>clock value divi                                                                                                     | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64                                                                 | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base                                              | clock value divi<br>clock value divi                                                                                 | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32                                      | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base                               | clock value divi<br>clock value divi                                                             | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16                         | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base                | clock value divi<br>clock value divi                                         | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8             | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0011 = Base | clock value divi<br>clock value divi                                                             | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 3                 |                |                   |              |  |  |  |  |

|               | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0011 = Base | clock value divi<br>clock value divi | ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 3                 |                |                   |              |  |  |  |  |

### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ128GA310 family devices support a larger number of remappable input only pins than remappable input/output pins. In this device family, there are up to 32 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31. Remappable input only pins are numbered above this range, from RPI32 to RPI43 (or the upper limit for that particular device).

See Table 1-4 for a summary of pinout options in each package offering.

### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- $I^2C^{TM}$  (input and output)

- Change Notification inputs

- RTCC alarm output(s)

- EPMP signals (input and output)

- LCD signals

- · Analog inputs

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., OCx, UARTx transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs (e.g., USB on USB-enabled devices) will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin-selectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

### 11.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-7 through Register 11-26). Each register contains two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field, with an appropriate 6-bit value, maps the RPn/RPIn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

| TABLE 11-3 | SELECTABLE INPUT SOURCES | (MAPS INPUT TO FUNCTION) <sup>(1)</sup> |

|------------|--------------------------|-----------------------------------------|

|            |                          |                                         |

| Input Name              | Function Name | Register | Function Mapping<br>Bits |

|-------------------------|---------------|----------|--------------------------|

| DSM Modulation Input    | MDMIN         | RPINR30  | MDMIR<5:0>               |

| DSM Carrier 1 Input     | MDCIN1        | RPINR31  | MDC1R<5:0>               |

| DSM Carrier 2 Input     | MDCIN2        | RPINR31  | MDC2R<5:0>               |

| External Interrupt 1    | INT1          | RPINR0   | INT1R<5:0>               |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<5:0>               |

| External Interrupt 3    | INT3          | RPINR1   | INT3R<5:0>               |

| External Interrupt 4    | INT4          | RPINR2   | INT4R<5:0>               |

| Input Capture 1         | IC1           | RPINR7   | IC1R<5:0>                |

| Input Capture 2         | IC2           | RPINR7   | IC2R<5:0>                |

| Input Capture 3         | IC3           | RPINR8   | IC3R<5:0>                |

| Input Capture 4         | IC4           | RPINR8   | IC4R<5:0>                |

| Input Capture 5         | IC5           | RPINR9   | IC5R<5:0>                |

| Input Capture 6         | IC6           | RPINR9   | IC6R<5:0>                |

| Input Capture 7         | IC7           | RPINR10  | IC7R<5:0>                |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<5:0>               |

| Output Compare Fault B  | OCFB          | RPINR11  | OCFBR<5:0>               |

| SPI1 Clock Input        | SCK1IN        | RPINR20  | SCK1R<5:0>               |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<5:0>               |

| SPI1 Slave Select Input | SS1IN         | RPINR21  | SS1R<5:0>                |

| SPI2 Clock Input        | SCK2IN        | RPINR22  | SCK2R<5:0>               |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<5:0>               |

| SPI2 Slave Select Input | SS2IN         | RPINR23  | SS2R<5:0>                |

| Timer1 External Clock   | T1CK          | RPINR23  | T1CKR<5:0>               |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<5:0>               |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<5:0>               |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<5:0>               |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<5:0>               |

| UART1 Clear-to-Send     | U1CTS         | RPINR18  | U1CTSR<5:0>              |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<5:0>               |

| UART2 Clear-to-Send     | U2CTS         | RPINR19  | U2CTSR<5:0>              |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<5:0>               |

| UART3 Clear-to-Send     | U3CTS         | RPINR21  | U3CTSR<5:0>              |

| UART3 Receive           | U3RX          | RPINR17  | U3RXR<5:0>               |

| UART4 Clear-to-Send     | U4CTS         | RPINR27  | U4CTSR<5:0>              |

| UART4 Receive           | U4RX          | RPINR27  | U4RXR<5:0>               |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

NOTES:

### REGISTER 16-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 1 | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Transmit has not yet started, SPIxTXB is full</li> <li>0 = Transmit has started, SPIxTXB is empty</li> </ul>                                                                                                                    |

|       | In Standard Buffer mode:<br>Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the SPIxTXB.<br>Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.                 |

|       | In Enhanced Buffer mode:<br>Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available<br>buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write. |

| bit 0 | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                  |

|       | <ul> <li>1 = Receive is complete, SPIxRXB is full</li> <li>0 = Receive is not complete, SPIxRXB is empty</li> </ul>                                                                                                                          |

|       | In Standard Buffer mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.                                      |

|       | In Enhanced Buffer mode:                                                                                                                                                                                                                     |

|       | Automatically set in hardware when SPIx transfers data from the SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.             |

**Note 1:** If SPIEN = 1, these functions must be assigned to available RPn/RPIn pins before use. See **Section 11.4** "**Peripheral Pin Select (PPS)**" for more information.

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- .

- .

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: If DISSCK = 0, SCKx must be configured to an available RPn pin. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- 2: If DISSDO = 0, SDOx must be configured to an available RPn pin. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- **3:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 4: If SSEN = 1, SSx must be configured to an available RPn/PRIn pin. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### 17.2 Setting Baud Rate When Operating as a Bus Master

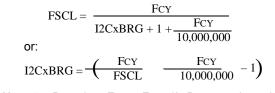

To compute the Baud Rate Generator reload value, use Equation 17-1.

### EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1,2)</sup>

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

### 17.3 Slave Address Masking

The I2CxMSK register (Register 17-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '0000000' and '0100000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Demained Overlage Fact | Fair   | I2CxB     | RG Value      |             |

|------------------------|--------|-----------|---------------|-------------|

| Required System Fsc∟   | FCY    | (Decimal) | (Hexadecimal) | Actual FscL |

| 100 kHz                | 16 MHz | 157       | 9D            | 100 kHz     |

| 100 kHz                | 8 MHz  | 78        | 4E            | 100 kHz     |

| 100 kHz                | 4 MHz  | 39        | 27            | 99 kHz      |

| 400 kHz                | 16 MHz | 37        | 25            | 404 kHz     |

| 400 kHz                | 8 MHz  | 18        | 12            | 404 kHz     |

| 400 kHz                | 4 MHz  | 9         | 9             | 385 kHz     |

| 400 kHz                | 2 MHz  | 4         | 4             | 385 kHz     |

| 1 MHz                  | 16 MHz | 13        | D             | 1.026 MHz   |

| 1 MHz                  | 8 MHz  | 6         | 6             | 1.026 MHz   |

| 1 MHz                  | 4 MHz  | 3         | 3             | 0.909 MHz   |

### **TABLE 17-1:** I2C<sup>™</sup> CLOCK RATES<sup>(1,2)</sup>

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

...

| TABLE 17-2: | I <sup>2</sup> C <sup>™</sup> RESERVED ADDRESSES <sup>(1)</sup> |  |

|-------------|-----------------------------------------------------------------|--|

|             |                                                                 |  |

| Slave Address | R/W Bit | Description                            |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|

| 000 000       | 0       | General Call Address <sup>(2)</sup>    |  |  |  |

| 0000 0000     | 1       | Start Byte                             |  |  |  |

| 0000 001      | x       | CBus Address                           |  |  |  |

| 0000 01x      | x       | Reserved                               |  |  |  |

| 0000 1xx      | x       | HS Mode Master Code                    |  |  |  |

| 1111 0xx      | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |

| 1111 1xx      | х       | Reserved                               |  |  |  |

Note 1: The address bits listed here will never cause an address match, independent of address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware is set or clear when Start, Repeated Start or Stop is detected.</li> </ul>                                          |

| bit 3 | S: Start bit                                                                                                                                                                                                                                    |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware is set or clear when Start, Repeated Start or Stop is detected.</li> </ul>                    |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                              |

|       | 1 = Read: Indicates the data transfer is output from the slave<br>0 = Write: Indicates the data transfer is input to the slave<br>Hardware is set or clear after the reception of an $I^2C$ device address byte.                                |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                             |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> <li>Hardware is set when I2CxRCV is written with the received byte; hardware is clear when the software reads I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                            |

|       | <ul> <li>1 = Transmit is in progress, I2CxTRN is full</li> <li>0 = Transmit is complete, I2CxTRN is empty</li> </ul>                                                                                                                            |

### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK  | <9:8> |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | AMSK  | <7:0> |       |       |       |

| bit 7  |       |       |       |       |       |       | bit 0 |

Hardware is set when software writes to I2CxTRN; hardware is clear at the completion of data transmission.

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

|----------|----------|----------|----------|----------|----------|---------|---------|

| SE(n+15) | SE(n+14) | SE(n+13) | SE(n+12) | SE(n+11) | SE(n+10) | SE(n+9) | SE(n+8) |

| bit 15   | •        | •        |          |          |          |         | bit 8   |

|          |          |          |          |          |          |         |         |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

| SE(n+7)  | SE(n+6)  | SE(n+5)  | SE(n+4)  | SE(n+3)  | SE(n+2)  | SE(n+1) | SE(n)   |

| bit 7    | •        | •        | •        | •        |          |         | bit 0   |

| <u></u>  |          |          |          |          |          |         |         |

### REGISTER 21-4: LCDSEx: LCD SEGMENT x ENABLE REGISTER

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0 SE(n + 15):SE(n): Segment Enable bits

For LCDSE0: n = 0For LCDSE1: n = 16For LCDSE2: n = 32For LCDSE3:  $n = 48^{(1)}$

$\ensuremath{\mathtt{1}}$  = Segment function of the pin is enabled, digital I/O is disabled

0 = Segment function of the pin is disabled, digital I/O is enabled

Note 1: For the SEG49 to work correctly, the JTAG needs to be disabled.

### REGISTER 21-5: LCDDATAX: LCD DATA x REGISTER

| R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0    | R/W-0    |

|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| S(n+15)Cy | S(n+14)Cy | S(n+13)Cy | S(n+12)Cy | S(n+11)Cy | S(n+10)Cy | S(n+9)Cy | S(n+8)Cy |

| bit 15    |           |           |           |           |           |          | bit 8    |

| R/W-0    | R/W-0  |

|----------|----------|----------|----------|----------|----------|----------|--------|

| S(n+7)Cy | S(n+6)Cy | S(n+5)Cy | S(n+4)Cy | S(n+3)Cy | S(n+2)Cy | S(n+1)Cy | S(n)Cy |

| bit 7    |          |          |          |          |          |          | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-0 S(n + 15)Cy:S(n)Cy: Pixel On bits

| <u>For registers, LCDDATA0 through LCDDATA3: n = (16x), y = 0</u>        |

|--------------------------------------------------------------------------|

| For registers, LCDDATA4 through LCDDATA7: $n = (16(x - 4))$ , $y = 1$    |

| For registers, LCDDATA8 through LCDDATA11: n = (16(x – 8)), y = 2        |

| For registers, LCDDATA12 through LCDDATA15: $n = (16(x - 12))$ , $y = 3$ |

| For registers, LCDDATA16 through LCDDATA19: $n = (16(x - 16)), y = 4$    |

| For registers, LCDDATA20 through LCDDATA23: $n = (16(x - 20)), y = 5$    |

| For registers, LCDDATA24 through LCDDATA27: $n = (16(x - 24))$ , $y = 6$ |

| For registers, LCDDATA28 through LCDDATA31: $n = (16(x - 28)), y = 7$    |

| 1 = Pixel is on                                                          |

| 0 = Pixel is off                                                         |

### REGISTER 24-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

- bit 1 **BUFM:** Buffer Fill Mode Select bit<sup>(1)</sup>

- 1 = ADC buffer is two, 13-word buffers, starting at ADC1BUF0 and ADC1BUF12, and sequential conversions fill the buffers alternately (Split mode)

- 0 = ADC buffer is a single, 26-word buffer and fills sequentially from ADC1BUF0 (FIFO mode)

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

- 0 = Always uses channel input selects for Sample A

- **Note 1:** These bits are only applicable when the buffer is used in FIFO mode (BUFREGEN = 0). In addition, BUFS is only used when BUFM = 1.

### REGISTER 24-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0  | R-0    | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | PUMPEN | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |        |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCS7 | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                                                                |                      |                    |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | adable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15   | ADRC: ADC Conversion Clock Source bit<br>1 = RC Clock                                                      |

|----------|------------------------------------------------------------------------------------------------------------|

|          | 0 = Clock derived from system clock                                                                        |

| bit 14   | EXTSAM: Extended Sampling Time bit                                                                         |

|          | <ul><li>1 = ADC is still sampling after SAMP = 0</li><li>0 = ADC is finished sampling</li></ul>            |

| bit 13   | PUMPEN: Charge Pump Enable bit                                                                             |

|          | <ul><li>1 = Charge pump for switches is enabled</li><li>0 = Charge pump for switches is disabled</li></ul> |

| bit 12-8 | SAMC<4:0>: Auto-Sample Time Select bits                                                                    |

|          | 11111 = <b>31 T</b> AD                                                                                     |

|          | •••                                                                                                        |

|          | 00001 = 1 TAD<br>00000 = 0 TAD                                                                             |

|          |                                                                                                            |

| bit 7-0  | ADCS<7:0>: ADC Conversion Clock Select bits                                                                |

|          | 11111111<br>- Decented                                                                                     |

|          | ••• = Reserved                                                                                             |

|          | $001111111 = 64 \cdot TCY = TAD$                                                                           |

|          | •••                                                                                                        |

|          | $0000001 = 2 \cdot \text{TCY} = \text{TAD}$                                                                |

|          | 00000000 = TCY = TAD                                                                                       |

|          |                                                                                                            |

| R/W-0        | R/W-0                   | R/W-0                                  | R/W-0           | U-0                 | U-0               | R/W-0             | R/W-0           |

|--------------|-------------------------|----------------------------------------|-----------------|---------------------|-------------------|-------------------|-----------------|

| ASEN         | LPEN                    | CTMREQ                                 | BGREQ           |                     | —                 | ASINT1            | ASINT0          |

| bit 15       |                         |                                        |                 |                     |                   |                   | bit 8           |

|              |                         |                                        |                 |                     |                   | <b>D</b> 111 A    |                 |

| U-0          | U-0                     | U-0                                    | U-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0           |

|              | —                       | —                                      | _               | WM1                 | WM0               | CM1               | CM0             |

| bit 7        |                         |                                        |                 |                     |                   |                   | bit C           |

| Legend:      |                         |                                        |                 |                     |                   |                   |                 |

| R = Readab   | le bit                  | W = Writable                           | oit             | U = Unimplem        | nented bit, rea   | d as '0'          |                 |

| -n = Value a | It POR                  | '1' = Bit is set                       |                 | '0' = Bit is clea   | ared              | x = Bit is unkr   | nown            |

|              |                         |                                        |                 |                     |                   |                   |                 |

| bit 15       | ASEN: Auto-S            | Scan Enable bi                         | t               |                     |                   |                   |                 |

|              | 1 = Auto-sca            |                                        |                 |                     |                   |                   |                 |

| L:1 4 4      | 0 = Auto-sca            |                                        |                 |                     |                   |                   |                 |

| bit 14       |                         | ower Enable bi<br>er is enabled at     |                 |                     |                   |                   |                 |

|              |                         | er is enabled af                       |                 |                     |                   |                   |                 |

| bit 13       |                         | rMU Request b                          |                 |                     |                   |                   |                 |

|              | 1 = CTMU is             | enabled when                           | the ADC is ena  | abled and active    | e                 |                   |                 |

|              |                         | not enabled by                         |                 |                     |                   |                   |                 |