Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

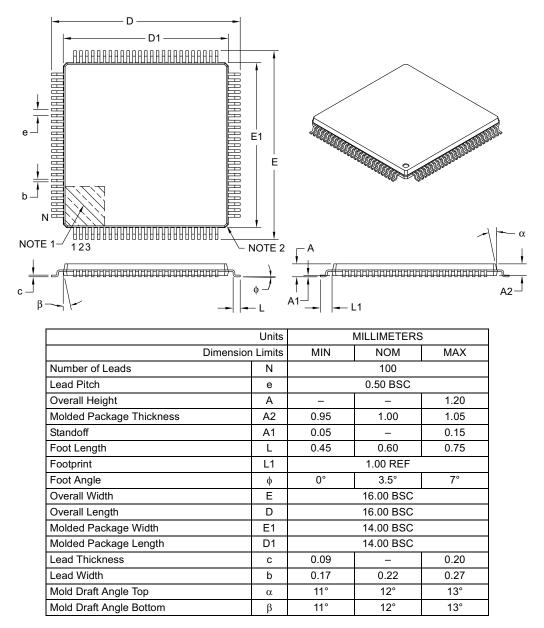

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga310-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <u>г т</u> | -4: PIC24FJ126GA310 FAMIL f |                |                 |                |     |                 |                    |

|------------|-----------------------------|----------------|-----------------|----------------|-----|-----------------|--------------------|

| Pin        | Pi                          | n Number/      | Grid Loca       | ter            |     | Innut           |                    |

| Function   | 64-Pin<br>TQFP              | 80-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O | Input<br>Buffer | Description        |

| RB0        | 16                          | 20             | 25              | K2             | I/O | ST              | PORTB Digital I/O. |

| RB1        | 15                          | 19             | 24              | K1             | I/O | ST              |                    |

| RB2        | 14                          | 18             | 23              | J2             | I/O | ST              |                    |

| RB3        | 13                          | 17             | 22              | J1             | I/O | ST              |                    |

| RB4        | 12                          | 16             | 21              | H2             | I/O | ST              |                    |

| RB5        | 11                          | 15             | 20              | H1             | I/O | ST              |                    |

| RB6        | 17                          | 21             | 26              | L1             | I/O | ST              |                    |

| RB7        | 18                          | 22             | 27              | J3             | I/O | ST              |                    |

| RB8        | 21                          | 27             | 32              | K4             | I/O | ST              |                    |

| RB9        | 22                          | 28             | 33              | L4             | I/O | ST              |                    |

| RB10       | 23                          | 29             | 34              | L5             | I/O | ST              |                    |

| RB11       | 24                          | 30             | 35              | J5             | I/O | ST              |                    |

| RB12       | 27                          | 33             | 41              | J7             | I/O | ST              |                    |

| RB13       | 28                          | 34             | 42              | L7             | I/O | ST              |                    |

| RB14       | 29                          | 35             | 43              | K7             | I/O | ST              |                    |

| RB15       | 30                          | 36             | 44              | L8             | I/O | ST              |                    |

| RC1        | _                           | 4              | 6               | D1             | I/O | ST              | PORTC Digital I/O. |

| RC2        | _                           | _              | 7               | E4             | I/O | ST              |                    |

| RC3        | _                           | 5              | 8               | E2             | I/O | ST              |                    |

| RC4        | _                           | _              | 9               | E1             | I/O | ST              |                    |

| RC12       | 39                          | 49             | 63              | F9             | I/O | ST              |                    |

| RC13       | 47                          | 59             | 73              | C10            | I   | ST              |                    |

| RC14       | 48                          | 60             | 74              | B11            | I   | ST              |                    |

| RC15       | 40                          | 50             | 64              | F11            | I/O | ST              |                    |

| RD0        | 46                          | 58             | 72              | D9             | I/O | ST              | PORTD Digital I/O. |

| RD1        | 49                          | 61             | 76              | A11            | I/O | ST              |                    |

| RD2        | 50                          | 62             | 77              | A10            | I/O | ST              |                    |

| RD3        | 51                          | 63             | 78              | B9             | I/O | ST              | ]                  |

| RD4        | 52                          | 66             | 81              | C8             | I/O | ST              | ]                  |

| RD5        | 53                          | 67             | 82              | B8             | I/O | ST              |                    |

| RD6        | 54                          | 68             | 83              | D7             | I/O | ST              | ]                  |

| RD7        | 55                          | 69             | 84              | C7             | I/O | ST              | ]                  |

| RD8        | 42                          | 54             | 68              | E9             | I/O | ST              | ]                  |

| RD9        | 43                          | 55             | 69              | E10            | I/O | ST              |                    |

| RD10       | 44                          | 56             | 70              | D11            | I/O | ST              | ]                  |

| RD11       | 45                          | 57             | 71              | C11            | I/O | ST              | ]                  |

| RD12       | _                           | 64             | 79              | A9             | I/O | ST              |                    |

| RD13       |                             | 65             | 80              | D8             | I/O | ST              | ]                  |

| RD14       |                             | 37             | 47              | L9             | I/O | ST              | ]                  |

| RD15       |                             | 38             | 48              | K9             | I/O | ST              | ]                  |

#### PIC24FJ128GA310 FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

TTL = TTL input buffer Legend: ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

#### TABLE 4-11: SPI REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                               | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8       | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------------------------------------|---------|--------|--------|---------|---------|-------------|-----------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT  | 0240 | SPIEN  | _                                    | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0     | SRMPT     | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1  | 0242 |        | _                                    | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE         | SSEN      | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2  | 0244 | FRMEN  | SPIFSD                               | SPIFPOL | _      | —      | —       | _       | _           | _         | _      | _      |        | -      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF   | 0248 |        |                                      |         |        |        |         | SPI1    | Transmit an | d Receive | Buffer |        |        |        |        |        |        | 0000          |

| SPI2STAT  | 0260 | SPIEN  | _                                    | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0     | SRMPT     | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1  | 0262 |        | _                                    | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE         | SSEN      | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2  | 0264 | FRMEN  | SPIFSD                               | SPIFPOL | —      | —      | —       | —       | _           | _         | _      | _      | _      | _      | —      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF   | 0268 |        | SPI2 Transmit and Receive Buffer 000 |         |        |        |         |         |             | 0000      |        |        |        |        |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: PORTA REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8            | Bit 7 <sup>(2)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4 <sup>(2)</sup> | Bit 3 <sup>(2)</sup> | Bit2 <sup>(2)</sup> | Bit 1 <sup>(2)</sup> | Bit 0 <sup>(2)</sup> | All<br>Resets |

|--------------|------|--------|---------|--------|--------|--------|--------|--------|------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|----------------------|----------------------|---------------|

| TRISA        | 02C0 | TRISA  | <15:14> | _      | _      | —      | TRISA  | <10:9> | _                |                      |                      |                      | TRISA                | <7:0>                |                     |                      |                      | C6FF          |

| PORTA        | 02C2 | RA<1   | 5:14>   |        | _      | _      | RA<1   | 10:9>  | P                |                      |                      | xxxx                 |                      |                      |                     |                      |                      |               |

| LATA         | 02C4 | LATA<  | 15:14>  |        | _      | _      | LATA<  | <10:9> | 0:9> — LATA<7:0> |                      |                      | xxxx                 |                      |                      |                     |                      |                      |               |

| ODCA         | 02C6 | ODA<   | 15:14>  | _      | _      | _      | ODA<   | :10:9> | —                |                      |                      |                      | ODA                  | <7:0>                |                     |                      |                      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: PORTA and all associated bits are unimplemented in 64-pin devices and read as '0'.

2: These bits are also unimplemented in 80-pin devices, read as '0'.

#### TABLE 4-13: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|----------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8 |        | TRISB<15:0> FI |        |        |        |        |       |       |       |       | FFFF  |       |       |       |       |       |               |

| PORTB        | 02CA |        |                |        |        |        |        |       | RB<   | 15:0> |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC |        | LATB<15:0> x   |        |        |        |        |       |       |       | xxxx  |       |       |       |       |       |       |               |

| ODCB         | 02CE |        | ODB<15:0> 0    |        |        |        |        |       |       |       | 0000  |       |       |       |       |       |       |               |

Legend: Reset values are shown in hexadecimal.

DS30009996G-page 53

| U-0          | U-0                                    | R/W-0                                                                                      | U-0            | U-0               | U-0             | U-0             | R/W-0  |  |  |  |

|--------------|----------------------------------------|--------------------------------------------------------------------------------------------|----------------|-------------------|-----------------|-----------------|--------|--|--|--|

|              |                                        | CTMUIF                                                                                     | _              |                   |                 |                 | HLVDIF |  |  |  |

| bit 15       |                                        |                                                                                            |                |                   |                 |                 | bit 8  |  |  |  |

|              |                                        |                                                                                            |                |                   |                 |                 |        |  |  |  |

| U-0          | U-0                                    | U-0                                                                                        | U-0            | R/W-0             | R/W-0           | R/W-0           | U-0    |  |  |  |

|              | —                                      | —                                                                                          |                | CRCIF             | U2ERIF          | U1ERIF          |        |  |  |  |

| bit 7        |                                        |                                                                                            |                |                   |                 |                 | bit (  |  |  |  |

| Legend:      |                                        |                                                                                            |                |                   |                 |                 |        |  |  |  |

| R = Readab   | ole bit                                | W = Writable                                                                               | oit            | U = Unimplem      | nented bit, rea | d as '0'        |        |  |  |  |

| -n = Value a | t POR                                  | '1' = Bit is set                                                                           |                | '0' = Bit is clea | ared            | x = Bit is unkn | own    |  |  |  |

|              |                                        |                                                                                            |                |                   |                 |                 |        |  |  |  |

| bit 15-14    | Unimpleme                              | nted: Read as 'o                                                                           | )'             |                   |                 |                 |        |  |  |  |

| bit 13       | CTMUIF: CT                             | CTMUIF: CTMU Interrupt Flag Status bit                                                     |                |                   |                 |                 |        |  |  |  |

|              |                                        | t request has oc                                                                           |                |                   |                 |                 |        |  |  |  |

|              | •                                      | t request has no                                                                           |                |                   |                 |                 |        |  |  |  |

| bit 12-9     | •                                      | nted: Read as '                                                                            |                |                   |                 |                 |        |  |  |  |

| bit 8        | -                                      | h/Low-Voltage E                                                                            | -              | t Flag Status bi  | l .             |                 |        |  |  |  |

|              |                                        | t request has oc<br>t request has no                                                       |                |                   |                 |                 |        |  |  |  |

| bit 7-4      |                                        | nted: Read as '(                                                                           |                |                   |                 |                 |        |  |  |  |

| bit 3        | -                                      | Generator Inte                                                                             |                | us bit            |                 |                 |        |  |  |  |

|              |                                        | t request has oc                                                                           |                |                   |                 |                 |        |  |  |  |

|              | 0 = Interrupt                          | t request has no                                                                           | t occurred     |                   |                 |                 |        |  |  |  |

| bit 2        | U2ERIF: UA                             | RT2 Error Interr                                                                           | upt Flag Statu | s bit             |                 |                 |        |  |  |  |

|              |                                        | t request has oc                                                                           |                |                   |                 |                 |        |  |  |  |

|              | 0 = Interrupt request has not occurred |                                                                                            |                |                   |                 |                 |        |  |  |  |

| bit 1        |                                        | <b>U1ERIF:</b> UART1 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                |                   |                 |                 |        |  |  |  |

|              |                                        | t request has oc<br>t request has no                                                       |                |                   |                 |                 |        |  |  |  |

| bit 0        |                                        | nted: Read as '(                                                                           |                |                   |                 |                 |        |  |  |  |

|              | ommpleme                               | neu. Neau as (                                                                             | )              |                   |                 |                 |        |  |  |  |

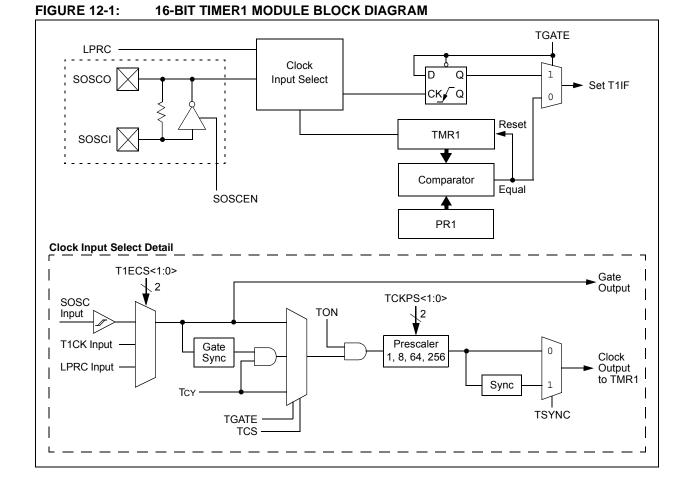

#### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Timers" (DS39704) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS, TECS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

#### 14.1.2 CASCADED (32-BIT) MODE

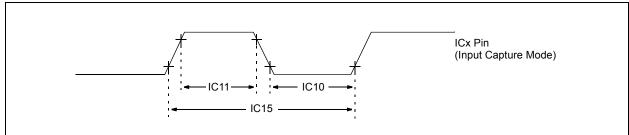

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs and the even module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

### 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every  $4^{th}$  or  $16^{th}$ ). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- 3. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired sync/trigger source.

- 5. Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source.

- 6. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '000000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG, and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8>) and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bits settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to set the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- **Note:** For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired Capture mode.

The module is ready to capture events when the time base and the sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

REGISTER 19-3:

#### R/W-x R/W-x R/W-x R/W-x U-0 R/W-x R/W-x R/W-x CH0<sup>(1)</sup> CH3(1) CH2<sup>(1)</sup> CH1<sup>(1)</sup> CHODIS CHPOL CHSYNC bit 15 bit 8 R/W-0 R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x U-0 CI 3<sup>(1)</sup> CI 2<sup>(1)</sup> CL1<sup>(1)</sup> CI 0<sup>(1)</sup> CLODIS CLPOL CLSYNC bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 CHODIS: Modulator High Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CH<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 14 CHPOL: Modulator High Carrier Polarity Select bit 1 = Selected high carrier signal is inverted 0 = Selected high carrier signal is not inverted bit 13 CHSYNC: Modulator High Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the high carrier before allowing a switch to the low carrier 0 = Modulator output is not synchronized to the high time carrier signal<sup>(1)</sup> bit 12 Unimplemented: Read as '0' bit 11-8 CH<3:0> Modulator Data High Carrier Selection bits<sup>(1)</sup> 1111 = Reserved . . . 1011 1010 = Output Compare/PWM Module 7 output 1001 = Output Compare/PWM Module 6 output 1000 = Output Compare/PWM Module 5 output 0111 = Output Compare/PWM Module 4 output 0110 = Output Compare/PWM Module 3 output 0101 = Output Compare/PWM Module 2 output 0100 = Output Compare/PWM Module 1 output 0011 = Reference clock (REFO) output 0010 = Input on MDCIN2 pin 0001 = Input on MDCIN1 pin 0000 = Vss bit 7 CLODIS: Modulator Low Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by CL<3:0>) is disabled 0 = Output signal driving the peripheral output pin is enabled bit 6 CLPOL: Modulator Low Carrier Polarity Select bit 1 = Selected low carrier signal is inverted 0 = Selected low carrier signal is not inverted bit 5 **CLSYNC:** Modulator Low Carrier Synchronization Enable bit 1 = Modulator waits for a falling edge on the low carrier before allowing a switch to the high carrier 0 = Modulator output is not synchronized to the low time carrier signal<sup>(1)</sup>bit 4 Unimplemented: Read as '0' CL<3:0> Modulator Data Low Carrier Selection bits<sup>(1)</sup> bit 3-0 Bit settings are identical to those for CH<3:0>.

MDCAR: MODULATOR CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### **REGISTER 21-3:** LCDPS: LCD PHASE REGISTER

| U-0          | U-0                                    | U-0                                         | U-0          | U-0               | U-0             | U-0             | U-0   |

|--------------|----------------------------------------|---------------------------------------------|--------------|-------------------|-----------------|-----------------|-------|

| —            | _                                      |                                             | _            | _                 |                 | _               | —     |

| oit 15       | ·                                      |                                             |              |                   |                 |                 | bit   |

| R/W-0        | R/W-0                                  | R-0                                         | R-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| WFT          | BIASMD                                 | LCDA                                        | WA           | LP3               | LP2             | LP1             | LP0   |

| bit 7        |                                        | LOBIN                                       |              | 210               |                 |                 | bit   |

|              |                                        |                                             |              |                   |                 |                 |       |

| Legend:      |                                        |                                             |              |                   |                 |                 |       |

| R = Readab   | le bit                                 | W = Writable b                              | oit          | U = Unimplem      | ented bit, read | d as '0'        |       |

| -n = Value a | t POR                                  | '1' = Bit is set                            |              | '0' = Bit is clea | ared            | x = Bit is unkn | iown  |

| bit 15-8     | Unimplemen                             | ted: Read as '0                             | )'           |                   |                 |                 |       |

| bit 7        | -                                      | rm Type Select                              |              |                   |                 |                 |       |

|              | 1 = Type-B w                           | vaveform (phase                             | e changes or | n each frame bou  |                 |                 |       |

|              | • •                                    |                                             | -            | ithin each commo  | on type)        |                 |       |

| bit 6        |                                        | s Mode Select I                             |              |                   |                 |                 |       |

|              |                                        | < <u>2:0&gt; = 000 or</u><br>s mode (do not |              |                   |                 |                 |       |

|              |                                        | <2:0> = 001 or                              | <u>010:</u>  |                   |                 |                 |       |

|              | 1 = 1/2 Bias mode<br>0 = 1/3 Bias mode |                                             |              |                   |                 |                 |       |

| bit 5        | LCDA: LCD A                            | Active Status bit                           |              |                   |                 |                 |       |

|              |                                        | er module is act<br>er module is ina        | -            |                   |                 |                 |       |

| bit 4        | WA: LCD Wri                            | te Allow Status                             | bit          |                   |                 |                 |       |

|              |                                        | to the LCDDAT/<br>to the LCDDAT/            |              |                   |                 |                 |       |

| bit 3-0      |                                        | D Prescaler Sel                             | -            |                   |                 |                 |       |

|              | 1111 <b>= 1:16</b>                     |                                             |              |                   |                 |                 |       |

|              | 1110 = 1:15                            |                                             |              |                   |                 |                 |       |

|              | 1101 = 1:14<br>1100 = 1:13             |                                             |              |                   |                 |                 |       |

|              | 1011 <b>= 1:12</b>                     |                                             |              |                   |                 |                 |       |

|              | 1010 <b>= 1:11</b>                     |                                             |              |                   |                 |                 |       |

|              | 1001 = 1:10                            |                                             |              |                   |                 |                 |       |

|              | 1000 = 1:9                             |                                             |              |                   |                 |                 |       |

|              | 0111 = 1:8<br>0110 = 1:7               |                                             |              |                   |                 |                 |       |

|              | 0101 = 1:6                             |                                             |              |                   |                 |                 |       |

|              | 0100 <b>= 1</b> :5                     |                                             |              |                   |                 |                 |       |

|              | 0011 = 1:4                             |                                             |              |                   |                 |                 |       |

|              | 0010 <b>= 1:3</b>                      |                                             |              |                   |                 |                 |       |

|              | 0001 = 1:2                             |                                             |              |                   |                 |                 |       |

#### REGISTER 22-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

| _      | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| —     | — | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

|-------|---|--------|--------|--------|--------|--------|--------|

| bit 7 |   |        |        |        |        |        | bit 0  |

|       |   |        |        |        |        |        |        |

|       |   |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           | Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 22-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

|       | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

#### REGISTER 24-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

- bit 1 **BUFM:** Buffer Fill Mode Select bit<sup>(1)</sup>

- 1 = ADC buffer is two, 13-word buffers, starting at ADC1BUF0 and ADC1BUF12, and sequential conversions fill the buffers alternately (Split mode)

- 0 = ADC buffer is a single, 26-word buffer and fills sequentially from ADC1BUF0 (FIFO mode)

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

- 0 = Always uses channel input selects for Sample A

- **Note 1:** These bits are only applicable when the buffer is used in FIFO mode (BUFREGEN = 0). In addition, BUFS is only used when BUFM = 1.

#### REGISTER 24-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0  | R-0    | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | PUMPEN | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |        |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCS7 | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 15   | ADRC: ADC Conversion Clock Source bit<br>1 = RC Clock                                                      |

|----------|------------------------------------------------------------------------------------------------------------|

|          | 0 = Clock derived from system clock                                                                        |

| bit 14   | EXTSAM: Extended Sampling Time bit                                                                         |

|          | <ul><li>1 = ADC is still sampling after SAMP = 0</li><li>0 = ADC is finished sampling</li></ul>            |

| bit 13   | PUMPEN: Charge Pump Enable bit                                                                             |

|          | <ul><li>1 = Charge pump for switches is enabled</li><li>0 = Charge pump for switches is disabled</li></ul> |

| bit 12-8 | SAMC<4:0>: Auto-Sample Time Select bits                                                                    |

|          | 11111 = <b>31 T</b> AD                                                                                     |

|          | •••                                                                                                        |

|          | 00001 = 1 TAD<br>00000 = 0 TAD                                                                             |

|          |                                                                                                            |

| bit 7-0  | ADCS<7:0>: ADC Conversion Clock Select bits                                                                |

|          | 11111111<br>- Decented                                                                                     |

|          | ••• = Reserved                                                                                             |

|          | $001111111 = 64 \cdot TCY = TAD$                                                                           |

|          | •••                                                                                                        |

|          | $0000001 = 2 \cdot \text{TCY} = \text{TAD}$                                                                |

|          | 00000000 = TCY = TAD                                                                                       |

|          |                                                                                                            |

| R/W-0        | R/W-0         | R/W-0                                                                | R/W-0           | U-0                 | U-0               | R/W-0             | R/W-0          |

|--------------|---------------|----------------------------------------------------------------------|-----------------|---------------------|-------------------|-------------------|----------------|

| ASEN         | LPEN          | CTMREQ                                                               | BGREQ           |                     | —                 | ASINT1            | ASINT0         |

| bit 15       |               |                                                                      |                 |                     |                   |                   | bit            |

| U-0          | U-0           | U-0                                                                  | U-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0          |

|              | _             | _                                                                    | —               | WM1                 | WM0               | CM1               | CM0            |

| bit 7        |               |                                                                      |                 |                     |                   |                   | bit            |

| Legend:      |               |                                                                      |                 |                     |                   |                   |                |

| R = Readab   | le bit        | W = Writable I                                                       | oit             | U = Unimplem        | nented bit, read  | d as '0'          |                |

| -n = Value a | t POR         | '1' = Bit is set                                                     |                 | '0' = Bit is clea   | ared              | x = Bit is unkr   | nown           |

| bit 15       | ASEN: Auto-   | -Scan Enable bit                                                     | I               |                     |                   |                   |                |

|              |               | an is enabled<br>an is disabled                                      |                 |                     |                   |                   |                |

| bit 14       | LPEN: Low-I   | Power Enable bi                                                      | t               |                     |                   |                   |                |

|              |               | ver is enabled af                                                    |                 |                     |                   |                   |                |

| bit 13       | CTMREQ: C     | TMU Request b                                                        | it              |                     |                   |                   |                |

|              |               | s enabled when<br>s not enabled by                                   |                 | abled and active    | е                 |                   |                |

| bit 12       | BGREQ: Ba     | nd Gap Request                                                       | bit             |                     |                   |                   |                |

|              |               | p is enabled wh<br>p is not enabled                                  |                 | enabled and ad      | ctive             |                   |                |

| bit 11-10    | Unimplemer    | nted: Read as 'o                                                     | )'              |                     |                   |                   |                |

| bit 9-8      | ASINT<1:0>    | : Auto-Scan (Th                                                      | reshold Detect  | :) Interrupt Mod    | e bits            |                   |                |

|              | 10 = Interru  | pt after Thresho<br>pt after valid cor<br>pt after Thresho<br>errupt | npare has occ   | urred               |                   | npare has occu    | urred          |

| bit 7-4      |               | nted: Read as 'o                                                     | )'              |                     |                   |                   |                |

| bit 3-2      | WM<1:0>: W    | /rite Mode bits                                                      |                 |                     |                   |                   |                |

|              | 11 = Reserv   |                                                                      |                 |                     |                   |                   | 4 1            |

|              |               | ompare only (con<br>occurs, as define                                |                 |                     |                   | s are generate    | d when a vai   |

|              | 01 = Conver   | t and save (con<br>match occurs, a                                   | version results | are saved to I      |                   | etermined by th   | ne register bi |

|              |               | operation (conv                                                      | -               |                     | tion determine    | ed by the buffer  | register bits  |

| bit 1-0      | CM<1:0>: C    | ompare Mode bi                                                       | ts              |                     |                   |                   |                |

|              |               | Window mode (                                                        |                 | urs if the conver   | rsion result is o | utside of the win | dow defined l  |

|              | 10 = Inside V | esponding buffer<br>Vindow mode (va<br>onding buffer pai             | alid match occu | irs if the convers  | sion result is in | side the window   | defined by th  |

|              |               | Than mode (va                                                        |                 | rs if the result is | s greater than    | the value in the  | correspondi    |

|              |               | nan mode (valid                                                      | match occurs i  | f the result is le  | ss than the val   | ue in the corres  | sponding buff  |

#### REGISTER 29-2: CW2: FLASH CONFIGURATION WORD 2

| U-1           | U-1           | U-1                                        | U-1            | U-1                | U-1              | U-1             | U-1          |  |  |  |

|---------------|---------------|--------------------------------------------|----------------|--------------------|------------------|-----------------|--------------|--|--|--|

| _             | —             | —                                          | _              | —                  | —                | _               |              |  |  |  |

| bit 23        | ÷             |                                            |                |                    |                  |                 | bit 16       |  |  |  |

|               |               |                                            |                |                    |                  |                 |              |  |  |  |

| R/PO-1        | r-1           | r-1                                        | R/PO-1         | R/PO-1             | R/PO-1           | R/PO-1          | R/PO-1       |  |  |  |

| IESO          | r             | r                                          | ALTVRF1        | ALTVRF0            | FNOSC2           | FNOSC1          | FNOSC0       |  |  |  |

| bit 15        |               | bit 8                                      |                |                    |                  |                 |              |  |  |  |

|               |               |                                            |                |                    |                  |                 |              |  |  |  |

| R/PO-1        | R/PO-1        | R/PO-1                                     | R/PO-1         | R/PO-1             | r-1              | R/PO-1          | R/PO-1       |  |  |  |

| FCKSM1        | FCKSM0        | OSCIOFCN                                   | IOL1WAY        | BOREN1             | r                | POSCMD1         | POSCMD0      |  |  |  |

| bit 7         |               |                                            |                |                    |                  |                 | bit 0        |  |  |  |

|               |               |                                            |                |                    |                  |                 |              |  |  |  |

| Legend:       |               | r = Reserved I                             |                | PO = Prograr       |                  |                 |              |  |  |  |

| R = Readabl   |               | W = Writable I                             | bit            |                    | nented bit, read | d as '0'        |              |  |  |  |

| -n = Value at | POR           | '1' = Bit is set                           |                | '0' = Bit is cle   | ared             | x = Bit is unkr | nown         |  |  |  |

|               |               |                                            |                |                    |                  |                 |              |  |  |  |

| bit 23-16     | -             | ted: Read as '1                            |                |                    |                  |                 |              |  |  |  |

| bit 15        |               | al External Swite                          |                | le l - el          |                  |                 |              |  |  |  |

|               |               | ode (Two-Speed<br>ode (Two-Speed           |                |                    |                  |                 |              |  |  |  |

| bit 14-13     |               | ways maintain a                            |                | Cabica             |                  |                 |              |  |  |  |

| bit 12-11     |               | -<br>>: Alternate VRI                      |                | Selection hits     |                  |                 |              |  |  |  |

|               |               | rator Voltage re                           |                |                    |                  | 31. ADC VREF    | + is RB0 and |  |  |  |

|               | ADC VF        | REF- is RB1                                |                |                    |                  |                 |              |  |  |  |

|               |               | rator Voltage re<br>REF- is RA9            | eference input | VREF+ is RB(       | ), VREF- is RB   | 1, ADC VREF+    | is RA10 and  |  |  |  |

|               | -             | rator Voltage re                           | eference input | VREF+ is RA        | 10. VREF- is R   | A9. ADC VREF    | + is RB0 and |  |  |  |

|               | ADC VF        | REF- is RB1                                |                |                    |                  |                 |              |  |  |  |

|               |               | rator Voltage re<br>REF- is RA9            | ference input  | VREF+ is RA1       | 0, VREF- is RA   | 19, ADC VREF    | is RA10 and  |  |  |  |

| bit 10-8      | FNOSC<2:0>    | : Initial Oscillate                        | or Select bits |                    |                  |                 |              |  |  |  |

|               |               | RC Oscillator wit                          | h Postscaler ( | FRCDIV)            |                  |                 |              |  |  |  |

|               | 110 = Reser   | ved<br>Power RC Oscill                     | ator (LPPC)    |                    |                  |                 |              |  |  |  |

|               |               | idary Oscillator                           | . ,            |                    |                  |                 |              |  |  |  |

|               | 011 = Prima   | ry Oscillator with                         | h PLL module   | (XTPLL, HSPL       | L, ECPLL)        |                 |              |  |  |  |

|               |               | ry Oscillator (XT                          |                | and DLL are advit  |                  |                 |              |  |  |  |

|               |               | RC Oscillator wit<br>RC Oscillator (FI     |                | and PLL module     | e (FRCPLL)       |                 |              |  |  |  |

| bit 7-6       |               | Clock Switchi                              | -              | afe Clock Monit    | tor Configuratio | n bits          |              |  |  |  |

|               |               | witching and Fa                            | -              |                    | -                |                 |              |  |  |  |

|               | 01 = Clock sv | witching is enab                           | led, Fail-Safe | Clock Monitor      | is disabled      |                 |              |  |  |  |

|               |               | witching is enab                           |                | Clock Monitor      | is enabled       |                 |              |  |  |  |

| bit 5         |               | OSCO Pin Con                               | 0              |                    |                  |                 |              |  |  |  |

|               |               | <u>1:0&gt; = 11 or 00</u><br>LKO/RC15 func |                | $\int (E_{OSC}/2)$ |                  |                 |              |  |  |  |

|               |               | LKO/RC15 lunc                              |                | . ,                |                  |                 |              |  |  |  |

|               |               | 1:0> = 10 or 01                            | -              | ( /                |                  |                 |              |  |  |  |

|               |               | nas no effect on                           |                | /RC15.             |                  |                 |              |  |  |  |

|               |               |                                            |                |                    |                  |                 |              |  |  |  |

#### 30.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 30.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 30.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 30.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 30.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| Assembly<br>Mnemonic |         | Assembly Syntax | Description                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|---------|-----------------|---------------------------------------------|---------------|----------------|--------------------------|

| BTSS                 | BTSS    | f,#bit4         | Bit Test f, Skip if Set                     | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSS    | Ws,#bit4        | Bit Test Ws, Skip if Set                    | 1             | 1<br>(2 or 3)  | None                     |

| BTST                 | BTST    | f,#bit4         | Bit Test f                                  | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,#bit4        | Bit Test Ws to C                            | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,#bit4        | Bit Test Ws to Z                            | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,Wb           | Bit Test Ws <wb> to C</wb>                  | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                  | 1             | 1              | Z                        |

| BTSTS                | BTSTS   | f,#bit4         | Bit Test then Set f                         | 1             | 1              | Z                        |

|                      | BTSTS.C | Ws,#bit4        | Bit Test Ws to C, then Set                  | 1             | 1              | С                        |

|                      | BTSTS.Z | Ws,#bit4        | Bit Test Ws to Z, then Set                  | 1             | 1              | Z                        |

| CALL                 | CALL    | lit23           | Call Subroutine                             | 2             | 2              | None                     |

|                      | CALL    | Wn              | Call Indirect Subroutine                    | 1             | 2              | None                     |

| CLR                  | CLR     | f               | f = 0x0000                                  | 1             | 1              | None                     |

| C                    | CLR     | WREG            | WREG = 0x0000                               | 1             | 1              | None                     |

|                      | CLR     | Ws              | Ws = 0x0000                                 | 1             | 1              | None                     |

| CLRWDT               | CLRWDT  |                 | Clear Watchdog Timer                        | 1             | 1              | WDTO, Sleep              |

| СОМ                  | СОМ     | f               | f = f                                       | 1             | 1              | N, Z                     |

|                      | СОМ     | f,WREG          | WREG = f                                    | 1             | 1              | N, Z                     |

|                      | СОМ     | Ws,Wd           | Wd = Ws                                     | 1             | 1              | N, Z                     |

| CP                   | CP      | f               | Compare f with WREG                         | 1             | 1              | C, DC, N, OV, 2          |

| 01                   | CP      | Wb,#lit5        | Compare Wb with lit5                        | 1             | 1              | C, DC, N, OV, 2          |

|                      | CP      | Wb,Ws           | Compare Wb with Ws (Wb – Ws)                | 1             | 1              | C, DC, N, OV, Z          |

| CP0                  | CP0     | f               | Compare f with 0x0000                       | 1             | 1              | C, DC, N, OV, Z          |

| CFU                  | CP0     | Ws              | Compare Ws with 0x0000                      | 1             | 1              | C, DC, N, OV, 2          |

| CPB                  | CPB     | f               | Compare f with WREG, with Borrow            | 1             | 1              | C, DC, N, OV, Z          |

| 010                  | CPB     | Wb,#lit5        | Compare Wb with lit5, with Borrow           | 1             | 1              | C, DC, N, OV, 2          |

|                      | CPB     | Wb,Ws           | Compare Wb with Ws, with Borrow             | 1             | 1              | C, DC, N, OV, 2          |

|                      |         |                 | $(Wb - Ws - \overline{C})$                  |               |                |                          |

| CPSEQ                | CPSEQ   | Wb,Wn           | Compare Wb with Wn, Skip if =               | 1             | 1<br>(2 or 3)  | None                     |

| CPSGT                | CPSGT   | Wb,Wn           | Compare Wb with Wn, Skip if >               | 1             | 1<br>(2 or 3)  | None                     |

| CPSLT                | CPSLT   | Wb,Wn           | Compare Wb with Wn, Skip if <               | 1             | 1<br>(2 or 3)  | None                     |

| CPSNE                | CPSNE   | Wb,Wn           | Compare Wb with Wn, Skip if ≠               | 1             | 1<br>(2 or 3)  | None                     |

| DAW                  | DAW.B   | Wn              | Wn = Decimal Adjust Wn                      | 1             | 1              | С                        |

| DEC                  | DEC     | f               | f = f - 1                                   | 1             | 1              | C, DC, N, OV, 2          |

|                      | DEC     | f,WREG          | WREG = f –1                                 | 1             | 1              | C, DC, N, OV, 2          |

|                      | DEC     | Ws,Wd           | Wd = Ws - 1                                 | 1             | 1              | C, DC, N, OV, 2          |

| DEC2                 | DEC2    | f               | f = f - 2                                   | 1             | 1              | C, DC, N, OV, 2          |

|                      | DEC2    | f,WREG          | WREG = $f - 2$                              | 1             | 1              | C, DC, N, OV, 2          |

|                      | DEC2    | Ws,Wd           | Wd = Ws - 2                                 | 1             | 1              | C, DC, N, OV, 2          |

| DISI                 | DISI    | #lit14          | Disable Interrupts for k Instruction Cycles | 1             | 1              | None                     |

| DIV                  | DIV.SW  | Wm,Wn           | Signed 16/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.SD  | Wm,Wn           | Signed 32/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UW  | Wm,Wn           | Unsigned 16/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UD  | Wm,Wn           | Unsigned 32/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

| EXCH                 | EXCH    | Wns,Wnd         | Swap Wns with Wnd                           | 1             | 1              | None                     |

| FF1L                 | FF1L    | Ws,Wnd          | Find First One from Left (MSb) Side         | 1             | 1              | С                        |

| FF1R                 | FF1R    | Ws,Wnd          | Find First One from Right (LSb) Side        | 1             | 1              | С                        |

#### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 32-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAC        | TERISTICS              |      | Standard Operating Conditions: 2V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                          |      |                   |  |

|------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Мах  | Units                                                                                                                                          | Operating<br>Temperature | Vdd  | Conditions        |  |

| Idle Current (   | lidle)                 |      |                                                                                                                                                |                          |      |                   |  |

| DC40             | 81                     | _    | μΑ                                                                                                                                             | -40°C to +85°C           | 2.0V | 1 MIPS,           |  |

|                  | 86                     | _    | μA                                                                                                                                             | -40°C to +85°C           | 3.3V | Fosc = 2 MHz      |  |

| DC43             | 0.27                   | _    | mA                                                                                                                                             | -40°C to +85°C           | 2.0V | 4 MIPS,           |  |

|                  | 0.28                   | _    | mA                                                                                                                                             | -40°C to +85°C           | 3.3V | Fosc = 8 MHz      |  |

| DC47             | 1                      | 1.35 | mA                                                                                                                                             | -40°C to +85°C           | 2.0V | 16 MIPS,          |  |