Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga310t-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Power Supply Pins

## 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

## 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

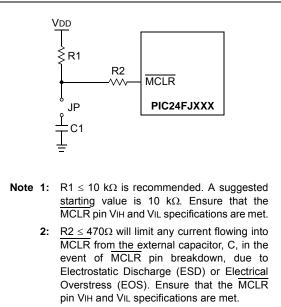

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "CPU with Extended Data Space (EDS)" (DS39732) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

The lower 32 Kbytes of the Data Space can be accessed linearly. The upper 32 Kbytes of the Data Space are referred to as Extended Data Space (EDS) to which the extended data RAM, EPMP memory space or program memory can be mapped.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs. The core supports Inherent (no operand), Relative, Literal and Memory Direct Addressing modes, along with three other groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit x 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit x 16-bit or 8-bit x 8-bit, integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

# 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory-mapped.

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space during code execution.

# 4.1 **Program Memory Space**

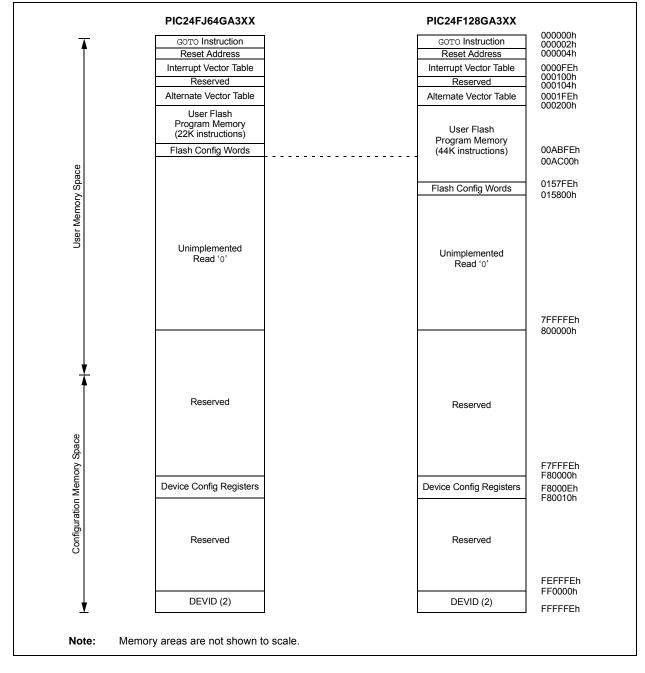

The program address memory space of the PIC24FJ128GA310 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.3** "Interfacing **Program and Data Memory Spaces**".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ128GA310 family of devices are shown in Figure 4-1.

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ128GA310 FAMILY DEVICES

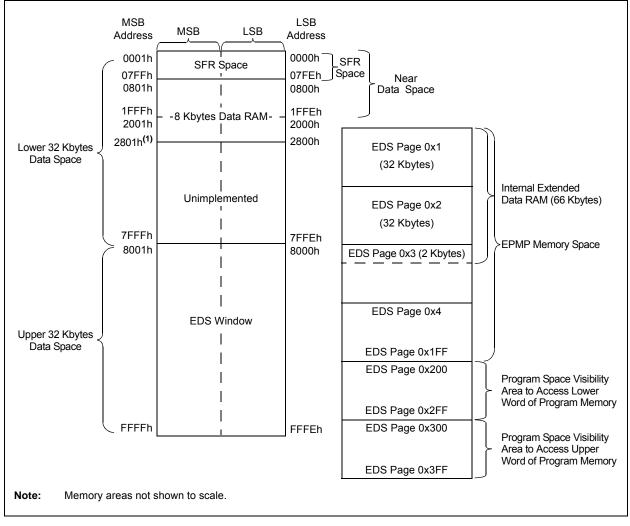

## 4.2 Data Memory Space

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to "Data Memory with Extended Data Space (EDS)" (DS39733) in the "dsPIC33/PIC24 Family Reference Manual". The information in this data sheet supersedes the information in the FRM.

The PIC24F core has a 16-bit-wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is shown in Figure 4-3.

The 16-bit wide data addresses in the data memory space point to bytes within the Data Space (DS). This gives a DS address range of 64 Kbytes or 32K words. The lower half (0000h to 7FFFh) is used for implemented (on-chip) memory addresses.

The upper half of data memory address space (8000h to FFFFh) is used as a window into the Extended Data Space (EDS). This allows the microcontroller to directly access a greater range of data beyond the standard 16-bit address range. EDS is discussed in detail in **Section 4.2.5 "Extended Data Space (EDS)**".

The lower half of DS is compatible with previous PIC24F microcontrollers without EDS. All PIC24FJ128GA310 family devices implement 8 Kbytes of data RAM in the lower half of DS, from 0800h to 27FFh.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

| R/W-0                | R/W-0                                             | U-0                                | R/W-0                   | U-0                     | R/W-0                       | R/W-0              | R/W-0                |  |

|----------------------|---------------------------------------------------|------------------------------------|-------------------------|-------------------------|-----------------------------|--------------------|----------------------|--|

| TRAPR <sup>(1)</sup> | IOPUWR <sup>(1)</sup>                             | —                                  | RETEN <sup>(2)</sup>    |                         | DPSLP <sup>(1)</sup>        | CM <sup>(1)</sup>  | VREGS <sup>(3)</sup> |  |

| bit 15               |                                                   |                                    |                         |                         |                             |                    | bit 8                |  |

| R/W-0                | R/W-0                                             | R/W-0                              | R/W-0                   | R/W-0                   | R/W-0                       | R/W-1              | R/W-1                |  |

| EXTR <sup>(1)</sup>  | SWR <sup>(1)</sup>                                | SWDTEN <sup>(4)</sup>              | WDTO <sup>(1)</sup>     | SLEEP <sup>(1)</sup>    | IDLE <sup>(1)</sup>         | BOR <sup>(1)</sup> | POR <sup>(1)</sup>   |  |

| bit 7                |                                                   | -                                  |                         | _                       |                             |                    | bit (                |  |

| Legend:              |                                                   |                                    |                         |                         |                             |                    |                      |  |

| R = Readab           | le bit                                            | W = Writable b                     | bit                     | U = Unimpler            | nented bit, read            | as '0'             |                      |  |

| -n = Value a         | t POR                                             | '1' = Bit is set                   |                         | '0' = Bit is cle        | ared                        | x = Bit is unkr    | nown                 |  |

| bit 15               | TRAPR: Trap                                       | Reset Flag bit                     | 1)                      |                         |                             |                    |                      |  |

|                      |                                                   | onflict Reset ha                   |                         |                         |                             |                    |                      |  |

|                      | •                                                 | onflict Reset ha                   |                         |                         |                             |                    |                      |  |

| bit 14               | •                                                 | gal Opcode or I                    |                         |                         | •                           |                    |                      |  |

|                      | 0                                                 | opcode detec<br>Pointer and cau    | . 0                     | address mod             | le or Uninitialize          | ed vv register     | is used as ar        |  |

|                      |                                                   | opcode or Unir                     |                         | set has not oc          | curred                      |                    |                      |  |

| bit 13               | Unimplement                                       | ed: Read as 'o                     | ,                       |                         |                             |                    |                      |  |

| bit 12               | RETEN: Reter                                      | ntion Mode Ena                     | able bit <sup>(2)</sup> |                         |                             |                    |                      |  |

|                      |                                                   | mode is enabl<br>mode is disab     |                         |                         | odes (1.2V reg<br>e present | ulator supplies    | to the core)         |  |

| bit 11               | Unimplement                                       | ed: Read as '0                     | ,                       |                         |                             |                    |                      |  |

| bit 10               | DPSLP: Deep Sleep Flag bit <sup>(1)</sup>         |                                    |                         |                         |                             |                    |                      |  |

|                      |                                                   | s been in Deep<br>s not been in D  |                         | de                      |                             |                    |                      |  |

| bit 9                | CM: Configura                                     | ation Word Misi                    | match Reset F           | lag bit <sup>(1)</sup>  |                             |                    |                      |  |

|                      | •                                                 | ration Word Mi<br>ration Word Mi   |                         |                         | red                         |                    |                      |  |

| bit 8                | VREGS: Prog                                       | ram Memory P                       | ower During S           | leep bit <sup>(3)</sup> |                             |                    |                      |  |

|                      |                                                   | memory bias vo<br>memory bias vo   |                         |                         |                             |                    |                      |  |

| bit 7                | -                                                 | al Reset (MCLI                     |                         |                         | 0                           |                    |                      |  |

|                      |                                                   | Clear (pin) Res<br>Clear (pin) Res |                         |                         |                             |                    |                      |  |

| bit 6                |                                                   | e Reset (Instru                    |                         |                         |                             |                    |                      |  |

|                      |                                                   | instruction has                    |                         |                         |                             |                    |                      |  |

|                      | 0 = A RESET                                       | instruction has                    | not been exec           | uted                    |                             |                    |                      |  |

|                      | Il of the Reset sta<br>ause a device Re           |                                    | e set or cleared        | d in software. S        | Setting one of th           | ese bits in soft   | ware does not        |  |

| <b>2:</b> If         | the LPCFG Contas no effect.                       |                                    | 1' (unprogramı          | med), the reter         | ntion regulator is          | disabled and       | the RETEN bit        |  |

| S                    | Re-enabling the re<br>leep. Application ccurring. |                                    |                         |                         |                             |                    |                      |  |

|                      | the FWDTEN Co<br>WDTEN bit settin                 | -                                  | is '1' (unprogra        | ammed), the V           | VDT is always e             | nabled, regard     | lless of the         |  |

# REGISTER 7-1: RCON: RESET CONTROL REGISTER

| U-0           | R/W-0                                                                                  | R/W-0                                                                                                     | R/W-0                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| —             | DMA1IE                                                                                 | AD1IE                                                                                                     | U1TXIE                | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |  |  |  |  |

| oit 15        |                                                                                        |                                                                                                           |                       | ·                 |                  |                 | bit 8  |  |  |  |  |

| R/W-0         | R/W-0                                                                                  | R/W-0                                                                                                     | R/W-0                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IE          | OC2IE                                                                                  | IC2IE                                                                                                     | DMA0IE                | T1IE              | OC1IE            | IC1IE           | INT0IE |  |  |  |  |

| bit 7         |                                                                                        | •                                                                                                         | ·                     |                   |                  |                 | bit (  |  |  |  |  |

| Legend:       |                                                                                        |                                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

| R = Readabl   | le bit                                                                                 | W = Writable                                                                                              | bit                   | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set                                                                                          |                       | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |  |  |  |

| bit 15        | Unimplemen                                                                             | ted: Read as '                                                                                            | 0'                    |                   |                  |                 |        |  |  |  |  |

| bit 14        | •                                                                                      |                                                                                                           | 。<br>Iterrupt Flag Er | nable bit         |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt                                                                          | request is not                                                                                            | enabled               |                   |                  |                 |        |  |  |  |  |

| bit 13        |                                                                                        |                                                                                                           | omplete Interru       | upt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal<br>request is not o                                                                       |                       |                   |                  |                 |        |  |  |  |  |

| bit 12        | U1TXIE: UART1 Transmitter Interrupt Enable bit                                         |                                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not                                                                                            |                       |                   |                  |                 |        |  |  |  |  |

| pit 11        | <b>U1RXIE:</b> UART1 Receiver Interrupt Enable bit<br>1 = Interrupt request is enabled |                                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | 0 = Interrupt request is not enabled                                                                      |                       |                   |                  |                 |        |  |  |  |  |

| oit 10        | SPI1IE: SPI1 Transfer Complete Interrupt Enable bit                                    |                                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

| bit 9         | •                                                                                      | <ul> <li>0 = Interrupt request is not enabled</li> <li>SPF1IE: SPI1 Fault Interrupt Enable bit</li> </ul> |                       |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt                                                                          | request is enal<br>request is not (                                                                       | bled                  |                   |                  |                 |        |  |  |  |  |

| bit 8         | •                                                                                      | Interrupt Enab                                                                                            |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal<br>request is not                                                                         |                       |                   |                  |                 |        |  |  |  |  |

| bit 7         |                                                                                        | Interrupt Enab                                                                                            |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal<br>request is not                                                                         |                       |                   |                  |                 |        |  |  |  |  |

| bit 6         |                                                                                        | •                                                                                                         | annel 2 Interru       | pt Enable bit     |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal                                                                                           |                       | -                 |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not                                                                                            |                       |                   |                  |                 |        |  |  |  |  |

| bit 5         | -                                                                                      | -                                                                                                         | el 2 Interrupt E      | nable bit         |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal<br>request is not o                                                                       |                       |                   |                  |                 |        |  |  |  |  |

| bit 4         | DMAOIE: DM                                                                             | A Channel 0 Ir                                                                                            | iterrupt Flag Er      | nable bit         |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enal<br>request is not                                                                         |                       |                   |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                        | Interrupt Enab<br>request is enal                                                                         |                       |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        |                                                                                                           |                       |                   |                  |                 |        |  |  |  |  |

# REGISTER 8-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

# REGISTER 8-21: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                         | R/W-0         | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------|-----------------|---------|--|--|--|--|

| _             | T1IP2                                                                                                                     | T1IP1                                                                                                         | T1IP0         | —                 | OC1IP2           | OC1IP1          | OC1IP0  |  |  |  |  |

| bit 15        |                                                                                                                           |                                                                                                               |               |                   |                  |                 | bit 8   |  |  |  |  |

|               |                                                                                                                           |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                         | R/W-0         | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

| —             | IC1IP2                                                                                                                    | IC1IP1                                                                                                        | IC1IP0        | —                 | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |

| bit 7         |                                                                                                                           |                                                                                                               |               |                   |                  |                 | bit (   |  |  |  |  |

|               |                                                                                                                           |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| Legend:       |                                                                                                                           |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| R = Readabl   |                                                                                                                           | W = Writable                                                                                                  | DIT           | -                 | nented bit, read |                 |         |  |  |  |  |

| -n = Value at | POR                                                                                                                       | '1' = Bit is set                                                                                              |               | '0' = Bit is cle  | ared             | x = Bit is unkr | nown    |  |  |  |  |

| bit 15        | Unimplemer                                                                                                                | nted: Read as '                                                                                               | )'            |                   |                  |                 |         |  |  |  |  |

| bit 14-12     | -                                                                                                                         | Timer1 Interrupt                                                                                              |               |                   |                  |                 |         |  |  |  |  |

|               |                                                                                                                           | -                                                                                                             | -             | v interrupt)      |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                     |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •<br>001 = Interrupt is Priority 1                                                                                        |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | 000 = Interrupt source is disabled                                                                                        |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| bit 11        |                                                                                                                           | nted: Read as '                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| bit 10-8      | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits                                                              |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                       |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| bit 7         |                                                                                                                           | nted: Read as '                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| bit 6-4       | -                                                                                                                         |                                                                                                               |               | runt Priority hit | e                |                 |         |  |  |  |  |

|               | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               |                                                                                                                           |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                       |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

| bit 3         |                                                                                                                           | nted: Read as '                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | -                                                                                                                         |                                                                                                               |               | site              |                  |                 |         |  |  |  |  |

| bit 2-0       |                                                                                                                           | INT0IP<2:0>: External Interrupt 0 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               | nighest phone | y interrupt)      |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | •                                                                                                                         |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               | 001 = Interrupt is Priority 1                                                                                             |                                                                                                               |               |                   |                  |                 |         |  |  |  |  |

|               |                                                                                                                           | upt is Priority 1<br>upt source is dis                                                                        |               |                   |                  |                 |         |  |  |  |  |

## REGISTER 8-35: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

|              |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                |                        |                 | -               |                    |  |  |  |

|--------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|-----------------|-----------------|--------------------|--|--|--|

| U-0          | U-0                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0              | U-0                    | R/W-1           | R/W-0           | R/W-0              |  |  |  |

| _            | _                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                | _                      | RTCIP2          | RTCIP1          | RTCIP0             |  |  |  |

| bit 15       |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                        |                 | -               | bit                |  |  |  |

|              |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                        |                 |                 |                    |  |  |  |

| U-0          | R/W-1                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0            | U-0                    | U-0             | U-0             | U-0                |  |  |  |

| —            | DMA5IP2                                  | DMA5IP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DMA5IP0          | —                      | —               | —               |                    |  |  |  |

| bit 7        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                        |                 |                 | bit (              |  |  |  |

|              |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                        |                 |                 |                    |  |  |  |

| Legend:      |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                        |                 |                 |                    |  |  |  |

| R = Readab   | ole bit                                  | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit              | U = Unimplen           | nented bit, rea | d as '0'        |                    |  |  |  |

| -n = Value a | it POR                                   | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | '0' = Bit is cleared x |                 | x = Bit is unkr | x = Bit is unknown |  |  |  |

|              | •<br>•                                   | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>.</li> <li></li></ul> |                  |                        |                 |                 |                    |  |  |  |