# E·XFL

#### NXP USA Inc. - KMPC8560PXAQFB Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DDR, SDRAM                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | - ·                                                                    |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | - ·                                                                    |

| Voltage - I/O                   | 2.5V, 3.3V                                                             |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 783-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8560pxaqfb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs

- Interrupt summary registers allow fast identification of interrupt source

- I<sup>2</sup>C controller

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 166 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-,16-, or 32-bit)

- Two three-speed (10/100/1Gb) Ethernet controllers (TSECs)

- Dual IEEE 802.3, 802.3u, 802.3x, 802.3z, 802.3ac, 802.3ab compliant controllers

- Support for different Ethernet physical interfaces:

- 10/100/1Gb Mbps IEEE 802.3 GMII

- 10/100 Mbps IEEE 802.3 MII

- 10 Mbps IEEE 802.3 MII

- 1000 Mbps IEEE 802.3z TBI

- 10/100/1Gb Mbps RGMII/RTBI

- Full- and half-duplex support

- Buffer descriptors are backward compatible with MPC8260 and MPC860T 10/100 programming models

- 9.6-Kbyte jumbo frame support

- RMON statistics support

- 2-Kbyte internal transmit and receive FIFOs

#### **Electrical Characteristics**

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the 8 counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>TM</sup>-compliant, JTAG boundary scan

- 783 FC-PBGA package

# 2 Electrical Characteristics

This section provides the electrical specifications and thermal characteristics for the MPC8560. The MPC8560 is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

|                     | Characteristic                                                     | Symbol           | Max Value                    | Unit | Notes |

|---------------------|--------------------------------------------------------------------|------------------|------------------------------|------|-------|

| Core supply voltage | For devices rated at 667 and 833 MHz<br>For devices rated at 1 GHz | V <sub>DD</sub>  | -0.3 to 1.32<br>-0.3 to 1.43 | V    | —     |

| PLL supply voltage  | For devices rated at 667 and 833 MHz<br>For devices rated at 1 GHz | AV <sub>DD</sub> | -0.3 to 1.32<br>-0.3 to 1.43 | V    | —     |

#### Table 1. Absolute Maximum Ratings <sup>1</sup>

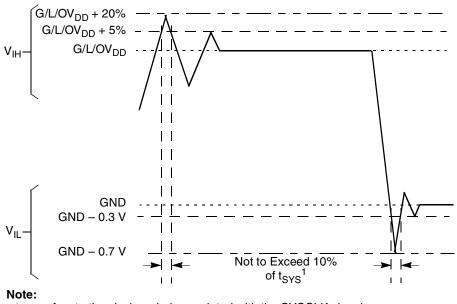

t<sub>SYS</sub> refers to the clock period associated with the SYSCLK signal.

#### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The MPC8560 core voltage must always be provided at nominal 1.2 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied  $MV_{REF}$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

#### **Electrical Characteristics**

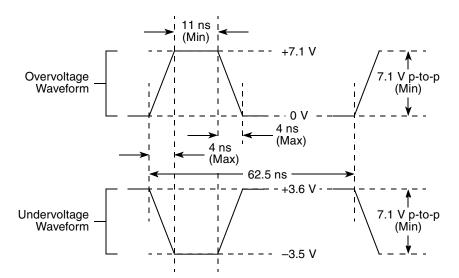

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8560 for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI interface for 3.3-V Signaling

### 2.1.4 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable Output<br>Impedance (Ω) | Supply Voltage               | Notes |

|---------------------------------------|--------------------------------------|------------------------------|-------|

| Local bus interface utilities signals | 25                                   | OV <sub>DD</sub> = 3.3 V     | 1     |

|                                       | 42 (default)                         |                              |       |

| PCI signals                           | 25                                   |                              | 2     |

|                                       | 42 (default)                         |                              |       |

| DDR signal                            | 20                                   | GV <sub>DD</sub> = 2.5 V     |       |

| CPM PA, PB, PC, and PD signals        | 42                                   | OV <sub>DD</sub> = 3.3 V     | —     |

| TSEC/10/100 signals                   | 42                                   | LV <sub>DD</sub> = 2.5/3.3 V | —     |

| DUART, system control, I2C, JTAG      | 42                                   | OV <sub>DD</sub> = 3.3 V     | —     |

| RapidIO N/A (LVDS signaling)          | N/A                                  |                              | —     |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

# 4.4 Real Time Clock Timing

Table 10 provides the real time clock (RTC) AC timing specifications for the MPC8560.

Table 10. RTC AC Timing Specifications

| Parameter/Condition | Symbol            | Min                         | Typical | Max | Unit | Notes |

|---------------------|-------------------|-----------------------------|---------|-----|------|-------|

| RTC clock high time | <sup>t</sup> RTCH | 2 x<br>t <sub>CCB_CLK</sub> | —       | _   | ns   | —     |

| RTC clock low time  | t <sub>RTCL</sub> | 2 х<br>t <sub>CCB_CLK</sub> | —       | _   | ns   | _     |

# **5 RESET Initialization**

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8560. Table 7 provides the RESET initialization AC timing specifications for the MPC8560.

Table 11. RESET Initialization Timing Specifications

| Parameter/Condition                                                                                     | Min | Max | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | _   | μs      | _     |

| Minimum assertion time for SRESET                                                                       | 512 | _   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before<br>HRESET negation                                       | 100 | _   | μs      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for POR configs (including PLL config) with respect to negation of HRESET               | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET |     | 5   | SYSCLKs | 1     |

Notes:

1.SYSCLK is identical to the PCI\_CLK signal and is the primary clock input for the MPC8560. See the MPC8560 PowerQUICC III™ Integrated Communications Processor Preliminary Reference Manual for more details.

Table 12 provides the PLL and DLL lock times.

Table 12. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit       | Notes |

|---------------------|------|---------|------------|-------|

| PLL lock times      | _    | 100     | μs         | —     |

| DLL lock times      | 7680 | 122,880 | CCB Clocks | 1, 2  |

Notes:

1.DLL lock times are a function of the ratio between the output clock and the platform (or CCB) clock. A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The CCB clock is determined by the SYSCLK  $\times$  platform PLL ratio.

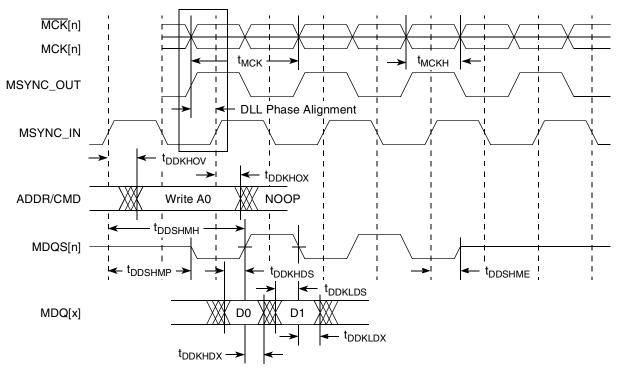

#### Table 16. DDR SDRAM Output AC Timing Specifications–DLL Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter         | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|-------------------|---------------------|-----|-----|------|-------|

| MDQS epilogue end | t <sub>DDSHME</sub> | 1.5 | 4.0 | ns   | 7, 8  |

#### Notes:

1.The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (OX or DX). For example, t<sub>DDKHOV</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (O) are valid (V) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.</sub>

2.All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3.Maximum possible clock skew between a clock MCK[n] and its relative inverse clock MCK[n], or between a clock MCK[n] and a relative clock MCK[m] or MSYNC\_OUT. Skew measured between complementary signals at GV<sub>DD</sub>/2.

4.ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK and MDQ/MECC/MDM/MDQS.

- 5.Note that t<sub>DDSHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDSHMH</sub> describes the DDR timing (DD) from the rising edge of the MSYNC\_IN clock (SH) until the MDQS signal is valid (MH). t<sub>DDSHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. These controls allow the relationship between the synchronous clock control timing and the source-synchronous DQS domain to be modified by the user. For best turnaround times, these may need to be set to delay t<sub>DDSHMH</sub> an additional 0.25t<sub>MCK</sub>. This will also affect t<sub>DDSHMP</sub> and t<sub>DDSHME</sub> accordingly. See the *MPC8560 PowerQUICC III Integrated Communications Processor Reference Manual* for a description and understanding of the timing modifications enabled by use of these bits.

- 6.Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8560.

- 7.All outputs are referenced to the rising edge of MSYNC\_IN (S) at the pins of the MPC8560. Note that t<sub>DDSHMP</sub> follows the symbol conventions described in note 1. For example, t<sub>DDSHMP</sub> describes the DDR timing (DD) from the rising edge of the MSYNC\_IN clock (SH) for the duration of the MDQS signal precharge period (MP).

8. Guaranteed by design.

9. Guaranteed by characterization.

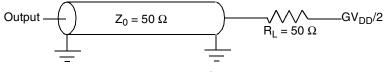

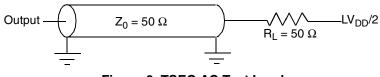

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

| Symbol           | DDR                        | Unit | Notes |

|------------------|----------------------------|------|-------|

| V <sub>TH</sub>  | MV <sub>REF</sub> ± 0.31 V | V    | 1     |

| V <sub>OUT</sub> | $0.5 	imes GV_{DD}$        | V    | 2     |

Notes:

1.Data input threshold measurement point.

2.Data output measurement point.

#### DDR SDRAM

Figure 6 shows the DDR SDRAM output timing diagram.

Figure 6. DDR SDRAM Output Timing Diagram

### 6.2.2.2 Load Effects on Address/Command Bus

Table 18 provides approximate delay information that can be expected for the address and command signals of the DDR controller for various loadings. These numbers are the result of simulations for one topology. The delay numbers will strongly depend on the topology used. These delay numbers show the total delay for the address and command to arrive at the DRAM devices. The actual delay could be different than the delays seen in simulation, depending on the system topology. If a heavily loaded system is used, the DLL loop may need to be adjusted to meet setup requirements at the DRAM.

| Load                                               | Delay | Unit |

|----------------------------------------------------|-------|------|

| 4 devices (12 pF)                                  | 3.0   | ns   |

| 9 devices (27 pF)                                  | 3.6   | ns   |

| 36 devices (108 pF) + 40 pF compensation capacitor | 5.0   | ns   |

| 36 devices (108 pF) + 80 pF compensation capacitor | 5.2   | ns   |

| Table 18. Expected Delays for Address/Command |

|-----------------------------------------------|

|-----------------------------------------------|

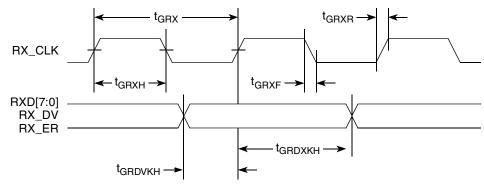

#### Table 22. GMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%, or LV<sub>DD</sub>=2.5V  $\pm$  5%.

| Parameter/Condition             | Symbol <sup>1</sup>                                  | Min | Тур | Max | Unit |

|---------------------------------|------------------------------------------------------|-----|-----|-----|------|

| RX_CLK clock rise and fall time | t <sub>GRXR</sub> , t <sub>GRXF</sub> <sup>2,3</sup> | _   |     | 1.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 8 provides the AC test load for TSEC.

Figure 8. TSEC AC Test Load

Figure 9 shows the GMII receive AC timing diagram.

Figure 9. GMII Receive AC Timing Diagram

# 7.2.2 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

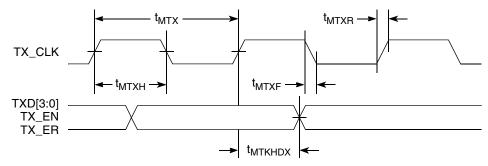

### 7.2.2.1 MII Transmit AC Timing Specifications

Table 23 provides the MII transmit AC timing specifications.

#### Table 23. MII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V ± 5%, or LV<sub>DD</sub>=2.5V ± 5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                                  | Min | Тур | Мах | Unit |

|-------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>                        | _   | 400 | —   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                                     | _   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH/</sub> t <sub>MTX</sub>                  | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                                  | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise and fall time            | t <sub>MTXR</sub> , t <sub>MTXF</sub> <sup>2,3</sup> | 1.0 | _   | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.3.Guaranteed by design.

Figure 10 shows the MII transmit AC timing diagram.

Figure 10. MII Transmit AC Timing Diagram

# 7.2.3 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 7.2.3.1 TBI Transmit AC Timing Specifications

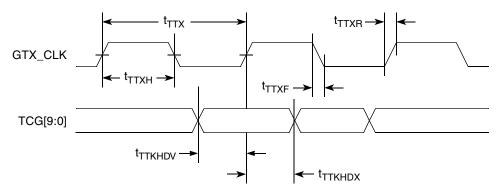

Table 25 provides the TBI transmit AC timing specifications.

#### Table 25. TBI Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V ± 5%, or LV<sub>DD</sub>=2.5V ± 5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                                  | Min | Тур | Max | Unit |

|--------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period                       | t <sub>TTX</sub>                                     | —   | 8.0 | _   | ns   |

| GTX_CLK duty cycle                         | t <sub>TTXH</sub> /t <sub>TTX</sub>                  | 40  | —   | 60  | %    |

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>                                  | 2.0 | —   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | <sup>t</sup> тткнdх                                  | 1.0 | —   | _   | ns   |

| GTX_CLK clock rise and fall time           | t <sub>TTXR</sub> , t <sub>TTXF</sub> <sup>2,3</sup> | —   | —   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t(first two letters of functional block)(signal)(state

)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 12 shows the TBI transmit AC timing diagram.

Figure 12. TBI Transmit AC Timing Diagram

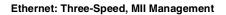

Figure 14. RGMII and RTBI AC Timing and Multiplexing Diagrams

# 7.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI and RTBI are specified in Section 7.1, "Three-Speed Ethernet Controller (TSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics."

# 7.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 28.

| Parameter                                                             | Symbol           | Min  | Мах                    | Unit |

|-----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                                | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )             | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                    | V <sub>IH</sub>  | 1.70 | —                      | V    |

| Input low voltage                                                     | V <sub>IL</sub>  | —    | 0.90                   | V    |

Table 28. MII Management DC Electrical Characteristics

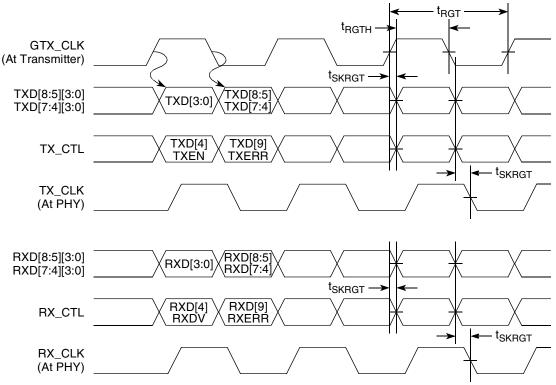

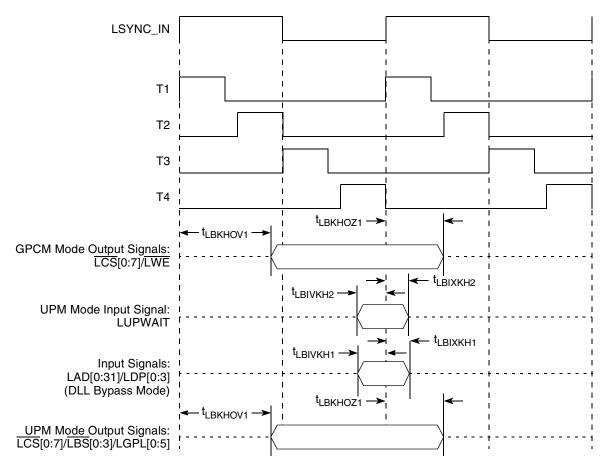

Local Bus

Figure 19. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

Local Bus

Figure 21. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Enabled)

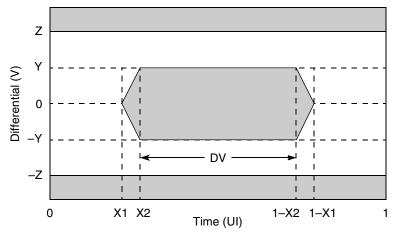

RapidIO

Figure 43. Example Compliance Mask

Y = minimum data valid amplitude

Z = maximum amplitude

1 UI = 1 unit interval = 1/baud rate

X1 = end of zero crossing region

X2 = beginning of data valid window

$DV = data valid window = 1 - 2 \times X2$

The waveform of the signal under test must fall within the unshaded area of the mask to be compliant. Different masks are used for the driver output and the receiver input allowing each to be separately specified.

## **13.3.1 RapidIO Driver AC Timing Specifications**

Driver AC timing specifications are provided in Table 48, Table 49, and Table 50. A driver shall comply with the specifications for each data rate/frequency for which operation of the driver is specified. Unless otherwise specified, these specifications are subject to the following conditions.

- The specifications apply over the supply voltage and ambient temperature ranges specified by the device vendor.

- The specifications apply for any combination of data patterns on the data signals.

- The output of a driver shall be connected to a 100  $\Omega$ , ±1%, differential (bridged) resistive load.

- Clock specifications apply only to clock signals.

- Data specifications apply only to data signals (FRAME, D[0:7]).

Table 48. RapidIO Driver AC Timing Specifications—500 Mbps Data Rate

| Characteristic                   | Symbol           | Rai  | nge  | Unit | Notes |

|----------------------------------|------------------|------|------|------|-------|

|                                  | Symbol           | Min  | Мах  |      |       |

| Differential output high voltage | V <sub>OHD</sub> | 200  | 540  | mV   | 1     |

| Differential output low voltage  | V <sub>OLD</sub> | -540 | -200 | mV   | 1     |

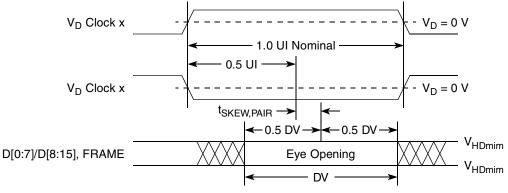

Figure 48 shows the definitions of the data to clock static skew parameter  $t_{SKEW,PAIR}$  and the data valid window parameter DV. The data and frame bits are those that are associated with the clock. The figure applies for all zero-crossings of the clock. All of the signals are differential signals.  $V_D$  represents  $V_{OD}$  for the transmitter and  $V_{ID}$  for the receiver. The center of the eye is defined as the midpoint of the region in which the magnitude of the signal voltage is greater than or equal to the minimum DV voltage.

Figure 48. Data to Clock Skew

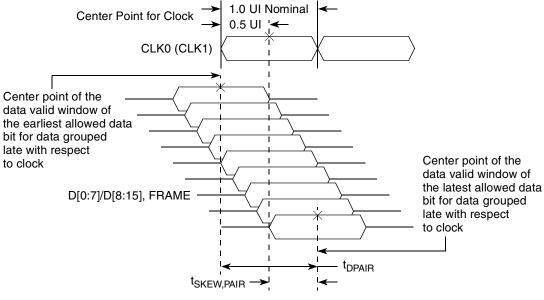

Figure 49 shows the definition of the data to data static skew parameter t<sub>DPAIR</sub> and how the skew parameters are applied.

Figure 49. Static Skew Diagram

Package and Pin Listings

| Signal         | Package Pin Number                                                                                           | Pin Type  | Power<br>Supply  | Notes |

|----------------|--------------------------------------------------------------------------------------------------------------|-----------|------------------|-------|

|                | Gigabit Reference Clock                                                                                      |           |                  |       |

| EC_GTX_CLK125  | E2                                                                                                           | I         | LV <sub>DD</sub> | —     |

|                | Three-Speed Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet) | hernet 1) |                  |       |

| TSEC1_TXD[7:4] | A6, F7, D7, C7                                                                                               | 0         | LV <sub>DD</sub> | 5, 9  |

| TSEC1_TXD[3:0] | B7, A7, G8, E8                                                                                               | 0         | LV <sub>DD</sub> | 9, 19 |

| TSEC1_TX_EN    | C8                                                                                                           | 0         | LV <sub>DD</sub> | 11    |

| TSEC1_TX_ER    | B8                                                                                                           | 0         | LV <sub>DD</sub> | _     |

| TSEC1_TX_CLK   | C6                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_GTX_CLK  | B6                                                                                                           | 0         | LV <sub>DD</sub> | 18    |

| TSEC1_CRS      | C3                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_COL      | G7                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_RXD[7:0] | D4, B4, D3, D5, B5, A5, F6, E6                                                                               | I         | LV <sub>DD</sub> | _     |

| TSEC1_RX_DV    | D2                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_RX_ER    | E5                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_RX_CLK   | D6                                                                                                           | I         | LV <sub>DD</sub> | _     |

|                | Three-Speed Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet) | hernet 2) |                  |       |

| TSEC2_TXD[7:2] | B10, A10, J10, K11,J11, H11                                                                                  | 0         | LV <sub>DD</sub> | 5, 9  |

| TSEC2_TXD[1:0] | G11, E11                                                                                                     | 0         | LV <sub>DD</sub> | _     |

| TSEC2_TX_EN    | B11                                                                                                          | 0         | LV <sub>DD</sub> | 11    |

| TSEC2_TX_ER    | D11                                                                                                          | 0         | LV <sub>DD</sub> | _     |

| TSEC2_TX_CLK   | D10                                                                                                          | I         | LV <sub>DD</sub> | _     |

| TSEC2_GTX_CLK  | C10                                                                                                          | 0         | LV <sub>DD</sub> | 18    |

| TSEC2_CRS      | D9                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC2_COL      | F8                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC2_RXD[7:0] | F9, E9, C9, B9, A9, H9, G10, F10                                                                             | I         | LV <sub>DD</sub> | _     |

| TSEC2_RX_DV    | Н8                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC2_RX_ER    | A8                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC2_RX_CLK   | E10                                                                                                          | I         | LV <sub>DD</sub> | _     |

|                | RapidIO Interface                                                                                            | 1         | 1                |       |

| RIO_RCLK       | Y25                                                                                                          | I         | OV <sub>DD</sub> | _     |

| RIO_RCLK       | Y24                                                                                                          | I         | OV <sub>DD</sub> | _     |

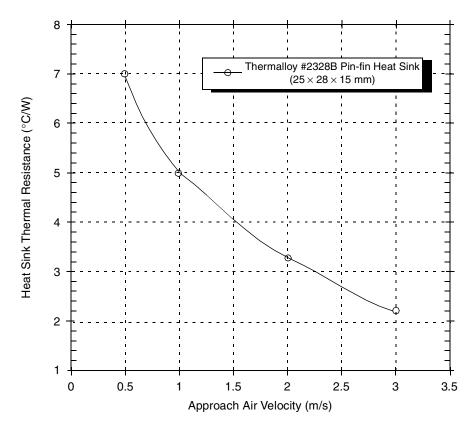

Figure 55. Thermalloy #2328B Heat Sink-to-Ambient Thermal Resistance Versus Airflow Velocity

### 16.2.4.2 Case 2

Every system application has different conditions that the thermal management solution must solve. As an alternate example, assume that the air reaching the component is 85 °C with an approach velocity of 1 m/sec. For a maximum junction temperature of 105 °C at 7 W, the total thermal resistance of junction to case thermal resistance plus thermal interface material plus heat sink thermal resistance must be less than 2.8 °C/W. The value of the junction to case thermal resistance in Table 60 includes the thermal interface resistance of a thin layer of thermal grease as documented in footnote 4 of the table. Assuming that the heat sink is flat enough to allow a thin layer of grease or phase change material, then the heat sink must be less than 2 °C/W.

Millennium Electronics (MEI) has tooled a heat sink MTHERM-1051 for this requirement assuming a compactPCI environment at 1 m/sec and a heat sink height of 12 mm. The MEI solution is illustrated in Figure 56 and Figure 57. This design has several significant advantages:

- The heat sink is clipped to a plastic frame attached to the application board with screws or plastic inserts at the corners away from the primary signal routing areas.

- The heat sink clip is designed to apply the force holding the heat sink in place directly above the die at a maximum force of less than 10 lbs.

- For applications with significant vibration requirements, silicone damping material can be applied between the heat sink and plastic frame.

# **17.6 Configuration Pin Muxing**

The MPC8560 provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately  $20 \text{ k}\Omega$ . This value should permit the  $4.7\text{-k}\Omega$  resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform/system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# **17.7 Pull-Up Resistor Requirements**

The MPC8560 requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including EPIC interrupt pins. I<sup>2</sup>C open drain type pins should be pulled up with ~1 k $\Omega$  resistors.

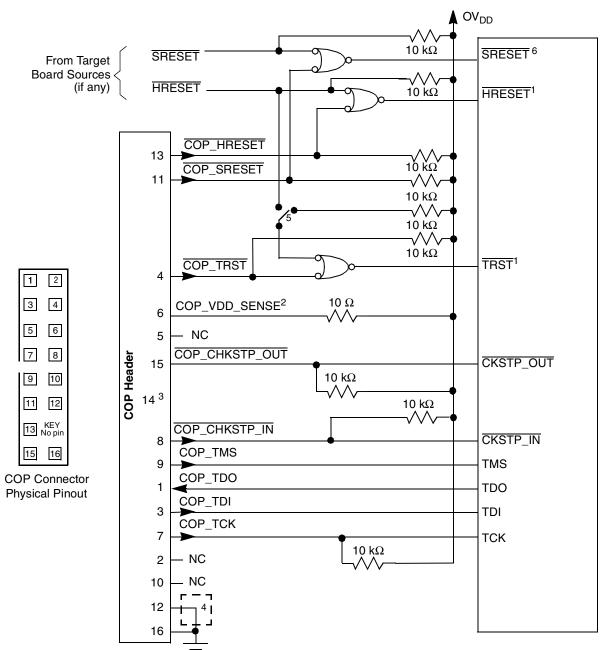

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 61. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

TSEC1\_TXD[3:0] must not be pulled low during reset. Some PHY chips have internal pulldowns that could cause this to happen. If such PHY chips are used, then a pullup must be placed on these signals strong enough to restore these signals to a logical 1 during reset.

Three test pins also require pull-up resistors (100  $\Omega$  - 1 k $\Omega$ ). These pins are L1\_TSTCLK, L2\_TSTCLK, and <u>LSSD\_MODE</u>. These signals are for factory use only and must be pulled up to OVDD for normal machine operation.

Refer to the PCI 2.2 specification for all pull-ups required for PCI.

#### System Design Information

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

#### Figure 61. JTAG Interface Connection

| Rev. No. | Substantive Change(s)                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0      | Section 1.1—Updated features list to coincide with latest version of the reference manual                                                                    |

|          | Table 1 and Table 2— Addition of CPM to $OV_{DD}$ and $OV_{IN}$ ; Addition of SYSCLK to $OV_{IN}$                                                            |

|          | Table 2—Addition of notes 1 and 2                                                                                                                            |

|          | Table 3—Addition of note 1                                                                                                                                   |

|          | Table 5—New                                                                                                                                                  |

|          | Section 4—New                                                                                                                                                |

|          | Table 13—Addition of IVREF                                                                                                                                   |

|          | Table 15—Modified maximum values for t <sub>DISKEW</sub>                                                                                                     |

|          | Table 16—Added MSYNC_OUT to t <sub>MCKSKEW2</sub>                                                                                                            |

|          | Figure 5—New                                                                                                                                                 |

|          | Section 6.2.1—Removed Figure 4, "DDR SDRAM Input Timing Diagram"                                                                                             |

|          | Section 7.1—Removed references to 2.5 V from first paragraph                                                                                                 |

|          | Figure 8—New                                                                                                                                                 |

|          | Table 19 and Table 20—Modified "conditions" for I <sub>IH</sub> and I <sub>IL</sub>                                                                          |

|          | Table 21—Addition of min and max for GTX_CLK125 reference clock duty cycle                                                                                   |

|          | Table 25—Addition of min and max for GTX_CLK125 reference clock duty cycle                                                                                   |

|          | Table 27—Addition of min and max for GTX_CLK125 reference clock duty cycle                                                                                   |

|          | Figure 17 and Figure 19—Changed LSYNC_IN to Internal clock at top of each figure                                                                             |

|          | Table 34—Modified values for t <sub>FIIVKH</sub> , t <sub>NIIVKH</sub> , and t <sub>TDIVKH</sub> ; addition of t <sub>PIIVKH</sub> and t <sub>PIIXKH</sub> . |

|          | Table 35—Modified values for t <sub>FEKHOX</sub> , t <sub>NIKHOX</sub> , t <sub>NEKHOX</sub> , t <sub>TDKHOX</sub> ; addition of t <sub>PIKHOX</sub> .       |

|          | Figure 16—New                                                                                                                                                |

|          | Figure 30—New                                                                                                                                                |

|          | Figure 16—New                                                                                                                                                |

|          | Figure 16—New                                                                                                                                                |

|          | Table 31—Removed row for t <sub>LBKHOX3</sub>                                                                                                                |

|          | Table 44—New (AC timing of PCI-X at 66 MHz)                                                                                                                  |

|          | Table 54—Addition of note 19                                                                                                                                 |

|          | Figure 61—Addition of jumper and note at top of diagram                                                                                                      |

|          | Table 56—Changed max bus freq for 667 core to 166                                                                                                            |

|          | Section 16.2.1—Modified first paragraph                                                                                                                      |

|          | Figure 52—Modified                                                                                                                                           |

|          | Figure 53—New                                                                                                                                                |

|          | Table 60—Modified thermal resistance data                                                                                                                    |

|          | Section 16.2.4.2—Modified first and second paragraphs                                                                                                        |

### Table 62. Document Revision History (continued)