# E·XFL

### NXP USA Inc. - MPC8560CPX667JB Datasheet

#### Welcome to E-XFL.COM

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 667MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                     |

| RAM Controllers                 | DDR, SDRAM                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers |                                                                         |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | - ·                                                                     |

| USB                             |                                                                         |

| Voltage - I/O                   | 2.5V, 3.3V                                                              |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 783-BFBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8560cpx667jb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **3 Power Characteristics**

The estimated power dissipation on the V<sub>DD</sub> supply for the MPC8560 is shown in Table 4.

| CCB Frequency (MHz) | Core Frequency (MHz) | Typical Power <sup>3,4</sup> | Maximum Power <sup>5</sup> | Unit |

|---------------------|----------------------|------------------------------|----------------------------|------|

| 200                 | 400                  | 5.1                          | 7.7                        | W    |

|                     | 500                  | 5.4                          | 8.0                        |      |

|                     | 600                  | 5.8                          | 8.4                        |      |

| 267                 | 533                  | 6.0                          | 8.7                        | W    |

|                     | 667                  | 6.4                          | 9.2                        |      |

|                     | 800                  | 6.9                          | 10.7                       |      |

| 333                 | 667                  | 6.8                          | 9.8                        | W    |

|                     | 833                  | 7.4                          | 11.4                       |      |

|                     | 1000 <sup>6</sup>    | 11.9                         | 16.5                       |      |

### Table 4. MPC8560 V<sub>DD</sub> Power Dissipation <sup>1,2</sup>

### Notes:

1. The values do not include I/O supply power (OV\_DD, LV\_DD, GV\_DD) or AV\_DD.

- 2. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, air flow, power dissipation of other components on the board, and board thermal resistance. Any customer design must take these considerations into account to ensure the maximum 105 °C junction temperature is not exceeded on this device.

- 3. Typical Power is based on a nominal voltage of  $V_{DD}$  = 1.2 V, a nominal process, a junction temperature of T<sub>i</sub> = 105 °C, and a Dhrystone 2.1 benchmark application.

- 4. Thermal solutions will likely need to design to a number higher than Typical Power based on the end application, T<sub>A</sub> target, and I/O power.

- 5. Maximum power is based on a nominal voltage of  $V_{DD}$  = 1.2 V, worst case process, a junction temperature of T<sub>i</sub> = 105 °C, and an artificial smoke test.

- 6. The nominal recommended  $V_{DD}$  is 1.3 V for this speed grade.

The estimated power dissipation on the  $AV_{DD}$  supplies for the MPC8560 PLLs is shown in Table 5.

| AV <sub>DD</sub> n | Typical <sup>1</sup> | Unit |

|--------------------|----------------------|------|

| AV <sub>DD</sub> 1 | 0.007                | W    |

| AV <sub>DD</sub> 2 | 0.014                | W    |

| AV <sub>DD</sub> 3 | 0.004                | W    |

### Table 5. MPC8560 AV<sub>DD</sub> Power Dissipation

Notes:

1.  $V_{DD}$  = 1.2 V(1.3 V for 1.0 GHz device),  $T_{J}$  = 105°C

### DDR SDRAM

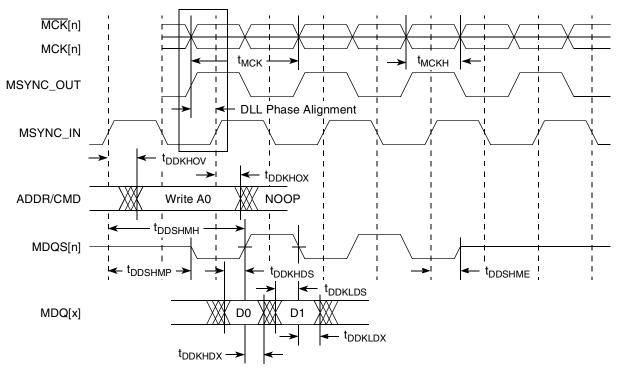

Figure 6 shows the DDR SDRAM output timing diagram.

Figure 6. DDR SDRAM Output Timing Diagram

### 6.2.2.2 Load Effects on Address/Command Bus

Table 18 provides approximate delay information that can be expected for the address and command signals of the DDR controller for various loadings. These numbers are the result of simulations for one topology. The delay numbers will strongly depend on the topology used. These delay numbers show the total delay for the address and command to arrive at the DRAM devices. The actual delay could be different than the delays seen in simulation, depending on the system topology. If a heavily loaded system is used, the DLL loop may need to be adjusted to meet setup requirements at the DRAM.

| Load                                               | Delay | Unit |

|----------------------------------------------------|-------|------|

| 4 devices (12 pF)                                  | 3.0   | ns   |

| 9 devices (27 pF)                                  | 3.6   | ns   |

| 36 devices (108 pF) + 40 pF compensation capacitor | 5.0   | ns   |

| 36 devices (108 pF) + 80 pF compensation capacitor | 5.2   | ns   |

| Table 18. Expected Delays for Address/Command |

|-----------------------------------------------|

|-----------------------------------------------|

## 7 Ethernet: Three-Speed, MII Management

This section provides the AC and DC electrical characteristics for three-speed and MII management.

## 7.1 Three-Speed Ethernet Controller (TSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all GMII (gigabit media independent interface), MII (media independent interface), TBI (ten-bit interface), RGMII (reduced gigabit media independent interface), and RTBI (reduced ten-bit interface) signals except MDIO (management data input/output) and MDC (management data clock). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII, MII, and TBI interfaces can be operated at 3.3 or 2.5 V. Whether the GMII, MII, or TBI interface is operated at 3.3 or 2.5 V, the timing is compliant with the IEEE 802.3 standard. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 7.3, "Ethernet Management Interface Electrical Characteristics."

## 7.1.1 TSEC DC Electrical Characteristics

All GMII,MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 19 and Table 20. The potential applied to the input of a GMII,MII, TBI, RGMII, or RTBI receiver may exceed the potential of the receiver's power supply (i.e., a GMII driver powered from a 3.6 V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5 V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5 V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                      | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3 V                                           | LV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $LV_{DD} = Min, I_{OH} = -4.0 mA$ )      | V <sub>OH</sub>  | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (LV <sub>DD</sub> = Min, $I_{OL}$ = 4.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                             | V <sub>IH</sub>  | 1.70 | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage                                              | V <sub>IL</sub>  | -0.3 | 0.90                   | V    |

| Input high current ( $V_{IN}^{1} = LV_{DD}$ )                  | I <sub>IH</sub>  | —    | 40                     | μA   |

| Input low current (V <sub>IN</sub> <sup>1</sup> = GND)         | IIL              | -600 | —                      | μA   |

| Table 19 | GMII, MII, | and TBI DC | Electrical | Characteristics |

|----------|------------|------------|------------|-----------------|

|----------|------------|------------|------------|-----------------|

Note:

1. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

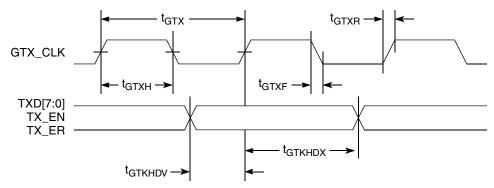

### Table 21. GMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%, or  $LV_{DD}$ =2.5V ± 5%.

| Parameter/Condition                   | Symbol <sup>1</sup>                                  | Min | Тур | Мах | Unit |

|---------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| GTX_CLK data clock rise and fall time | t <sub>GTXR</sub> , t <sub>GTXF</sub> <sup>2,4</sup> | _   |     | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by characterization.

4.Guaranteed by design.

### Figure 7 shows the GMII transmit AC timing diagram.

Figure 7. GMII Transmit AC Timing Diagram

### 7.2.1.2 GMII Receive AC Timing Specifications

Table 22 provides the GMII receive AC timing specifications.

### Table 22. GMII Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%, or LV<sub>DD</sub>=2.5V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   |     | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.5 |     |     | ns   |

### 7.2.4 RGMII and RTBI AC Timing Specifications

Table 27 presents the RGMII and RTBI AC timing specifications.

### Table 27. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>                                  | Min  | Тур | Мах  | Unit |

|-----------------------------------------------------|------------------------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub> 5                                 | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>                                   | 1.0  | —   | 2.8  | ns   |

| Clock period <sup>3</sup>                           | t <sub>RGT</sub> <sup>6</sup>                        | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub> <sup>6</sup>     | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> <sup>6</sup>     | 40   | 50  | 60   | %    |

| Rise and fall time                                  | t <sub>RGTR</sub> , t <sub>RGTF</sub> <sup>6,7</sup> | —    | —   | 0.75 | ns   |

Notes:

1.Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

2. The RGMII specification requires that PC board designer add 1.5 ns or greater in trace delay to the RX\_CLK in order to meet this specification. However, as stated above, this device will function with only 1.0 ns of delay.

3.For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

4.Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5.Guaranteed by characterization.

6.Guaranteed by design.

7.Signal timings are measured at 0.5 V and 2.0 V voltage levels.

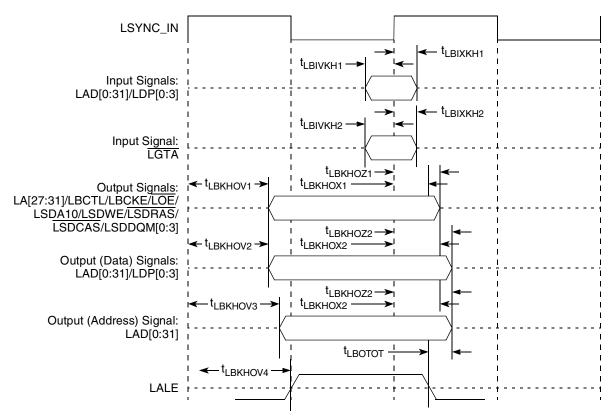

| Parameter                                                             | POR Configuration                | Symbol <sup>1</sup>  | Min | Max | Unit | Notes   |  |

|-----------------------------------------------------------------------|----------------------------------|----------------------|-----|-----|------|---------|--|

| Input setup to local bus clock (except LUPWAIT)                       | _                                | t <sub>LBIVKH1</sub> | 1.8 |     | ns   | 4, 5, 8 |  |

| LUPWAIT input setup to local bus clock                                | —                                | t <sub>LBIVKH2</sub> | 1.7 | —   | ns   | 4, 5    |  |

| Input hold from local bus clock (except<br>LUPWAIT)                   | _                                | t <sub>LBIXKH1</sub> | 0.5 | _   | ns   | 4, 5, 8 |  |

| LUPWAIT input hold from local bus clock                               | —                                | t <sub>LBIXKH2</sub> | 1.0 | —   | ns   | 4, 5    |  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | _                                | t <sub>lbotot</sub>  | 1.5 | —   | ns   | 6       |  |

| Local bus clock to output valid (except                               | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOV1</sub> |     | 2.0 | ns   | 4, 8    |  |

| LAD/LDP and LALE)                                                     | TSEC2_TXD[6:5] = 11<br>(default) |                      |     | 3.5 |      |         |  |

| Local bus clock to data valid for LAD/LDP                             | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOV2</sub> | _   | 2.2 | ns   | 4, 8    |  |

|                                                                       | TSEC2_TXD[6:5] = 11<br>(default) |                      |     | 3.7 |      |         |  |

| Local bus clock to address valid for LAD                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOV3</sub> |     | 2.3 | ns   | 4, 8    |  |

|                                                                       | TSEC2_TXD[6:5] = 11<br>(default) |                      |     | 3.8 |      |         |  |

| Local bus clock to LALE assertion                                     |                                  | t <sub>LBKHOV4</sub> | _   | 2.3 | ns   | 4, 8    |  |

| Output hold from local bus clock (except                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOX1</sub> | 0.7 | —   | ns   | 4, 8    |  |

| LAD/LDP and LALE)                                                     | TSEC2_TXD[6:5] = 11<br>(default) |                      | 1.6 |     |      |         |  |

| Output hold from local bus clock for                                  | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOX2</sub> | 0.7 | —   | ns   | 4, 8    |  |

| LAD/LDP                                                               | TSEC2_TXD[6:5] = 11<br>(default) |                      | 1.6 |     |      |         |  |

| Local bus clock to output high Impedance                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOZ1</sub> |     | 2.5 | ns   | 7, 9    |  |

| (except LAD/LDP and LALE)                                             | TSEC2_TXD[6:5] = 11<br>(default) |                      |     | 3.8 |      |         |  |

### Table 31. Local Bus General Timing Parameters—DLL Enabled (continued)

### Local Bus

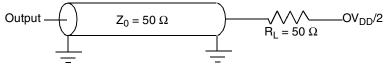

Figure 16 provides the AC test load for the local bus.

Figure 16. Local Bus AC Test Load

Figure 17 through Figure 22 show the local bus signals.

Figure 17. Local Bus Signals, Nonspecial Signals Only (DLL Enabled)

## 10 JTAG

JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8560.

Table 39 provides the JTAG AC timing specifications as defined in Figure 32 through Figure 35.

### Table 39. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | _     |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       |          | ns   |       |

| JTAG external clock pulse width measured at 1.4 V                          | t <sub>JTKHKL</sub>                        | 15       |          | ns   |       |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | 6     |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       |          | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 |          | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | <sup>t</sup> jtkldx<br>t <sub>jtklox</sub> |          | —        | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | <sup>t</sup> jtkldz<br><sup>t</sup> jtkloz | 3<br>3   | 19<br>9  | ns   | 5, 6  |

### Notes:

2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example,  $t_{JTDVKH}$  symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the  $t_{JTG}$  clock reference (K) going to the high (H) state or setup time. Also,  $t_{JTDXKH}$  symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the  $t_{JTG}$  clock reference (K) going to the high (H) state or setup time. Also,  $t_{JTDXKH}$  symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the  $t_{JTG}$  clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4.Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

5.Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

6.Guaranteed by design.

<sup>1.</sup>All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50- $\Omega$  load (see Figure 31). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

| Table 45. | PCI-X AC | Timing | Specifications | at 133 | MHz (contin | ued) |

|-----------|----------|--------|----------------|--------|-------------|------|

|-----------|----------|--------|----------------|--------|-------------|------|

| Parameter                                        | Symbol              | Min | Мах | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1.See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3.Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4.For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6.Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7.A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

- 9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the *PCI-X* 1.0a *Specification.*

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

- 12.Guaranteed by design.

## 13 RapidIO

This section describes the DC and AC electrical specifications for the RapidIO interface of the MPC8560.

## **13.1 RapidIO DC Electrical Characteristics**

RapidIO driver and receiver DC electrical characteristics are provided in Table 46 and Table 47, respectively.

### Table 46. RapidIO 8/16 LP-LVDS Driver DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V ± 5%.

| Characteristic                   | Symbol            | Min   | Мах   | Unit | Notes |

|----------------------------------|-------------------|-------|-------|------|-------|

| Differential output high voltage | V <sub>OHD</sub>  | 247   | 454   | mV   | 1, 2  |

| Differential output low voltage  | V <sub>OLD</sub>  | -454  | -247  | mV   | 1, 2  |

| Differential offset voltage      | $\Delta V_{OSD}$  | -     | 50    | mV   | 1,3   |

| Output high common mode voltage  | V <sub>OHCM</sub> | 1.125 | 1.375 | V    | 1, 4  |

| Output low common mode voltage   | V <sub>OLCM</sub> | 1.125 | 1.375 | V    | 1, 5  |

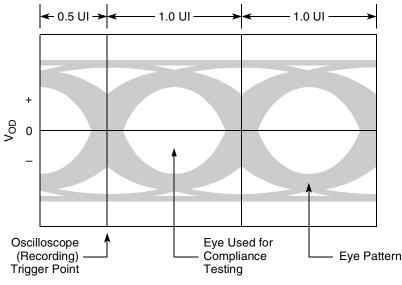

The eye pattern for a data signal is generated by making a large number of recordings of the signal and then overlaying the recordings. The number of recordings used to generate the eye shall be large enough that further increasing the number of recordings used does not cause the resulting eye pattern to change from one that complies with the RapidIO transmit mask to one that does not. Each data signal in the interface shall be carrying random or pseudo-random data when the recordings are made. If pseudo-random data is used, the length of the pseudo-random sequence (repeat length) shall be long enough that increasing the length of the sequence does not cause the resulting eye pattern to change from one that complies with the RapidIO transmit mask to one that does not comply with the mask. The data carried by any given data signal in the interface may not be correlated with the data carried by any other data signal in the interface. The zero-crossings of the clock associated with a data signal shall be used as the timing reference for aligning the multiple recordings of the data signal when the recordings are overlaid.

While the method used to make the recordings and overlay them to form the eye pattern is not specified, the method used shall be demonstrably equivalent to the following method. The signal under test is repeatedly recorded with a digital oscilloscope in infinite persistence mode. Each recording is triggered by a zero-crossing of the clock associated with the data signal under test. Roughly half of the recordings are triggered by positive-going clock zero-crossings and roughly half are triggered by negative-going clock zero-crossings. Each recording is at least 1.9 UI in length (to ensure that at least one complete eye is formed) and begins 0.5 UI before the trigger point (0.5 UI before the associated clock zero-crossing). Depending on the length of the individual recordings used to generate the eye pattern, one or more complete eyes will be formed. Regardless of the number of eyes, the eye whose center is immediately to the right of the trigger point is the eye used for compliance testing.

An example of an eye pattern generated using the above method with recordings 3 UI in length is shown in Figure 45. In this example, there is no skew between the signal under test and the associated clock used to trigger the recordings. If skew was present, the eye pattern would be shifted to the left or right relative to the oscilloscope trigger point.

Figure 45. Example Driver Output Eye Pattern

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

- 7. The socket lid must always be oriented to A1.

## **14.3 Pinout Listings**

Table 54 provides the pin-out listing for the MPC8560, 783 FC-PBGA package.

### Table 54. MPC8560 Pinout Listing

| Signal        | Signal Package Pin Number                                                                                                                                                                                                                                                                                                                                                               |     | Power<br>Supply  | Notes |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------|

|               | PCI/PCI-X                                                                                                                                                                                                                                                                                                                                                                               |     |                  |       |

| PCI_AD[63:0]  | AA14, AB14, AC14, AD14, AE14, AF14, AG14, AH14,<br>V15, W15, Y15, AA15, AB15, AC15, AD15, AG15,<br>AH15, V16, W16, AB16, AC16, AD16, AE16, AF16,<br>V17, W17, Y17, AA17, AB17, AE17, AF17, AF18, AH6,<br>AD7, AE7, AH7, AB8, AC8, AF8, AG8, AD9, AE9, AF9,<br>AG9, AH9, W10, Y10, AA10, AE11, AF11, AG11,<br>AH11, V12, W12, Y12, AB12, AD12, AE12, AG12,<br>AH12, V13, Y13, AB13, AC13 | I/O | OV <sub>DD</sub> | 17    |

| PCI_C_BE[7:0] | AG13, AH13, V14, W14, AH8, AB10, AD11, AC12                                                                                                                                                                                                                                                                                                                                             | I/O | OV <sub>DD</sub> | 17    |

| PCI_PAR       | AA11                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | —     |

| PCI_PAR64     | Y14                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> | _     |

| PCI_FRAME     | AC10                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2     |

| PCI_TRDY      | AG10                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2     |

| PCI_IRDY      | AD10                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2     |

| PCI_STOP      | V11                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> | 2     |

| PCI_DEVSEL    | AH10                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2     |

| PCI_IDSEL     | AA9                                                                                                                                                                                                                                                                                                                                                                                     | I   | OV <sub>DD</sub> | —     |

| PCI_REQ64     | AE13                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 5, 10 |

| PCI_ACK64     | AD13                                                                                                                                                                                                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2     |

| PCI_PERR      | W11                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> | 2     |

| PCI_SERR      | Y11                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> | 2, 4  |

| PCI_REQ0      | AF5                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> | —     |

| PCI_REQ[1:4]  | AF3, AE4, AG4, AE5                                                                                                                                                                                                                                                                                                                                                                      | I   | OV <sub>DD</sub> |       |

| PCI_GNT[0]    | AE6                                                                                                                                                                                                                                                                                                                                                                                     | I/O | OV <sub>DD</sub> |       |

| PCI_GNT[1:4]  | AG5, AH5, AF6, AG6                                                                                                                                                                                                                                                                                                                                                                      | 0   | OV <sub>DD</sub> | 5, 9  |

Package and Pin Listings

| Signal         | Signal Package Pin Number                                                                                                                                                                                                                                                                                                                        |     | Power<br>Supply     | Notes |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-------|

|                | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                                                       |     |                     |       |

| MDQ[0:63]      | M26, L27, L22, K24, M24, M23, K27, K26, K22, J28,<br>F26, E27, J26, J23, H26, G26, C26, E25, C24, E23,<br>D26, C25, A24, D23, B23, F22, J21, G21, G22, D22,<br>H21, E21, N18, J18, D18, L17, M18, L18, C18, A18,<br>K17, K16, C16, B16, G17, L16, A16, L15, G15, E15,<br>C14, K13, C15, D15, E14, D14, D13, E13, D12, A11,<br>F13, H13, A13, B12 | I/O | GV <sub>DD</sub>    |       |

| MECC[0:7]      | N20, M20, L19, E19, C21, A21, G19, A19                                                                                                                                                                                                                                                                                                           | I/O | ${\sf GV}_{\sf DD}$ | _     |

| MDM[0:8]       | L24, H28, F24, L21, E18, E16, G14, B13, M19                                                                                                                                                                                                                                                                                                      | 0   | $GV_DD$             | _     |

| MDQS[0:8]      | L26, J25, D25, A22, H18, F16, F14, C13, C20                                                                                                                                                                                                                                                                                                      | I/O | GV <sub>DD</sub>    | _     |

| MBA[0:1]       | B18, B19                                                                                                                                                                                                                                                                                                                                         | 0   | GV <sub>DD</sub>    | _     |

| MA[0:14]       | N19, B21, F21, K21, M21, C23, A23, B24, H23, G24,<br>K19, B25, D27, J14, J13                                                                                                                                                                                                                                                                     | 0   | GV <sub>DD</sub>    | _     |

| MWE            | D17                                                                                                                                                                                                                                                                                                                                              | 0   | GV <sub>DD</sub>    |       |

| MRAS           | F17                                                                                                                                                                                                                                                                                                                                              | 0   | GV <sub>DD</sub>    |       |

| MCAS           | J16                                                                                                                                                                                                                                                                                                                                              | 0   | GV <sub>DD</sub>    |       |

| MCS[0:3]       | H16, G16, J15, H15                                                                                                                                                                                                                                                                                                                               | 0   | GV <sub>DD</sub>    | _     |

| MCKE[0:1]      | E26, E28                                                                                                                                                                                                                                                                                                                                         | 0   | GV <sub>DD</sub>    | 11    |

| MCK[0:5]       | J20, H25, A15, D20, F28, K14                                                                                                                                                                                                                                                                                                                     | 0   | GV <sub>DD</sub>    |       |

| MCK[0:5]       | F20, G27, B15, E20, F27, L14                                                                                                                                                                                                                                                                                                                     | 0   | GV <sub>DD</sub>    | _     |

| MSYNC_IN       | M28                                                                                                                                                                                                                                                                                                                                              | I   | GV <sub>DD</sub>    | _     |

| MSYNC_OUT      | N28                                                                                                                                                                                                                                                                                                                                              | 0   | GV <sub>DD</sub>    |       |

|                | Local Bus Controller Interface                                                                                                                                                                                                                                                                                                                   |     | l                   |       |

| LA[27]         | U18                                                                                                                                                                                                                                                                                                                                              | 0   | OV <sub>DD</sub>    | 5, 9  |

| LA[28:31]      | T18, T19, T20, T21                                                                                                                                                                                                                                                                                                                               | 0   | OV <sub>DD</sub>    | 7, 9  |

| LAD[0:31]      | AD26, AD27, AD28, AC26, AC27, AC28, AA22, AA23,<br>AA26, Y21, Y22, Y26, W20, W22, W26, V19, T22, R24,<br>R23, R22, R21, R18, P26, P25, P20, P19, P18, N22,<br>N23, N24, N25, N26                                                                                                                                                                 | I/O | OV <sub>DD</sub>    |       |

| LALE           | V21                                                                                                                                                                                                                                                                                                                                              | 0   | OV <sub>DD</sub>    | 8, 9  |

| LBCTL          | V20                                                                                                                                                                                                                                                                                                                                              | 0   | OV <sub>DD</sub>    | 9     |

| LCKE           | U23                                                                                                                                                                                                                                                                                                                                              | 0   | OV <sub>DD</sub>    | —     |

| LCLK[0:2]      | U27, U28, V18                                                                                                                                                                                                                                                                                                                                    | 0   | OV <sub>DD</sub>    | —     |

| LCS[0:4]       | Y27, Y28, W27, W28, R27                                                                                                                                                                                                                                                                                                                          | 0   | OV <sub>DD</sub>    | 18    |

| LCS5/DMA_DREQ2 | R28                                                                                                                                                                                                                                                                                                                                              | I/O | OV <sub>DD</sub>    | 1     |

Package and Pin Listings

| Signal         | Signal Package Pin Number                                                                                    |           | Power<br>Supply  | Notes |

|----------------|--------------------------------------------------------------------------------------------------------------|-----------|------------------|-------|

|                | Gigabit Reference Clock                                                                                      |           |                  |       |

| EC_GTX_CLK125  | E2                                                                                                           | I         | LV <sub>DD</sub> |       |

|                | Three-Speed Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet) | hernet 1) |                  |       |

| TSEC1_TXD[7:4] | A6, F7, D7, C7                                                                                               | 0         | LV <sub>DD</sub> | 5, 9  |

| TSEC1_TXD[3:0] | B7, A7, G8, E8                                                                                               | 0         | LV <sub>DD</sub> | 9, 19 |

| TSEC1_TX_EN    | C8                                                                                                           | 0         | LV <sub>DD</sub> | 11    |

| TSEC1_TX_ER    | B8                                                                                                           | 0         | LV <sub>DD</sub> | —     |

| TSEC1_TX_CLK   | C6                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_GTX_CLK  | B6                                                                                                           | 0         | LV <sub>DD</sub> | 18    |

| TSEC1_CRS      | C3                                                                                                           | I         | LV <sub>DD</sub> | _     |

| TSEC1_COL      | G7                                                                                                           | I         | LV <sub>DD</sub> | —     |

| TSEC1_RXD[7:0] | D4, B4, D3, D5, B5, A5, F6, E6                                                                               | I         | LV <sub>DD</sub> | —     |

| TSEC1_RX_DV    | D2                                                                                                           | I         | LV <sub>DD</sub> | —     |

| TSEC1_RX_ER    | E5                                                                                                           | I         | LV <sub>DD</sub> | —     |

| TSEC1_RX_CLK   | D6                                                                                                           | I         | LV <sub>DD</sub> | —     |

|                | Three-Speed Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet Controller (Gigabit Ethernet) | hernet 2) |                  |       |

| TSEC2_TXD[7:2] | B10, A10, J10, K11,J11, H11                                                                                  | 0         | LV <sub>DD</sub> | 5, 9  |

| TSEC2_TXD[1:0] | G11, E11                                                                                                     | 0         | LV <sub>DD</sub> |       |

| TSEC2_TX_EN    | B11                                                                                                          | 0         | LV <sub>DD</sub> | 11    |

| TSEC2_TX_ER    | D11                                                                                                          | 0         | LV <sub>DD</sub> |       |

| TSEC2_TX_CLK   | D10                                                                                                          | I         | LV <sub>DD</sub> |       |

| TSEC2_GTX_CLK  | C10                                                                                                          | 0         | LV <sub>DD</sub> | 18    |

| TSEC2_CRS      | D9                                                                                                           | I         | LV <sub>DD</sub> |       |

| TSEC2_COL      | F8                                                                                                           | I         | LV <sub>DD</sub> |       |

| TSEC2_RXD[7:0] | F9, E9, C9, B9, A9, H9, G10, F10                                                                             | I         | LV <sub>DD</sub> |       |

| TSEC2_RX_DV    | H8                                                                                                           |           | LV <sub>DD</sub> |       |

| TSEC2_RX_ER    | A8                                                                                                           |           | LV <sub>DD</sub> |       |

| TSEC2_RX_CLK   | E10                                                                                                          | I         | LV <sub>DD</sub> |       |

|                | RapidIO Interface                                                                                            | I         | 1                |       |

| RIO_RCLK       | Y25                                                                                                          | I         | OV <sub>DD</sub> |       |

| RIO_RCLK       | Y24                                                                                                          | I         | OV <sub>DD</sub> |       |

| Signal            | Package Pin Number                                                                                                                                                                                                        | Pin Type                                                                    | Power<br>Supply   | Notes |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|-------|

| LV <sub>DD</sub>  | A4, C5, E7, H10                                                                                                                                                                                                           | Reference Voltage;<br>Three-Speed<br>Ethernet I/O (2.5 V,<br>3.3 V)         | LV <sub>DD</sub>  | _     |

| MV <sub>REF</sub> | N27                                                                                                                                                                                                                       | Reference Voltage<br>Signal; DDR                                            | MV <sub>REF</sub> | -     |

| No Connects       | AH26, AH27, AH28, AG28, AF28, AE28,<br>AH1, AG1, AH2, B1, B2, A2, A3, AH25                                                                                                                                                | —                                                                           | -                 | 16    |

| OV <sub>DD</sub>  | D1, E4, H3, K4, K10, L7, M5, N3, P22, R19, R25, T2,<br>T7, U5, U20, U26, V8, W4, W13, W19, W21, Y7, Y23,<br>AA5, AA12, AA16, AA20, AB7, AB9, AB26, AC5, AC11,<br>AC17, AD4, AE1, AE8, AE10, AE15, AF7, AF12, AG27,<br>AH4 | PCI/PCI-X,<br>RapidIO, 10/100<br>Ethernet, and other<br>Standard<br>(3.3 V) | OV <sub>DD</sub>  | _     |

| RESERVED          | C1, T11, U11, AF1                                                                                                                                                                                                         | —                                                                           | —                 | 15    |

| SENSEVDD          | L12                                                                                                                                                                                                                       | Power for Core<br>(1.2 V)                                                   | V <sub>DD</sub>   | 13    |

| SENSEVSS          | K12                                                                                                                                                                                                                       | —                                                                           | —                 | 13    |

| V <sub>DD</sub>   | M13, M15, M17, N14, N16, P13, P15, P17, R12, R14,<br>R16, T13, T15, T17, U12, U14                                                                                                                                         | Power for Core<br>(1.2 V)                                                   | V <sub>DD</sub>   | -     |

|                   | СРМ                                                                                                                                                                                                                       |                                                                             |                   |       |

| PA[0:31]          | H1, H2, J1, J2, J3, J4, J5, J6, J7, J8, K8, K7, K6, K3,<br>K2, K1, L1, L2, L3, L4, L5, L8, L9, L10, L11, M10, M9,<br>M8, M7, M6, M3, M2                                                                                   | Ι/Ο                                                                         | OV <sub>DD</sub>  | _     |

| PB[4:31]          | M1, N1, N4, N5, N6, N7, N8, N9, N10, N11, P11, P10,<br>P9, P8, P7, P6, P5, P4, P3, P2, P1, R1, R2, R3, R4, R5,<br>R6, R7                                                                                                  | Ι/Ο                                                                         | OV <sub>DD</sub>  | _     |

| PC[0:31]          | R8, R9, R10, R11, T9, T6, T5, T4, T1, U1, U2, U3, U4,<br>U7, U8, U9, U10, V9, V6, V5, V4, V3, V2, V1, W1, W2,<br>W3, W6, W7, W8, W9, Y9                                                                                   | Ι/Ο                                                                         | OV <sub>DD</sub>  | _     |

### Table 54. MPC8560 Pinout Listing (continued)

## 15.2 Platform/System PLL Ratio

The platform clock is the clock that drives the L2 cache, the DDR SDRAM data rate, and the e500 core complex bus (CCB), and is also called the CCB clock. The values are determined by the binary value on LA[28:31] at power up, as shown in Table 57.

There is no default for this PLL ratio; these signals must be pulled to the desired values.

| Binary Value of LA[28:31] Signals | Ratio Description                      |

|-----------------------------------|----------------------------------------|

| 0000                              | 16:1 ratio CCB clock: SYSCLK (PCI bus) |

| 0001                              | Reserved                               |

| 0010                              | 2:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0011                              | 3:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0100                              | 4:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0101                              | 5:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0110                              | 6:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0111                              | Reserved                               |

| 1000                              | 8:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1001                              | 9:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1010                              | 10:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1011                              | Reserved                               |

| 1100                              | 12:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1101                              | Reserved                               |

| 1110                              | Reserved                               |

| 1111                              | Reserved                               |

### Table 57. CCB Clock Ratio

## 15.3 e500 Core PLL Ratio

Table 58 describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LALE and LGPL2 at power up, as shown in Table 58.

| Table \$ | 58. | e500 | Core | to | ССВ | Ratio |

|----------|-----|------|------|----|-----|-------|

|----------|-----|------|------|----|-----|-------|

| Binary Value of LALE, LGPL2 Signals | Ratio Description |

|-------------------------------------|-------------------|

| 00                                  | 2:1 e500 core:CCB |

| 01                                  | 5:2 e500 core:CCB |

| 10                                  | 3:1 e500 core:CCB |

| 11                                  | 7:2 e500 core:CCB |

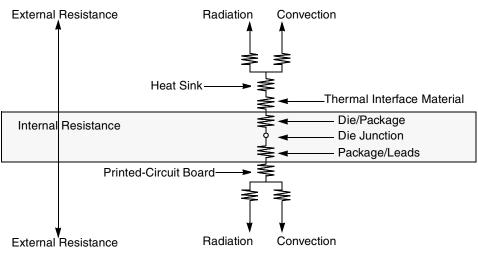

### Thermal

Figure 53 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

(Note the internal versus external package resistance)

### Figure 53. Package with Heat Sink Mounted to a Printed-Circuit Board

The heat sink removes most of the heat from the device. Heat generated on the active side of the chip is conducted through the silicon and through the lid, then through the heat sink attach material (or thermal interface material), and finally to the heat sink. The junction-to-case thermal resistance is low enough that the heat sink attach material and heat sink thermal resistance are the dominant terms.

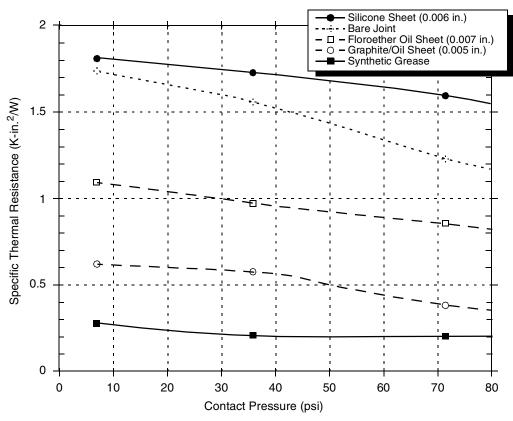

### **16.2.3 Thermal Interface Materials**

A thermal interface material is required at the package-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 54 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. The bare joint results in a thermal resistance approximately six times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 51). Therefore, the synthetic grease offers the best thermal performance, especially at the low interface pressure.

When removing the heat sink for re-work, it is preferable to slide the heat sink off slowly until the thermal interface material loses its grip. If the support fixture around the package prevents sliding off the heat sink, the heat sink should be slowly removed. Heating the heat sink to 40-50°C with an air gun can soften the interface material and make the removal easier. The use of an adhesive for heat sink attach is not recommended.

The system board designer can choose between several types of thermal interface. There are several commercially-available thermal interfaces provided by the following vendors:

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                                      | 781-935-4850 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                                | 888-642-7674 |

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                        | 800-347-4572 |

| Rev. No. | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2      | Section 1.1.1—Updated feature list.<br>Section 1.2.1.1—Updated notes for Table 1.                                                                                                                                                                                                                                                                                           |

|          | Section 1.2.1.2—Removed 5-V PCI interface overshoot and undershoot figure.                                                                                                                                                                                                                                                                                                  |

|          | Section 1.2.1.3—Added this section to summarize impedance driver settings for various interfaces.                                                                                                                                                                                                                                                                           |

|          | Section 1.4—Updated rows in Reset Initialization timing specifications table. Added a table with DLL and PLL timing specifications.                                                                                                                                                                                                                                         |

|          | Section 1.5.2.2—Updated note 6 of DDR SDRAM Output AC Timing Specifications table.                                                                                                                                                                                                                                                                                          |

|          | Section 1.7—Changed the minimum input low current from -600 to -15 $\mu A$ for the RGMII DC electrical characteristics.                                                                                                                                                                                                                                                     |

|          | Section 1.7.2—Changed LCS[3:4] to TSEC1_TXD[6:5]. Updated notes regarding LCS[3:4].                                                                                                                                                                                                                                                                                         |

|          | Section 1.13.2—Updated the mechanical dimensions diagram for the package.                                                                                                                                                                                                                                                                                                   |

|          | Section 1.13.3—Updated the notes for LBCTL, TRIG_OUT, and ASLEEP. Corrected pin assignments for IIC_SDA and IIC_SCL. Corrected reserved pin assignment of V11 to U11. V11 is actually PCI_STOP. Section 1.14.1—Updated the table for frequency options with respect to platform/CCB frequencies. Section 1.14.4—Edited Frequency options with respect to memory bus speeds. |

|          |                                                                                                                                                                                                                                                                                                                                                                             |

| 1.1      | Made updates throughout document.                                                                                                                                                                                                                                                                                                                                           |

|          | Section 1.6.1—Added symbols and note for the GTX_CLK125 timing parameters.                                                                                                                                                                                                                                                                                                  |

|          | Section 1.11.3—Updated pin list table: LGPL5/LSDAMUX to LGPL5, LA[27:29] and LA[30:31] to LA[27:31], TRST to TRST, added GBE Clocking section and EC_GTX_CLK125 signal.                                                                                                                                                                                                     |

|          | Figure 50—Updated pin 2 connection information.                                                                                                                                                                                                                                                                                                                             |

| 1        | Original Customer Version.                                                                                                                                                                                                                                                                                                                                                  |

## **19.2 Part Marking**

Parts are marked as the example shown in Figure 62.

### Notes:

MMMMM is the 5-digit mask number.

ATWLYYWWA is the traceability code.

CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States. YWWLAZ is the assembly traceability code.

### Figure 62. Part Marking for FC-PBGA Device

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. The described product is a PowerPC microprocessor. The PowerPC mare is a trademark of IBM Corp. and is used under license. IEEE 802.3, 802.1, and 1149.1 are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Document Number: MPC8560EC Rev. 4.2 1/2008