# E·XFL

### NXP USA Inc. - MPC8560CVT667JB Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 667MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                     |

| RAM Controllers                 | DDR, SDRAM                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 2.5V, 3.3V                                                              |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 783-BFBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8560cvt667jb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- General-purpose parallel ports—16 parallel I/O lines with interrupt capability

- Supports inverse muxing of ATM cells (IMA)

- 256 Kbyte L2 cache/SRAM

- Can be configured as follows

- Full cache mode (256-Kbyte cache).

- Full memory-mapped SRAM mode (256-Kbyte SRAM mapped as a single 256-Kbyte block or two 128-Kbyte blocks)

- Half SRAM and half cache mode (128-Kbyte cache and 128-Kbyte memory-mapped SRAM)

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing)

- Eight-way set-associative cache organization (1024 sets of 32-byte cache lines)

- Supports locking the entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions

- Global locking and flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be flash cleared separately

- Read and write buffering for internal bus accesses

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global)

- Regions can reside at any aligned location in the memory map

- Byte accessible ECC is protected using read-modify-write transactions accesses for smaller than cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 32-bit address space

- Inbound and outbound ATMUs map to larger external address spaces

- Three inbound windows plus a configuration window on PCI/PCI-X

- Four inbound windows plus a default and configuration window on RapidIO

- Four outbound windows plus default translation for PCI

- Eight outbound windows plus default translation for RapidIO

- DDR memory controller

- Programmable timing supporting DDR-1 SDRAM

- 64-bit data interface, up to 333-MHz data rate

- Four banks of memory supported, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbits to 1 Gbit with x8/x16 data ports

- Full ECC support

- Page mode support (up to 16 simultaneous open pages)

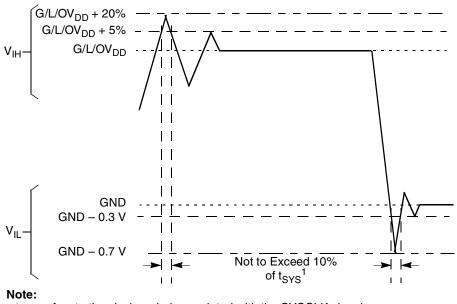

t<sub>SYS</sub> refers to the clock period associated with the SYSCLK signal.

#### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The MPC8560 core voltage must always be provided at nominal 1.2 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied  $MV_{REF}$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

# **3 Power Characteristics**

The estimated power dissipation on the V<sub>DD</sub> supply for the MPC8560 is shown in Table 4.

| CCB Frequency (MHz) | Core Frequency (MHz) | Typical Power <sup>3,4</sup> | Maximum Power <sup>5</sup> | Unit |

|---------------------|----------------------|------------------------------|----------------------------|------|

| 200                 | 400                  | 5.1                          | 7.7                        | W    |

|                     | 500                  | 5.4                          | 8.0                        |      |

|                     | 600                  | 5.8                          | 8.4                        |      |

| 267                 | 533                  | 6.0                          | 8.7                        | W    |

|                     | 667                  | 6.4                          | 9.2                        |      |

|                     | 800                  | 6.9                          | 10.7                       |      |

| 333                 | 667                  | 6.8                          | 9.8                        | W    |

|                     | 833                  | 7.4                          | 11.4                       |      |

|                     | 1000 <sup>6</sup>    | 11.9                         | 16.5                       |      |

### Table 4. MPC8560 V<sub>DD</sub> Power Dissipation <sup>1,2</sup>

#### Notes:

1. The values do not include I/O supply power (OV\_DD, LV\_DD, GV\_DD) or AV\_DD.

- 2. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, air flow, power dissipation of other components on the board, and board thermal resistance. Any customer design must take these considerations into account to ensure the maximum 105 °C junction temperature is not exceeded on this device.

- 3. Typical Power is based on a nominal voltage of  $V_{DD}$  = 1.2 V, a nominal process, a junction temperature of T<sub>i</sub> = 105 °C, and a Dhrystone 2.1 benchmark application.

- 4. Thermal solutions will likely need to design to a number higher than Typical Power based on the end application, T<sub>A</sub> target, and I/O power.

- 5. Maximum power is based on a nominal voltage of  $V_{DD}$  = 1.2 V, worst case process, a junction temperature of T<sub>i</sub> = 105 °C, and an artificial smoke test.

- 6. The nominal recommended  $V_{DD}$  is 1.3 V for this speed grade.

The estimated power dissipation on the  $AV_{DD}$  supplies for the MPC8560 PLLs is shown in Table 5.

| AV <sub>DD</sub> n | Typical <sup>1</sup> | Unit |

|--------------------|----------------------|------|

| AV <sub>DD</sub> 1 | 0.007                | W    |

| AV <sub>DD</sub> 2 | 0.014                | W    |

| AV <sub>DD</sub> 3 | 0.004                | W    |

#### Table 5. MPC8560 AV<sub>DD</sub> Power Dissipation

Notes:

1.  $V_{DD}$  = 1.2 V(1.3 V for 1.0 GHz device),  $T_{J}$  = 105°C

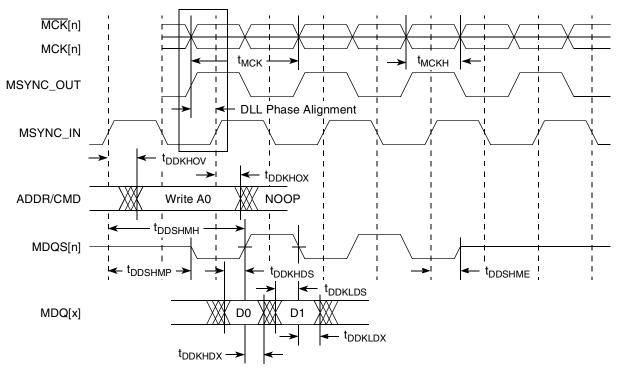

# 6.2.2 DDR SDRAM Output AC Timing Specifications

For chip selects  $\overline{\text{MCS1}}$  and  $\overline{\text{MCS2}}$ , there will always be at least 200 DDR memory clocks coming out of self-refresh after an  $\overline{\text{HRESET}}$  before a precharge occurs. This will not necessarily be the case for chip selects  $\overline{\text{MCS0}}$  and  $\overline{\text{MCS3}}$ .

# 6.2.2.1 DLL Enabled Mode

Table 16 and Table 17 provide the output AC timing specifications and measurement conditions for the DDR SDRAM interface with the DDR DLL enabled.

#### Table 16. DDR SDRAM Output AC Timing Specifications-DLL Mode

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                        | Мах                        | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|----------------------------|----------------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                        | t <sub>MCK</sub>                            | 6                          | 10                         | ns   | 2     |

| On chip Clock Skew                                                                 | t <sub>MCKSKEW</sub>                        | _                          | 150                        | ps   | 3, 8  |

| MCK[n] duty cycle                                                                  | t <sub>MCKH</sub> /t <sub>MCK</sub>         | 45                         | 55                         | %    | 8     |

| ADDR/CMD output valid                                                              | t <sub>DDKHOV</sub>                         | —                          | 3                          | ns   | 4, 9  |

| ADDR/CMD output invalid                                                            | t <sub>DDKHOX</sub>                         | 1                          | —                          | ns   | 4, 9  |

| Write CMD to first MDQS capture edge                                               | t <sub>DDSHMH</sub>                         | t <sub>MCK</sub> + 1.5     | t <sub>MCK</sub> + 4.0     | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz | t <sub>DDKHDS,</sub><br>t <sub>DDKLDS</sub> | 900<br>1100<br>1200        | _                          | ps   | 6, 9  |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>t</sup> ddkhdx,<br><sup>t</sup> ddkldx | 900<br>1100<br>1200        | —                          | ps   | 6, 9  |

| MDQS preamble start                                                                | t <sub>DDSHMP</sub>                         | $0.75 	imes t_{MCK} + 1.5$ | $0.75 	imes t_{MCK}$ + 4.0 | ns   | 7, 8  |

#### Table 16. DDR SDRAM Output AC Timing Specifications–DLL Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter         | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|-------------------|---------------------|-----|-----|------|-------|

| MDQS epilogue end | t <sub>DDSHME</sub> | 1.5 | 4.0 | ns   | 7, 8  |

#### Notes:

1.The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (OX or DX). For example, t<sub>DDKHOV</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (O) are valid (V) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.</sub>

2.All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3.Maximum possible clock skew between a clock MCK[n] and its relative inverse clock MCK[n], or between a clock MCK[n] and a relative clock MCK[m] or MSYNC\_OUT. Skew measured between complementary signals at GV<sub>DD</sub>/2.

4.ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK and MDQ/MECC/MDM/MDQS.

- 5.Note that t<sub>DDSHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDSHMH</sub> describes the DDR timing (DD) from the rising edge of the MSYNC\_IN clock (SH) until the MDQS signal is valid (MH). t<sub>DDSHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. These controls allow the relationship between the synchronous clock control timing and the source-synchronous DQS domain to be modified by the user. For best turnaround times, these may need to be set to delay t<sub>DDSHMH</sub> an additional 0.25t<sub>MCK</sub>. This will also affect t<sub>DDSHMP</sub> and t<sub>DDSHME</sub> accordingly. See the *MPC8560 PowerQUICC III Integrated Communications Processor Reference Manual* for a description and understanding of the timing modifications enabled by use of these bits.

- 6.Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8560.

- 7.All outputs are referenced to the rising edge of MSYNC\_IN (S) at the pins of the MPC8560. Note that t<sub>DDSHMP</sub> follows the symbol conventions described in note 1. For example, t<sub>DDSHMP</sub> describes the DDR timing (DD) from the rising edge of the MSYNC\_IN clock (SH) for the duration of the MDQS signal precharge period (MP).

8. Guaranteed by design.

9. Guaranteed by characterization.

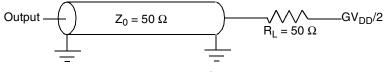

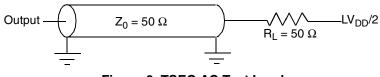

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

| Symbol           | DDR                        | Unit | Notes |

|------------------|----------------------------|------|-------|

| V <sub>TH</sub>  | MV <sub>REF</sub> ± 0.31 V | V    | 1     |

| V <sub>OUT</sub> | $0.5 	imes GV_{DD}$        | V    | 2     |

Notes:

1.Data input threshold measurement point.

2.Data output measurement point.

#### DDR SDRAM

Figure 6 shows the DDR SDRAM output timing diagram.

Figure 6. DDR SDRAM Output Timing Diagram

# 6.2.2.2 Load Effects on Address/Command Bus

Table 18 provides approximate delay information that can be expected for the address and command signals of the DDR controller for various loadings. These numbers are the result of simulations for one topology. The delay numbers will strongly depend on the topology used. These delay numbers show the total delay for the address and command to arrive at the DRAM devices. The actual delay could be different than the delays seen in simulation, depending on the system topology. If a heavily loaded system is used, the DLL loop may need to be adjusted to meet setup requirements at the DRAM.

| Load                                               | Delay | Unit |

|----------------------------------------------------|-------|------|

| 4 devices (12 pF)                                  | 3.0   | ns   |

| 9 devices (27 pF)                                  | 3.6   | ns   |

| 36 devices (108 pF) + 40 pF compensation capacitor | 5.0   | ns   |

| 36 devices (108 pF) + 80 pF compensation capacitor | 5.2   | ns   |

| Table 18. Expected Delays for Address/Command |

|-----------------------------------------------|

|-----------------------------------------------|

#### Table 22. GMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%, or LV<sub>DD</sub>=2.5V  $\pm$  5%.

| Parameter/Condition             | Symbol <sup>1</sup>                                  | Min | Тур | Max | Unit |

|---------------------------------|------------------------------------------------------|-----|-----|-----|------|

| RX_CLK clock rise and fall time | t <sub>GRXR</sub> , t <sub>GRXF</sub> <sup>2,3</sup> | _   |     | 1.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 8 provides the AC test load for TSEC.

Figure 8. TSEC AC Test Load

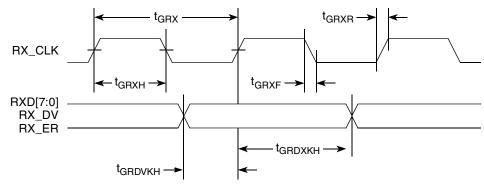

Figure 9 shows the GMII receive AC timing diagram.

Figure 9. GMII Receive AC Timing Diagram

# 7.2.3.2 TBI Receive AC Timing Specifications

Table 26 provides the TBI receive AC timing specifications.

#### Table 26. TBI Receive AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%, or LV<sub>DD</sub>=2.5V  $\pm$  5%.

| Parameter/Condition                  | Symbol <sup>1</sup>                                  | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------------------------------------|-----|------|-----|------|

| RX_CLK clock period                  | t <sub>TRX</sub>                                     |     | 16.0 |     | ns   |

| RX_CLK skew                          | t <sub>SKTRX</sub>                                   | 7.5 | _    | 8.5 | ns   |

| RX_CLK duty cycle                    | t <sub>TRXH</sub> /t <sub>TRX</sub>                  | 40  | _    | 60  | %    |

| RCG[9:0] setup time to rising RX_CLK | t <sub>TRDVKH</sub>                                  | 2.5 | —    | _   | ns   |

| RCG[9:0] hold time to rising RX_CLK  | t <sub>TRDXKH</sub>                                  | 1.5 | —    | _   | ns   |

| RX_CLK clock rise time and fall time | t <sub>TRXR</sub> , t <sub>TRXF</sub> <sup>2,3</sup> | 0.7 | _    | 2.4 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state)

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) relative to the t<sub>TRX</sub> clock reference (K) going to the high (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

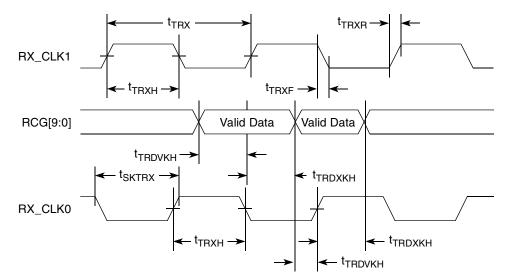

Figure 13 shows the TBI receive AC timing diagram.

Figure 13. TBI Receive AC Timing Diagram

#### Local Bus

| Parameter                                | POR Configuration                | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------|----------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOZ2</sub> | _   | 2.5 | ns   | 7, 9  |

| for LAD/LDP                              | TSEC2_TXD[6:5] = 11<br>(default) |                      |     | 3.8 |      |       |

Table 31. Local Bus General Timing Parameters—DLL Enabled (continued)

Notes:

1.The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.</sub></sub>

2.All timings are in reference to LSYNC\_IN for DLL enabled mode.

3.Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at OV<sub>DD</sub>/2.

4.All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN for DLL enabled to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

5.Input timings are measured at the pin.

- 6.The value of t<sub>LBOTOT</sub> is defined as the sum of 1/2 or 1 ccb\_clk cycle as programmed by LBCR[AHD], and the number of local bus buffer delays used as programmed at power-on reset with configuration pins TSEC2\_TXD[6:5].

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

8. Guaranteed by characterization.

9.Guaranteed by design.

Table 32 describes the general timing parameters of the local bus interface of the MPC8560 with the DLL bypassed.

Table 32. Local Bus General Timing Parameters—DLL Bypassed

| Parameter                                                             | POR Configuration                | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------------------|----------------------|------|------|------|-------|

| Local bus cycle time                                                  | _                                | t <sub>LBK</sub>     | 6.0  | —    | ns   | 2     |

| Internal launch/capture clock to LCLK delay                           | _                                | t <sub>lbkhkt</sub>  | 2.3  | 3.9  | ns   | 8     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | _                                | t <sub>LBKSKEW</sub> | _    | 150  | ps   | 3, 9  |

| Input setup to local bus clock (except LUPWAIT)                       | _                                | <sup>t</sup> LBIVKH1 | 5.7  | —    | ns   | 4, 5  |

| LUPWAIT input setup to local bus clock                                | _                                | t <sub>LBIVKH2</sub> | 5.6  | —    | ns   | 4, 5  |

| Input hold from local bus clock (except LUPWAIT)                      | _                                | t <sub>LBIXKH1</sub> | -1.8 | —    | ns   | 4, 5  |

| LUPWAIT input hold from local bus clock                               | _                                | t <sub>LBIXKH2</sub> | -1.3 | —    | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | _                                | t <sub>LBOTOT</sub>  | 1.5  | —    | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   | 4     |

|                                                                       | TSEC2_TXD[6:5] = 11<br>(default) |                      |      | 1.2  |      |       |

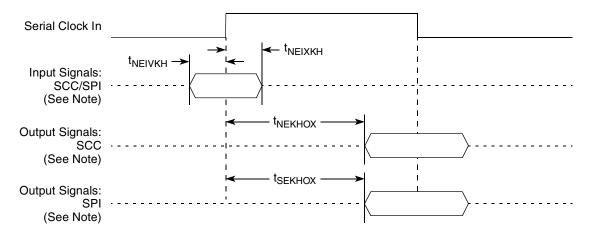

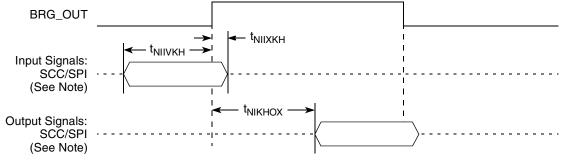

Figure 27 shows the SCC/SPI external clock.

Note: The clock edge is selectable on SCC and SPI.

#### Figure 27. SCC/SPI AC Timing External Clock Diagram

Note: The clock edge is selectable on SCC and SPI.

#### Figure 28. SCC/SPI AC Timing Internal Clock Diagram

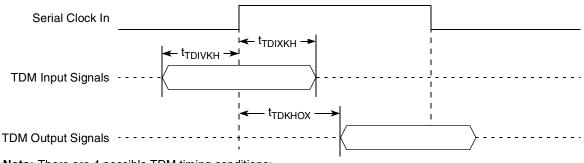

Figure 29 shows TDM input and output signals.

Note: There are 4 possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

#### Figure 29. TDM Signal AC Timing Diagram

# PCI/PCI-X

# **12.2 PCI/PCI-X AC Electrical Specifications**

This section describes the general AC timing parameters of the PCI/PCI-X bus of the MPC8560. Note that the SYSCLK signal is used as the PCI input clock. Table 43 provides the PCI AC timing specifications at 66 MHz.

| Parameter                               | Symbol <sup>1</sup> | Min                | Max | Unit   | Notes    |

|-----------------------------------------|---------------------|--------------------|-----|--------|----------|

| SYSCLK to output valid                  | <sup>t</sup> PCKHOV | _                  | 6.0 | ns     | 2        |

| Output hold from SYSCLK                 | t <sub>PCKHOX</sub> | 2.0                | _   | ns     | 2, 9     |

| SYSCLK to output high impedance         | t <sub>PCKHOZ</sub> |                    | 14  | ns     | 2, 3, 10 |

| Input setup to SYSCLK                   | t <sub>PCIVKH</sub> | 3.0                | _   | ns     | 2, 4, 9  |

| Input hold from SYSCLK                  | t <sub>PCIXKH</sub> | 0                  | _   | ns     | 2, 4, 9  |

| REQ64 to HRESET <sup>9</sup> setup time | t <sub>PCRVRH</sub> | $10 	imes t_{SYS}$ | _   | clocks | 5, 6, 10 |

| HRESET to REQ64 hold time               | t <sub>PCRHRX</sub> | 0                  | 50  | ns     | 6, 10    |

| HRESET high to first FRAME assertion    | t <sub>PCRHFV</sub> | 10                 | _   | clocks | 7, 10    |

#### Table 43. PCI AC Timing Specifications at 66 MHz

Notes:

1.Note that the symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional</sub>

block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI/PCI-X timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the SYSCLK clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI/PCI-X timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

2.See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

3.For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4.Input timings are measured at the pin.

- 5. The timing parameter t<sub>SYS</sub> indicates the minimum and maximum CLK cycle times for the various specified frequencies. The system clock period must be kept within the minimum and maximum defined ranges. For values see Section 15, "Clocking."

6.The setup and hold time is with respect to the rising edge of HRESET.

- 7. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI 2.2 Local Bus Specifications*.

- 8. The reset assertion timing requirement for  $\overline{\text{HRESET}}$  is 100 µs.

- 9. Guaranteed by characterization.

10.Guaranteed by design.

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes |

|---------------------------------------------------|---------------------|-----|-----|--------|-------|

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  | _   | clocks | 11    |

| HRESET to PCI-X initialization pattern hold time  | t <sub>PCRHIX</sub> | 0   | 50  | ns     | 6, 11 |

#### Table 44. PCI-X AC Timing Specifications at 66 MHz (continued)

Notes:

1.See the timing measurement conditions in the PCI-X 1.0a Specification.

2.Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

3.Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

4.For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6.Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7.A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8.Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification*. 10. Guaranteed by characterization.

11.Guaranteed by design.

#### Table 45 provides the PCI-X AC timing specifications at 133 MHz.

| Table 45. PCI-X AC TIMING Specifications at 133 MHz |                     |     |     |        |                  |

|-----------------------------------------------------|---------------------|-----|-----|--------|------------------|

| Parameter                                           | Symbol              | Min | Мах | Unit   | Notes            |

| SYSCLK to signal valid delay                        | <sup>t</sup> PCKHOV | _   | 3.8 | ns     | 1, 2, 3,<br>7, 8 |

| Output hold from SYSCLK                             | t <sub>PCKHOX</sub> | 0.7 | _   | ns     | 1, 11            |

| SYSCLK to output high impedance                     | t <sub>PCKHOZ</sub> | _   | 7   | ns     | 1, 4, 8,<br>12   |

| Input setup time to SYSCLK                          | t <sub>PCIVKH</sub> | 1.4 |     | ns     | 3, 5, 9,<br>11   |

| Input hold time from SYSCLK                         | t <sub>PCIXKH</sub> | 0.5 | _   | ns     | 11               |

| REQ64 to HRESET setup time                          | t <sub>PCRVRH</sub> | 10  | _   | clocks | 12               |

| HRESET to REQ64 hold time                           | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 12               |

| HRESET high to first FRAME assertion                | t <sub>PCRHFV</sub> | 10  | _   | clocks | 10, 12           |

| PCI-X initialization pattern to HRESET setup time   | <sup>t</sup> PCIVRH | 10  | —   | clocks | 12               |

### Table 45. PCI-X AC Timing Specifications at 133 MHz

RapidIO

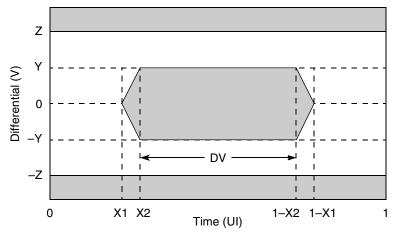

Figure 43. Example Compliance Mask

Y = minimum data valid amplitude

Z = maximum amplitude

1 UI = 1 unit interval = 1/baud rate

X1 = end of zero crossing region

X2 = beginning of data valid window

$DV = data valid window = 1 - 2 \times X2$

The waveform of the signal under test must fall within the unshaded area of the mask to be compliant. Different masks are used for the driver output and the receiver input allowing each to be separately specified.

# **13.3.1 RapidIO Driver AC Timing Specifications**

Driver AC timing specifications are provided in Table 48, Table 49, and Table 50. A driver shall comply with the specifications for each data rate/frequency for which operation of the driver is specified. Unless otherwise specified, these specifications are subject to the following conditions.

- The specifications apply over the supply voltage and ambient temperature ranges specified by the device vendor.

- The specifications apply for any combination of data patterns on the data signals.

- The output of a driver shall be connected to a 100  $\Omega$ , ±1%, differential (bridged) resistive load.

- Clock specifications apply only to clock signals.

- Data specifications apply only to data signals (FRAME, D[0:7]).

Table 48. RapidIO Driver AC Timing Specifications—500 Mbps Data Rate

| Characteristic                   | Symbol           | Rai  | nge  | Unit | Notes |

|----------------------------------|------------------|------|------|------|-------|

| Characteristic                   | Symbol           | Min  | Мах  |      | Notes |

| Differential output high voltage | V <sub>OHD</sub> | 200  | 540  | mV   | 1     |

| Differential output low voltage  | V <sub>OLD</sub> | -540 | -200 | mV   | 1     |

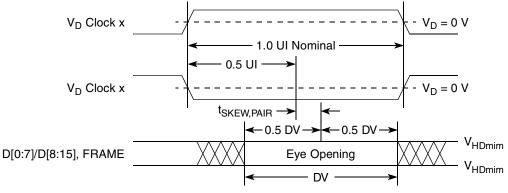

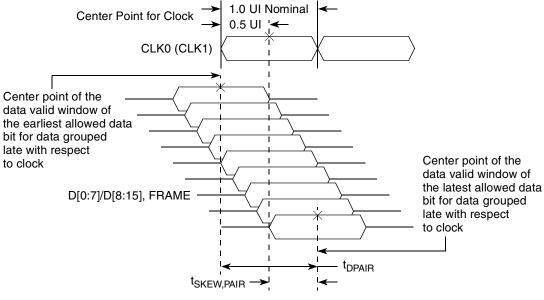

Figure 48 shows the definitions of the data to clock static skew parameter  $t_{SKEW,PAIR}$  and the data valid window parameter DV. The data and frame bits are those that are associated with the clock. The figure applies for all zero-crossings of the clock. All of the signals are differential signals.  $V_D$  represents  $V_{OD}$  for the transmitter and  $V_{ID}$  for the receiver. The center of the eye is defined as the midpoint of the region in which the magnitude of the signal voltage is greater than or equal to the minimum DV voltage.

Figure 48. Data to Clock Skew

Figure 49 shows the definition of the data to data static skew parameter t<sub>DPAIR</sub> and how the skew parameters are applied.

Figure 49. Static Skew Diagram

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

- 7. The socket lid must always be oriented to A1.

# **14.3 Pinout Listings**

Table 54 provides the pin-out listing for the MPC8560, 783 FC-PBGA package.

#### Table 54. MPC8560 Pinout Listing

| Signal        | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|               | PCI/PCI-X                                                                                                                                                                                                                                                                                                                                                                               |          |                  |       |

| PCI_AD[63:0]  | AA14, AB14, AC14, AD14, AE14, AF14, AG14, AH14,<br>V15, W15, Y15, AA15, AB15, AC15, AD15, AG15,<br>AH15, V16, W16, AB16, AC16, AD16, AE16, AF16,<br>V17, W17, Y17, AA17, AB17, AE17, AF17, AF18, AH6,<br>AD7, AE7, AH7, AB8, AC8, AF8, AG8, AD9, AE9, AF9,<br>AG9, AH9, W10, Y10, AA10, AE11, AF11, AG11,<br>AH11, V12, W12, Y12, AB12, AD12, AE12, AG12,<br>AH12, V13, Y13, AB13, AC13 | I/O      | OV <sub>DD</sub> | 17    |

| PCI_C_BE[7:0] | AG13, AH13, V14, W14, AH8, AB10, AD11, AC12                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 17    |

| PCI_PAR       | AA11                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —     |

| PCI_PAR64     | Y14                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | _     |

| PCI_FRAME     | AC10                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2     |

| PCI_TRDY      | AG10                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2     |

| PCI_IRDY      | AD10                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2     |

| PCI_STOP      | V11                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | 2     |

| PCI_DEVSEL    | AH10                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2     |

| PCI_IDSEL     | AA9                                                                                                                                                                                                                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —     |

| PCI_REQ64     | AE13                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 5, 10 |

| PCI_ACK64     | AD13                                                                                                                                                                                                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2     |

| PCI_PERR      | W11                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | 2     |

| PCI_SERR      | Y11                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | 2, 4  |

| PCI_REQ0      | AF5                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | —     |

| PCI_REQ[1:4]  | AF3, AE4, AG4, AE5                                                                                                                                                                                                                                                                                                                                                                      | I        | OV <sub>DD</sub> | —     |

| PCI_GNT[0]    | AE6                                                                                                                                                                                                                                                                                                                                                                                     | I/O      | OV <sub>DD</sub> | —     |

| PCI_GNT[1:4]  | AG5, AH5, AF6, AG6                                                                                                                                                                                                                                                                                                                                                                      | 0        | OV <sub>DD</sub> | 5, 9  |

Package and Pin Listings

| Signal         | Package Pin Number                                                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply     | Notes |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|-------|

|                | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                                                       |          |                     |       |

| MDQ[0:63]      | M26, L27, L22, K24, M24, M23, K27, K26, K22, J28,<br>F26, E27, J26, J23, H26, G26, C26, E25, C24, E23,<br>D26, C25, A24, D23, B23, F22, J21, G21, G22, D22,<br>H21, E21, N18, J18, D18, L17, M18, L18, C18, A18,<br>K17, K16, C16, B16, G17, L16, A16, L15, G15, E15,<br>C14, K13, C15, D15, E14, D14, D13, E13, D12, A11,<br>F13, H13, A13, B12 | I/O      | GV <sub>DD</sub>    |       |

| MECC[0:7]      | N20, M20, L19, E19, C21, A21, G19, A19                                                                                                                                                                                                                                                                                                           | I/O      | ${\sf GV}_{\sf DD}$ | _     |

| MDM[0:8]       | L24, H28, F24, L21, E18, E16, G14, B13, M19                                                                                                                                                                                                                                                                                                      | 0        | $GV_DD$             | _     |

| MDQS[0:8]      | L26, J25, D25, A22, H18, F16, F14, C13, C20                                                                                                                                                                                                                                                                                                      | I/O      | GV <sub>DD</sub>    | _     |

| MBA[0:1]       | B18, B19                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>    | _     |

| MA[0:14]       | N19, B21, F21, K21, M21, C23, A23, B24, H23, G24,<br>K19, B25, D27, J14, J13                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub>    | _     |

| MWE            | D17                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>    |       |

| MRAS           | F17                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>    |       |

| MCAS           | J16                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>    |       |

| MCS[0:3]       | H16, G16, J15, H15                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub>    | _     |

| MCKE[0:1]      | E26, E28                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>    | 11    |

| MCK[0:5]       | J20, H25, A15, D20, F28, K14                                                                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub>    |       |

| MCK[0:5]       | F20, G27, B15, E20, F27, L14                                                                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub>    | _     |

| MSYNC_IN       | M28                                                                                                                                                                                                                                                                                                                                              | I        | GV <sub>DD</sub>    | _     |

| MSYNC_OUT      | N28                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>    |       |

|                | Local Bus Controller Interface                                                                                                                                                                                                                                                                                                                   |          | l                   |       |

| LA[27]         | U18                                                                                                                                                                                                                                                                                                                                              | 0        | OV <sub>DD</sub>    | 5, 9  |

| LA[28:31]      | T18, T19, T20, T21                                                                                                                                                                                                                                                                                                                               | 0        | OV <sub>DD</sub>    | 7, 9  |

| LAD[0:31]      | AD26, AD27, AD28, AC26, AC27, AC28, AA22, AA23,<br>AA26, Y21, Y22, Y26, W20, W22, W26, V19, T22, R24,<br>R23, R22, R21, R18, P26, P25, P20, P19, P18, N22,<br>N23, N24, N25, N26                                                                                                                                                                 | I/O      | OV <sub>DD</sub>    |       |

| LALE           | V21                                                                                                                                                                                                                                                                                                                                              | 0        | OV <sub>DD</sub>    | 8, 9  |

| LBCTL          | V20                                                                                                                                                                                                                                                                                                                                              | 0        | OV <sub>DD</sub>    | 9     |

| LCKE           | U23                                                                                                                                                                                                                                                                                                                                              | 0        | OV <sub>DD</sub>    | —     |

| LCLK[0:2]      | U27, U28, V18                                                                                                                                                                                                                                                                                                                                    | 0        | OV <sub>DD</sub>    | —     |

| LCS[0:4]       | Y27, Y28, W27, W28, R27                                                                                                                                                                                                                                                                                                                          | 0        | OV <sub>DD</sub>    | 18    |

| LCS5/DMA_DREQ2 | R28                                                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub>    | 1     |

# **18 Document Revision History**

Table 62 provides a revision history for this hardware specification.

| Table 62 | Document | Revision | History |

|----------|----------|----------|---------|

|----------|----------|----------|---------|

| Rev. No. | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2      | Added "Note: Rise/Fall Time on CPM Input Pins" and following note text to Section 9.2, "CPM AC Timing Specifications."                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1      | Inserted Figure 3 and paragraph above it.<br>Added PCI/PCI-X row to Input Voltage characteristic and added footnote 6 to Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4        | Updated Section 2.1.2, "Power Sequencing."<br>Updated back page information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.5      | Updated Section 2.1.2, "Power Sequencing."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.4      | Updated MV <sub>REF</sub> Max Value in Table 1.<br>Updated MV <sub>REF</sub> Max Value in Table 2.<br>Added new revision level information to Table 63                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3      | Updated MV <sub>REF</sub> Max Value in Table 1.<br>Removed Figure 3.<br>In Table 4, replaced TBD with power numbers and added footnote.<br>Updated specs and footnotes in Table 8.<br>Corrected max number for MV <sub>REF</sub> in Table 13.<br>Changed parameter "Clock cycle duration" to "Clock period" in Table 27.<br>Added note 4 to t <sub>LBKHOV1</sub> and removed LALE reference from t <sub>LBKHOV3</sub> in Table 31 and Table 32.<br>Updated LALE signal in Figure 17 and Figure 18.<br>Modified Figure 21.<br>Modified Figure 61. |

| Rev. No. | Substantive Change(s)                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

| 3.2      | Updated Table 1 and Table 2 with 1.0 GHz device parameter requirements.                                             |

|          | Added Section 2.1.2, "Power Sequencing".                                                                            |

|          | Added CPM port signal drive strength to Table 3.                                                                    |

|          | Updated Table 4 with Maximum power data.                                                                            |

|          | Updated Table 4 and Table 5 with 1 GHz speed grade information.                                                     |

|          | Updated Table 6 with corrected typical I/O power numbers.                                                           |

|          | Updated Table 7 Note 2 lower voltage measurement point.                                                             |

|          | Replaced Table 7 Note 5 with spread spectrum clocking guidelines.                                                   |

|          | Added to Table 8 rise and fall time information.                                                                    |

|          | Added Section 4.4, "Real Time Clock Timing".                                                                        |

|          | Added precharge information to Section 6.2.2, "DDR SDRAM Output AC Timing Specifications".                          |

|          | Removed $V_{IL}$ and $V_{IH}$ references from Table 21, Table 22, Table 23, and Table 24.                           |

|          | Added reference level note to Table 21, Table 22, Table 23, Table 24, Table 25, Table 26, and Table 27.             |

|          | Updated TXD references to TCG in Section 7.2.3.1, "TBI Transmit AC Timing Specifications".                          |

|          | Updated t <sub>TTKHDX</sub> value in Table 25.                                                                      |

|          | Updated PMA_RX_CLK references to RX_CLK in Section 7.2.3.2, "TBI Receive AC Timing                                  |

|          | Specifications".                                                                                                    |

|          | Updated RXD references to RCG in Section 7.2.3.2, "TBI Receive AC Timing Specifications".                           |

|          | Updated Table 27 Note 2.                                                                                            |

|          | Corrected Table 29 f <sub>MDC</sub> and t <sub>MDC</sub> to reflect the correct minimum operating frequency.        |

|          | Updated Table 29 t <sub>MDKHDV</sub> and t <sub>MDKHDX</sub> values for clarification.                              |

|          | Added t <sub>LBKHKT</sub> and updated Note 2 in Table 32.                                                           |

|          | Corrected LGTA timing references in Figure 17.                                                                      |

|          | Updated Figure 18, Figure 20, and Figure 22.                                                                        |

|          | Corrected FCC output timing reference labels in Figure 24 and Figure 25.                                            |

|          | Updated Figure 50.                                                                                                  |

|          | Clarified Table 54 Note 5.                                                                                          |

|          | Updated Table 55 and Table 56 with 1 GHz information.                                                               |

|          | Added heat sink removal discussion to Section 16.2.3, "Thermal Interface Materials".                                |

|          | Corrected and added 1 GHz part number to Table 63.                                                                  |

| 3.1      | Updated Table 4 and Table 5.                                                                                        |

|          | Added Table 6.                                                                                                      |

|          | Added MCK duty cycle to Table 16.                                                                                   |

|          | Updated f <sub>MDC</sub> , t <sub>MDC</sub> , t <sub>MDKHDV</sub> , and t <sub>MDKHDX</sub> parameters in Table 29. |

|          | Added LALE to t <sub>LBKHOV3</sub> parameter in Table 31 and Table 32, and updated Figure 17.                       |

|          | Corrected active level designations of some of the pins in Table 54.                                                |

|          | Updated Table 63.                                                                                                   |

|          |                                                                                                                     |

### Table 62. Document Revision History (continued)

| Rev. No. | Substantive Change(s)                                                                                                                                                                                |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3.0      | Table 1—Corrected MII management voltage reference                                                                                                                                                   |  |  |  |  |

|          | Section 2.1.3—New                                                                                                                                                                                    |  |  |  |  |

|          | Table 2—Corrected MII management voltage reference                                                                                                                                                   |  |  |  |  |

|          | Table 5—Removed 'minimum' column                                                                                                                                                                     |  |  |  |  |

|          | Table 5—Added AV <sub>DD</sub> power table                                                                                                                                                           |  |  |  |  |

|          | Table 8—New                                                                                                                                                                                          |  |  |  |  |

|          | Table 9—New                                                                                                                                                                                          |  |  |  |  |

|          | Table 9—New                                                                                                                                                                                          |  |  |  |  |

|          | Table 13—Added overshoot/undershoot note.                                                                                                                                                            |  |  |  |  |

|          | Figure 4—New                                                                                                                                                                                         |  |  |  |  |

|          | Table 16—Restated t <sub>MCKSKEW1</sub> as t <sub>MCKSKEW</sub> , removed t <sub>MCKSKEW2</sub> ; added speed-specific minimum values for 333, 266, and 200 MHz; updated t <sub>DDSHME</sub> values. |  |  |  |  |

|          | Updated chapter to reflect that GMII, MII and TBI can be run with 2.5V signalling.                                                                                                                   |  |  |  |  |

|          | Table 29—Added MDIO output valid timing                                                                                                                                                              |  |  |  |  |

|          | Table 31—Updated t <sub>LBIVKH1</sub> , t <sub>LBIXKH1</sub> , and t <sub>LBOTOT</sub> .                                                                                                             |  |  |  |  |

|          | Table 32—New                                                                                                                                                                                         |  |  |  |  |

|          | Figure 20, Figure 22—Updated clock reference                                                                                                                                                         |  |  |  |  |

|          | Table 34—Updated t <sub>TDIVKH</sub>                                                                                                                                                                 |  |  |  |  |

|          | Table 35—Updated t <sub>TDKHOX</sub>                                                                                                                                                                 |  |  |  |  |

|          | Added tables and figures for CPM I <sup>2</sup> C                                                                                                                                                    |  |  |  |  |

|          | Table 45—Updated t <sub>PCIVKH</sub>                                                                                                                                                                 |  |  |  |  |

|          | Section 14.1— Changed minimum height from 2.22 to 3.07 and maximum from 2.76 to 3.75                                                                                                                 |  |  |  |  |

|          | Table 54.—Updated MII management voltage reference and added note 20.                                                                                                                                |  |  |  |  |

|          | Section 16.2.4.1—Changed $\theta_{JC}$ from 0.3 to 0.8; changed die-junction temperature from 67° to 71°                                                                                             |  |  |  |  |

|          | Section 17.7—Added paragraph that begins "TSEC1_TXD[3:0]"                                                                                                                                            |  |  |  |  |

| 2.1      | Section 2.1.3—New                                                                                                                                                                                    |  |  |  |  |

|          | Table 16—Added speed-specific minimum values for 333, 266, and 200 MHz                                                                                                                               |  |  |  |  |

|          | Table 31—Replaced all references to TSEC1_TXD[6:5] to TSEC2_TXD[6:5]                                                                                                                                 |  |  |  |  |

|          | Table 31—Added t <sub>LBSKEW</sub> and note 3                                                                                                                                                        |  |  |  |  |

|          | Table 31—Added comment about rev. 2.x devices to note 5                                                                                                                                              |  |  |  |  |

|          | Section 14.1— Changed minimum height from 2.22 to 3.07 and maximum from 2.76 to 3.75                                                                                                                 |  |  |  |  |

|          | Section 16.2.4.1—Changed $\theta_{JC}$ from 0.3 to 0.8; changed die-junction temperature from 67° to 71°                                                                                             |  |  |  |  |

|          | Section 17.7—Added paragraph that begins "TSEC1_TXD[3:0]"                                                                                                                                            |  |  |  |  |

| L        |                                                                                                                                                                                                      |  |  |  |  |

### Table 62. Document Revision History (continued)

**Device Nomenclature**

# THIS PAGE INTENTIONALLY LEFT BLANK