# E·XFL

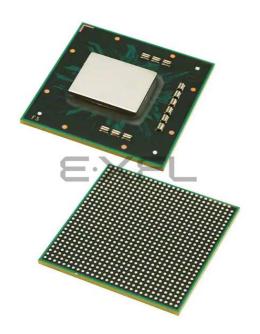

### NXP USA Inc. - MPC8560VT833LC Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 833MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DDR, SDRAM                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 2.5V, 3.3V                                                             |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | ·                                                                      |

| Package / Case                  | 783-BFBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8560vt833Ic |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Contiguous or discontiguous memory mapping

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self refresh SDRAM

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL2 compatible I/O

- RapidIO interface unit

- 8-bit RapidIO I/O and messaging protocols

- Source-synchronous double data rate (DDR) interfaces

- Supports small type systems (small domain, 8-bit device ID)

- Supports four priority levels (ordering within a level)

- Reordering across priority levels

- Maximum data payload of 256 bytes per packet

- Packet pacing support at the physical layer

- CRC protection for packets

- Supports atomic operations increment, decrement, set, and clear

- LVDS signaling

- RapidIO-compliant message unit

- One inbound data message structure (inbox)

- One outbound data message structure (outbox)

- Supports chaining and direct modes in the outbox

- Support of up to 16 packets per message

- Support of up to 256 bytes per packet and up to 4 Kbytes of data per message

- Supports one inbound doorbell message structure

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters that can generate interrupts

- Supports 22 other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing

#### **Electrical Characteristics**

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the 8 counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>TM</sup>-compliant, JTAG boundary scan

- 783 FC-PBGA package

# 2 Electrical Characteristics

This section provides the electrical specifications and thermal characteristics for the MPC8560. The MPC8560 is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

|                     | Characteristic                                                     | Symbol           | Max Value                    | Unit | Notes |

|---------------------|--------------------------------------------------------------------|------------------|------------------------------|------|-------|

| Core supply voltage | For devices rated at 667 and 833 MHz<br>For devices rated at 1 GHz | V <sub>DD</sub>  | -0.3 to 1.32<br>-0.3 to 1.43 | V    | —     |

| PLL supply voltage  | For devices rated at 667 and 833 MHz<br>For devices rated at 1 GHz | AV <sub>DD</sub> | -0.3 to 1.32<br>-0.3 to 1.43 | V    | _     |

### Table 1. Absolute Maximum Ratings <sup>1</sup>

Table 6. Estimated Typical I/O Power Consumption (continued)

| Interface    | Parameter   | GV <sub>DD</sub> (2.5 V) | OV <sub>DD</sub> (3.3 V) | LV <sub>DD</sub> (3.3 V) | LV <sub>DD</sub> (2.5 V) | Units | Notes |

|--------------|-------------|--------------------------|--------------------------|--------------------------|--------------------------|-------|-------|

| TDMA or TDMB | Nibble mode | —                        | 10                       |                          | —                        | mW    | 7     |

|              | Per channel | —                        | 5                        | _                        | _                        |       |       |

Notes:

1. GV<sub>DD</sub>=2.5, ECC enabled, 66% bus utilization, 33% write cycles, 10pF load on data, 10pF load on address/command, 10pF load on clock

- 2. OV<sub>DD</sub>=3.3, 30pF load per pin, 54% bus utilization, 33% write cycles

- 3. OV<sub>DD</sub>=3.3, 25pF load per pin, 5pF load on clock, 40% bus utilization, 33% write cycles

4. V<sub>DD</sub>=1.2, OV<sub>DD</sub>=3.3

- 5. LVDD=2.5/3.3, 15pF load per pin, 25% bus utilization

- 6. Power dissipation for one TSEC only

- 7. OV<sub>DD</sub>=3.3, 10pF load per pin, 50% bus utilization

# 4 Clock Timing

### 4.1 System Clock Timing

Table 7 provides the system clock (SYSCLK) AC timing specifications for the MPC8560.

| Parameter/Condition       | Symbol                                 | Min | Typical | Max     | Unit | Notes |

|---------------------------|----------------------------------------|-----|---------|---------|------|-------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                    | _   | _       | 166     | MHz  | 1     |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                    | 6.0 | —       | _       | ns   | —     |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>      | 0.6 | 1.0     | 1.2     | ns   | 2     |

| SYSCLK duty cycle         | t <sub>KHKL</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60      | %    | 3     |

| SYSCLK jitter             | —                                      | _   | —       | +/- 150 | ps   | 4, 5  |

Table 7. SYSCLK AC Timing Specifications

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. For spread spectrum clocking, guidelines are +/-1% of the input frequency with a maximum of 60 kHz of modulation regardless of the input frequency.

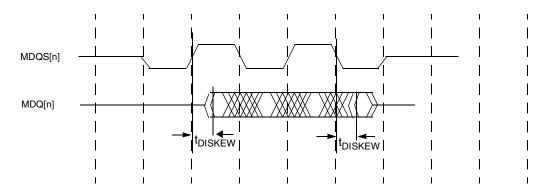

# 6.2 DDR SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR SDRAM Input AC Timing Specifications

Table 15 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 15. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                   | Symbol              | Min                      | Мах                      | Unit | Notes |

|-----------------------------------------------------------------------------|---------------------|--------------------------|--------------------------|------|-------|

| AC input low voltage                                                        | V <sub>IL</sub>     | —                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage                                                       | V <sub>IH</sub>     | MV <sub>REF</sub> + 0.31 | GV <sub>DD</sub> + 0.3   | V    | —     |

| MDQS—MDQ/MECC input skew per byte<br>For DDR = 333 MHz<br>For DDR ≤ 266 MHz | <sup>t</sup> DISKEW | -750<br>-1125            | 750<br>1125              | ps   | 1, 2  |

Note:

1.Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n +  $\{0...7\}$ ] if  $0 \le n \le 7$ ) or ECC (MECC[ $\{0...7\}$ ] if n=8).

2.For timing budget analysis, the MPC8560 consumes  $\pm$ 550 ps of the total budget.

Figure 4. DDR SDRAM Interface Input Timing

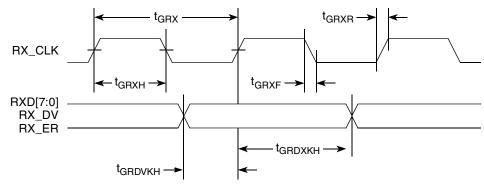

### Table 22. GMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%, or LV<sub>DD</sub>=2.5V  $\pm$  5%.

| Parameter/Condition             | Symbol <sup>1</sup>                                  | Min | Тур | Max | Unit |

|---------------------------------|------------------------------------------------------|-----|-----|-----|------|

| RX_CLK clock rise and fall time | t <sub>GRXR</sub> , t <sub>GRXF</sub> <sup>2,3</sup> | _   |     | 1.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

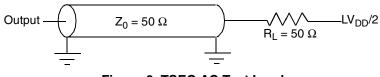

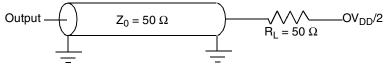

Figure 8 provides the AC test load for TSEC.

Figure 8. TSEC AC Test Load

Figure 9 shows the GMII receive AC timing diagram.

Figure 9. GMII Receive AC Timing Diagram

### 7.2.2 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 7.2.2.1 MII Transmit AC Timing Specifications

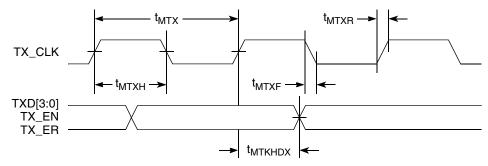

Table 23 provides the MII transmit AC timing specifications.

#### Table 23. MII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V ± 5%, or LV<sub>DD</sub>=2.5V ± 5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                                  | Min | Тур | Мах | Unit |

|-------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>                        | _   | 400 | —   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                                     | _   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH/</sub> t <sub>MTX</sub>                  | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                                  | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise and fall time            | t <sub>MTXR</sub> , t <sub>MTXF</sub> <sup>2,3</sup> | 1.0 | _   | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.3.Guaranteed by design.

Figure 10 shows the MII transmit AC timing diagram.

Figure 10. MII Transmit AC Timing Diagram

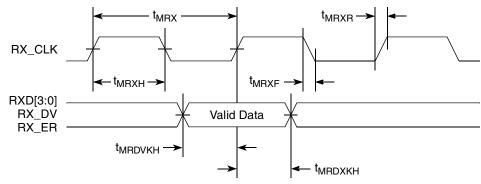

### 7.2.2.2 MII Receive AC Timing Specifications

Table 24 provides the MII receive AC timing specifications.

### Table 24. MII Receive AC Timing Specifications

At recommended operating conditions with LV\_{DD} of 3.3 V  $\pm$  5%, or LV\_{DD}=2.5V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                    | Min  | Тур | Max | Unit |

|---------------------------------------------|----------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> <sup>3</sup>          | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                       | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub>    | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                    | 10.0 | —   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                    | 10.0 | _   | _   | ns   |

| RX_CLK clock rise and fall time             | $t_{MRXR}$ , $t_{MRXF}$ <sup>2,3</sup> | 1.0  | —   | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2.Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 11 shows the MII receive AC timing diagram.

Figure 11. MII Receive AC Timing Diagram

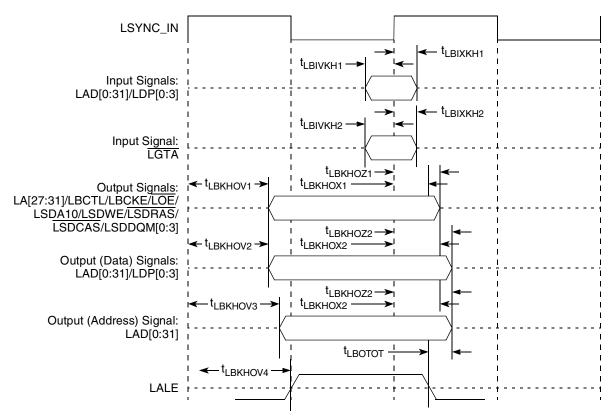

|                                                                       |                                  |                        |     |     |      | T       |     |  |  |

|-----------------------------------------------------------------------|----------------------------------|------------------------|-----|-----|------|---------|-----|--|--|

| Parameter                                                             | POR Configuration                | Symbol <sup>1</sup>    | Min | Max | Unit | Notes   |     |  |  |

| Input setup to local bus clock (except LUPWAIT)                       | _                                | t <sub>LBIVKH1</sub>   | 1.8 |     | ns   | 4, 5, 8 |     |  |  |

| LUPWAIT input setup to local bus clock                                | —                                | t <sub>LBIVKH2</sub>   | 1.7 | —   | ns   | 4, 5    |     |  |  |

| Input hold from local bus clock (except<br>LUPWAIT)                   | _                                | t <sub>LBIXKH1</sub>   | 0.5 | _   | ns   | 4, 5, 8 |     |  |  |

| LUPWAIT input hold from local bus clock                               | —                                | t <sub>LBIXKH2</sub>   | 1.0 | —   | ns   | 4, 5    |     |  |  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | _                                | t <sub>lbotot</sub>    | 1.5 | —   | ns   | 6       |     |  |  |

| Local bus clock to output valid (except                               | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOV1</sub>   |     | 2.0 | ns   | 4, 8    |     |  |  |

| LAD/LDP and LALE)                                                     | TSEC2_TXD[6:5] = 11<br>(default) |                        |     |     |      |         | 3.5 |  |  |

| Local bus clock to data valid for LAD/LDP                             | TSEC2_TXD[6:5] = 00              | 0 t <sub>LBKHOV2</sub> | _   | 2.2 | ns   | 4, 8    |     |  |  |

| TSEC2_TXD[6:5] = 11<br>(default)                                      |                                  |                        | 3.7 |     |      |         |     |  |  |

| Local bus clock to address valid for LAD                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOV3</sub>   |     | 2.3 | ns   | 4, 8    |     |  |  |

|                                                                       | TSEC2_TXD[6:5] = 11<br>(default) |                        |     | 3.8 |      |         |     |  |  |

| Local bus clock to LALE assertion                                     |                                  | t <sub>LBKHOV4</sub>   | _   | 2.3 | ns   | 4, 8    |     |  |  |

| Output hold from local bus clock (except                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOX1</sub>   | 0.7 | —   | ns   | 4, 8    |     |  |  |

| LAD/LDP and LALE)                                                     | TSEC2_TXD[6:5] = 11<br>(default) |                        | 1.6 |     |      |         |     |  |  |

| Output hold from local bus clock for                                  | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOX2</sub>   | 0.7 | —   | ns   | 4, 8    |     |  |  |

| LAD/LDP                                                               | TSEC2_TXD[6:5] = 11<br>(default) |                        | 1.6 |     |      |         |     |  |  |

| Local bus clock to output high Impedance                              | TSEC2_TXD[6:5] = 00              | t <sub>LBKHOZ1</sub>   |     | 2.5 | ns   | 7, 9    |     |  |  |

| (except LAD/LDP and LALE)                                             | TSEC2_TXD[6:5] = 11<br>(default) |                        |     | 3.8 |      |         |     |  |  |

### Table 31. Local Bus General Timing Parameters—DLL Enabled (continued)

| Parameter                                                  | POR Configuration                | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|------------------------------------------------------------|----------------------------------|----------------------|------|------|------|-------|

| Local bus clock to data valid for LAD/LDP                  | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

|                                                            | TSEC2_TXD[6:5] = 11<br>(default) |                      |      | 1.4  |      |       |

| Local bus clock to address valid for LAD                   | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOV3</sub> | _    | 0    | ns   | 4     |

|                                                            | TSEC2_TXD[6:5] = 11<br>(default) |                      |      | 1.5  |      |       |

| Local bus clock to LALE assertion                          |                                  | t <sub>LBKHOV4</sub> | —    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE) | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOX1</sub> | -3.2 | —    | ns   | 4     |

|                                                            | TSEC2_TXD[6:5] = 11<br>(default) |                      | -2.3 |      |      |       |

| Output hold from local bus clock for                       | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOX2</sub> | -3.2 | —    | ns   | 4     |

| LAD/LDP                                                    | TSEC2_TXD[6:5] = 11<br>(default) |                      | -2.3 |      |      |       |

| Local bus clock to output high Impedance                   | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| (except LAD/LDP and LALE)                                  | TSEC2_TXD[6:5] = 11<br>(default) |                      |      | 1.5  |      |       |

| Local bus clock to output high impedance                   | TSEC2_TXD[6:5] = 00              | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

| for LAD/LDP                                                | TSEC2_TXD[6:5] = 11<br>(default) |                      |      | 1.5  |      |       |

| Table 32, Local Bus Ger | neral Timing Parameters- | -DLL Bypassed (continued) |

|-------------------------|--------------------------|---------------------------|

|                         | liera inning i arametere |                           |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.</sub>

2.All timings are in reference to local bus clock for DLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by tLBKHKT.

3.Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at OV<sub>DD</sub>/2.

4.All signals are measured from  $OV_{DD}/2$  of the rising edge of local bus clock for DLL bypass mode to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

5.Input timings are measured at the pin.

6. The value of t<sub>LBOTOT</sub> is defined as the sum of 1/2 or 1 ccb\_clk cycle as programmed by LBCR[AHD], and the number of local bus buffer delays used as programmed at power-on reset with configuration pins TSEC2\_TXD[6:5].

7.For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

8. Guaranteed by characterization.

9. Guaranteed by design.

#### Local Bus

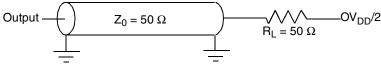

Figure 16 provides the AC test load for the local bus.

Figure 16. Local Bus AC Test Load

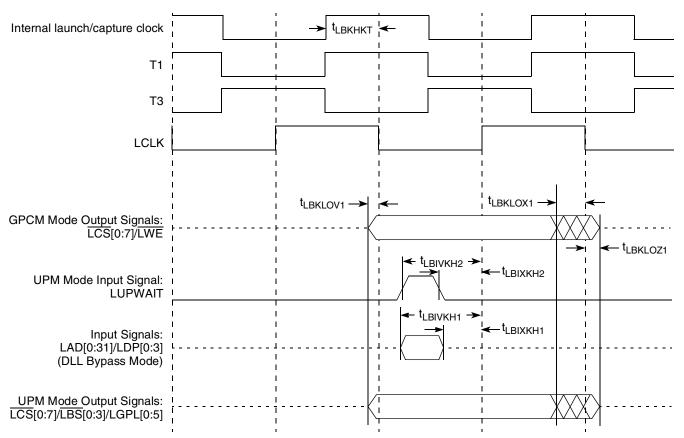

Figure 17 through Figure 22 show the local bus signals.

Figure 17. Local Bus Signals, Nonspecial Signals Only (DLL Enabled)

Figure 20. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode)

### Table 34. CPM Input AC Timing Specifications <sup>1</sup> (continued)

| Characteristic           | Symbol <sup>2</sup> | Min <sup>3</sup> | Unit |

|--------------------------|---------------------|------------------|------|

| COL/CRS width high (FCC) | t <sub>FCCH</sub>   | 1.5              | CLK  |

#### Notes:

- 1.Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of Serial Clock. Timings are measured at the pin.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional</sub>

block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>FIIVKH</sub> symbolizes the FCC inputs internal timing (FI) with respect to the time the input signals (I) reaching the valid state (V) relative to the reference clock t<sub>FCC</sub> (K) going to the high (H) state or setup time. And t<sub>TDIXKH</sub> symbolizes the TDM timing (TD) with respect to the time the input signals (I) reach the invalid state (X) relative to the reference clock t<sub>FCC</sub> (K) going to the high (H) state or hold time.

3.PIO and TIMER inputs and outputs are asynchronous to SYSCLK or any other externally visible clock. PIO/TIMER inputs are internally synchronized to the CPM internal clock. PIO/TIMER outputs should be treated as asynchronous.

| Characteristic                              | Symbol <sup>2</sup> | Min | Мах | Unit |

|---------------------------------------------|---------------------|-----|-----|------|

| FCC outputs—internal clock (NMSI) delay     | t <sub>FIKHOX</sub> | 1   | 5.5 | ns   |

| FCC outputs—external clock (NMSI) delay     | t <sub>FEKHOX</sub> | 2   | 8   | ns   |

| SCC/SPI outputs-internal clock (NMSI) delay | t <sub>NIKHOX</sub> | 0.5 | 10  | ns   |

| SCC outputs—external clock (NMSI) delay     | t <sub>NEKHOX</sub> | 2   | 8   | ns   |

| SPI output—external clock (NMSI) delay      | t <sub>SEKHOX</sub> | 2   | 11  | ns   |

| TDM outputs/SI delay                        | t <sub>TDKHOX</sub> | 2.5 | 11  | ns   |

### Table 35. CPM Output AC Timing Specifications <sup>1</sup>

#### Notes:

1.Output specifications are measured from the 50% level of the rising edge of Serial Clock to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub>

(reference)(state) for inputs and t<sub>(first two letters of functional block</sub>)(reference)(state)(signal)(state) for outputs. For example, t<sub>FIKHOX</sub> symbolizes the FCC inputs internal timing (FI) for the time t<sub>FCC</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

Figure 16 provides the AC test load for the CPM.

Figure 23. CPM AC Test Load

Figure 24 through Figure 29 represent the AC timing from Table 34 and Table 35. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

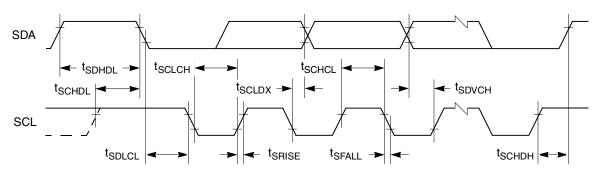

# Table 36 shows CPM I<sup>2</sup>C AC Timing.

| Table 36. CPM I <sup>2</sup> C AC Timing | Table 36 | . CPM | I <sup>2</sup> C AC | Timing |

|------------------------------------------|----------|-------|---------------------|--------|

|------------------------------------------|----------|-------|---------------------|--------|

| Characteristic                          | Symbol Min         |                                   | Мах                        | Unit |

|-----------------------------------------|--------------------|-----------------------------------|----------------------------|------|

| SCL clock frequency (slave)             | f <sub>SCL</sub>   | 0 F <sub>MAX</sub> <sup>1</sup>   |                            | Hz   |

| SCL clock frequency (master)            | f <sub>SCL</sub>   | BRGCLK/16512                      | BRGCLK/48                  | Hz   |

| Bus free time between transmissions     | t <sub>SDHDL</sub> | 1/(2.2 * f <sub>SCL</sub> )       | —                          | S    |

| Low period of SCL                       | t <sub>SCLCH</sub> | 1/(2.2 * f <sub>SCL</sub> )       | —                          | S    |

| High period of SCL                      | t <sub>SCHCL</sub> | 1/(2.2 * f <sub>SCL</sub> ) —     |                            | S    |

| Start condition setup time <sup>2</sup> | t <sub>SCHDL</sub> | 2/(divider * f <sub>SCL</sub> )   | —                          | S    |

| Start condition hold time <sup>2</sup>  | t <sub>SDLCL</sub> | 3/(divider * f <sub>SCL</sub> )   | —                          | S    |

| Data hold time <sup>2</sup>             | t <sub>SCLDX</sub> | 2/(divider * f <sub>SCL</sub> )   | —                          | S    |

| Data setup time <sup>2</sup>            | t <sub>SDVCH</sub> | 3/(divider * f <sub>SCL</sub> ) — |                            | S    |

| SDA/SCL rise time                       | t <sub>SRISE</sub> | — 1/(10 * f <sub>SCL</sub> )      |                            | S    |

| SDA/SCL fall time                       | t <sub>SFALL</sub> | —                                 | 1/(33 * f <sub>SCL</sub> ) | S    |

| Stop condition setup time               | t <sub>SCHDH</sub> | 2/(divider * f <sub>SCL</sub> )   | _                          | S    |

Notes:

1.F<sub>MAX</sub> = BRGCLK/(min\_divider\*prescaler). Where prescaler=25-I2MODE[PDIV]; and min\_divider=12 if digital filter disabled and 18 if enabled.

Example #1: if I2MODE[PDIV]=11 (prescaler=4) and I2MODE[FLT]=0 (digital filter disabled) then FMAX=BRGCLK/48

Example #2: if I2MODE[PDIV]=00 (prescaler=32) and I2MODE[FLT]=1 (digital filter enabled) then FMAX=BRGCLK/576

2.divider =  $f_{SCL}$ /prescaler.

In master mode: divider = BRGCLK/(f<sub>SCL</sub>\*prescaler) = 2\*(I2BRG[DIV]+3) In slave mode: divider = BRGCLK/(f<sub>SCL</sub>\*prescaler)

Figure 30 is a a diagram of CPM I<sup>2</sup>C Bus Timing.

Figure 30. CPM I<sup>2</sup>C Bus Timing Diagram

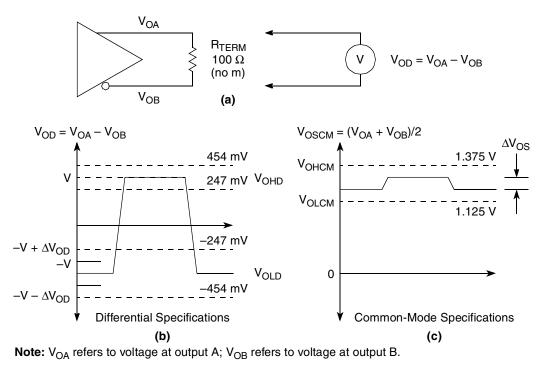

### RapidIO

Figure 41 shows the DC driver signal levels.

Figure 41. DC Driver Signal Levels

# **13.2 RapidIO AC Electrical Specifications**

This section contains the AC electrical specifications for a RapidIO 8/16 LP-LVDS device. The interface defined is a parallel differential low-power high-speed signal interface. Note that the source of the transmit clock on the RapidIO interface is dependent on the settings of the LGPL[0:1] signals at reset. Note that the default setting makes the core complex bus (CCB) clock the source of the transmit clock. See Chapter 4 of the Reference Manual for more details on reset configuration settings.

# **13.3 RapidIO Concepts and Definitions**

This section specifies signals using differential voltages. Figure 42 shows how the signals are defined. The figure shows waveforms for either a transmitter output (TD and TD) or a receiver input (RD and RD). Each signal swings between A volts and B volts where A > B. Using these waveforms, the definitions are as follows:

- The transmitter output and receiver input signals TD, TD, RD, and RD each have a peak-to-peak swing of A-B volts.

- The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD} V_{\overline{TD}}$ .

- The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$ .

- The differential output signal of the transmitter or input signal of the receiver, ranges from A B volts to -(A B) volts.

RapidIO

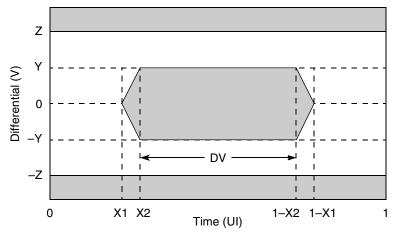

Figure 43. Example Compliance Mask

Y = minimum data valid amplitude

Z = maximum amplitude

1 UI = 1 unit interval = 1/baud rate

X1 = end of zero crossing region

X2 = beginning of data valid window

$DV = data valid window = 1 - 2 \times X2$

The waveform of the signal under test must fall within the unshaded area of the mask to be compliant. Different masks are used for the driver output and the receiver input allowing each to be separately specified.

### **13.3.1 RapidIO Driver AC Timing Specifications**

Driver AC timing specifications are provided in Table 48, Table 49, and Table 50. A driver shall comply with the specifications for each data rate/frequency for which operation of the driver is specified. Unless otherwise specified, these specifications are subject to the following conditions.

- The specifications apply over the supply voltage and ambient temperature ranges specified by the device vendor.

- The specifications apply for any combination of data patterns on the data signals.

- The output of a driver shall be connected to a 100  $\Omega$ , ±1%, differential (bridged) resistive load.

- Clock specifications apply only to clock signals.

- Data specifications apply only to data signals (FRAME, D[0:7]).

Table 48. RapidIO Driver AC Timing Specifications—500 Mbps Data Rate

| Characteristic                   | Symbol           | Range |      | Unit | Notes |

|----------------------------------|------------------|-------|------|------|-------|

| Characteristic                   | Symbol           | Min   | Мах  | onn  | Notes |

| Differential output high voltage | V <sub>OHD</sub> | 200   | 540  | mV   | 1     |

| Differential output low voltage  | V <sub>OLD</sub> | -540  | -200 | mV   | 1     |

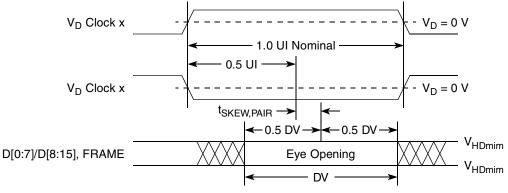

Figure 48 shows the definitions of the data to clock static skew parameter  $t_{SKEW,PAIR}$  and the data valid window parameter DV. The data and frame bits are those that are associated with the clock. The figure applies for all zero-crossings of the clock. All of the signals are differential signals.  $V_D$  represents  $V_{OD}$  for the transmitter and  $V_{ID}$  for the receiver. The center of the eye is defined as the midpoint of the region in which the magnitude of the signal voltage is greater than or equal to the minimum DV voltage.

Figure 48. Data to Clock Skew

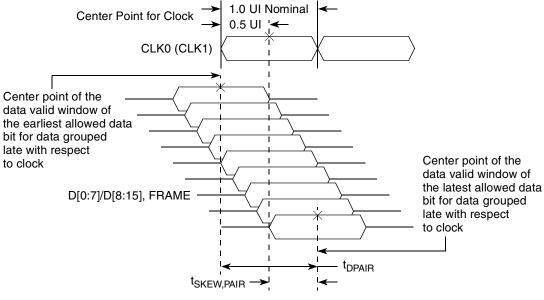

Figure 49 shows the definition of the data to data static skew parameter t<sub>DPAIR</sub> and how the skew parameters are applied.

Figure 49. Static Skew Diagram

# **17 System Design Information**

This section provides electrical and thermal design recommendations for successful application of the MPC8560.

# 17.1 System Clocking

The MPC8560 includes three PLLs.

- 1. The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 15.2, "Platform/System PLL Ratio."

- 2. The e500 Core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 15.3, "e500 Core PLL Ratio."

- 3. The CPM PLL is slaved to the platform clock and is used to generate clocks used internally by the CPM block. The ratio between the CPM PLL and the platform clock is fixed and not under user control.

# 17.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, and AV<sub>DD</sub>3, respectively). The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages will be derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide three independent filter circuits as illustrated in Figure 58, one to each of the three  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the 783 FC-PBGA footprint, without the inductance of vias.

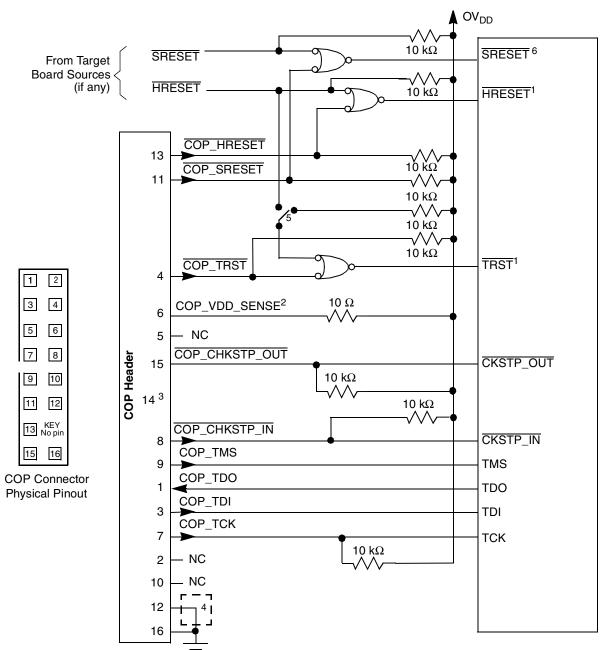

#### System Design Information

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

#### Figure 61. JTAG Interface Connection

| Rev. No. | Substantive Change(s)                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

| 3.2      | Updated Table 1 and Table 2 with 1.0 GHz device parameter requirements.                                             |

|          | Added Section 2.1.2, "Power Sequencing".                                                                            |

|          | Added CPM port signal drive strength to Table 3.                                                                    |

|          | Updated Table 4 with Maximum power data.                                                                            |

|          | Updated Table 4 and Table 5 with 1 GHz speed grade information.                                                     |

|          | Updated Table 6 with corrected typical I/O power numbers.                                                           |

|          | Updated Table 7 Note 2 lower voltage measurement point.                                                             |

|          | Replaced Table 7 Note 5 with spread spectrum clocking guidelines.                                                   |

|          | Added to Table 8 rise and fall time information.                                                                    |

|          | Added Section 4.4, "Real Time Clock Timing".                                                                        |

|          | Added precharge information to Section 6.2.2, "DDR SDRAM Output AC Timing Specifications".                          |

|          | Removed $V_{IL}$ and $V_{IH}$ references from Table 21, Table 22, Table 23, and Table 24.                           |

|          | Added reference level note to Table 21, Table 22, Table 23, Table 24, Table 25, Table 26, and Table 27.             |

|          | Updated TXD references to TCG in Section 7.2.3.1, "TBI Transmit AC Timing Specifications".                          |

|          | Updated t <sub>TTKHDX</sub> value in Table 25.                                                                      |

|          | Updated PMA_RX_CLK references to RX_CLK in Section 7.2.3.2, "TBI Receive AC Timing                                  |

|          | Specifications".                                                                                                    |

|          | Updated RXD references to RCG in Section 7.2.3.2, "TBI Receive AC Timing Specifications".                           |

|          | Updated Table 27 Note 2.                                                                                            |

|          | Corrected Table 29 f <sub>MDC</sub> and t <sub>MDC</sub> to reflect the correct minimum operating frequency.        |

|          | Updated Table 29 t <sub>MDKHDV</sub> and t <sub>MDKHDX</sub> values for clarification.                              |

|          | Added t <sub>LBKHKT</sub> and updated Note 2 in Table 32.                                                           |

|          | Corrected LGTA timing references in Figure 17.                                                                      |

|          | Updated Figure 18, Figure 20, and Figure 22.                                                                        |

|          | Corrected FCC output timing reference labels in Figure 24 and Figure 25.                                            |

|          | Updated Figure 50.                                                                                                  |

|          | Clarified Table 54 Note 5.                                                                                          |

|          | Updated Table 55 and Table 56 with 1 GHz information.                                                               |

|          | Added heat sink removal discussion to Section 16.2.3, "Thermal Interface Materials".                                |

|          | Corrected and added 1 GHz part number to Table 63.                                                                  |

| 3.1      | Updated Table 4 and Table 5.                                                                                        |

|          | Added Table 6.                                                                                                      |

|          | Added MCK duty cycle to Table 16.                                                                                   |

|          | Updated f <sub>MDC</sub> , t <sub>MDC</sub> , t <sub>MDKHDV</sub> , and t <sub>MDKHDX</sub> parameters in Table 29. |

|          | Added LALE to t <sub>LBKHOV3</sub> parameter in Table 31 and Table 32, and updated Figure 17.                       |

|          | Corrected active level designations of some of the pins in Table 54.                                                |

|          | Updated Table 63.                                                                                                   |

|          |                                                                                                                     |

### Table 62. Document Revision History (continued)

# **19 Device Nomenclature**

Ordering information for the parts fully covered by this specification document is provided in Section 19.1, "Part Numbers Fully Addressed by this Document."

# **19.1 Part Numbers Fully Addressed by this Document**

Table 63 provides the Freescale part numbering nomenclature for the MPC8560. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | t                                      | рр                                        | ff(f)                                  | С                         | r                                                                        |

|-----------------|--------------------|----------------------------------------|-------------------------------------------|----------------------------------------|---------------------------|--------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature<br>Range <sup>1</sup>      | Package <sup>2</sup>                      | Processor<br>Frequency <sup>3, 4</sup> | Platform<br>Frequency     | Revision Level                                                           |

| MPC             | 8560               | Blank = 0 to 105°C<br>C= -40 to 105°C  |                                           | 833 = 833 MHz<br>667 = 667 MHz         | L = 333 MHz<br>J= 266 MHz | B = Rev. 2.0<br>(SVR = 0x80700020)<br>C = Rev. 2.1<br>(SVR = 0x80700021) |

| MPC             | 8560               | Blank = 0 to 105°C<br>C = −40 to 105°C | PX = FC-PBGA<br>VT = FC-PBGA<br>(Pb-free) | AQ = 1.0 GHz                           | F = 333 MHz               | B = Rev. 2.0<br>(SVR = 0x80700020)<br>C = Rev. 2.1<br>(SVR = 0x80700021) |

### Table 63. Part Numbering Nomenclature

#### Notes:

1.For Temperature Range=C, Processor Frequency is limited to 667 MHz.

2.See Section 14, "Package and Pin Listings" for more information on available package types.

- 3. Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. The core must be clocked at a minimum frequency of 400 MHz. A device must not be used beyond the core frequency or platform frequency indicated on the device.

- 4. Designers should use the maximum power value corresponding to the core and platform frequency grades indicated on the device. A lower maximum power value should not be assumed for design purposes even when running at a lower frequency.