Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HCS12                                                      |

| Core Size                  | 16-Bit                                                     |

| Speed                      | 32MHz                                                      |

| Connectivity               | CANbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 64                                                         |

| Program Memory Size        | 128KB (128K x 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 4K x 8                                                     |

| RAM Size                   | 6K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                               |

| Data Converters            | A/D 10x12b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 80-QFP                                                     |

| Supplier Device Package    | 80-QFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12p128mqk |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | A.1.10 Supply Currents                                 | 510 |

|------|--------------------------------------------------------|-----|

| A.2  | ATD Characteristics                                    |     |

|      | A.2.1 ATD Operating Characteristics.                   | 512 |

|      | A.2.2 Factors Influencing Accuracy                     | 513 |

|      | A.2.3 ATD Accuracy                                     | 514 |

| A.3  | NVM                                                    | 518 |

|      | A.3.1 Timing Parameters                                | 518 |

|      | A.3.2 NVM Reliability Parameters.                      | 522 |

| A.4  | Phase Locked Loop                                      | 523 |

|      | A.4.1 Jitter Definitions                               |     |

|      | A.4.2 Electrical Characteristics for the PLL.          | 525 |

| A.5  | Electrical Characteristics for the IRC1M               | 525 |

| A.6  | Electrical Characteristics for the Oscillator (OSCLCP) | 526 |

| A.7  | Reset Characteristics                                  | 526 |

| A.8  | Electrical Specification for Voltage Regulator         | 527 |

| A.9  | Chip Power-up and Voltage Drops                        | 527 |

| A.10 | MSCAN                                                  | 529 |

| A.11 | SPI Timing                                             | 529 |

|      | A.11.1 Master Mode                                     | 529 |

|      | A.11.2 Slave Mode                                      | 531 |

# Appendix B Ordering Information

# Appendix C

# Package Information

| C.1 | 80 QFP Package Mechanical Outline  | . 536 |

|-----|------------------------------------|-------|

| C.2 | 48 QFN Package Mechanical Outline  | . 539 |

| C.3 | 64 LQFP Package Mechanical Outline | . 542 |

# Appendix D Detailed Register Address Map

| D.1 | Detailed Register | lap |  | 5 |

|-----|-------------------|-----|--|---|

|-----|-------------------|-----|--|---|

- Pulse width modulation (PWM) module with 6 x 8-bit channels

- 10-channel, 12-bit resolution successive approximation analog-to-digital converter (ATD)

- One serial peripheral interface (SPI) module

- One serial communication interface (SCI) module supporting LIN communications

- One multi-scalable controller area network (MSCAN) module (supporting CAN protocol 2.0A/B)

- On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

- Autonomous periodic interrupt (API)

## 1.3 Module Features

The following sections provide more details of the modules implemented on the MC9S12P family.

## 1.3.1 S12 16-Bit Central Processor Unit (CPU)

S12 CPU is a high-speed 16-bit processing unit:

- Full 16-bit data paths supports efficient arithmetic operation and high-speed math execution

- Includes many single-byte instructions. This allows much more efficient use of ROM space.

- Extensive set of indexed addressing capabilities, including:

- Using the stack pointer as an indexing register in all indexed operations

- Using the program counter as an indexing register in all but auto increment/decrement mode

- Accumulator offsets using A, B, or D accumulators

- Automatic index predecrement, preincrement, postdecrement, and postincrement (by -8 to +8)

## 1.3.2 On-Chip Flash with ECC

On-chip flash memory on the MC9S12P features the following:

- Up to 128 Kbyte of program flash memory

- 32 data bits plus 7 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 512 bytes

- Automated program and erase algorithm

- User margin level setting for reads

- Protection scheme to prevent accidental program or erase

- 4 Kbyte data flash space

- 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 256 bytes

- Automated program and erase algorithm

- User margin level setting for reads

## 1.7.3.10 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general-purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference. The ECLK output has a programmable prescaler.

## 1.7.3.11 PE[3:2] — Port E I/O Pin 3

PE[3:2] are a general-purpose input or output pins.

## 1.7.3.12 PE1 / IRQ — Port E Input Pin 1

PE1 is a general-purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode.

## 1.7.3.13 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general-purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode. The XIRQ interrupt is level sensitive and active low. As XIRQ is level sensitive, while this pin is low the MCU will not enter STOP mode.

## 1.7.3.14 PJ[7:6, 2:0] / KWJ[7:6, 2:0] — Port J I/O Pins 7-6, 2-0

PJ[7:6, 2:0] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs.

## 1.7.3.15 PM[7:6] — Port M I/O Pins 7-6

PM[7:6] are a general-purpose input or output pins.

#### 1.7.3.16 PM5 / SCK — Port M I/O Pin 5

PM5 is a general-purpose input or output pin. It can be configured as the serial clock pin SCK of the serial peripheral interface (SPI).

#### 1.7.3.17 PM4 / MOSI — Port M I/O Pin 4

PM4 is a general-purpose input or output pin. It can be configured as the master output (during master mode) or slave input pin (during slave mode) MOSI for the serial peripheral interface (SPI).

#### 1.7.3.18 PM3 / SS — Port M I/O Pin 3

PM3 is a general-purpose input or output pin. It can be configured as the slave select pin  $\overline{SS}$  of the serial peripheral interface (SPI).

#### 1.7.3.19 PM2 / MISO— Port M I/O Pin 3

PM2 is a general-purpose input or output pin. It can be configured as the master input (during master mode) or slave output pin (during slave mode) MISO for the serial peripheral interface (SPI)

**Device Overview MC9S12P-Family**

# NP

# 1.12 COP Configuration

The COP time-out rate bits CR[2:0] and the WCOP bit in the CPMUCOP register at address 0x003C are loaded from the Flash register FOPT. See Table 1-13 and Table 1-14 for coding. The FOPT register is loaded from the Flash configuration field byte at global address 0x3\_FF0E during the reset sequence.

| NV[2:0] in<br>FOPT Register | CR[2:0] in<br>COPCTL Register |

|-----------------------------|-------------------------------|

| 000                         | 111                           |

| 001                         | 110                           |

| 010                         | 101                           |

| 011                         | 100                           |

| 100                         | 011                           |

| 101                         | 010                           |

| 110                         | 001                           |

| 111                         | 000                           |

#### Table 1-14. Initial WCOP Configuration

| NV[3] in<br>FOPT Register | WCOP in<br>COPCTL Register |  |  |

|---------------------------|----------------------------|--|--|

| 1                         | 0                          |  |  |

| 0                         | 1                          |  |  |

# 1.13 ATD External Trigger Input Connection

The ATD module includes external trigger inputs ETRIG0 and ETRIG1. The external trigger allows the user to synchronize ATD conversion to external trigger events. Table 1-15 shows the connection of the external trigger inputs.

| External Trigger<br>Input Connectivity |               |

|----------------------------------------|---------------|

| ETRIG0                                 | PWM channel 1 |

| ETRIG1                                 | PWM channel 3 |

Consult the ATD section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

sgration Module (S12PPIMV1)

| Port | Pin Name                       | Pin Function<br>& Priority <sup>(1)</sup> | I/O                                     | Description                                                                                         | Pin Function<br>after Reset |

|------|--------------------------------|-------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------|

| М    | PM5                            | SCK                                       | I/O                                     | Serial Peripheral Interface serial clock pin                                                        | GPIO                        |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     | -                           |

|      | PM4                            | MOSI                                      | I/O                                     | Serial Peripheral Interface master out/slave in pin                                                 | 7                           |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     |                             |

|      | PM3                            | SS                                        | I/O                                     | Serial Peripheral Interface slave select output in master mode, input in slave mode or master mode. |                             |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     | ]                           |

|      | PM2                            | MISO                                      | I/O                                     | Serial Peripheral Interface master in/slave out pin                                                 | ]                           |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     | ]                           |

|      | PM1 TXCAN O MSCAN transmit pin |                                           | ]                                       |                                                                                                     |                             |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     | ]                           |

|      | PM0                            | RXCAN                                     | I                                       | MSCAN receive                                                                                       |                             |

|      |                                | GPIO                                      | I/O                                     | General purpose                                                                                     |                             |

| Р    | PP7                            | GPIO/KWP7                                 | I/O                                     | General purpose; with interrupt                                                                     | GPIO                        |

|      | PP5                            | PWM5                                      | I/O                                     | Pulse Width Modulator channel 5; emergency shut-down                                                |                             |

|      |                                | GPIO/KWP5                                 | I/O                                     | General purpose; with interrupt                                                                     |                             |

|      | PP[4:0]                        | PWM[4:0]                                  | 0                                       | Pulse Width Modulator channel 4 - 0                                                                 |                             |

|      |                                | GPIO/KWP[4:0]                             | I/O                                     | General purpose; with interrupt                                                                     |                             |

| J    | PJ[7:6]                        | GPIO/KWJ[7:6]                             | :6] I/O General purpose; with interrupt |                                                                                                     | GPIO                        |

|      | PJ[2:0]                        | GPIO/KWJ[2:0]                             | I/O                                     | General purpose; with interrupt                                                                     |                             |

| AD   | PAD[9:0]                       | GPIO                                      | I/O                                     | General purpose                                                                                     | GPIO                        |

|      |                                | AN[9:0]<br>s denote alternative           | Ι                                       | ATD analog                                                                                          |                             |

1. Signals in brackets denote alternative module routing pins.

2. Function active when  $\overline{\text{RESET}}$  asserted.

# 2.3 Memory Map and Register Definition

This section provides a detailed description of all Port Integration Module registers.

# 2.3.1 Memory Map

Table 2-2 shows the register map of the Port Integration Module.

Table 2-2. Block Memory Map

| Port | Offset or<br>Address | Register                                     |     | Reset Value | Section/Page |

|------|----------------------|----------------------------------------------|-----|-------------|--------------|

| A    | 0x0000               | PORTA—Port A Data Register                   |     | 0x00        | 2.3.3/2-63   |

| В    | 0x0001               | PORTB—Port B Data Register                   |     | 0x00        | 2.3.4/2-63   |

|      | 0x0002               | DDRA—Port A Data Direction Register R/W 0x00 |     | 0x00        | 2.3.5/2-64   |

|      | 0x0003               | DDRB—Port B Data Direction Register          | R/W | 0x00        | 2.3.6/2-64   |

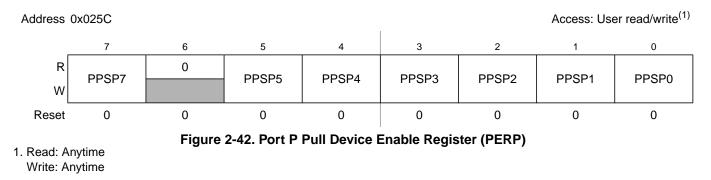

# 2.3.44 Port P Pull Device Enable Register (PERP)

#### Table 2-39. PERP Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,5-0<br>PERP | <ul> <li>Port P pull device enable—Enable pull device on input pin</li> <li>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has no effect. The polarity is selected by the related polarity select register bit.</li> <li>1 Pull device enabled</li> <li>0 Pull device disabled</li> </ul> |

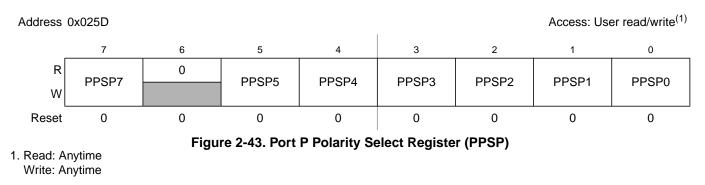

# 2.3.45 Port P Polarity Select Register (PPSP)

#### Table 2-40. PPSP Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                   |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7,5-0<br>PPSP | <b>Port P pull device select</b> —Configure pull device and pin interrupt edge polarity on input pin<br>This bit selects a pull-up or a pull-down device if enabled on the associated port input pin.<br>This bit also selects the polarity of the active pin interrupt edge. |  |

|               | 1 A pull-down device is selected; rising edge selected<br>0 A pull-up device is selected; falling edge selected                                                                                                                                                               |  |

## 2.3.58 Port AD Data Register (PT1AD)

| Address             | 0x0271 |        |        |        |        |        | Access: Use | er read/write <sup>(1)</sup> |

|---------------------|--------|--------|--------|--------|--------|--------|-------------|------------------------------|

|                     | 7      | 6      | 5      | 4      | 3      | 2      | 1           | 0                            |

| R<br>W              | PT1AD7 | PT1AD6 | PT1AD5 | PT1AD4 | PT1AD3 | PT1AD2 | PT1AD1      | PT1AD0                       |

| Altern.<br>Function | AN7    | AN6    | AN5    | AN4    | AN3    | AN2    | AN1         | ANO                          |

| Reset               | 0      | 0      | 0      | 0      | 0      | 0      | 0           | 0                            |

Figure 2-56. Port AD Data Register (PT1AD)

1. Read: Anytime. The data source is depending on the data direction value. Write: Anytime

#### Table 2-52. PT1AD Register Field Descriptions

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | Port AD general purpose input/output data—Data Register, ATD AN analog input                                                                                                    |

| PT1AD | When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin. |

|       | If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.                            |

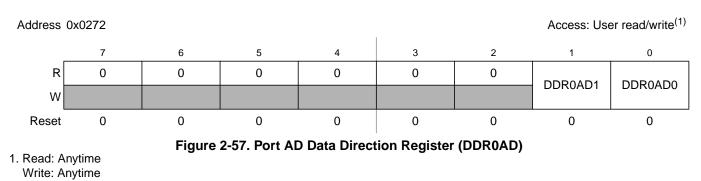

## 2.3.59 Port AD Data Direction Register (DDR0AD)

#### Table 2-53. DDR0AD Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0<br>DDR0AD | <ul> <li>Port AD data direction—</li> <li>This bit determines whether the associated pin is an input or output.</li> <li>To use the digital input function the ATD Digital Input Enable Register (ATDDIEN) has to be set to logic level "1".</li> <li>1 Associated pin is configured as output</li> <li>0 Associated pin is configured as input</li> </ul> |

#### 2.4.2.8 Interrupt enable register (PIEx)

If the pin is used as an interrupt input this register serves as a mask to the interrupt flag to enable/disable the interrupt.

## 2.4.2.9 Interrupt flag register (PIFx)

If the pin is used as an interrupt input this register holds the interrupt flag after a valid pin event.

#### 2.4.2.10 Module routing register (PTTRR)

This register allows software re-configuration of the pinouts of the different package options for specific peripherals:

• PTTRR supports the re-routing of the PWM channels to alternative ports

#### 2.4.3 Pins and Ports

#### NOTE

Please refer to the device pinout section to determine the pin availability in the different package options.

#### 2.4.3.1 BKGD pin

The BKGD pin is associated with the BDM module.

During reset, the BKGD pin is used as MODC input.

#### 2.4.3.2 Port A, B

Port A pins PA[7:0] and Port B pins PB[7:0] can be used for general purpose I/O.

#### 2.4.3.3 Port E

Port E is associated with the free-running clock outputs ECLK, ECLKX2 and interrupt inputs  $\overline{\text{IRQ}}$  and  $\overline{\text{XIRQ}}$ .

Port E pins PE[6:5,3:2] can be used for either general purpose I/O or with the alternative functions.

Port E pin PE[7] an be used for either general purpose I/O or as the free-running clock ECLKX2 output running at the core clock rate.

Port E pin PE[4] an be used for either general purpose I/O or as the free-running clock ECLK output running at the bus clock rate or at the programmed divided clock rate.

Port E pin PE[1] can be used for either general purpose input or as the level- or falling edge-sensitive  $\overline{IRQ}$  interrupt input.  $\overline{IRQ}$  will be enabled by setting the IRQEN configuration bit (2.3.14/2-70) and clearing the I-bit in the CPU condition code register. It is inhibited at reset so this pin is initially configured as a simple input with a pull-up.

- 2-58 I bit maskable interrupt vector requests (at addresses vector base + 0x0082-0x00F2).

- I bit maskable interrupts can be nested.

- One X bit maskable interrupt vector request (at address vector base + 0x00F4).

- One non-maskable software interrupt request (SWI) or background debug mode vector request (at address vector base + 0x00F6).

- One non-maskable unimplemented op-code trap (TRAP) vector (at address vector base + 0x00F8).

- Three system reset vectors (at addresses 0xFFFA–0xFFFE).

- Determines the highest priority interrupt vector requests, drives the vector to the bus on CPU request

- Wakes up the system from stop or wait mode when an appropriate interrupt request occurs.

## 4.1.3 Modes of Operation

• Run mode

This is the basic mode of operation.

• Wait mode

In wait mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from wait mode if an interrupt occurs. Please refer to Section 4.5.3, "Wake Up from Stop or Wait Mode" for details.

• Stop Mode

In stop mode, the clock to the INT module is disabled. The INT module is however capable of waking-up the CPU from stop mode if an interrupt occurs. Please refer to Section 4.5.3, "Wake Up from Stop or Wait Mode" for details.

• Freeze mode (BDM active)

In freeze mode (BDM active), the interrupt vector base register is overridden internally. Please refer to Section 4.3.1.1, "Interrupt Vector Base Register (IVBR)" for details.

## 4.1.4 Block Diagram

Figure 4-1 shows a block diagram of the INT module.

<sup>1.</sup> The vector base is a 16-bit address which is accumulated from the contents of the interrupt vector base register (IVBR, used as upper byte) and 0x00 (used as lower byte).

If the X bit maskable interrupt request is used to wake-up the MCU with the X bit in the CCR set, the associated ISR is not called. The CPU then resumes program execution with the instruction following the WAI or STOP instruction. This features works following the same rules like any interrupt request, that is care must be taken that the X interrupt request used for wake-up remains active at least until the system begins execution of the instruction following the WAI or STOP instruction; otherwise, wake-up may not occur.

clock please make sure that the communication rate is adapted accordingly and a communication time-out (BDM soft reset) has occurred.

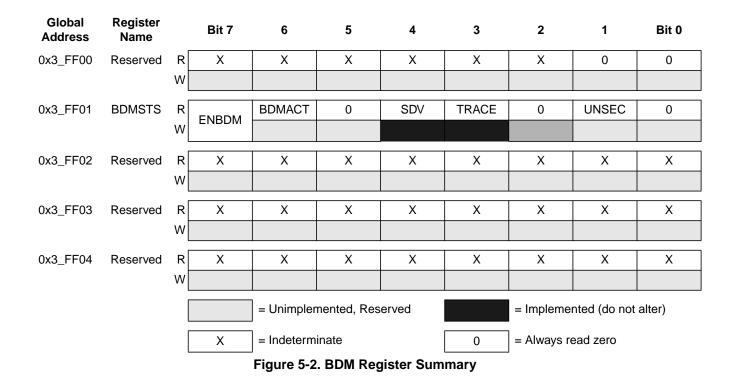

# 5.3 Memory Map and Register Definition

## 5.3.1 Module Memory Map

Table 5-1 shows the BDM memory map when BDM is active.

Table 5-1. BDM Memory Map

| Global Address    | Global Address Module                |     |

|-------------------|--------------------------------------|-----|

| 0x3_FF00-0x3_FF0B | BDM registers                        | 12  |

| 0x3_FF0C-0x3_FF0E | BDM firmware ROM                     | 3   |

| 0x3_FF0F          | Family ID (part of BDM firmware ROM) | 1   |

| 0x3_FF10-0x3_FFFF | BDM firmware ROM                     | 240 |

# 5.3.2 Register Descriptions

A summary of the registers associated with the BDM is shown in Figure 5-2. Registers are accessed by host-driven communications to the BDM hardware using READ\_BD and WRITE\_BD commands.

S12P-Family Reference Manual, Rev. 1.13

ck, Reset and Power Management Unit (S12CPMU)

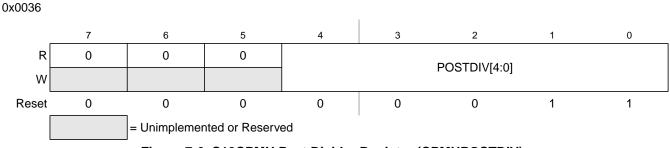

## 7.3.2.3 S12CPMU Post Divider Register (CPMUPOSTDIV)

The POSTDIV register controls the frequency ratio between the VCOCLK and the PLLCLK.

Figure 7-6. S12CPMU Post Divider Register (CPMUPOSTDIV)

Read: Anytime

Write: If PLLSEL=1 write anytime, else write has no effect.

If PLL is locked (LOCK=1)  $f_{PLL} = \frac{f_{VCO}}{(POSTDIV + 1)}$ If PLL is not locked (LOCK=0)  $f_{PLL} = \frac{f_{VCO}}{4}$ If PLL is selected (PLLSEL=1)  $f_{bus} = \frac{f_{PLL}}{2}$

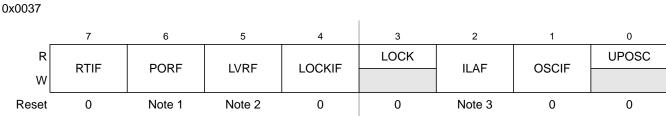

## 7.3.2.4 S12CPMU Flags Register (CPMUFLG)

This register provides S12CPMU status bits and flags.

1. PORF is set to 1 when a power on reset occurs. Unaffected by System Reset.

2. LVRF is set to 1 when a low voltage reset occurs. Unaffected by System Reset. Set by power on reset.

3. ILAF is set to 1 when an illegal address reset occurs. Unaffected by System Reset. Cleared by power on reset.

#### Figure 7-7. S12CPMU Flags Register (CPMUFLG)

Read: Anytime

S12P-Family Reference Manual, Rev. 1.13

## 7.4.6.3 PLL Bypassed External Mode (PBE)

In this mode, the Bus Clock is based on the external oscillator clock. The reference clock for the PLL is based on the external oscillator. The adaptive spike filter and detection logic can be enabled which uses the VCOCLK to filter and qualify the external oscillator clock.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock.

This mode can be entered from default mode PEI by performing the following steps:

- 1. Make sure the PLL configuration is valid

- 2. Optionally the adaptive spike filter and detection logic can be enabled by calculating the integer value for the OSCFIL[4:0] bits and setting the bandwidth (OSCBW) accordingly.

- 3. Enable the external oscillator (OSCE bit)

- 4. Wait for the PLL being locked (LOCK = 1) and the oscillator to start-up and additionally being qualified if the adaptive spike filter is enabled (UPOSC = 1).

- 5. Clear all flags in the CPMUFLG register to be able to detect any status bit change.

- 6. Optionally status interrupts can be enabled (CPMUINT register).

- 7. Select the Oscillator Clock (OSCCLK) as Bus Clock (PLLSEL=0)

Since the adaptive spike filter (filter and detection logic) uses VCOCLK (from PLL) to continuously filter and qualify the external oscillator clock, loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status in PBE mode is as follows:

- PLLSEL is set automatically and the Bus Clock is switched back to the PLLCLK.

- The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

In the PBE mode, not every noise disturbance can be indicated by bits LOCK and UPOSC (both bits are based on the Bus Clock domain). There are clock disturbances possible, after which UPOSC and LOCK both stay asserted while occasional pauses on the filtered OSCCLK and resulting Bus Clock occur. The spike filter is still functional and protects the Bus Clock from frequency overshoot due to spikes on the external oscillator clock. The filtered OSCCLK and resulting Bus Clock will pause until the PLL has stabilized again.

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN9                                                                           |

| 1     | 0     | 1     | 1     | AN9                                                                           |

| 1     | 1     | 0     | 0     | AN9                                                                           |

| 1     | 1     | 0     | 1     | AN9                                                                           |

| 1     | 1     | 1     | 0     | AN9                                                                           |

| 1     | 1     | 1     | 1     | AN9                                                                           |

Table 9-2. Multi-Channel Wrap Around Coding

1. If only AN0 should be converted use MULT=0.

#### 9.3.2.2 **ATD Control Register 1 (ATDCTL1)**

Writes to this register will abort current conversion sequence.

Module Base + 0x0001

| _      | 7        | 6     | 5     | 4       | 3        | 2        | 1        | 0        |

|--------|----------|-------|-------|---------|----------|----------|----------|----------|

| R<br>W | ETRIGSEL | SRES1 | SRES0 | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |

| Reset  | 0        | 0     | 1     | 0       | 1        | 1        | 1        | 1        |

Figure 9-4. ATD Control Register 1 (ATDCTL1)

Read: Anytime

Write: Anytime

#### Table 9-3. ATDCTL1 Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ETRIGSEL    | <b>External Trigger Source Select</b> — This bit selects the external trigger source to be either one of the AD channels or one of the ETRIG3-0 inputs. See device specification for availability and connectivity of ETRIG3-0 inputs. If a particular ETRIG3-0 input option is not available, writing a 1 to ETRISEL only sets the bit but has not effect, this means that one of the AD channels (selected by ETRIGCH3-0) is configured as the source for external trigger. The coding is summarized in Table 9-5. |

| 6–5<br>SRES[1:0] | <b>A/D Resolution Select</b> — These bits select the resolution of A/D conversion results. See Table 9-4 for coding.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Register<br>Name   |        | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

|--------------------|--------|-------|------------|----------------|-------|-------|-------|-------|-------|

| 0x0000<br>PWME     | R<br>W | 0     | 0          | PWME5          | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |

| 0x0001<br>PWMPOL   | R<br>W | 0     | 0          | PPOL5          | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |

| 0x0002<br>PWMCLK   | R<br>W | 0     | 0          | PCLK5          | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |

| 0x0003<br>PWMPRCLK | R<br>W | 0     | PCKB2      | PCKB1          | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |

| 0x0004<br>PWMCAE   | R<br>W | 0     | 0          | CAE5           | CAE4  | CAE2  | CAE2  | CAE1  | CAE0  |

| 0x0005<br>PWMCTL   | R<br>W | 0     | CON45      | CON23          | CON01 | PSWAI | PFRZ  | 0     | 0     |

| 0x0006<br>PWMTST   | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x0007<br>PWMPRSC  | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x0008<br>PWMSCLA  | R<br>W | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0009<br>PWMSCLB  | R<br>W | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| 0x000A<br>PWMSCNTA | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x000B<br>PWMSCNTB | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000C</u>      | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT0            | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000D</u>      | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT1            | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x000E             | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT2            | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000F</u>      | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT3            | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

|                    | [      |       | = Unimpler | nented or Rese | erved |       |       |       |       |

Figure 10-2. PWM Register Summary

Figure 13-25. Flash Reserved7 Register (FRSV7)

All bits in the FRSV7 register read 0 and are not writable.

# 13.4 Functional Description

## 13.4.1 Modes of Operation

The FTMRC128K1 module provides the modes of operation shown in Table 13-25. The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, and DFPROT registers, Scratch RAM writes, and the command set availability (see Table 13-27).

Table 13-25. Modes and Mode Control Inputs

| FTMRC Input    |

|----------------|

| mmc_mode_ss_t2 |

| 0              |

| 1              |

|                |

## 13.4.2 IFR Version ID Word

The version ID word is stored in the IFR at address  $0x0_40B6$ . The contents of the word are defined in Table 13-26.

| Table | 13-26. | IFR | Version | ID | Fields |

|-------|--------|-----|---------|----|--------|

|-------|--------|-----|---------|----|--------|

| [15:4]   | [3:0]  |

|----------|--------|

| Reserved | VERNUM |

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

# 13.4.3 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

#### 13.4.3.3 Valid Flash Module Commands

|      |                              | Unse      | cured             | Secured   |                   |  |

|------|------------------------------|-----------|-------------------|-----------|-------------------|--|

| FCMD | Command                      | NS<br>(1) | SS <sup>(2)</sup> | NS<br>(3) | SS <sup>(4)</sup> |  |

| 0x01 | Erase Verify All Blocks      | *         | *                 | *         | *                 |  |

| 0x02 | Erase Verify Block           | *         | *                 | *         | *                 |  |

| 0x03 | Erase Verify P-Flash Section | *         | *                 | *         |                   |  |

| 0x04 | Read Once                    | *         | *                 | *         |                   |  |

| 0x06 | Program P-Flash              | *         | *                 | *         |                   |  |

| 0x07 | Program Once                 | *         | *                 | *         |                   |  |

| 0x08 | Erase All Blocks             |           | *                 |           | *                 |  |

| 0x09 | Erase Flash Block            | *         | *                 | *         |                   |  |

| 0x0A | Erase P-Flash Sector         | *         | *                 | *         |                   |  |

| 0x0B | Unsecure Flash               |           | *                 |           | *                 |  |

| 0x0C | Verify Backdoor Access Key   | *         |                   | *         |                   |  |

| 0x0D | Set User Margin Level        | *         | *                 | *         |                   |  |

| 0x0E | Set Field Margin Level       |           | *                 |           |                   |  |

| 0x10 | Erase Verify D-Flash Section | *         | *                 | *         |                   |  |

| 0x11 | Program D-Flash              | *         | *                 | *         |                   |  |

| 0x12 | Erase D-Flash Sector         | *         | *                 | *         |                   |  |

Table 13-27. Flash Commands by Mode

1. Unsecured Normal Single Chip mode.

2. Unsecured Special Single Chip mode.

3. Secured Normal Single Chip mode.

4. Secured Special Single Chip mode.

#### 13.4.3.4 P-Flash Commands

Table 13-28 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                          | Function on P-Flash Memory                                                       |

|------|----------------------------------|----------------------------------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks       | Verify that all P-Flash (and D-Flash) blocks are erased.                         |

| 0x02 | Erase Verify Block               | Verify that a P-Flash block is erased.                                           |

| 0x03 | Erase Verify P-<br>Flash Section | Verify that a given number of words starting at the address provided are erased. |

Table 13-28. P-Flash Commands

| CCOBIX[2:0] | FCCOB Parameters     |

|-------------|----------------------|

| 011         | Word 1 program value |

| 100         | Word 2 program value |

| 101         | Word 3 program value |

Table 13-39. Program P-Flash Command FCCOB Requirements

1. Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 13-27)                      |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the global address [17:0] points to a protected area                         |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 13-40. Program P-Flash Command Error Handling

## 13.4.5.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash. The Program Once reserved field can be read using the Read Once command as described in Section 13.4.5.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash cannot be erased. The Program Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters          |                                             |  |  |  |  |  |  |

|-------------|---------------------------|---------------------------------------------|--|--|--|--|--|--|

| 000         | 0x07                      | Not Required                                |  |  |  |  |  |  |

| 001         | Program Once phrase in    | Program Once phrase index (0x0000 - 0x0007) |  |  |  |  |  |  |

| 010         | Program Once word 0 value |                                             |  |  |  |  |  |  |

| 011         | Program Once word 1 value |                                             |  |  |  |  |  |  |

| 100         | Program Once word 2 value |                                             |  |  |  |  |  |  |

| 101         | Program Once word 3 value |                                             |  |  |  |  |  |  |

Table 13-41. Program Once Command FCCOB Requirements

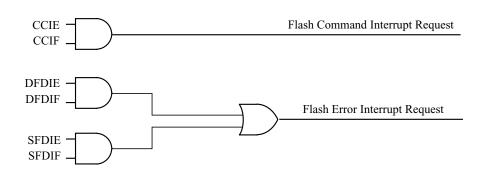

Figure 13-27. Flash Module Interrupts Implementation

## 13.4.7 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 13.4.6, "Interrupts").

## 13.4.8 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

# 13.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 13-10). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x3\_FF0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

## 13.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0x3\_FF00-0x3\_FF07). If the KEYEN[1:0] bits are in the enabled state (see Section 13.3.2.2), the Verify Backdoor Access Key command (see Section 13.4.5.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC

#### **Detailed Register Address Map**

#### 0x0240 -0x027F Port Integration Module (PIM) Map 4 of 4

| Address           | Name     |   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------------------|----------|---|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x0276            | PER0AD0  | R | PER0AD0 |

|                   |          | W | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| 0x0277            | PER1AD0  | R | PER1AD0 |

|                   |          | W | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| 0x0278-<br>0x027F | Reserved | R | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

|                   |          | W |         |         |         |         |         |         |         |         |

#### 0x0280-0x02EF Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0280-<br>0x02EF | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   |          | w |       |       |       |       |       |       |       |       |

#### 0x02F0-0x02FF Clock and Power Management Unit (CPMU) Map 2 of 2

| Address | Name       |            | Bit 7    | Bit 6       | Bit 5  | Bit 4  | Bit 3   | Bit 2       | Bit 1 | Bit 0   |       |       |       |

|---------|------------|------------|----------|-------------|--------|--------|---------|-------------|-------|---------|-------|-------|-------|

| 0x02F0  | CPMUHTCL   | R          | 0        | 0           | VSEL   | 0      | HTEN    | HTDS        | HTIE  | HTIF    |       |       |       |

| 0,021.0 | OFMOTTOE   | W          |          |             |        |        |         |             |       |         |       |       |       |

| 0x02F1  | CPMULVCTL  | R          | 0        | 0           | 0      | 0      | 0       | LVDS        | LVIE  | LVIF    |       |       |       |

| 0/1021  | 0010.1     | W          |          |             |        |        |         |             | 2012  |         |       |       |       |

| 0x02F2  | CPMUAPICTL | R<br>W     | APICLK   | 0           | 0      | APIFES | APIEA   | APIFE       | APIE  | APIF    |       |       |       |

| 0x02F3  | VREGAPITR  | R<br>W     | APITR5   | APITR4      | APITR3 | APITR2 | APITR1  | APITR0      | 0     | 0       |       |       |       |

|         |            | R          |          |             |        |        |         |             |       |         |       |       |       |

| 0x02F4  | CPMUAPIRH  | R<br>W     | APIR15   | APIR14      | APIR13 | APIR12 | APIR11  | APIR10      | APIR9 | APIR8   |       |       |       |

| 0x02F5  | CPMUAPIRL  | R<br>W     | APIR7    | APIR6       | APIR5  | APIR4  | APIR3   | APIR2       | APIR1 | APIR0   |       |       |       |

| 0x02F6  | Reserved   | R          | 0        | 0           | 0      | 0      | 0       | 0           | 0     | 0       |       |       |       |

| 0X02F0  |            | W          |          |             |        |        |         |             |       |         |       |       |       |

| 0x02F7  | CPMUHTTR   |            | CPMUHTTR |             | R      | HTOEN  | 0       | 0           | 0     | HTTR3   | HTTR2 | HTTR1 | HTTR0 |

| 070217  |            | W          | moen     |             |        |        | 111113  | 1111112     |       |         |       |       |       |

| 0x02F8  | CPMU       | R          |          | TCTRIM[3:0] |        |        |         | 0           | IRCTR | IM[9:8] |       |       |       |

|         | IRCTRIMH   | W          |          |             | []     |        |         |             |       | []      |       |       |       |

| 0x02F9  | CPMU       | R          |          |             |        | IRCTR  | IM[7:0] |             |       |         |       |       |       |

|         | IRCTRIML   | W          |          |             | I      |        | []      |             |       |         |       |       |       |

| 0x02FA  | CPMUOSC    | R          | OSCE     | OSCBW       | 0      |        | (       | DSCFILT[4:0 | 1     |         |       |       |       |

| 0x02FB  |            | W          |          |             |        |        |         |             |       |         |       |       |       |

|         | CPMUPROT   | B CPMUPROT | R        | 0           | 0      | 0      | 0       | 0           | 0     | 0       | PROT  |       |       |

| 0x02FC  |            | W          | 0        | 0           | 0      | 0      | 0       | 0           | 0     |         |       |       |       |

|         | Reserved   | R          | 0        | 0           | 0      | 0      | 0       | 0           | 0     | 0       |       |       |       |

|         |            | W          |          |             |        |        |         |             |       |         |       |       |       |