Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 32MHz                                                                |

| Connectivity               | CANbus, SCI, SPI                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 34                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 4K x 8                                                               |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                         |

| Data Converters            | A/D 10x12b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-TFQFN Exposed Pad                                                 |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12p64cft |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1Device Overview MC9S12P-Family

| 1.1  | Introduction                                       | 17 |

|------|----------------------------------------------------|----|

| 1.2  | Features                                           | 17 |

|      | 1.2.1 MC9S12P Family Comparison                    | 18 |

|      | 1.2.2 Chip-Level Features                          | 18 |

| 1.3  | Module Features                                    | 19 |

|      | 1.3.1 S12 16-Bit Central Processor Unit (CPU)      | 19 |

|      | 1.3.2 On-Chip Flash with ECC                       | 19 |

|      | 1.3.3 On-Chip SRAM                                 | 20 |

|      | 1.3.4 Main External Oscillator (XOSC)              | 20 |

|      | 1.3.5 Internal RC Oscillator (IRC)                 | 20 |

|      | 1.3.6 Internal Phase-Locked Loop (IPLL)            | 20 |

|      | 1.3.7 System Integrity Support                     | 20 |

|      | 1.3.8 Timer (TIM)                                  | 21 |

|      | 1.3.9 Pulse Width Modulation Module (PWM)          | 21 |

|      | 1.3.10 Controller Area Network Module (MSCAN)      | 21 |

|      | 1.3.11 Serial Communication Interface Module (SCI) | 21 |

|      | 1.3.12 Serial Peripheral Interface Module (SPI)    | 22 |

|      | 1.3.13 Analog-to-Digital Converter Module (ATD)    | 22 |

|      | 1.3.14 On-Chip Voltage Regulator (VREG)            | 22 |

|      | 1.3.15 Background Debug (BDM)                      | 22 |

|      | 1.3.16 Debugger (DBG)                              |    |

| 1.4  | Block Diagram                                      | 24 |

| 1.5  | Device Memory Map                                  | 25 |

| 1.6  | Part ID Assignments                                | 28 |

| 1.7  | Signal Description                                 | 28 |

|      | 1.7.1 Device Pinout                                | 29 |

|      | 1.7.2 Pin Assignment Overview                      | 31 |

|      | 1.7.3 Detailed Signal Descriptions                 | 38 |

|      | 1.7.4 Power Supply Pins                            | 41 |

| 1.8  | System Clock Description                           | 42 |

| 1.9  | Modes of Operation                                 | 42 |

|      | 1.9.1 Chip Configuration Summary                   |    |

|      | 1.9.2 Low Power Operation                          | 14 |

| 1.10 | Security                                           | 14 |

| 1.11 | Resets and Interrupts                              | 14 |

|      | 1.11.1 Resets                                      | 14 |

|      | 1.11.2 Interrupt Vectors                           | 14 |

|      | 1.11.3 Effects of Reset                            | 46 |

|      | COP Configuration                                  |    |

| 1.13 | ATD External Trigger Input Connection              | 17 |

|      |                                                    |    |

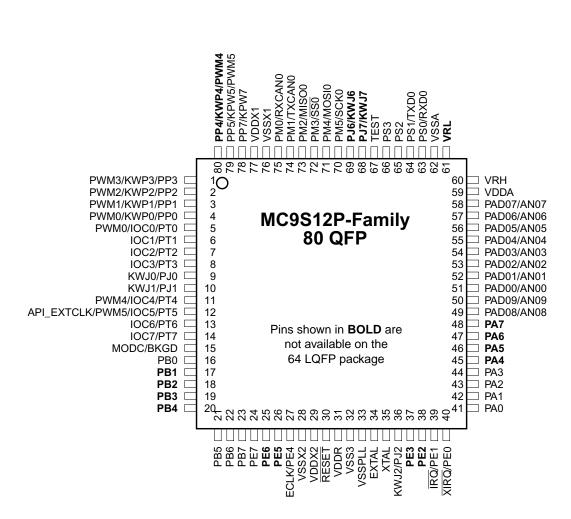

Figure 1-3. MC9S12P-Family 80 QFP pinout

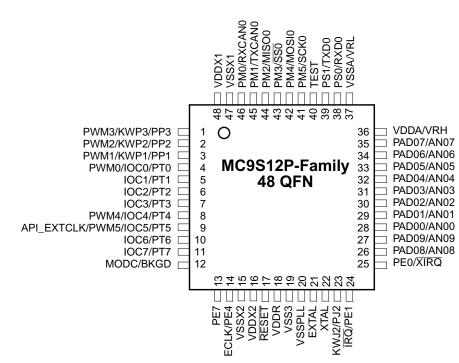

### Figure 1-5. MC9S12P-Family 48 QFN pinout

### 1.7.2 Pin Assignment Overview

Table 1-6 provides a summary of which Ports are available for each package option. Routing of pin functions is summarized in Table 1-7.

| Port                                 | 80 QFP | 64 LQFP | 48 QFN |

|--------------------------------------|--------|---------|--------|

| Port AD/ADC Channels                 | 10/10  | 10/10   | 10/10  |

| Port A pins                          | 8      | 4       | 0      |

| Port B pins                          | 8      | 4       | 0      |

| Port E pins inc. IRQ/XIRQ input only | 8      | 4       | 4      |

| Port J                               | 5      | 3       | 1      |

| Port M                               | 6      | 6       | 6      |

| Port P                               | 7      | 6       | 3      |

| Port S                               | 4      | 4       | 2      |

Table 1-6. Port Availability by Package Option

| Register<br>Name                                                                                         |                                                                                             | Bit 7                 | 6                     | 5                      | 4                      | 3                                    | 2                                    | 1                                    | Bit 0                                     |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------|-----------------------|------------------------|------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------|

| 0x0020–<br>0x023F<br>Non-PIM<br>Address<br>Range                                                         | R<br>W                                                                                      |                       |                       |                        | Non-PIM Add            | dress Range                          |                                      |                                      |                                           |

| 0x0240<br>PTT                                                                                            | R<br>W                                                                                      | PTT7                  | PTT6                  | PTT5                   | PTT4                   | PTT3                                 | PTT2                                 | PTT1                                 | PTT0                                      |

| Ox0241<br>PTIT                                                                                           | R<br>W                                                                                      | PTIT7                 | PTIT6                 | PTIT5                  | PTIT4                  | PTIT3                                | PTIT2                                | PTIT1                                | PTIT0                                     |

| 0x0242<br>DDRT                                                                                           | R<br>W                                                                                      | DDRT7                 | DDRT6                 | DDRT5                  | DDRT4                  | DDRT3                                | DDRT2                                | DDRT1                                | DDRT0                                     |

| 0x0243<br>RDRT                                                                                           | R<br>W                                                                                      | RDRT7                 | RDRT6                 | RDRT5                  | RDRT4                  | RDRT3                                | RDRT2                                | RDRT1                                | RDRT0                                     |

| 0x0244<br>PERT                                                                                           | R<br>W                                                                                      | PERT7                 | PERT6                 | PERT5                  | PERT4                  | PERT3                                | PERT2                                | PERT1                                | PERT0                                     |

| 0x0245<br>PPST                                                                                           | R<br>W                                                                                      | PPST7                 | PPST6                 | PPST5                  | PPST4                  | PPST3                                | PPST2                                | PPST1                                | PPST0                                     |

| <u>0x0246</u>                                                                                            | R                                                                                           | 0                     | 0                     | 0                      | 0                      | 0                                    | 0                                    | 0                                    | 0                                         |

| Reserved                                                                                                 |                                                                                             |                       |                       | Ŭ                      | 0                      | 0                                    | 0                                    | ÿ                                    | Ŭ                                         |

| Reserved<br>0x0247<br>PTTRR                                                                              |                                                                                             | 0                     | 0                     | • PTTRR5               | PTTRR4                 | 0                                    | 0                                    | 0                                    | PTTRR0                                    |

| 0x0247                                                                                                   | W<br>R                                                                                      |                       |                       |                        |                        |                                      |                                      |                                      |                                           |

| 0x0247<br>PTTRR<br>0x0248                                                                                | W<br>R<br>W<br>R                                                                            | 0                     | 0                     | PTTRR5                 | PTTRR4                 | 0                                    | 0                                    | 0                                    | PTTRR0                                    |

| 0x0247<br>PTTRR<br>0x0248<br>PTS<br>0x0249                                                               | W<br>R<br>W<br>R<br>W                                                                       | 0                     | 0                     | PTTRR5                 | PTTRR4                 | 0<br>PTS3                            | 0<br>PTS2                            | 0<br>PTS1                            | PTTRR0<br>PTS0                            |

| 0x0247<br>PTTRR<br>0x0248<br>PTS<br>0x0249<br>PTIS<br>0x024A                                             | W<br>R<br>W<br>R<br>W<br>R<br>R                                                             | 0 0 0 0               | 0                     | PTTRR5                 | PTTRR4<br>0<br>0       | 0<br>PTS3<br>PTIS3                   | 0<br>PTS2<br>PTIS2                   | 0<br>PTS1<br>PTIS1                   | PTTRR0<br>PTS0<br>PTIS0                   |

| 0x0247<br>PTTRR<br>0x0248<br>PTS<br>0x0249<br>PTIS<br>0x024A<br>DDRS<br>0x024B                           | W<br>R<br>W<br>R<br>W<br>R<br>W<br>R                                                        | 0 0 0 0 0 0 0         | 0                     | PTTRR5 0 0 0 0         | PTTRR4<br>0<br>0       | 0<br>PTS3<br>PTIS3<br>DDRS3          | 0<br>PTS2<br>PTIS2<br>DDRS2          | 0<br>PTS1<br>PTIS1<br>DDRS1          | PTTRR0<br>PTS0<br>PTIS0<br>DDRS0          |

| 0x0247<br>PTTRR<br>0x0248<br>PTS<br>0x0249<br>PTIS<br>0x024A<br>DDRS<br>0x024A<br>DDRS<br>0x024B<br>RDRS | W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W<br>R<br>W | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0 | PTTRR5 0 0 0 0 0 0 0 0 | PTTRR4 0 0 0 0 0 0 0 0 | 0<br>PTS3<br>PTIS3<br>DDRS3<br>RDRS3 | 0<br>PTS2<br>PTIS2<br>DDRS2<br>RDRS2 | 0<br>PTS1<br>PTIS1<br>DDRS1<br>RDRS1 | PTTRR0<br>PTS0<br>PTIS0<br>DDRS0<br>RDRS0 |

### Table 2-29. PTIM Register Field Descriptions

| Field | Description                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0   | Port M input data—                                                                                                                                  |

| PTIM  | A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

## 2.3.34 Port M Data Direction Register (DDRM)

Access: User read/write<sup>(1)</sup>

|       | 7 | 6 | 5       | 4       | 3       | 2      | 1      | 0       |

|-------|---|---|---------|---------|---------|--------|--------|---------|

| R     | 0 | 0 | DDRM5   | DDRM4   | DDRM3   | DDRM2  | DDRM1  | DDRM0   |

| w     |   |   | DDRIVIS | DDRIVI4 | DDRIVIS | DDRIMZ | DURINI | DDRIVIO |

| Reset | 0 | 0 | 0       | 0       | 0       | 0      | 0      | 0       |

Figure 2-32. Port M Data Direction Register (DDRM)

1. Read: Anytime Write: Anytime

### Table 2-30. DDRM Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>DDRM | Port M data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SPI the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|           | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

| 4<br>DDRM | Port M data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SPI the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|           | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

| 3<br>DDRM | Port M data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SPI the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|           | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

If the X bit maskable interrupt request is used to wake-up the MCU with the X bit in the CCR set, the associated ISR is not called. The CPU then resumes program execution with the instruction following the WAI or STOP instruction. This features works following the same rules like any interrupt request, that is care must be taken that the X interrupt request used for wake-up remains active at least until the system begins execution of the instruction following the WAI or STOP instruction; otherwise, wake-up may not occur.

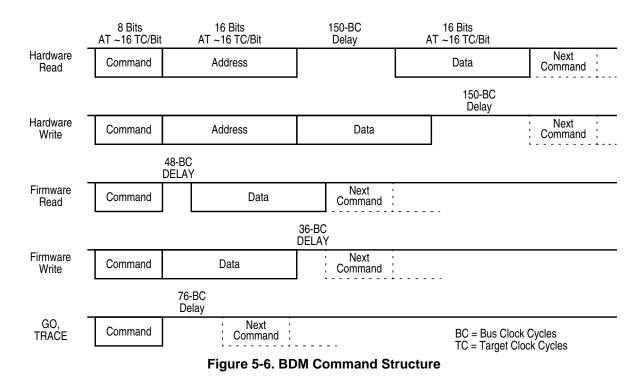

## 5.4.6 BDM Serial Interface

The BDM communicates with external devices serially via the BKGD pin. During reset, this pin is a mode select input which selects between normal and special modes of operation. After reset, this pin becomes the dedicated serial interface pin for the BDM.

The BDM serial interface is timed based on the VCO clock (please refer to the CPMU Block Guide for more details), which gets divided by 8. This clock will be referred to as the target clock in the following explanation.

The BDM serial interface uses a clocking scheme in which the external host generates a falling edge on the BKGD pin to indicate the start of each bit time. This falling edge is sent for every bit whether data is transmitted or received. Data is transferred most significant bit (MSB) first at 16 target clock cycles per bit. The interface times out if 512 clock cycles occur between falling edges from the host.

The BKGD pin is a pseudo open-drain pin and has an weak on-chip active pull-up that is enabled at all times. It is assumed that there is an external pull-up and that drivers connected to BKGD do not typically drive the high level. Since R-C rise time could be unacceptably long, the target system and host provide brief driven-high (speedup) pulses to drive BKGD to a logic 1. The source of this speedup pulse is the host for transmit cases and the target for receive cases.

The timing for host-to-target is shown in Figure 5-7 and that of target-to-host in Figure 5-8 and Figure 5-9. All four cases begin when the host drives the BKGD pin low to generate a falling edge. Since the host and target are operating from separate clocks, it can take the target system up to one full clock cycle to recognize this edge. The target measures delays from this perceived start of the bit time while the host measures delays from the point it actually drove BKGD low to start the bit up to one target clock cycle

#### >bug Module (S12SDBGV2)

SZ bits allow the size of access (word or byte) to be considered in the compare. Only comparators A and B feature SZE and SZ.

The TAG bit in each comparator control register is used to determine the match condition. By setting TAG, the comparator qualifies a match with the output of opcode tracking logic and a state sequencer transition occurs when the tagged instruction reaches the CPU execution stage. Whilst tagging the RW, RWE, SZE, and SZ bits and the comparator data registers are ignored; the comparator address register must be loaded with the exact opcode address.

If the TAG bit is clear (forced type match) a comparator match is generated when the selected address appears on the system address bus. If the selected address is an opcode address, the match is generated when the opcode is fetched from the memory, which precedes the instruction execution by an indefinite number of cycles due to instruction pipelining. For a comparator match of an opcode at an odd address when TAG = 0, the corresponding even address must be contained in the comparator register. Thus for an opcode at odd address (n), the comparator register must contain address (n-1).

Once a successful comparator match has occurred, the condition that caused the original match is not verified again on subsequent matches. Thus if a particular data value is verified at a given address, this address may not still contain that data value when a subsequent match occurs.

Match[0, 1, 2] map directly to Comparators [A, B, C] respectively, except in range modes (see 6.3.2.4). Comparator channel priority rules are described in the priority section (6.4.3.4).

#### 6.4.2.1 Single Address Comparator Match

With range comparisons disabled, the match condition is an exact equivalence of address bus with the value stored in the comparator address registers. Further qualification of the type of access (R/W, word/byte) and databus contents is possible, depending on comparator channel.

#### 6.4.2.1.1 **Comparator C**

Comparator C offers only address and direction (R/W) comparison. The exact address is compared, thus with the comparator address register loaded with address (n) a word access of address (n-1) also accesses (n) but does not cause a match.

| Condition For Valid Match          | Comp C Address         | RWE | RW | Examples                             |

|------------------------------------|------------------------|-----|----|--------------------------------------|

| Read and write accesses of ADDR[n] | ADDR[n] <sup>(1)</sup> | 0   | Х  | LDAA ADDR[n]<br>STAA #\$BYTE ADDR[n] |

| Write accesses of ADDR[n]          | ADDR[n]                | 1   | 0  | STAA #\$BYTE ADDR[n]                 |

| Read accesses of ADDR[n]           | ADDR[n]                | 1   | 1  | LDAA #\$BYTE ADDR[n]                 |

Table 6-32. Comparator C Access Considerations

1. A word access of ADDR[n-1] also accesses ADDR[n] but does not generate a match. The comparator address register must contain the exact address from the code.

#### 6.4.2.1.2 **Comparator B**

Comparator B offers address, direction (R/W) and access size (word/byte) comparison. If the SZE bit is set the access size (word or byte) is compared with the SZ bit value such that only the specified size of

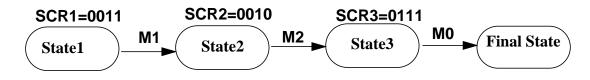

# 6.5.2 Scenario 1

A trigger is generated if a given sequence of 3 code events is executed.

Figure 6-27. Scenario 1

Scenario 1 is possible with S12SDBGV1 SCR encoding

# 6.5.3 Scenario 2

A trigger is generated if a given sequence of 2 code events is executed.

Figure 6-28. Scenario 2a

A trigger is generated if a given sequence of 2 code events is executed, whereby the first event is entry into a range (COMPA,COMPB configured for range mode). M1 is disabled in range modes.

A trigger is generated if a given sequence of 2 code events is executed, whereby the second event is entry into a range (COMPA,COMPB configured for range mode)

All 3 scenarios 2a,2b,2c are possible with the S12SDBGV1 SCR encoding

S12P-Family Reference Manual, Rev. 1.13

#### ck, Reset and Power Management Unit (S12CPMU)

### 7.3.2.8 S12CPMU RTI Control Register (CPMURTI)

This register selects the time-out period for the Real Time Interrupt.

The clock source for the RTI is either IRCCLK or OSCCLK depending on the setting of the RTIOSCSEL bit. In Stop Mode with PSTP=1 (Pseudo Stop Mode) and RTIOSCSEL=1 the RTI continues to run, else the RTI counter halts in Stop Mode.

0x003B

|        | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|-------|------|------|------|------|------|------|------|

| R<br>W | RTDEC | RTR6 | RTR5 | RTR4 | RTR3 | RTR2 | RTR1 | RTR0 |

| Reset  | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Figure 7-11. S12CPMU RTI Control Register (CPMURTI)

Read: Anytime

Write: Anytime

### NOTE

A write to this register starts the RTI time-out period. A change of the RTIOSCSEL bit (writing a different value or loosing UPOSC status) re-starts the RTI time-out period.

| Field           | Description                                                                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTDEC      | <ul> <li>Decimal or Binary Divider Select Bit — RTDEC selects decimal or binary based prescaler values.</li> <li>0 Binary based divider value. See Table 7-9</li> <li>1 Decimal based divider value. See Table 7-10</li> </ul>              |

| 6–4<br>RTR[6:4] | <b>Real Time Interrupt Prescale Rate Select Bits</b> — These bits select the prescale rate for the RTI. See Table 7-9 and Table 7-10.                                                                                                       |

| 3–0<br>RTR[3:0] | <b>Real Time Interrupt Modulus Counter Select Bits</b> — These bits select the modulus counter target value to provide additional granularity. Table 7-9 and Table 7-10 show all possible divide values selectable by the CPMURTI register. |

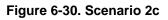

### Figure 7-19. Waveform selected on API\_EXTCLK pin (APIEA=1, APIFE=1)

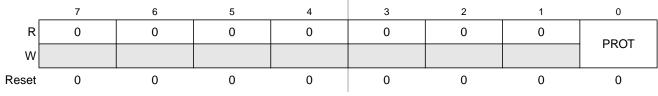

## 7.3.2.22 S12CPMU Protection Register (CPMUPROT)

This register protects the clock configuration registers from accidental overwrite:

CPMUSYNR, CPMUREFDIV, CPMUCLKS, CPMUPLL, CPMUIRCTRIMH/L and CPMUOSC

### 0x02FB

Figure 7-29. S12CPMU Protection Register (CPMUPROT)

Read: Anytime

Write: Anytime

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>PROT | <ul> <li>Clock Configuration Registers Protection Bit — This bit protects the clock configuration registers from accidental overwrite (see list of affected registers above).</li> <li>Writing 0x26 to the CPMUPROT register clears the PROT bit, other write accesses set the PROT bit.</li> <li>Protection of clock configuration registers is disabled.</li> <li>Protection of clock configuration registers is enabled. CPMUSYNR, CPMUREFDIV, CPMUCLKS, CPMUPLL, CPMUIRCTRIMH/L and CPMUOSC registers are not writable.</li> </ul> |

# 7.4.6 System Clock Configurations

## 7.4.6.1 PLL Engaged Internal Mode (PEI)

This mode is the default mode after System Reset or Power-On Reset.

The Bus Clock is based on the PLLCLK, the reference clock for the PLL is internally generated (IRC1M). The PLL is configured to 64 MHz VCOCLK with POSTDIV set to 0x03. If locked (LOCK=1) this results in a PLLCLK of 16 MHz and a Bus Clock of 8 MHz. The PLL can be re-configured to other bus frequencies.

The clock sources for COP and RTI are based on the internal reference clock generator (IRC1M).

## 7.4.6.2 PLL Engaged External Mode (PEE)

In this mode, the Bus Clock is based on the PLLCLK as well (like PEI). The reference clock for the PLL is based on the external oscillator. The adaptive spike filter and detection logic which uses the VCOCLK to filter and qualify the external oscillator clock can be enabled.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock.

This mode can be entered from default mode PEI by performing the following steps:

- 1. Configure the PLL for desired bus frequency.

- 2. Optionally the adaptive spike filter and detection logic can be enabled by calculating the integer value for the OSCFIL[4:0] bits and setting the bandwidth (OSCBW) accordingly.

- 3. Enable the external oscillator (OSCE bit).

- 4. Wait for the PLL being locked (LOCK = 1) and the oscillator to start-up and additionally being qualified if the adaptive spike filter is enabled (UPOSC = 1).

- 5. Clear all flags in the CPMUFLG register to be able to detect any future status bit change.

- 6. Optionally status interrupts can be enabled (CPMUINT register).

Since the adaptive spike filter (filter and detection logic) uses the VCOCLK to continuously filter and qualify the external oscillator clock, loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status in PEE mode is as follows:

• The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

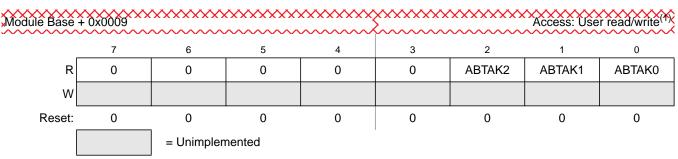

### 8.3.2.10 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register.

Figure 8-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK) 1. Read: Anytime

Write: Unimplemented

### NOTE

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

### Table 8-16. CANTAAK Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2-0<br>ABTAK[2:0] | <ul> <li>Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.</li> <li>0 The message was not aborted.</li> <li>1 The message was aborted.</li> </ul> |  |  |

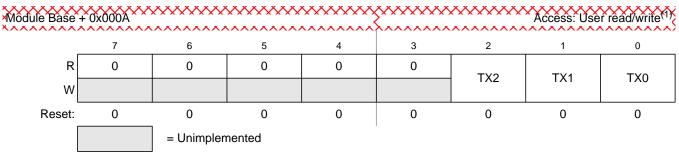

### 8.3.2.11 MSCAN Transmit Buffer Selection Register (CANTBSEL)

The CANTBSEL register allows the selection of the actual transmit message buffer, which then will be accessible in the CANTXFG register space.

### Figure 8-14. MSCAN Transmit Buffer Selection Register (CANTBSEL)

1. Read: Find the lowest ordered bit set to 1, all other bits will be read as 0 Write: Anytime when not in initialization mode

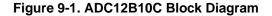

#### ICLK Bus Clock Internal Clock ATD\_12B10C Clock Prescaler ATD Clock Sequence Complete ETRIGO Trigger Interrupt Mux ETRIG1 Mode and ETRIG2 **Compare Interrupt Timing Control** ETRIG3 1 (See device specification for availability and connectivity) ATDCTL1 ATDDIEN Results ATD 0 ATD 1 ATD 2 ATD 3 ATD 4 VSSA ATD 5 Successive ATD 6 V<sub>RH</sub> Approximation ATD 7 V<sub>RL</sub> ATD 8 Register (SAR) ATD 9 and DAC Sample & Hold AN9 🛛 AN8 🛛 Comparator Analog MUX AN7 AN6 🛛 AN5 🖾 AN4 🖾 AN3 🛛 AN2 🛛 AN1 🛛 ANO 🛛

### 9.1.3 Block Diagram

S12P-Family Reference Manual, Rev. 1.13

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ASCIE  | <ul> <li>ATD Sequence Complete Interrupt Enable</li> <li>0 ATD Sequence Complete interrupt requests are disabled.</li> <li>1 ATD Sequence Complete interrupt will be requested whenever SCF=1 is set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>ACMPIE | <ul> <li>ATD Compare Interrupt Enable — If automatic compare is enabled for conversion <i>n</i> (CMPE[<i>n</i>]=1 in ATDCMPE register) this bit enables the compare interrupt. If the CCF[<i>n</i>] flag is set (showing a successful compare for conversion <i>n</i>), the compare interrupt is triggered.</li> <li>0 ATD Compare interrupt requests are disabled.</li> <li>1 For the conversions in a sequence for which automatic compare is enabled (CMPE[<i>n</i>]=1), ATD Compare Interrupt will be requested whenever any of the respective CCF flags is set.</li> </ul> |

| ETRIGLE | ETRIGP | External Trigger Sensitivity |

|---------|--------|------------------------------|

| 0       | 0      | Falling edge                 |

| 0       | 1      | Rising edge                  |

| 1       | 0      | Low level                    |

| 1       | 1      | High level                   |

Table 9-7. External Trigger Configurations

## 9.3.2.4 ATD Control Register 3 (ATDCTL3)

Writes to this register will abort current conversion sequence.

Module Base + 0x0003

### Figure 9-6. ATD Control Register 3 (ATDCTL3)

Read: Anytime

Write: Anytime

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                             |

|          |           | Set if an invalid global address [17:16] is supplied                    |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

Table 13-34. Erase Verify Block Command Error Handling

### 13.4.5.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

Table 13-35. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |

|-------------|----------------------------------------------------------|----------------------------------------------|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |

| 010         | Number of phrases to be verified                         |                                              |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                              |

|----------|-----------|------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                                  |

|          |           | Set if command not available in current mode (see Table 13-27)               |

|          |           | Set if an invalid global address [17:0] is supplied                          |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000) |

| FSIAI    |           | Set if the requested section crosses a 128 Kbyte boundary                    |

|          | FPVIOL    | None                                                                         |

|          | MGSTAT1   | Set if any errors have been encountered during the read                      |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read      |

Table 13-36. Erase Verify P-Flash Section Command Error Handling

### 13.4.5.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once

# A.3 NVM

# A.3.1 Timing Parameters

The time base for all NVM program or erase operations is derived from the bus clock using the FCLKDIV register. The frequency of this derived clock must be set within the limits specified as  $f_{NVMOP}$ . The NVM module does not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. When attempting to program or erase the NVM module at a lower frequency, a full program or erase transition is not assured.

The following sections provide equations which can be used to determine the time required to execute specific flash commands. All timing parameters are a function of the bus clock frequency,  $f_{NVMBUS}$ . All program and erase times are also a function of the NVM operating frequency,  $f_{NVMOP}$ . A summary of key timing parameters can be found in Table A-18.

# A.3.1.1 Erase Verify All Blocks (Blank Check) (FCMD=0x01)

The time required to perform a blank check on all blocks is dependent on the location of the first non-blank word starting at relative address zero. It takes one bus cycle per phrase to verify plus a setup of the command. Assuming that no non-blank location is found, then the time to erase verify all blocks is given by:

$t_{check} = 35500 \cdot \frac{1}{f_{NVMBUS}}$

# A.3.1.2 Erase Verify Block (Blank Check) (FCMD=0x02)

The time required to perform a blank check is dependent on the location of the first non-blank word starting at relative address zero. It takes one bus cycle per phrase to verify plus a setup of the command.

Assuming that no non-blank location is found, then the time to erase verify a P-Flash block is given by:

$$t_{pcheck} = 33500 \cdot \frac{1}{f_{NVMBUS}}$$

Assuming that no non-blank location is found, then the time to erase verify a D-Flash block is given by:

$$t_{dcheck} = 2800 \cdot \frac{1}{f_{NVMBUS}}$$

#### How to Reach Us:

#### USA/Europe/Locations not listed:

Freescale Semiconductor Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor H.K. Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong 852-26668334

#### Learn More:

For more information about Freescale Semiconductor products, please visit http://www.freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2010