#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 32MHz                                                                |

| Connectivity               | CANbus, SCI, SPI                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 49                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 4K x 8                                                               |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                         |

| Data Converters            | A/D 10x12b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12p64vlh |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Part ID Assignments** 1.6

The part ID is located in two 8-bit registers PARTIDH and PARTIDL (addresses 0x001A and 0x001B). The read-only value is a unique part ID for each revision of the chip. Table 1-5 shows the assigned part ID number and Mask Set number.

The Version ID in Table 1-5. is a word located in a flash information row. The version ID number indicates a specific version of internal NVM controller.

| Device     | Mask Set Number | Part ID <sup>(1)</sup> | Version ID |

|------------|-----------------|------------------------|------------|

| MC9S12P128 | 0M01N           | \$3980                 | \$FF       |

| MC9S12P96  | 0M01N           | \$3980                 | \$FF       |

| MC9S12P64  | 0M01N           | \$3980                 | \$FF       |

| MC9S12P32  | 0M01N           | \$3980                 | \$FF       |

Table 1-5. Assigned Part ID Numbers

The coding is as follows:

Bit 15-12: Major family identifier

Bit 11-6: Minor family identifier

Bit 5-4: Major mask set revision number including FAB transfers

Bit 3-0: Minor — non full — mask set revision

#### 1.7 **Signal Description**

This section describes signals that connect off-chip. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals. It is built from the signal description sections of the individual IP blocks on the device.

# 1.9.1 Chip Configuration Summary

The different modes and the security state of the MCU affect the debug features (enabled or disabled).

The operating mode out of reset is determined by the state of the MODC signal during reset (see Table 1-10). The MODC bit in the MODE register shows the current operating mode and provides limited mode switching during operation. The state of the MODC signal is latched into this bit on the rising edge of RESET.

| Table 1-1 | 0. Chip | Modes |

|-----------|---------|-------|

|-----------|---------|-------|

| Chip Modes          | MODC |

|---------------------|------|

| Normal single chip  | 1    |

| Special single chip | 0    |

## 1.9.1.1 Normal Single-Chip Mode

This mode is intended for normal device operation. The opcode from the on-chip memory is being executed after reset (requires the reset vector to be programmed correctly). The processor program is executed from internal memory.

## 1.9.1.2 Special Single-Chip Mode

This mode is used for debugging single-chip operation, boot-strapping, or security related operations. The background debug module BDM is active in this mode. The CPU executes a monitor program located in an on-chip ROM. BDM firmware waits for additional serial commands through the BKGD pin.

| egister<br>Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | Bit 7                 | 6           | 5          | 4                   | 3                         | 2          | 1     | Bit 0         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|------------|---------------------|---------------------------|------------|-------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | 0                     | 0           | 0          | 0                   | 0                         | 0          | 0     | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | 0                     | 0           | 0          | 0                   | 0                         | 0          | 0     | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | 0                     | 0           | 0          | 0                   | 0                         | 0          | 0     | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | 0                     | 0           | 0          | 0                   | 0                         | 0          | 0     | 0             |

| ODTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R<br>W           | PE7                   | PE6         | PE5        | PE4                 | PE3                       | PE2        | PE1   | PE0           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | DDRE7                 | DDRE6       | DDRE5      | DDRE4               | DDRE3                     | DDRE2      | 0     | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R<br>W           | Non-PIM Address Range |             |            |                     |                           |            |       |               |

| Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                       |             |            |                     |                           |            |       |               |

| Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R                | 0                     | BKPUE       | 0          | PUPEE               | 0                         | 0          | PUPBE | PUPAE         |

| Range<br>0x000C<br>PUCR \<br>0x000D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | 0                     | BKPUE       | 0          | PUPEE               | 0                         | 0          | PUPBE | PUPAE<br>RDPA |

| Range<br><u>)x000C</u><br><u>PUCR</u><br><u>)x000D</u><br>RDRIV<br><u>x000E–</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | w<br>R           |                       |             |            |                     | 0                         |            |       |               |

| Range<br>X000C<br>PUCR<br>X000D<br>RDRIV<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X0                                                 | N<br>R<br>N<br>R |                       |             |            | RDPE                | 0                         |            |       |               |

| Range<br>X000C<br>PUCR<br>X000D<br>RDRIV<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X000E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X00E-<br>X                                                 |                  | 0                     | 0           | 0          | RDPE<br>Non-PIM Add | 0<br>dress Range          | 0          | RDPB  | RDPA          |

| Range<br>PUCR \<br>PUCR \<br>x000D<br>RDRIV \<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x000E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x00E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x0E-<br>x | W<br>R<br>R<br>R | 0<br>NECLK            | 0<br>NCLKX2 | 0<br>DIV16 | RDPE<br>Non-PIM Ada | 0<br>dress Range<br>EDIV3 | 0<br>EDIV2 | EDIV1 | RDPA<br>EDIV0 |

S12P-Family Reference Manual, Rev. 1.13

egration Module (S12PPIMV1)

## 2.4.2.8 Interrupt enable register (PIEx)

If the pin is used as an interrupt input this register serves as a mask to the interrupt flag to enable/disable the interrupt.

## 2.4.2.9 Interrupt flag register (PIFx)

If the pin is used as an interrupt input this register holds the interrupt flag after a valid pin event.

## 2.4.2.10 Module routing register (PTTRR)

This register allows software re-configuration of the pinouts of the different package options for specific peripherals:

• PTTRR supports the re-routing of the PWM channels to alternative ports

## 2.4.3 Pins and Ports

## NOTE

Please refer to the device pinout section to determine the pin availability in the different package options.

## 2.4.3.1 BKGD pin

The BKGD pin is associated with the BDM module.

During reset, the BKGD pin is used as MODC input.

## 2.4.3.2 Port A, B

Port A pins PA[7:0] and Port B pins PB[7:0] can be used for general purpose I/O.

## 2.4.3.3 Port E

Port E is associated with the free-running clock outputs ECLK, ECLKX2 and interrupt inputs  $\overline{\text{IRQ}}$  and  $\overline{\text{XIRQ}}$ .

Port E pins PE[6:5,3:2] can be used for either general purpose I/O or with the alternative functions.

Port E pin PE[7] an be used for either general purpose I/O or as the free-running clock ECLKX2 output running at the core clock rate.

Port E pin PE[4] an be used for either general purpose I/O or as the free-running clock ECLK output running at the bus clock rate or at the programmed divided clock rate.

Port E pin PE[1] can be used for either general purpose input or as the level- or falling edge-sensitive  $\overline{IRQ}$  interrupt input.  $\overline{IRQ}$  will be enabled by setting the IRQEN configuration bit (2.3.14/2-70) and clearing the I-bit in the CPU condition code register. It is inhibited at reset so this pin is initially configured as a simple input with a pull-up.

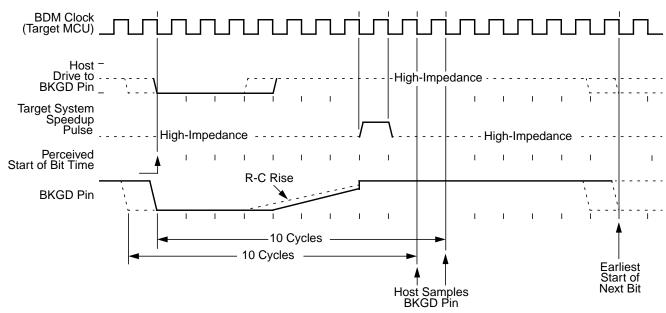

Figure 5-8. BDM Target-to-Host Serial Bit Timing (Logic 1)

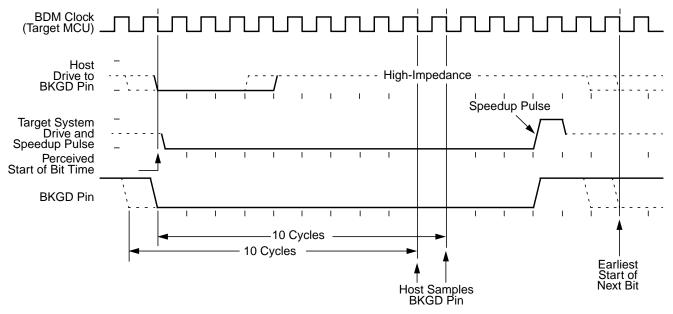

Figure 5-9 shows the host receiving a logic 0 from the target. Since the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 5-9. BDM Target-to-Host Serial Bit Timing (Logic 0)

S12P-Family Reference Manual, Rev. 1.13

### ound Debug Module (S12SBDMV1)

If an interrupt is pending when a TRACE1 command is issued, the interrupt stacking operation occurs but no user instruction is executed. Once back in standard BDM firmware execution, the program counter points to the first instruction in the interrupt service routine.

Be aware when tracing through the user code that the execution of the user code is done step by step but all peripherals are free running. Hence possible timing relations between CPU code execution and occurrence of events of other peripherals no longer exist.

Do not trace the CPU instruction BGND used for soft breakpoints. Tracing over the BGND instruction will result in a return address pointing to BDM firmware address space.

When tracing through user code which contains stop or wait instructions the following will happen when the stop or wait instruction is traced:

The CPU enters stop or wait mode and the TRACE1 command can not be finished before leaving the low power mode. This is the case because BDM active mode can not be entered after CPU executed the stop instruction. However all BDM hardware commands except the BACKGROUND command are operational after tracing a stop or wait instruction and still being in stop or wait mode. If system stop mode is entered (all bus masters are in stop mode) no BDM command is operational.

As soon as stop or wait mode is exited the CPU enters BDM active mode and the saved PC value points to the entry of the corresponding interrupt service routine.

In case the handshake feature is enabled the corresponding ACK pulse of the TRACE1 command will be discarded when tracing a stop or wait instruction. Hence there is no ACK pulse when BDM active mode is entered as part of the TRACE1 command after CPU exited from stop or wait mode. All valid commands sent during CPU being in stop or wait mode or after CPU exited from stop or wait mode will have an ACK pulse. The handshake feature becomes disabled only when system stop mode has been reached. Hence after a system stop mode the handshake feature must be enabled again by sending the ACK\_ENABLE command.

# 5.4.11 Serial Communication Time Out

The host initiates a host-to-target serial transmission by generating a falling edge on the BKGD pin. If BKGD is kept low for more than 128 target clock cycles, the target understands that a SYNC command was issued. In this case, the target will keep waiting for a rising edge on BKGD in order to answer the SYNC request pulse. If the rising edge is not detected, the target will keep waiting forever without any time-out limit.

Consider now the case where the host returns BKGD to logic one before 128 cycles. This is interpreted as a valid bit transmission, and not as a SYNC request. The target will keep waiting for another falling edge marking the start of a new bit. If, however, a new falling edge is not detected by the target within 512 clock cycles since the last falling edge, a time-out occurs and the current command is discarded without affecting memory or the operating mode of the MCU. This is referred to as a soft-reset.

If a read command is issued but the data is not retrieved within 512 serial clock cycles, a soft-reset will occur causing the command to be disregarded. The data is not available for retrieval after the time-out has occurred. This is the expected behavior if the handshake protocol is not enabled. In order to allow the data to be retrieved even with a large clock frequency mismatch (between BDM and CPU) when the hardware

## 6.4.2.1.4 Comparator A Data Bus Comparison NDB Dependency

Comparator A features an NDB control bit, which allows data bus comparators to be configured to either trigger on equivalence or trigger on difference. This allows monitoring of a difference in the contents of an address location from an expected value.

When matching on an equivalence (NDB=0), each individual data bus bit position can be masked out by clearing the corresponding mask bit (DBGADHM/DBGADLM) so that it is ignored in the comparison. A match occurs when all data bus bits with corresponding mask bits set are equivalent. If all mask register bits are clear, then a match is based on the address bus only, the data bus is ignored.

When matching on a difference, mask bits can be cleared to ignore bit positions. A match occurs when any data bus bit with corresponding mask bit set is different. Clearing all mask bits, causes all bits to be ignored and prevents a match because no difference can be detected. In this case address bus equivalence does not cause a match.

| NDB | DBGADHM[n] /<br>DBGADLM[n] | Comment                                     |  |  |  |

|-----|----------------------------|---------------------------------------------|--|--|--|

| 0   | 0                          | Do not compare data bus bit.                |  |  |  |

| 0   | 1                          | Compare data bus bit. Match on equivalence. |  |  |  |

| 1   | 0                          | Do not compare data bus bit.                |  |  |  |

| 1   | 1                          | Compare data bus bit. Match on difference.  |  |  |  |

Table 6-35. NDB and MASK bit dependency

## 6.4.2.2 Range Comparisons

Using the AB comparator pair for a range comparison, the data bus can also be used for qualification by using the comparator A data registers. Furthermore the DBGACTL RW and RWE bits can be used to qualify the range comparison on either a read or a write access. The corresponding DBGBCTL bits are ignored. The SZE and SZ control bits are ignored in range mode. The comparator A TAG bit is used to tag range comparisons. The comparator B TAG bit is ignored in range modes. In order for a range comparison using comparators A and B, both COMPEA and COMPEB must be set; to disable range comparisons both must be cleared. The comparator A BRK bit is used to for the AB range, the comparator B BRK bit is ignored in range mode.

When configured for range comparisons and tagging, the ranges are accurate only to word boundaries.

# 6.4.2.2.1 Inside Range (CompA\_Addr $\leq$ address $\leq$ CompB\_Addr)

In the Inside Range comparator mode, comparator pair A and B can be configured for range comparisons. This configuration depends upon the control register (DBGC2). The match condition requires that a valid match for both comparators happens on the same bus cycle. A match condition on only one comparator is not valid. An aligned word access which straddles the range boundary is valid only if the aligned address is inside the range.

|            | RTR[6:4] =       |                           |                           |                           |                           |                           |                           |                           |  |  |

|------------|------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|

| RTR[3:0]   | 000<br>(OFF)     | 001<br>(2 <sup>10</sup> ) | 010<br>(2 <sup>11</sup> ) | 011<br>(2 <sup>12</sup> ) | 100<br>(2 <sup>13</sup> ) | 101<br>(2 <sup>14</sup> ) | 110<br>(2 <sup>15</sup> ) | 111<br>(2 <sup>16</sup> ) |  |  |

| 0000 (÷1)  | OFF <sup>1</sup> | 2 <sup>10</sup>           | 2 <sup>11</sup>           | 2 <sup>12</sup>           | 2 <sup>13</sup>           | 2 <sup>14</sup>           | 2 <sup>15</sup>           | 2 <sup>16</sup>           |  |  |

| 0001 (÷2)  | OFF              | 2x2 <sup>10</sup>         | 2x2 <sup>11</sup>         | 2x2 <sup>12</sup>         | 2x2 <sup>13</sup>         | 2x2 <sup>14</sup>         | 2x2 <sup>15</sup>         | 2x2 <sup>16</sup>         |  |  |

| 0010 (÷3)  | OFF              | 3x2 <sup>10</sup>         | 3x2 <sup>11</sup>         | 3x2 <sup>12</sup>         | 3x2 <sup>13</sup>         | 3x2 <sup>14</sup>         | 3x2 <sup>15</sup>         | 3x2 <sup>16</sup>         |  |  |

| 0011 (÷4)  | OFF              | 4x2 <sup>10</sup>         | 4x2 <sup>11</sup>         | 4x2 <sup>12</sup>         | 4x2 <sup>13</sup>         | 4x2 <sup>14</sup>         | 4x2 <sup>15</sup>         | 4x2 <sup>16</sup>         |  |  |

| 0100 (÷5)  | OFF              | 5x2 <sup>10</sup>         | 5x2 <sup>11</sup>         | 5x2 <sup>12</sup>         | 5x2 <sup>13</sup>         | 5x2 <sup>14</sup>         | 5x2 <sup>15</sup>         | 5x2 <sup>16</sup>         |  |  |

| 0101 (÷6)  | OFF              | 6x2 <sup>10</sup>         | 6x2 <sup>11</sup>         | 6x2 <sup>12</sup>         | 6x2 <sup>13</sup>         | 6x2 <sup>14</sup>         | 6x2 <sup>15</sup>         | 6x2 <sup>16</sup>         |  |  |

| 0110 (÷7)  | OFF              | 7x2 <sup>10</sup>         | 7x2 <sup>11</sup>         | 7x2 <sup>12</sup>         | 7x2 <sup>13</sup>         | 7x2 <sup>14</sup>         | 7x2 <sup>15</sup>         | 7x2 <sup>16</sup>         |  |  |

| 0111 (÷8)  | OFF              | 8x2 <sup>10</sup>         | 8x2 <sup>11</sup>         | 8x2 <sup>12</sup>         | 8x2 <sup>13</sup>         | 8x2 <sup>14</sup>         | 8x2 <sup>15</sup>         | 8x2 <sup>16</sup>         |  |  |

| 1000 (÷9)  | OFF              | 9x2 <sup>10</sup>         | 9x2 <sup>11</sup>         | 9x2 <sup>12</sup>         | 9x2 <sup>13</sup>         | 9x2 <sup>14</sup>         | 9x2 <sup>15</sup>         | 9x2 <sup>16</sup>         |  |  |

| 1001 (÷10) | OFF              | 10x2 <sup>10</sup>        | 10x2 <sup>11</sup>        | 10x2 <sup>12</sup>        | 10x2 <sup>13</sup>        | 10x2 <sup>14</sup>        | 10x2 <sup>15</sup>        | 10x2 <sup>16</sup>        |  |  |

| 1010 (÷11) | OFF              | 11x2 <sup>10</sup>        | 11x2 <sup>11</sup>        | 11x2 <sup>12</sup>        | 11x2 <sup>13</sup>        | 11x2 <sup>14</sup>        | 11x2 <sup>15</sup>        | 11x2 <sup>16</sup>        |  |  |

| 1011 (÷12) | OFF              | 12x2 <sup>10</sup>        | 12x2 <sup>11</sup>        | 12x2 <sup>12</sup>        | 12x2 <sup>13</sup>        | 12x2 <sup>14</sup>        | 12x2 <sup>15</sup>        | 12x2 <sup>16</sup>        |  |  |

| 1100 (÷13) | OFF              | 13x2 <sup>10</sup>        | 13x2 <sup>11</sup>        | 13x2 <sup>12</sup>        | 13x2 <sup>13</sup>        | 13x2 <sup>14</sup>        | 13x2 <sup>15</sup>        | 13x2 <sup>16</sup>        |  |  |

| 1101 (÷14) | OFF              | 14x2 <sup>10</sup>        | 14x2 <sup>11</sup>        | 14x2 <sup>12</sup>        | 14x2 <sup>13</sup>        | 14x2 <sup>14</sup>        | 14x2 <sup>15</sup>        | 14x2 <sup>16</sup>        |  |  |

| 1110 (÷15) | OFF              | 15x2 <sup>10</sup>        | 15x2 <sup>11</sup>        | 15x2 <sup>12</sup>        | 15x2 <sup>13</sup>        | 15x2 <sup>14</sup>        | 15x2 <sup>15</sup>        | 15x2 <sup>16</sup>        |  |  |

| 1111 (÷16) | OFF              | 16x2 <sup>10</sup>        | 16x2 <sup>11</sup>        | 16x2 <sup>12</sup>        | 16x2 <sup>13</sup>        | 16x2 <sup>14</sup>        | 16x2 <sup>15</sup>        | 16x2 <sup>16</sup>        |  |  |

<sup>1</sup> Denotes the default value out of reset. This value should be used to disable the RTI to ensure future backwards compatibility.

| TCTRIM[3:0] | IRC1M indicative relative TC variation | IRC1M indicative frequency drift for relative TC variation |

|-------------|----------------------------------------|------------------------------------------------------------|

| 0000        | 0 (nominal TC of the IRC1M)            | 0%                                                         |

| 0001        | -0.54%                                 | -0.8%                                                      |

| 0010        | -1.08%                                 | -1.6%                                                      |

| 0011        | -1.63%                                 | -2.4%                                                      |

| 0100        | -2.20%                                 | -3.2%                                                      |

| 0101        | -2.77%                                 | -4.0%                                                      |

| 0110        | -3.33%                                 | -4.8%                                                      |

| 0111        | -3.91%                                 | -5.5%                                                      |

| 1000        | 0 (nominal TC of the IRC1M)            | 0%                                                         |

| 1001        | +0.54%                                 | +0.8%                                                      |

| 1010        | +1.07%                                 | +1.6%                                                      |

| 1011        | +1.59%                                 | +2.4%                                                      |

| 1100        | +2.11%                                 | +3.2%                                                      |

| 1101        | +2.62%                                 | +4.0%                                                      |

| 1110        | +3.12%                                 | +4.8%                                                      |

| 1111        | +3.62%                                 | +5.5%                                                      |

Table 7-21. TC trimming of the IRC1M frequency at ambient temperature

### NOTE

Since the IRC1M frequency is not a linear function of the temperature, but more like a parabola, the above relative TC variation is only an indication and should be considered with care.

Be aware that the output frequency vary with TC trimming, A frequency trimming correction is therefore necessary. The values provided in Table 7-21 are typical values at ambient temperature which can vary from device to device.

## NOTE

The CANTBSEL register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK=1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

### Table 8-17. CANTBSEL Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>TX[2:0] | <ul> <li>Transmit Buffer Select — The lowest numbered bit places the respective transmit buffer in the CANTXFG register space (e.g., TX1 = 1 and TX0 = 1 selects transmit buffer TX0; TX1 = 1 and TX0 = 0 selects transmit buffer TX1). Read and write accesses to the selected transmit buffer will be blocked, if the corresponding TXEx bit is cleared and the buffer is scheduled for transmission (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)").</li> <li>0 The associated message buffer is deselected</li> <li>1 The associated message buffer is selected, if lowest numbered bit</li> </ul> |

The following gives a short programming example of the usage of the CANTBSEL register:

To get the next available transmit buffer, application software must read the CANTFLG register and write this value back into the CANTBSEL register. In this example Tx buffers TX1 and TX2 are available. The value read from CANTFLG is therefore 0b0000\_0110. When writing this value back to CANTBSEL, the Tx buffer TX1 is selected in the CANTXFG because the lowest numbered bit set to 1 is at bit position 1. Reading back this value out of CANTBSEL results in 0b0000\_0010, because only the lowest numbered bit position set to 1 is presented. This mechanism eases the application software the selection of the next available Tx buffer.

- LDAA CANTFLG; value read is 0b0000\_0110

- STAA CANTBSEL; value written is 0b0000\_0110

- LDAA CANTBSEL; value read is 0b0000\_0010

If all transmit message buffers are deselected, no accesses are allowed to the CANTXFG registers.

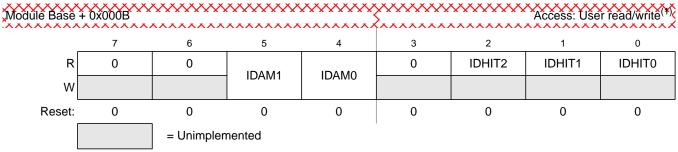

# 8.3.2.12 MSCAN Identifier Acceptance Control Register (CANIDAC)

The CANIDAC register is used for identifier acceptance control as described below.

## Figure 8-15. MSCAN Identifier Acceptance Control Register (CANIDAC)

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except bits IDHITx, which are read-only

## 8.3.2.17 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 8.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 8.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 8-20. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3 1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 8-22. CANIDAR0–CANIDAR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

Module Base + 0x0018 to Module Base + 0x001B

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# Figure 8-21. MSCAN Identifier Acceptance Registers (Second Bank) — CANIDAR4–CANIDAR7

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

# Chapter 9 Analog-to-Digital Converter (ADC12B10C) Revision History

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                       |

|-------------------|------------------|-------------------|--------|----------------------------------------------------------------------------------------------|

| V01.00            | 25 July 2007     | 25 July 2007      |        | Initial version                                                                              |

| V01.01            | 14 Sept 2007     | 14 Sept 2007      |        | Added reserved registers at the end the memory map.                                          |

| V01.02            | 1 Oct 2007       | 1 Oct 2007        |        | Added following mention where applies:<br>(n conversion number, NOT channel number!)         |

| V01.03            | 9 Oct 2007       | 9 Oct 2007        |        | Modified table "Analog Input Channel Select Coding" due to new customer feature (SPECIAL17). |

# 9.1 Introduction

The ADC12B10C is a 10-channel, 12-bit, multiplexed input successive approximation analog-to-digital converter. Refer to device electrical specifications for ATD accuracy.

## 9.1.1 Features

- 8-, 10-, or 12-bit resolution.

- Conversion in Stop Mode using internally generated clock

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 10 analog input channels.

- Special conversions for  $V_{RH}$ ,  $V_{RL}$ ,  $(V_{RL}+V_{RH})/2$ .

- 1-to-10 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

S12P-Family Reference Manual, Rev. 1.13

### Table 10-4. PWMCLK Field Descriptions

| Field      | Description                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>PCLK5 | Pulse Width Channel 5 Clock Select         0 Clock A is the clock source for PWM channel 5.         1 Clock SA is the clock source for PWM channel 5.             |

| 4<br>PCLK4 | Pulse Width Channel 4 Clock Select         0 Clock A is the clock source for PWM channel 4.         1 Clock SA is the clock source for PWM channel 4.             |

| 3<br>PCLK3 | Pulse Width Channel 3 Clock Select         0       Clock B is the clock source for PWM channel 3.         1       Clock SB is the clock source for PWM channel 3. |

| 2<br>PCLK2 | Pulse Width Channel 2 Clock Select         0       Clock B is the clock source for PWM channel 2.         1       Clock SB is the clock source for PWM channel 2. |

| 1<br>PCLK1 | Pulse Width Channel 1 Clock Select         0 Clock A is the clock source for PWM channel 1.         1 Clock SA is the clock source for PWM channel 1.             |

| 0<br>PCLK0 | Pulse Width Channel 0 Clock Select         0 Clock A is the clock source for PWM channel 0.         1 Clock SA is the clock source for PWM channel 0.             |

## 10.3.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

This register selects the prescale clock source for clocks A and B independently.

Module Base + 0x0003

| ~~~~~ | ******                      | ****** | ****** |        | ~~~~~~~ | ~~~~~~~ | ~~~~~~ |       |  |  |  |  |

|-------|-----------------------------|--------|--------|--------|---------|---------|--------|-------|--|--|--|--|

|       | 7                           | 6      | 5      | 4      | 3       | 2       | 1      | 0     |  |  |  |  |

| R     | 0                           | PCKB2  | PCKB1  | PCKB0  | 0       | PCKA2   | PCKA1  | PCKA0 |  |  |  |  |

| W     |                             | T OND2 | TORDT  | I OKDO |         |         | TORAT  |       |  |  |  |  |

| Reset | 0                           | 0      | 0      | 0 0    |         | 0       | 0      | 0     |  |  |  |  |

|       | = Unimplemented or Reserved |        |        |        |         |         |        |       |  |  |  |  |

### Figure 10-6. PWM Prescaler Clock Select Register (PWMPRCLK)

Read: anytime

Write: anytime

## NOTE

PCKB2–PCKB0 and PCKA2–PCKA0 register bits can be written anytime. If the clock prescale is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

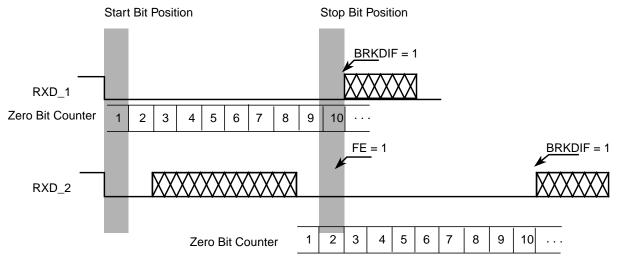

Figure 11-17 shows two cases of break detect. In trace RXD\_1 the break symbol starts with the start bit, while in RXD\_2 the break starts in the middle of a transmission. If BRKDFE = 1, in RXD\_1 case there will be no byte transferred to the receive buffer and the RDRF flag will not be modified. Also no framing error or parity error will be flagged from this transfer. In RXD\_2 case, however the break signal starts later during the transmission. At the expected stop bit position the byte received so far will be transferred to the receive buffer, the receive data register full flag will be set, a framing error and if enabled and appropriate a parity error will be set.

Figure 11-17. Break Detection if BRKDFE = 1 (M = 0)

## 11.4.5.4 Idle Characters