Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 32MHz                                                                |

| Connectivity               | CANbus, SCI, SPI                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 34                                                                   |

| Program Memory Size        | 96KB (96K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 4K x 8                                                               |

| RAM Size                   | 6K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                         |

| Data Converters            | A/D 10x12b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-TFQFN Exposed Pad                                                 |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12p96cft |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 8.2.3     | CAN System                            | 254 |

|-----|-----------|---------------------------------------|-----|

| 8.3 | Memor     | y Map and Register Definition         | 254 |

|     | 8.3.1     | Module Memory Map                     | 254 |

|     | 8.3.2     | Register Descriptions                 | 256 |

|     | 8.3.3     | Programmer's Model of Message Storage | 275 |

| 8.4 | Functio   | nal Description                       | 285 |

|     | 8.4.1     | General                               | 285 |

|     | 8.4.2     | Message Storage                       | 286 |

|     | 8.4.3     | Identifier Acceptance Filter          | 289 |

|     | 8.4.4     | Modes of Operation                    | 295 |

|     | 8.4.5     | Low-Power Options                     | 297 |

|     | 8.4.6     | Reset Initialization                  | 301 |

|     | 8.4.7     | Interrupts                            | 301 |

| 8.5 | Initializ | ation/Application Information         | 303 |

|     | 8.5.1     | MSCAN initialization                  | 303 |

|     | 8.5.2     | Bus-Off Recovery                      | 303 |

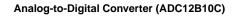

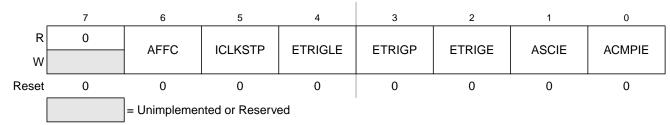

### Chapter 9 Analog-to-Digital Converter (ADC12B10C)

| 9.1 | Introduction                       |  |

|-----|------------------------------------|--|

|     | 9.1.1 Features                     |  |

|     | 9.1.2 Modes of Operation           |  |

|     | 9.1.3 Block Diagram                |  |

| 9.2 | Signal Description                 |  |

|     | 9.2.1 Detailed Signal Descriptions |  |

| 9.3 | Memory Map and Register Definition |  |

|     | 9.3.1 Module Memory Map            |  |

|     | 9.3.2 Register Descriptions        |  |

| 9.4 | Functional Description             |  |

|     | 9.4.1 Analog Sub-Block             |  |

|     | 9.4.2 Digital Sub-Block            |  |

| 9.5 | Resets                             |  |

| 9.6 | Interrupts                         |  |

|     |                                    |  |

# Chapter 10

# Pulse-Width Modulator (PWM8B6CV1) Block Description

| 10.1 | Introduction                                        | 329 |

|------|-----------------------------------------------------|-----|

|      | 10.1.1 Features                                     | 329 |

|      | 10.1.2 Modes of Operation                           | 329 |

|      | 10.1.3 Block Diagram                                | 330 |

| 10.2 | External Signal Description                         | 330 |

|      | 10.2.1 PWM5 — Pulse Width Modulator Channel 5 Pin   | 330 |

|      | 10.2.2 PWM4 — Pulse Width Modulator Channel 4 Pin   | 330 |

|      | 10.2.3 PWM3 — Pulse Width Modulator Channel 3 Pin 3 | 330 |

|      |                                                     |     |

# 1.3.3 On-Chip SRAM

• Up to 6 Kbytes of general-purpose RAM

# 1.3.4 Main External Oscillator (XOSC)

- Loop control Pierce oscillator using a 4 MHz to 16 MHz crystal

- Current gain control on amplitude output

- Signal with low harmonic distortion

- Low power

- Good noise immunity

- Eliminates need for external current limiting resistor

- Transconductance sized for optimum start-up margin for typical crystals

# 1.3.5 Internal RC Oscillator (IRC)

- Trimmable internal reference clock.

- Frequency: 1 MHz

- Trimmed accuracy over  $-40^{\circ}$ C to  $+125^{\circ}$ C ambient temperature range:  $\pm 1.5\%$

### 1.3.6 Internal Phase-Locked Loop (IPLL)

- Phase-locked-loop clock frequency multiplier

- No external components required

- Reference divider and multiplier allow large variety of clock rates

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- Reference clock sources:

- External 4–16 MHz resonator/crystal (XOSC)

- Internal 1 MHz RC oscillator (IRC)

### 1.3.7 System Integrity Support

- Power-on reset (POR)

- System reset generation

- Illegal address detection with reset

- Low-voltage detection with interrupt or reset

- Real time interrupt (RTI)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

# 1.3.16 Debugger (DBG)

- Trace buffer with depth of 64 entries

- Three comparators (A, B and C)

- Comparators A compares the full address bus and full 16-bit data bus

- Exact address or address range comparisons

- Two types of comparator matches

- Tagged This matches just before a specific instruction begins execution

- Force This is valid on the first instruction boundary after a match occurs

- Four trace modes

- Four stage state sequencer

Freescale Semiconductor

S12P-Family Reference Manual, Rev. 1.13

| Package Pin |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power                                                                                                                                                                                                                                                                                                                              | Internal Pull<br>Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP<br>64  | QFN<br>48                                                                                                         | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2nd<br>Func.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3rd<br>Func.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supply                                                                                                                                                                                                                                                                                                                             | CTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reset<br>State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

| 29          | 22                                                                                                                | XTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDP<br>LL                                                                                                                                                                                                                                                                                                                         | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Oscillator pin                                                                                                                                                                                                                                                                                                                                                                                                |

| 30          | 23                                                                                                                | PJ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | KWJ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PERJ/PPSJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port J I/O, interrupt                                                                                                                                                                                                                                                                                                                                                                                         |

| -           | -                                                                                                                 | PE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port E I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| -           | -                                                                                                                 | PE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port E I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31          | 24                                                                                                                | PE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ĪRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port E Input, maskable<br>interrupt                                                                                                                                                                                                                                                                                                                                                                           |

| 32          | 25                                                                                                                | PE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XIRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port E Input, non-<br>maskable interrupt                                                                                                                                                                                                                                                                                                                                                                      |

| 33          | -                                                                                                                 | PA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| 34          | -                                                                                                                 | PA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| 35          | -                                                                                                                 | PA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| 36          | -                                                                                                                 | PA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| -           | -                                                                                                                 | PA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |

| -           | -                                                                                                                 | PA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDX                                                                                                                                                                                                                                                                                                                               | PUCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port A I/O                                                                                                                                                                                                                                                                                                                                                                                                    |