Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, SCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                           |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-TFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p128j0cft |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.3.3 On-Chip SRAM

• Up to 6 Kbytes of general-purpose RAM

# 1.3.4 Main External Oscillator (XOSC)

- Loop control Pierce oscillator using a 4 MHz to 16 MHz crystal

- Current gain control on amplitude output

- Signal with low harmonic distortion

- Low power

- Good noise immunity

- Eliminates need for external current limiting resistor

- Transconductance sized for optimum start-up margin for typical crystals

# 1.3.5 Internal RC Oscillator (IRC)

- Trimmable internal reference clock.

- Frequency: 1 MHz

- Trimmed accuracy over  $-40^{\circ}$ C to  $+125^{\circ}$ C ambient temperature range:  $\pm 1.5\%$

# 1.3.6 Internal Phase-Locked Loop (IPLL)

- Phase-locked-loop clock frequency multiplier

- No external components required

- Reference divider and multiplier allow large variety of clock rates

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- Reference clock sources:

- External 4–16 MHz resonator/crystal (XOSC)

- Internal 1 MHz RC oscillator (IRC)

# 1.3.7 System Integrity Support

- Power-on reset (POR)

- System reset generation

- Illegal address detection with reset

- Low-voltage detection with interrupt or reset

- Real time interrupt (RTI)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

# 1.7.3.10 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general-purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference. The ECLK output has a programmable prescaler.

### 1.7.3.11 PE[3:2] — Port E I/O Pin 3

PE[3:2] are a general-purpose input or output pins.

### 1.7.3.12 PE1 / IRQ — Port E Input Pin 1

PE1 is a general-purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode.

### 1.7.3.13 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general-purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from stop or wait mode. The XIRQ interrupt is level sensitive and active low. As XIRQ is level sensitive, while this pin is low the MCU will not enter STOP mode.

### 1.7.3.14 PJ[7:6, 2:0] / KWJ[7:6, 2:0] — Port J I/O Pins 7-6, 2-0

PJ[7:6, 2:0] are a general-purpose input or output pins. They can be configured as keypad wakeup inputs.

### 1.7.3.15 PM[7:6] — Port M I/O Pins 7-6

PM[7:6] are a general-purpose input or output pins.

### 1.7.3.16 PM5 / SCK — Port M I/O Pin 5

PM5 is a general-purpose input or output pin. It can be configured as the serial clock pin SCK of the serial peripheral interface (SPI).

### 1.7.3.17 PM4 / MOSI — Port M I/O Pin 4

PM4 is a general-purpose input or output pin. It can be configured as the master output (during master mode) or slave input pin (during slave mode) MOSI for the serial peripheral interface (SPI).

### 1.7.3.18 PM3 / SS — Port M I/O Pin 3

PM3 is a general-purpose input or output pin. It can be configured as the slave select pin  $\overline{SS}$  of the serial peripheral interface (SPI).

### 1.7.3.19 PM2 / MISO— Port M I/O Pin 3

PM2 is a general-purpose input or output pin. It can be configured as the master input (during master mode) or slave output pin (during slave mode) MISO for the serial peripheral interface (SPI)

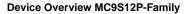

# 2.3.38 Port M Wired-Or Mode Register (WOMM)

#### Table 2-34. WOMM Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0<br>WOMM | <b>Port M wired-or mode</b> —Enable open-drain functionality on output pin<br>This bit configures an output pin as wired-or (open-drain) or push-pull. In wired-or mode a logic "0" is driven active<br>low while a logic "1" remains undriven. This allows a multipoint connection of several serial modules. The bit has no<br>influence on pins used as input. |

|             | <ol> <li>Output buffer operates as open-drain output.</li> <li>Output buffer operates as push-pull output.</li> </ol>                                                                                                                                                                                                                                             |

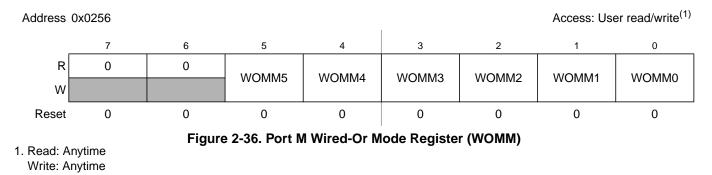

# 2.3.39 PIM Reserved Register

1. Read: Always reads 0x00 Write: Unimplemented

If the X bit maskable interrupt request is used to wake-up the MCU with the X bit in the CCR set, the associated ISR is not called. The CPU then resumes program execution with the instruction following the WAI or STOP instruction. This features works following the same rules like any interrupt request, that is care must be taken that the X interrupt request used for wake-up remains active at least until the system begins execution of the instruction following the WAI or STOP instruction; otherwise, wake-up may not occur.

Several examples of PLL divider settings are shown in Table 7-23. The following rules help to achieve optimum stability and shortest lock time:

- Use lowest possible  $f_{VCO} / f_{REF}$  ratio (SYNDIV value).

- Use highest possible REFCLK frequency  $f_{REF}$ .

| f <sub>osc</sub> | REFDIV[3:0] | f <sub>REF</sub> | REFFRQ[1:0] | SYNDIV[5:0] | f <sub>VCO</sub> | VCOFRQ[1:0] | POSTDIV[4:0] | f <sub>PLL</sub> | f <sub>bus</sub> |

|------------------|-------------|------------------|-------------|-------------|------------------|-------------|--------------|------------------|------------------|

| off              | \$00        | 1MHz             | 00          | \$1F        | 64MHz            | 01          | \$03         | 16MHz            | 8MHz             |

| off              | \$00        | 1MHz             | 00          | \$1F        | 64MHz            | 01          | \$00         | 64MHz            | 32MHz            |

| off              | \$00        | 1MHz             | 00          | \$0F        | 32MHz            | 00          | \$00         | 32MHz            | 16MHz            |

| 4MHz             | \$00        | 4MHz             | 01          | \$03        | 32MHz            | 01          | \$00         | 32MHz            | 16MHz            |

### Table 7-23. Examples of PLL Divider Settings

The phase detector inside the PLL compares the feedback clock (FBCLK = VCOCLK/(SYNDIV+1)) with the reference clock (REFCLK = IRC1M or OSCCLK/REFDIV+1)). Correction pulses are generated based on the phase difference between the two signals. The loop filter alters the DC voltage on the internal filter capacitor, based on the width and direction of the correction pulse, which leads to a higher or lower VCO frequency.

The user must select the range of the REFCLK frequency (REFFRQ[1:0] bits) and the range of the VCOCLK frequency (VCOFRQ[1:0] bits) to ensure that the correct PLL loop bandwidth is set.

The lock detector compares the frequencies of the FBCLK and the REFCLK. Therefore the speed of the lock detector is directly proportional to the reference clock frequency. The circuit determines the lock condition based on this comparison.

If PLL LOCK interrupt requests are enabled, the software can wait for an interrupt request and for instance check the LOCK bit. If interrupt requests are disabled, software can poll the LOCK bit continuously (during PLL start-up) or at periodic intervals. In either case, only when the LOCK bit is set, the VCOCLK will have stabilized to the programmed frequency.

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within the tolerance  $\Delta_{Lock}$  and is cleared when the VCO frequency is out of the tolerance  $\Delta_{unl}$ .

- Interrupt requests can occur if enabled (LOCKIE = 1) when the lock condition changes, toggling the LOCK bit.

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-2<br>TSTAT[1:0]       | Transmitter Status Bits — The values of the error counters control the actual CAN bus status of the MSCAN.As soon as the status change interrupt flag (CSCIF) is set, these bits indicate the appropriate transmitter relatedCAN bus status of the MSCAN. The coding for the bits TSTAT1, TSTAT0 is:00 TxOK: 0 ≤ transmit error counter ≤ 9601 TxWRN: 96 < transmit error counter ≤ 127                                                                                                                                                                                                                                                                                                                                                                     |

| 1<br>OVRIF              | Overrun Interrupt Flag — This flag is set when a data overrun condition occurs. If not masked, an error interrupt is pending while this flag is set.         0       No data overrun condition         1       A data overrun detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0<br>RXF <sup>(2)</sup> | <ul> <li>Receive Buffer Full Flag — RXF is set by the MSCAN when a new message is shifted in the receiver FIFO. This flag indicates whether the shifted buffer is loaded with a correctly received message (matching identifier, matching cyclic redundancy code (CRC) and no other errors detected). After the CPU has read that message from the RxFG buffer in the receiver FIFO, the RXF flag must be cleared to release the buffer. A set RXF flag prohibits the shifting of the next FIFO entry into the foreground buffer (RxFG). If not masked, a receive interrupt is pending while this flag is set.</li> <li>No new message available within the RxFG</li> <li>The receiver FIFO is not empty. A new message is available in the RxFG</li> </ul> |

#### Table 8-11. CANRFLG Register Field Descriptions (continued)

1. Redundant Information for the most critical CAN bus status which is "bus-off". This only occurs if the Tx error counter exceeds a number of 255 errors. Bus-off affects the receiver state. As soon as the transmitter leaves its bus-off state the receiver state skips to RxOK too. Refer also to TSTAT[1:0] coding in this register.

2. To ensure data integrity, do not read the receive buffer registers while the RXF flag is cleared. For MCUs with dual CPUs, reading the receive buffer registers while the RXF flag is cleared may result in a CPU fault condition.

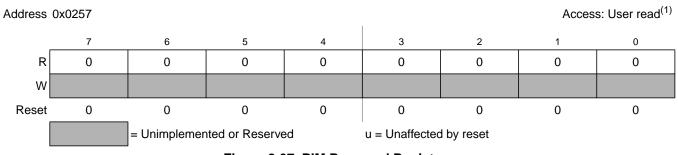

# 8.3.2.6 MSCAN Receiver Interrupt Enable Register (CANRIER)

This register contains the interrupt enable bits for the interrupt flags described in the CANRFLG register.

| R<br>W | WUPIE | CSCIE | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE | RXFIE |

|--------|-------|-------|---------|---------|---------|---------|-------|-------|

| Reset: | 0     | 0     | 0       | 0       | 0       | 0       | 0     | 0     |

Figure 8-9. MSCAN Receiver Interrupt Enable Register (CANRIER)

1. Read: Anytime

Write: Anytime when not in initialization mode

### NOTE

The CANRIER register is held in the reset state when the initialization mode is active (INITRQ=1 and INITAK=1). This register is writable when not in initialization mode (INITRQ=0 and INITAK=0).

The RSTATE[1:0], TSTATE[1:0] bits are not affected by initialization mode.

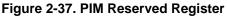

Môdule Base + 0x000E Access: User read/write 7 6 5 4 3 2 1 0 RXERR7 RXERR6 RXERR5 RXERR4 RXERR3 RXERR2 RXERR1 RXERR0 R ۱Λ 0 0 0 0 0 0 0 0 Reset: = Unimplemented

Figure 8-18. MSCAN Receive Error Counter (CANRXERR)

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

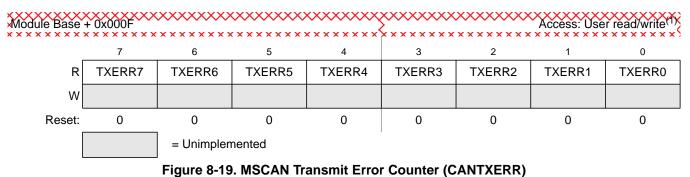

### 8.3.2.16 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

le's Scalable Controller Area Network (S12MSCANV3)

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

#### Table 8-23. CANIDAR4–CANIDAR7 Register Field Descriptions

### 8.3.2.18 MSCAN Identifier Mask Registers (CANIDMR0–CANIDMR7)

The identifier mask register specifies which of the corresponding bits in the identifier acceptance register are relevant for acceptance filtering. To receive standard identifiers in 32 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR1 and CANIDMR5 to "don't care." To receive standard identifiers in 16 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR1 and CANIDMR5 to "don't care." To receive standard identifiers in 16 bit filter mode, it is required to program the last three bits (AM[2:0]) in the mask registers CANIDMR5, and CANIDMR7 to "don't care."

# Module Base + 0x0014 to Module Base + 0x0017

| •••••  |     |     |     |     |     |     |     |     |  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AMO |  |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Figure 8-22. MSCAN Identifier Mask Registers (First Bank) — CANIDMR0–CANIDMR3

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 8-24. CANIDMR0–CANIDMR3 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AM[7:0] | Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.<br>0 Match corresponding acceptance code register and identifier bits<br>1 Ignore corresponding acceptance code register bit |

# Module Base + 0x001C to Module Base + 0x001F Access: User read/write<sup>(1)</sup>

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 8-23. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4–CANIDMR7

#### to-Digital Converter (ADC12B10C)

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

### 9.1.2 Modes of Operation

### 9.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

### 9.1.2.2 MCU Operating Modes

#### • Stop Mode

### — ICLKSTP=0 (in ATDCTL2 register)

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

#### — ICLKSTP=1 (in ATDCTL2 register)

A/D conversion sequence seamless continues in Stop Mode based on the internally generated clock ICLK as ATD clock. For conversions during transition from Run to Stop Mode or vice versa the result is not written to the results register, no CCF flag is set and no compare is done. When converting in Stop Mode (ICLKSTP=1) an ATD Stop Recovery time  $t_{ATDSTPRCV}$  is required to switch back to bus clock based ATDCLK when leaving Stop Mode. Do not access ATD registers during this time.

#### • Wait Mode

ADC12B10C behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

#### • Freeze Mode

In Freeze Mode the ADC12B10C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

# Chapter 10 Pulse-Width Modulator (PWM8B6CV1) Block Description

# 10.1 Introduction

The pulse width modulation (PWM) definition is based on the HC12 PWM definitions. The PWM8B6CV1 module contains the basic features from the HC11 with some of the enhancements incorporated on the HC12, that is center aligned output mode and four available clock sources. The PWM8B6CV1 module has six channels with independent control of left and center aligned outputs on each channel.

Each of the six PWM channels has a programmable period and duty cycle as well as a dedicated counter. A flexible clock select scheme allows a total of four different clock sources to be used with the counters. Each of the modulators can create independent continuous waveforms with software-selectable duty rates from 0% to 100%. The PWM outputs can be programmed as left aligned outputs or center aligned outputs

### 10.1.1 Features

- Six independent PWM channels with programmable period and duty cycle

- Dedicated counter for each PWM channel

- Programmable PWM enable/disable for each channel

- Software selection of PWM duty pulse polarity for each channel

- Period and duty cycle are double buffered. Change takes effect when the end of the effective period is reached (PWM counter reaches 0) or when the channel is disabled.

- Programmable center or left aligned outputs on individual channels

- Six 8-bit channel or three 16-bit channel PWM resolution

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies.

- Programmable clock select logic

- Emergency shutdown

# 10.1.2 Modes of Operation

There is a software programmable option for low power consumption in wait mode that disables the input clock to the prescaler.

In freeze mode there is a software programmable option to disable the input clock to the prescaler. This is useful for emulation.

S12P-Family Reference Manual, Rev. 1.13

| Register<br>Name               |        | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

|--------------------------------|--------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| 0x0000<br>PWME                 | R<br>W | 0                           | 0     | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |  |  |

| 0x0001<br>PWMPOL               | R<br>W | 0                           | 0     | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |  |  |

| 0x0002<br>PWMCLK               | R<br>W | 0                           | 0     | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |  |  |

| 0x0003<br>PWMPRCLK             | R<br>W | 0                           | PCKB2 | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |  |  |

| 0x0004<br>PWMCAE               | R<br>W | 0                           | 0     | CAE5  | CAE4  | CAE2  | CAE2  | CAE1  | CAE0  |  |  |

| 0x0005<br>PWMCTL               | R<br>W | 0                           | CON45 | CON23 | CON01 | PSWAI | PFRZ  | 0     | 0     |  |  |

| 0x0006<br>PWMTST               | R<br>W | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| 0x0007<br>PWMPRSC              | R<br>W | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| <mark>0x0008</mark><br>PWMSCLA | R<br>W | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| 0x0009<br>PWMSCLB              | R<br>W | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| 0x000A<br>PWMSCNTA             | R<br>W | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| 0x000B<br>PWMSCNTB             | R<br>W | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| <u>0x000C</u>                  | R      | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| PWMCNT0                        | W      | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| <u>0x000D</u>                  | R      | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| PWMCNT1                        | W      | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| <u>0x000E</u>                  | R      | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| PWMCNT2                        | W      | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| <u>0x000F</u>                  | R      | Bit 7                       | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

| PWMCNT3                        | W      | 0                           | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

|                                | [      | = Unimplemented or Reserved |       |       |       |       |       |       |       |  |  |

Figure 10-2. PWM Register Summary

#### Pulse-Width Modulator (PWM8B6CV1) Block Description

|        | ase + 0x001D |   |   |   |   |   |   |       |

|--------|--------------|---|---|---|---|---|---|-------|

|        | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

| R<br>W | Bit 7        | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

Figure 10-32. PWM Channel Duty Registers (PWMDTY5)

Read: anytime

Write: anytime

### 10.3.2.15 PWM Shutdown Register (PWMSDN)

The PWMSDN register provides for the shutdown functionality of the PWM module in the emergency cases.

Module Base + 0x00E ~~~~~~~~~~

|       | 7                           | 6     | 5        | 4      | 3 | 2      | 1       | 0          |  |

|-------|-----------------------------|-------|----------|--------|---|--------|---------|------------|--|

| R     | PWMIF                       | PWMIE | 0        | PWMLVL | 0 | PWM5IN | PWM5INL | PWM5ENA    |  |

| W     |                             |       | PWMRSTRT |        |   |        |         | FVIVIJEINA |  |

| Reset | 0                           | 0     | 0        | 0      | 0 | 0      | 0       | 0          |  |

|       | = Unimplemented or Reserved |       |          |        |   |        |         |            |  |

Figure 10-33. PWM Shutdown Register (PWMSDN)

Read: anytime

Write: anytime

#### Table 10-10. PWMSDN Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PWMIF    | <ul> <li>PWM Interrupt Flag — Any change from passive to asserted (active) state or from active to passive state will be flagged by setting the PWMIF flag = 1. The flag is cleared by writing a logic 1 to it. Writing a 0 has no effect.</li> <li>0 No change on PWM5IN input.</li> <li>1 Change on PWM5IN input</li> </ul> |

| 6<br>PWMIE    | <ul> <li>PWM Interrupt Enable — If interrupt is enabled an interrupt to the CPU is asserted.</li> <li>0 PWM interrupt is disabled.</li> <li>1 PWM interrupt is enabled.</li> </ul>                                                                                                                                            |

| 5<br>PWMRSTRT | <b>PWM Restart</b> — The PWM can only be restarted if the PWM channel input 5 is deasserted. After writing a logic 1 to the PWMRSTRT bit (trigger event) the PWM channels start running after the corresponding counter passes next "counter = 0" phase.                                                                      |

|               | Also, if the PWM5ENA bit is reset to 0, the PWM do not start before the counter passes 0x0000.                                                                                                                                                                                                                                |

|               | The bit is always read as 0.                                                                                                                                                                                                                                                                                                  |

| 4<br>PWMLVL   | <ul> <li>PWM Shutdown Output Level — If active level as defined by the PWM5IN input, gets asserted all enabled PWM channels are immediately driven to the level defined by PWMLVL.</li> <li>0 PWM outputs are forced to 0</li> <li>1 PWM outputs are forced to 1.</li> </ul>                                                  |

| Table 11-2. SCIBDH and SCIBDL Field Descriptions |

|--------------------------------------------------|

|--------------------------------------------------|

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IREN               | <ul> <li>Infrared Enable Bit — This bit enables/disables the infrared modulation/demodulation submodule.</li> <li>0 IR disabled</li> <li>1 IR enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6:5<br>TNP[1:0]         | <b>Transmitter Narrow Pulse Bits</b> — These bits enable whether the SCI transmits a 1/16, 3/16, 1/32 or 1/4 narrow pulse. See Table 11-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4:0<br>7:0<br>SBR[12:0] | <ul> <li>SCI Baud Rate Bits — The baud rate for the SCI is determined by the bits in this register. The baud rate is calculated two different ways depending on the state of the IREN bit.</li> <li>The formulas for calculating the baud rate are:<br/>When IREN = 0 then,<br/>SCI baud rate = SCI bus clock / (16 x SBR[12:0])</li> <li>When IREN = 1 then,<br/>SCI baud rate = SCI bus clock / (32 x SBR[12:1])</li> <li>Note: The baud rate generator is disabled after reset and not started until the TE bit or the RE bit is set for the first time. The baud rate generator is disabled when (SBR[12:0] = 0 and IREN = 0) or (SBR[12:1] = 0 and IREN = 1).</li> <li>Note: Writing to SCIBDH has no effect without writing to SCIBDL, because writing to SCIBDH puts the data in a temporary location until SCIBDL is written to.</li> </ul> |

Table 11-3. IRSCI Transmit Pulse Width

| TNP[1:0] | Narrow Pulse Width |

|----------|--------------------|

| 11       | 1/4                |

| 10       | 1/32               |

| 01       | 1/16               |

| 00       | 3/16               |

# 11.3.2.2 SCI Control Register 1 (SCICR1)

| _      | 7     | 6       | 5    | 4 | 3    | 2   | 1  | 0  |

|--------|-------|---------|------|---|------|-----|----|----|

| R<br>W | LOOPS | SCISWAI | RSRC | Μ | WAKE | ILT | PE | PT |

| Reset  | 0     | 0       | 0    | 0 | 0    | 0   | 0  | 0  |

### Figure 11-5. SCI Control Register 1 (SCICR1)

Read: Anytime, if AMAP = 0.

Write: Anytime, if AMAP = 0.

### NOTE

This register is only visible in the memory map if AMAP = 0 (reset condition).

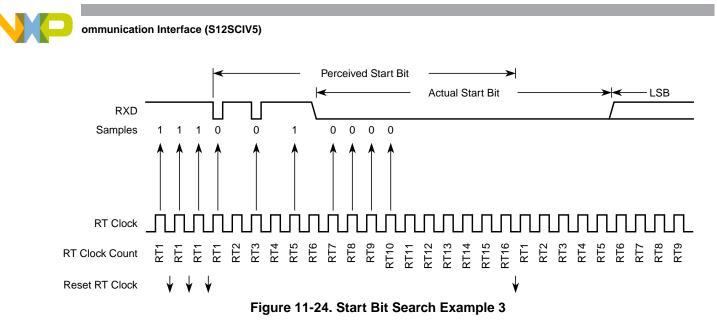

Figure 11-25 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

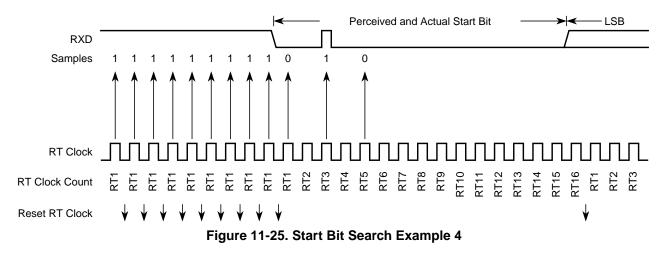

Figure 11-26 shows a burst of noise near the beginning of the start bit that resets the RT clock. The sample after the reset is low but is not preceded by three high samples that would qualify as a falling edge. Depending on the timing of the start bit search and on the data, the frame may be missed entirely or it may set the framing error flag.

### NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

# 11.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

Figure 11-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

### NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

# 11.5 Initialization/Application Information

### 11.5.1 Reset Initialization

See Section 11.3.2, "Register Descriptions".

# 11.5.2 Modes of Operation

### 11.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 11.4.5.2, "Character Transmission".

### 11.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

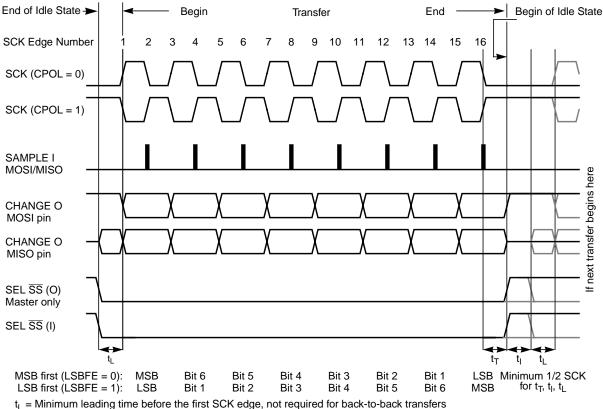

The CPOL clock polarity control bit specifies an active high or low clock and has no significant effect on the transmission format.

The CPHA clock phase control bit selects one of two fundamentally different transmission formats.

Clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transmissions to allow a master device to communicate with peripheral slaves having different requirements.

### 12.4.3.2 CPHA = 0 Transfer Format

The first edge on the SCK line is used to clock the first data bit of the slave into the master and the first data bit of the master into the slave. In some peripherals, the first bit of the slave's data is available at the slave's data out pin as soon as the slave is selected. In this format, the first SCK edge is issued a half cycle after  $\overline{SS}$  has become low.

A half SCK cycle later, the second edge appears on the SCK line. When this second edge occurs, the value previously latched from the serial data input pin is shifted into the LSB or MSB of the shift register, depending on LSBFE bit.

After this second edge, the next bit of the SPI master data is transmitted out of the serial data output pin of the master to the serial input pin on the slave. This process continues for a total of 16 edges on the SCK line, with data being latched on odd numbered edges and shifted on even numbered edges.

Data reception is double buffered. Data is shifted serially into the SPI shift register during the transfer and is transferred to the parallel SPI data register after the last bit is shifted in.

After 2n<sup>1</sup> (last) SCK edges:

- Data that was previously in the master SPI data register should now be in the slave data register and the data that was in the slave data register should be in the master.

- The SPIF flag in the SPI status register is set, indicating that the transfer is complete.

Figure 12-12 is a timing diagram of an SPI transfer where CPHA = 0. SCK waveforms are shown for CPOL = 0 and CPOL = 1. The diagram may be interpreted as a master or slave timing diagram because the SCK, MISO, and MOSI pins are connected directly between the master and the slave. The MISO signal is the output from the slave and the MOSI signal is the output from the master. The  $\overline{SS}$  pin of the master must be either high or reconfigured as a general-purpose output not affecting the SPI.

<sup>1.</sup> n depends on the selected transfer width, please refer to Section 12.3.2.2, "SPI Control Register 2 (SPICR2)

#### eripheral Interface (S12SPIV5)

When the third edge occurs, the value previously latched from the serial data input pin is shifted into the LSB or MSB of the SPI shift register, depending on LSBFE bit. After this edge, the next bit of the master data is coupled out of the serial data output pin of the master to the serial input pin on the slave.

This process continues for a total of  $n^1$  edges on the SCK line with data being latched on even numbered edges and shifting taking place on odd numbered edges.

Data reception is double buffered, data is serially shifted into the SPI shift register during the transfer and is transferred to the parallel SPI data register after the last bit is shifted in.

After 2n<sup>1</sup> SCK edges:

- Data that was previously in the SPI data register of the master is now in the data register of the slave, and data that was in the data register of the slave is in the master.

- The SPIF flag bit in SPISR is set indicating that the transfer is complete.

Figure 12-14 shows two clocking variations for CPHA = 1. The diagram may be interpreted as a master or slave timing diagram because the SCK, MISO, and MOSI pins are connected directly between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The  $\overline{SS}$  pin of the master must be either high or reconfigured as a general-purpose output not affecting the SPI.

$t_T$  = Minimum trailing time after the last SCK edge

$t_1 =$  Minimum idling time between transfers (minimum  $\overline{SS}$  high time), not required for back-to-back transfers

Figure 12-14. SPI Clock Format 1 (CPHA = 1), with 8-Bit Transfer Width selected (XFRW = 0)

S12P-Family Reference Manual, Rev. 1.13

#### /te Flash Module (S12FTMRC128K1V1)

- 7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

- 8. Reset the MCU

# 13.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 13-27.

# 13.6 Initialization

On each system reset the Flash module executes a reset sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and DFPROT protection registers, and the FOPT and FSEC registers. The Flash module reverts to using built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF remains clear throughout the reset sequence. The Flash module holds off all CPU access for the initial portion of the reset sequence. While Flash memory reads and access to most Flash registers are possible when the hold is removed, writes to the FCCOBIX, FCCOBHI, and FCCOBLO registers are ignored. Completion of the reset sequence is marked by setting CCIF high which enables writes to the FCCOBIX, FCCOBHI, and FCCOBLO registers to the FCCOBIX, FCCOBHI, and FCCOBLO registers to the FCCOBIX.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

Read: Anytime but will always return 0x0000 (1 state is transient)

#### Write: Anytime

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FOC[7:0] | <ul> <li>Force Output Compare Action for Channel 7:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set.</li> <li>Note: A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. If forced output compare on any channel occurs at the same time as the successful output compare then forced output compare action will take precedence and interrupt flag won't get set.</li> </ul> |

### 14.3.2.3 Output Compare 7 Mask Register (OC7M)

# Module Base + 0x0002

| ^^^^   |       |       |       | ~~~~~ | ~~~~~ | ~~~~~ |       |       |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 14-8. Output Compare 7 Mask Register (OC7M)

Read: Anytime

Write: Anytime

#### Table 14-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

|     |   | s are shown in Table A-4. unless<br>s are tested to be valid with no F |        |        |      |      |     |        |

|-----|---|------------------------------------------------------------------------|--------|--------|------|------|-----|--------|

| Num | С | Rating <sup>(1)</sup>                                                  |        | Symbol | Min  | Тур  | Мах | Unit   |

| 1   | Ρ | Resolution                                                             | 12-Bit | LSB    |      | 1.25 |     | mV     |

| 2   | Ρ | Differential Nonlinearity                                              | 12-Bit | DNL    | -4   | ±2   | 4   | counts |

| 3   | Р | Integral Nonlinearity                                                  | 12-Bit | INL    | -5   | ±2.5 | 5   | counts |

| 4   | Ρ | Absolute Error <sup>(2)</sup>                                          | 12-Bit | AE     | -7   | ±4   | 7   | counts |

| 5   | С | Resolution                                                             | 10-Bit | LSB    |      | 5    |     | mV     |

| 6   | С | Differential Nonlinearity                                              | 10-Bit | DNL    | -1   | ±0.5 | 1   | counts |

| 7   | С | Integral Nonlinearity                                                  | 10-Bit | INL    | -2   | ±1   | 2   | counts |

| 8   | С | Absolute Error <sup>2.</sup>                                           | 10-Bit | AE     | -3   | ±2   | 3   | counts |

| 9   | С | Resolution                                                             | 8-Bit  | LSB    |      | 20   |     | mV     |

| 10  | С | Differential Nonlinearity                                              | 8-Bit  | DNL    | -0.5 | ±0.3 | 0.5 | counts |

| 11  | С | Integral Nonlinearity                                                  | 8-Bit  | INL    | -1   | ±0.5 | 1   | counts |

| 12  | С | Absolute Error <sup>2.</sup>                                           | 8-Bit  | AE     | -1.5 | ±1   | 1.5 | counts |

#### Table A-16. ATD Conversion Performance 5V range

1. The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

2. These values include the quantization error which is inherently 1/2 count for any A/D converter.

#### Table A-17. ATD Conversion Performance 3.3V range

| Num | C Rating <sup>(1)</sup> |                               | 1)     | Symbol | Min  | Тур   | Max | Unit   |

|-----|-------------------------|-------------------------------|--------|--------|------|-------|-----|--------|

| 1   | Р                       | Resolution                    | 12-Bit | LSB    |      | 0.80  |     | mV     |

| 2   | Р                       | Differential Nonlinearity     | 12-Bit | DNL    | -6   | ±3    | 6   | counts |

| 3   | Р                       | Integral Nonlinearity         | 12-Bit | INL    | -7   | ±3    | 7   | counts |

| 4   | Р                       | Absolute Error <sup>(2)</sup> | 12-Bit | AE     | -8   | ±4    | 8   | counts |

| 5   | С                       | Resolution                    | 10-Bit | LSB    |      | 3.22  |     | mV     |

| 6   | С                       | Differential Nonlinearity     | 10-Bit | DNL    | -1.5 | ±1    | 1.5 | counts |

| 7   | С                       | Integral Nonlinearity         | 10-Bit | INL    | -2   | ±1    | 2   | counts |

| 8   | С                       | Absolute Error <sup>2.</sup>  | 10-Bit | AE     | -3   | ±2    | 3   | counts |

| 9   | С                       | Resolution                    | 8-Bit  | LSB    |      | 12.89 |     | mV     |

| 10  | С                       | Differential Nonlinearity     | 8-Bit  | DNL    | -0.5 | ±0.3  | 0.5 | counts |

| 11  | С                       | Integral Nonlinearity         | 8-Bit  | INL    | -1   | ±0.5  | 1   | counts |

| 12  | С                       | Absolute Error <sup>2.</sup>  | 8-Bit  | AE     | -1.5 | ±1    | 1.5 | counts |

1. The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

2. These values include the quantization error which is inherently 1/2 count for any A/D converter.