Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, SCI, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 64                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                           |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p128j0cqk |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |            |           |          |              |                              |        | •                  |                |                                            |

|-----------|------------|-----------|----------|--------------|------------------------------|--------|--------------------|----------------|--------------------------------------------|

| Р         | ackage Pi  | in        | Function |              |                              | Power  | Internal<br>Resist |                | Description                                |

| QFP<br>80 | LQFP<br>64 | QFN<br>48 | Pin      | 2nd<br>Func. | 3rd<br>Func.                 | Supply | CTRL               | Reset<br>State | Description                                |

| 1         | 1          | 1         | PP3      | KWP3         | PWM3                         | VDDX   | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM channel      |

| 2         | 2          | 2         | PP2      | KWP2         | PWM2                         | VDDX   | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM channel      |

| 3         | 3          | 3         | PP1      | KWP1         | PWM1                         | VDDX   | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM channel      |

| 4         | 4          | -         | PP0      | KWP0         | PWM0                         | VDDX   | PERP/PPSP          | Disabled       | Port P I/O, interrupt,<br>PWM/ channel     |

| 5         | 5          | 4         | PT0      | IOC0         | PWM0                         | VDDX   | PERT/PPST          | Disabled       | Port T I/O, TIM channel                    |

| 6         | 6          | 5         | PT1      | IOC1         | —                            | VDDX   | PERT/PPST          | Disabled       | Port T I/O, TIM channel                    |

| 7         | 7          | 6         | PT2      | IOC2         | —                            | VDDX   | PERT/PPST          | Disabled       | Port T I/O, TIM channel                    |

| 8         | 8          | 7         | PT3      | IOC3         | _                            | VDDX   | PERT/PPST          | Disabled       | Port T I/O, TIM channel                    |

| 9         | 9          | -         | PJ0      | KWJ0         | —                            | VDDX   | PERJ/PPSJ          | Up             | Port J I/O, interrupt                      |

| 10        | 10         | -         | PJ1      | KWJ1         | —                            | VDDX   | PERJ/PPSJ          | Up             | Port J I/O, interrupt                      |

| 11        | 11         | 8         | PT4      | IOC4         | PWM4                         | VDDX   | PERT/PPST          | Disabled       | Port T I/O, PWM/TIM channel                |

| 12        | 12         | 9         | PT5      | IOC5         | PWM5<br>or<br>API_EX<br>TCLK | VDDX   | PERT/PPST          | Disabled       | Port T I/O, PWM/TIM<br>channel, API output |

| 13        | 13         | 10        | PT6      | IOC6         |                              | VDDX   | PERT/PPST          | Disabled       | Port T I/O, channel of TIM                 |

| 14        | 14         | 11        | PT7      | IOC7         |                              | VDDX   | PERT/PPST          | Disabled       | Port T I/O, channel of TIM                 |

| 15        | 15         | 12        | BKGD     | MODC         | _                            | VDDX   | Always on          | Up             | Background debug                           |

## Table 1-8. Pin-Out Summary<sup>(1)</sup>

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6, 3-1<br>PTT | <ul> <li>Port T general purpose input/output data—Data Register, TIM output</li> <li>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin.</li> <li>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.</li> <li>The TIM output function takes precedence over the general purpose I/O function if the related channel is enabled.</li> </ul>                                                                                                                                                                                                                                                                   |

| 5<br>PTT        | <ul> <li>Port T general purpose input/output data—Data Register, TIM output, routed PWM output, API_EXTCLK output When not used with the alternative function, the associated pin can be used as general purpose I/O. In general purpose output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered pin input state is read.</li> <li>The TIM output function takes precedence over the routed PWM, API_EXTCLK function and the general purpose I/O function if the related channel is enabled.</li> <li>The routed PWM function takes precedence over API_EXTCLK and the general purpose I/O function if the related channel is enabled.</li> </ul>                                                             |

| 4,0<br>PTT      | <ul> <li>The API_EXTCLK takes precedence over the general purpose I/O function if enabled.</li> <li>Port T general purpose input/output data—Data Register, TIM output, routed PWM output<br/>When not used with the alternative function, the associated pin can be used as general purpose I/O. In general<br/>purpose output mode the register bit value is driven to the pin.<br/>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the buffered<br/>pin input state is read.</li> <li>The TIM output function takes precedence over the routed PWM and the general purpose I/O function if the<br/>related channel is enabled.</li> <li>The routed PWM function takes precedence over the general purpose I/O function if the related channel is<br/>enabled.</li> </ul> |

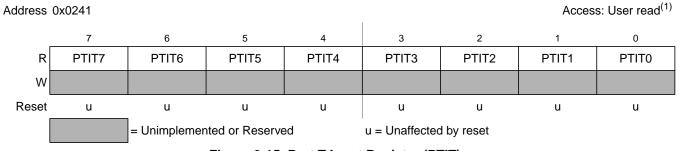

# 2.3.17 Port T Input Register (PTIT)

#### Figure 2-15. Port T Input Register (PTIT)

1. Read: Anytime

Write:Never, writes to this register have no effect.

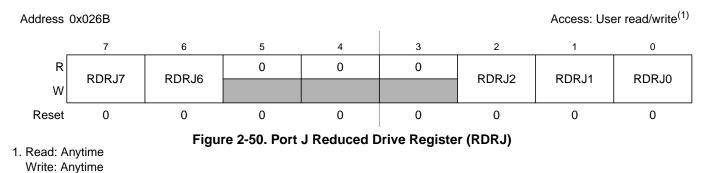

# 2.3.52 Port J Reduced Drive Register (RDRJ)

#### Table 2-46. RDRJ Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-6, 2-0<br>RDRJ | <b>Port J reduced drive</b> —Select reduced drive for output pin<br>This bit configures the drive strength of the associated output pin as either full or reduced. If a pin is used as input<br>this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin.<br>1 Reduced drive selected (approx. 1/5 of the full drive strength)<br>0 Full drive strength enabled |  |

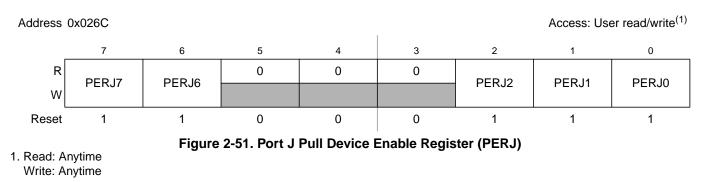

## 2.3.53 Port J Pull Device Enable Register (PERJ)

#### Table 2-47. PERJ Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6, 2-0<br>PERJ | <b>Port J pull device enable</b> —Enable pull device on input pin<br>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has<br>no effect. The polarity is selected by the related polarity select register bit. |

|                  | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                      |

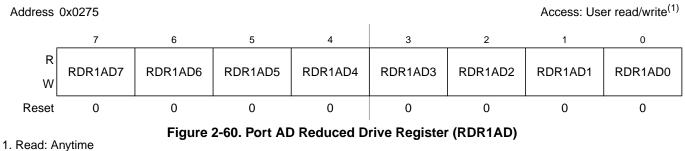

## 2.3.62 Port AD Reduced Drive Register (RDR1AD)

Write: Anytime

#### Table 2-56. RDR1AD Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDR1AD | <ul> <li>Port AD reduced drive—Select reduced drive for output pin</li> <li>This bit configures the drive strength of the associated output pin as either full or reduced. If a pin is used as input this bit has no effect. The reduced drive function is independent of which function is being used on a particular pin.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength)</li> <li>0 Full drive strength enabled</li> </ul> |

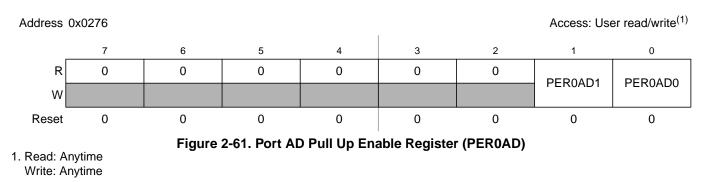

## 2.3.63 Port AD Pull Up Enable Register (PER0AD)

#### Table 2-57. PER0AD Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-0<br>PER0AD | <ul> <li>Port AD pull-up enable—Enable pull-up device on input pin</li> <li>This bit controls whether a pull device on the associated port input pin is active. If a pin is used as output this bit has no effect.</li> <li>1 Pull device enabled</li> <li>0 Pull device disabled</li> </ul> |  |

### 6.4.5.2.1 Normal Mode

In Normal Mode, change of flow (COF) program counter (PC) addresses are stored.

COF addresses are defined as follows:

- Source address of taken conditional branches (long, short, bit-conditional, and loop primitives)

- Destination address of indexed JMP, JSR, and CALL instruction

- Destination address of RTI, RTS, and RTC instructions

- Vector address of interrupts, except for BDM vectors

LBRA, BRA, BSR, BGND as well as non-indexed JMP, JSR, and CALL instructions are not classified as change of flow and are not stored in the trace buffer.

Stored information includes the full 18-bit address bus and information bits, which contains a source/destination bit to indicate whether the stored address was a source address or destination address.

#### NOTE

When a COF instruction with destination address is executed, the destination address is stored to the trace buffer on instruction completion, indicating the COF has taken place. If an interrupt occurs simultaneously then the next instruction carried out is actually from the interrupt service routine. The instruction at the destination address of the original program flow gets executed after the interrupt service routine.

In the following example an IRQ interrupt occurs during execution of the indexed JMP at address MARK1. The BRN at the destination (SUB\_1) is not executed until after the IRQ service routine but the destination address is entered into the trace buffer to indicate that the indexed JMP COF has taken place.

| MARK1<br>MARK2 | LDX<br>JMP<br>NOP | #SUB_1<br>0,X               | ;; | IRQ interrupt occurs during execution of this |

|----------------|-------------------|-----------------------------|----|-----------------------------------------------|

| SUB_1          | BRN               | *                           | ;  | JMP Destination address TRACE BUFFER ENTRY 1  |

|                |                   |                             | ;  | RTI Destination address TRACE BUFFER ENTRY 3  |

|                | NOP               |                             | ;  |                                               |

| ADDR1          | DBNE              | A,PART5                     | ;  | Source address TRACE BUFFER ENTRY 4           |

|                |                   |                             |    |                                               |

| IRQ_ISR        | LDAB              | #\$F0                       | ;  | IRQ Vector \$FFF2 = TRACE BUFFER ENTRY 2      |

|                | STAB              | VAR_C1                      |    |                                               |

|                | RTI               |                             | ;  |                                               |

|                | Th                | e execution flow taking int | to | account the IRQ is as follows                 |

|                | LDX               | #SUB 1                      |    |                                               |

| MARK1          | JMP               | 0,X                         | ;  |                                               |

| IRQ_ISR        | LDAB              | #\$F0                       |    |                                               |

| 1102_1010      | STAB              | VAR C1                      | '  |                                               |

|                | RTI               | VIII(_C1                    |    |                                               |

| SUB_1          | BRN               | *                           | '  |                                               |

| 202_1          |                   |                             |    |                                               |

;

;

ADDR1

NOP

DBNE

A, PART5

## 7.4.6 System Clock Configurations

## 7.4.6.1 PLL Engaged Internal Mode (PEI)

This mode is the default mode after System Reset or Power-On Reset.

The Bus Clock is based on the PLLCLK, the reference clock for the PLL is internally generated (IRC1M). The PLL is configured to 64 MHz VCOCLK with POSTDIV set to 0x03. If locked (LOCK=1) this results in a PLLCLK of 16 MHz and a Bus Clock of 8 MHz. The PLL can be re-configured to other bus frequencies.

The clock sources for COP and RTI are based on the internal reference clock generator (IRC1M).

## 7.4.6.2 PLL Engaged External Mode (PEE)

In this mode, the Bus Clock is based on the PLLCLK as well (like PEI). The reference clock for the PLL is based on the external oscillator. The adaptive spike filter and detection logic which uses the VCOCLK to filter and qualify the external oscillator clock can be enabled.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock.

This mode can be entered from default mode PEI by performing the following steps:

- 1. Configure the PLL for desired bus frequency.

- 2. Optionally the adaptive spike filter and detection logic can be enabled by calculating the integer value for the OSCFIL[4:0] bits and setting the bandwidth (OSCBW) accordingly.

- 3. Enable the external oscillator (OSCE bit).

- 4. Wait for the PLL being locked (LOCK = 1) and the oscillator to start-up and additionally being qualified if the adaptive spike filter is enabled (UPOSC = 1).

- 5. Clear all flags in the CPMUFLG register to be able to detect any future status bit change.

- 6. Optionally status interrupts can be enabled (CPMUINT register).

Since the adaptive spike filter (filter and detection logic) uses the VCOCLK to continuously filter and qualify the external oscillator clock, loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status in PEE mode is as follows:

• The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

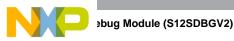

#### Figure 8-4. MSCAN Control Register 0 (CANCTL0)

1. Read: Anytime Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode)

#### NOTE

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

#### Table 8-3. CANCTL0 Register Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>RXFRM <sup>(1)</sup> | <ul> <li>Received Frame Flag — This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. After it is set, it remains set until cleared by software or reset. Clearing is done by writing a 1. Writing a 0 is ignored. This bit is not valid in loopback mode.</li> <li>0 No valid message was received since last clearing this flag</li> <li>1 A valid message was received since last clearing of this flag</li> </ul>                                                                                                                                                    |  |  |  |  |

| 6<br>RXACT                | <ul> <li>Receiver Active Status — This read-only flag indicates the MSCAN is receiving a message. The flag is controlled by the receiver front end. This bit is not valid in loopback mode.</li> <li>0 MSCAN is transmitting or idle<sup>2</sup></li> <li>1 MSCAN is receiving a message (including when arbitration is lost)<sup>(2)</sup></li> </ul>                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 5<br>CSWAI <sup>(3)</sup> | <ul> <li>CAN Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling all the clocks at the CPU bus interface to the MSCAN module.</li> <li>0 The module is not affected during wait mode</li> <li>1 The module ceases to be clocked during wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 4<br>SYNCH                | <ul> <li>Synchronized Status — This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and able to participate in the communication process. It is set and cleared by the MSCAN.</li> <li>0 MSCAN is not synchronized to the CAN bus</li> <li>1 MSCAN is synchronized to the CAN bus</li> </ul>                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 3<br>TIME                 | <b>Timer Enable</b> — This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock rate.<br>If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. Right after the EOF of a valid message on the CAN bus, the time stamp is written to the highest bytes (0x000E, 0x000F) in the appropriate buffer (see Section 8.3.3, "Programmer's Model of Message Storage"). The internal timer is reset (all bits set to 0) when disabled. This bit is held low in initialization mode.<br>0 Disable internal MSCAN timer<br>1 Enable internal MSCAN timer |  |  |  |  |

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

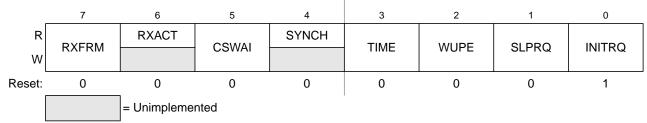

#### Figure 8-36, Transmit Buffer Priority Register (TBPR)

1. Read: Anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

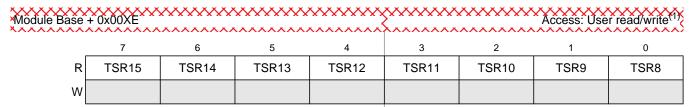

#### 8.3.3.5 Time Stamp Register (TSRH–TSRL)

х

х

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 8.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

х Figure 8-37. Time Stamp Register — High Byte (TSRH)

х

х

1. Read: Anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)") Write: Unimplemented

Access: User read/write Module Base + 0x00XF 7 6 5 4 3 2 1 0 R TSR7 TSR6 TSR5 TSR4 TSR3 TSR2 TSR1 TSR0 W Reset: х х х х х х х х Figure 8-38. Time Stamp Register — Low Byte (TSRL)

S12P-Family Reference Manual, Rev. 1.13

х

х

Reset:

х

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN9                                                                           |

| 1     | 0     | 1     | 1     | AN9                                                                           |

| 1     | 1     | 0     | 0     | AN9                                                                           |

| 1     | 1     | 0     | 1     | AN9                                                                           |

| 1     | 1     | 1     | 0     | AN9                                                                           |

| 1     | 1     | 1     | 1     | AN9                                                                           |

Table 9-2. Multi-Channel Wrap Around Coding

1. If only AN0 should be converted use MULT=0.

#### 9.3.2.2 **ATD Control Register 1 (ATDCTL1)**

Writes to this register will abort current conversion sequence.

Module Base + 0x0001

|        | 7        | 6     | 5     | 4       | 3        | 2        | 1        | 0        |

|--------|----------|-------|-------|---------|----------|----------|----------|----------|

| R<br>W | ETRIGSEL | SRES1 | SRES0 | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |

| Reset  | 0        | 0     | 1     | 0       | 1        | 1        | 1        | 1        |

Figure 9-4. ATD Control Register 1 (ATDCTL1)

Read: Anytime

Write: Anytime

#### Table 9-3. ATDCTL1 Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>ETRIGSEL    | <b>External Trigger Source Select</b> — This bit selects the external trigger source to be either one of the AD channels or one of the ETRIG3-0 inputs. See device specification for availability and connectivity of ETRIG3-0 inputs. If a particular ETRIG3-0 input option is not available, writing a 1 to ETRISEL only sets the bit but has not effect, this means that one of the AD channels (selected by ETRIGCH3-0) is configured as the source for external trigger. The coding is summarized in Table 9-5. |  |  |  |  |  |

| 6–5<br>SRES[1:0] | <b>A/D Resolution Select</b> — These bits select the resolution of A/D conversion results. See Table 9-4 for coding.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

## 11.1.2 Features

The SCI includes these distinctive features:

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit data format

- Separately enabled transmitter and receiver

- Programmable polarity for transmitter and receiver

- Programmable transmitter output parity

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receive wakeup on active edge

- Transmit collision detect supporting LIN

- Break Detect supporting LIN

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

## 11.1.3 Modes of Operation

The SCI functions the same in normal, special, and emulation modes. It has two low power modes, wait and stop modes.

- Run mode

- Wait mode

- Stop mode

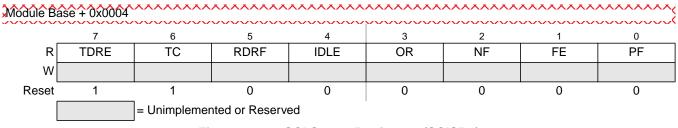

## 11.3.2.7 SCI Status Register 1 (SCISR1)

The SCISR1 and SCISR2 registers provides inputs to the MCU for generation of SCI interrupts. Also, these registers can be polled by the MCU to check the status of these bits. The flag-clearing procedures require that the status register be read followed by a read or write to the SCI data register. It is permissible to execute other instructions between the two steps as long as it does not compromise the handling of I/O, but the order of operations is important for flag clearing.

#### Figure 11-10. SCI Status Register 1 (SCISR1)

Read: Anytime

Write: Has no meaning or effect

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set when the transmit shift register receives a byte from the SCI data register. When TDRE is 1, the transmit data register (SCIDRH/L) is empty and can receive a new value to transmit.Clear TDRE by reading SCI status register 1 (SCISR1), with TDRE set and then writing to SCI data register low (SCIDRL).         0       No byte transferred to transmit shift register; transmit data register empty                                                                                                                                                                                                                                               |

| 6<br>TC   | Transmit Complete Flag — TC is set low when there is a transmission in progress or when a preamble or break character is loaded. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL). TC is cleared automatically when data, preamble, or break is queued and ready to be sent. TC is cleared in the event of a simultaneous set and clear of the TC flag (transmission not complete).         0       Transmission in progress         1       No transmission in progress |

| 5<br>RDRF | Receive Data Register Full Flag — RDRF is set when the data in the receive shift register transfers to the SCI data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data register low (SCIDRL).         0       Data not available in SCI data register         1       Received data available in SCI data register                                                                                                                                                                                                                                                                                                                                 |

| 4<br>IDLE | Idle Line Flag — IDLE is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M =1) appear on the receiver input. Once the IDLE flag is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag.Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).         0       Receiver input is either active now or has never become active since the IDLE flag was last cleared 1 Receiver input has become idle         Note: When the receiver wakeup bit (RWU) is set, an idle line condition does not set the IDLE flag.                                                  |

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3<br>OR | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs:</li> </ul>   |  |  |  |  |  |  |

|         | <ol> <li>After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear)</li> <li>Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set);</li> <li>Read data register SCIDRL (returns first frame and clears RDRF flag in the status register);</li> <li>Read status register SCISR1 (returns RDRF clear and OR set).</li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received.</li> </ol> |  |  |  |  |  |  |

| 2<br>NF | <ul> <li>Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1) and then reading SCI data register low (SCIDRL).</li> <li>0 No noise</li> <li>1 Noise</li> </ul>                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul>                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>                                                                                                                                                                                                                                |  |  |  |  |  |  |

#### Table 11-11. SCISR1 Field Descriptions (continued)

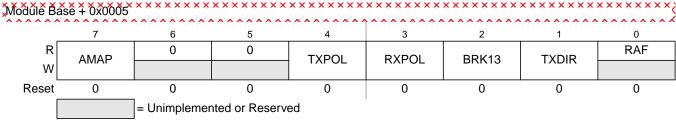

## 11.3.2.8 SCI Status Register 2 (SCISR2)

#### Figure 11-11. SCI Status Register 2 (SCISR2)

Read: Anytime

S12P-Family Reference Manual, Rev. 1.13

### NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

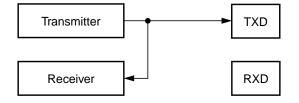

## 11.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

Figure 11-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

#### NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

## 11.5 Initialization/Application Information

## 11.5.1 Reset Initialization

See Section 11.3.2, "Register Descriptions".

## 11.5.2 Modes of Operation

## 11.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 11.4.5.2, "Character Transmission".

## 11.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

| Field              | Description                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                            |  |  |  |  |  |  |

| 2<br>RSVD          | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 13.4.5, "Flash Command Description," and Section 13.6, "Initialization" for details. |  |  |  |  |  |  |

#### Table 13-14. FSTAT Field Descriptions (continued)

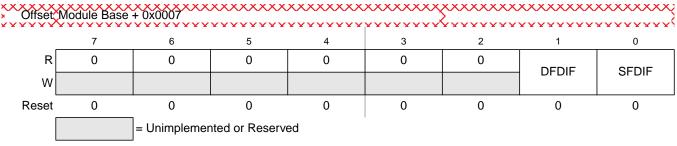

## 13.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

#### Figure 13-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

#### Table 13-15. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation was attempted on a Flash block that was under a Flash command operation.<sup>(1)</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.</li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or an invalid Flash array read operation attempted</li> </ul>               |

| 0<br>SFDIF | Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation was attempted on a Flash block that was under a Flash command operation. <sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.<br>0 No single bit fault detected<br>1 Single bit fault detected and corrected or an invalid Flash array read operation attempted |

The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (read attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

## 13.3.2.9 P-Flash Protection Register (FPROT)

The FPROT register defines which P-Flash sectors are protected against program and erase operations.

Figure 13-25. Flash Reserved7 Register (FRSV7)

All bits in the FRSV7 register read 0 and are not writable.

## 13.4 Functional Description

## 13.4.1 Modes of Operation

The FTMRC128K1 module provides the modes of operation shown in Table 13-25. The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, and DFPROT registers, Scratch RAM writes, and the command set availability (see Table 13-27).

Table 13-25. Modes and Mode Control Inputs

| FTMRC Input    |  |  |  |

|----------------|--|--|--|

| mmc_mode_ss_t2 |  |  |  |

| 0              |  |  |  |

| 1              |  |  |  |

|                |  |  |  |

## 13.4.2 IFR Version ID Word

The version ID word is stored in the IFR at address  $0x0_40B6$ . The contents of the word are defined in Table 13-26.

| Table | 13-26. | IFR | Version | ID | Fields |

|-------|--------|-----|---------|----|--------|

|-------|--------|-----|---------|----|--------|

| [15:4]   | [3:0]  |  |  |

|----------|--------|--|--|

| Reserved | VERNUM |  |  |

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

## 13.4.3 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

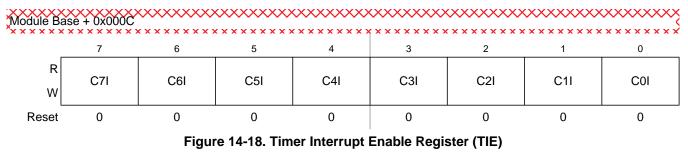

## 14.3.2.10 Timer Interrupt Enable Register (TIE)

#### Read: Anytime

Write: Anytime.

#### Table 14-12. TIE Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Input Capture/Output Compare "x" Interrupt Enable</b> — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |

## 14.3.2.11 Timer System Control Register 2 (TSCR2)

# Module Base + 0x000D

|       | 7                           | 6 | 5 | 4 | 3    | 2    | 1   | 0   |

|-------|-----------------------------|---|---|---|------|------|-----|-----|

| R     | TOI                         | 0 | 0 | 0 | TCRE | PR2  | PR1 | PR0 |

| w     | 101                         |   |   |   | TORE | TINZ |     |     |

| Reset | 0                           | 0 | 0 | 0 | 0    | 0    | 0   | 0   |

|       | = Unimplemented or Reserved |   |   |   |      |      |     |     |

#### Figure 14-19. Timer System Control Register 2 (TSCR2)

Read: Anytime

Write: Anytime.

| Table 14-13 | . TSCR2 Fie | Id Descriptions |

|-------------|-------------|-----------------|

|-------------|-------------|-----------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOI     | Timer Overflow Interrupt Enable         0 Interrupt inhibited.         1 Hardware interrupt requested when TOF flag set.                                                                                                                                                                                                                                                                                                                                       |

| 3<br>TCRE    | Timer Counter Reset Enable — This bit allows the timer counter to be reset by a successful output compare 7<br>event. This mode of operation is similar to an up-counting modulus counter.0Counter reset inhibited and counter free runs.1Counter reset by a successful output compare 7.If TC7 = 0x0000 and TCRE = 1, TCNT will stay at 0x0000 continuously. If TC7 = 0xFFFF and TCRE = 1, TOF<br>will never be set when TCNT is reset from 0xFFFF to 0x0000. |

| 2<br>PR[2:0] | <b>Timer Prescaler Select</b> — These three bits select the frequency of the timer prescaler clock derived from the Bus Clock as shown in Table 14-14.                                                                                                                                                                                                                                                                                                         |

| PR2 | PR1 | PR0 | Timer Clock     |

|-----|-----|-----|-----------------|

| 0   | 0   | 0   | Bus Clock / 1   |

| 0   | 0   | 1   | Bus Clock / 2   |

| 0   | 1   | 0   | Bus Clock / 4   |

| 0   | 1   | 1   | Bus Clock / 8   |

| 1   | 0   | 0   | Bus Clock / 16  |

| 1   | 0   | 1   | Bus Clock / 32  |

| 1   | 1   | 0   | Bus Clock / 64  |

| 1   | 1   | 1   | Bus Clock / 128 |

| Table 14-14. Timer Clock Selection |

|------------------------------------|

|------------------------------------|

#### NOTE

The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero.

## 14.3.2.12 Main Timer Interrupt Flag 1 (TFLG1)

\*\*\*\*\* Module Base + 0x000E х 7 6 5 3 2 0 4 1 R C7F C6F C5F C4F C3F C2F C1F C0F W 0 0 0 0 0 0 0 0 Reset

Figure 14-20. Main Timer Interrupt Flag 1 (TFLG1)

#### Read: Anytime

Write: Used in the clearing mechanism (set bits cause corresponding bits to be cleared). Writing a zero will not affect current status of the bit.

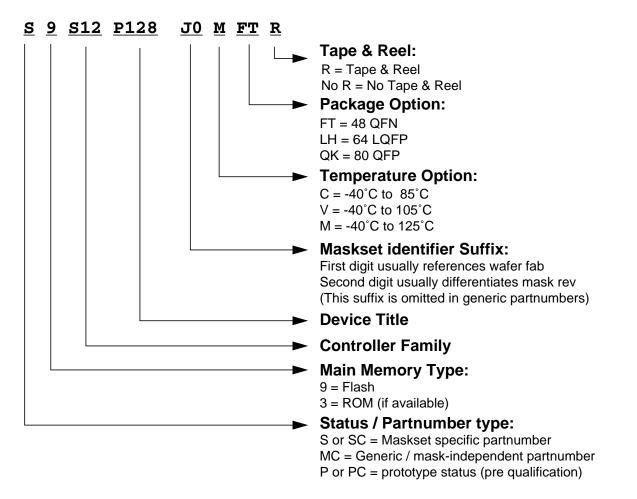

# Appendix B Ordering Information

The following figure provides an ordering partnumber example for the devices covered by this data book. There are two options when ordering a device. Customers must choose between ordering either the mask-specific partnumber or the generic / mask-independent partnumber. Ordering the mask-specific partnumber enables the customer to specify which particular maskset they will receive whereas ordering the generic maskset means that FSL will ship the currently preferred maskset (which may change over time).

In either case, the marking on the device will always show the generic / mask-independent partnumber and the mask set number.

### NOTE

# The mask identifier suffix and the Tape & Reel suffix are always both omitted from the partnumber which is actually marked on the device.

For specific partnumbers to order, please contact your local sales office. The below figure illustrates the structure of a typical mask-specific ordering number for the MC9S12P-Family devices

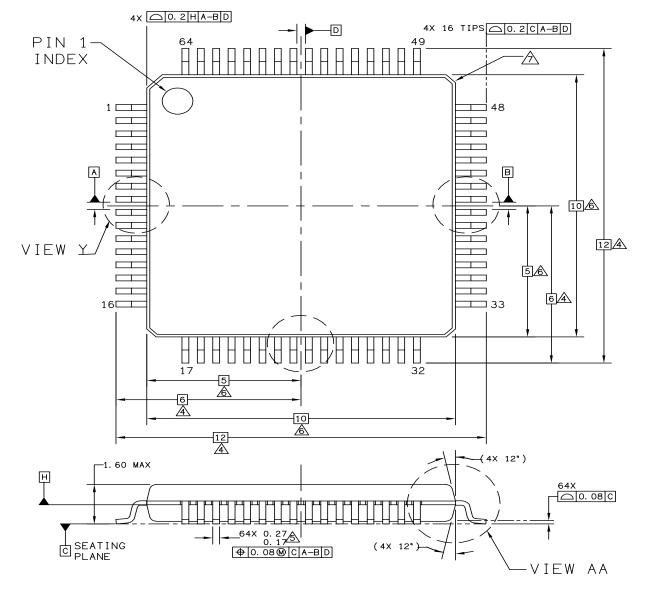

C.3 64 LQFP Package Mechanical Outline

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                       | PRINT VERSION NO | DT TO SCALE |  |  |

|---------------------------------------------------------|-----------|---------------------------------|------------------|-------------|--|--|

| TITLE: 64LD LQFP,                                       |           | DOCUMENT NO: 98ASS23234W REV: E |                  |             |  |  |

| 10 X 10 X 1.4 P                                         | •         | CASE NUMBER: 840F-02 11 AUG 200 |                  |             |  |  |

| 0.5 PITCH, CASE OL                                      | ITLINE    | STANDARD: JEDEC MS-026 BCD      |                  |             |  |  |

S12P-Family Reference Manual, Rev. 1.13

## 0x00D8-0x00DF Serial Peripheral Interface (SPI) Map

| Address        | Name       |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x00DC SPIDRH  | SDIDDU     | R | R15   | R14   | R13   | R12   | R11   | R10   | R9    | R8    |

|                | SFIDRIT    | W | T15   | T14   | T13   | T12   | T11   | T10   | Т9    | T8    |

| 0x00DD SPI0DRI | SDIODDI    | R | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0    |

|                | SPIUDRL    | W | T7    | T6    | T5    | T4    | Т3    | T2    | T1    | Т0    |

| 0x00DE Reser   | Percentred | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                | Reserved   | W |       |       |       |       |       |       |       |       |

| 0x00DF         | Reserved   | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                |            | W |       |       |       |       |       |       |       |       |

#### 0x00E0-0x00FF Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x00E0- | Recorved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x00FF  | Reserved | W |       |       |       |       |       |       |       |       |

## 0x0100-0x0113 NVM Contol Register (FTMRC) Map

| Address | Name          |            | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   |       |

|---------|---------------|------------|--------|--------|--------|--------|--------|---------|---------|---------|-------|

| 0x0100  | FCLKDIV       | R<br>W     | FDIVLD | FDIV6  | FDIV5  | FDIV4  | FDIV3  | FDIV2   | FDIV1   | FDIV0   |       |

| 0x0101  | FSEC          | R          | KEYEN1 | KEYEN0 | RNV5   | RNV4   | RNV3   | RNV2    | SEC1    | SEC0    |       |

| 0.0101  | 1 GLC         | W          |        |        |        |        |        |         |         |         |       |

| 0x0102  | FCCOBIX       | R          | 0      | 0      | 0      | 0      | 0      | CCOBIX2 | CCOBIX1 | ССОВІХО |       |

|         |               | W          |        |        |        |        |        |         |         |         |       |

| 0x0103  | FRSV0         | R          | 0      | 0      | 0      | 0      | 0      | 0       | 0       | 0       |       |

|         |               | W          |        | 0      | 0      |        | 0      | 0       |         |         |       |

| 0x0104  | FCNFG         | R<br>W     | CCIE   | 0      | 0      | IGNSF  | 0      | 0       | FDFD    | FSFD    |       |

|         |               | R          | 0      | 0      | 0      | 0      | 0      | 0       |         |         |       |

| 0x0105  | FERCNEG       | FERCNEG    | W      | -      | 0      | 0      | 0      | 0       | 0       | DFDIE   | SFDIE |

|         |               | R          |        | 0      |        |        | MGBUSY | RSVD    | MGSTAT1 | MGSTAT0 |       |

| 0x0106  | FSTAT         | Ŵ          | CCIF   |        | ACCERR | FPVIOL |        | INCORD  |         |         |       |

| 0.0407  | FEDOTAT       | R          | 0      | 0      | 0      | 0      | 0      | 0       | DEDIE   | 05015   |       |

| 0x0107  | FERSTAT       | W          |        |        |        |        |        |         | DFDIF   | SFDIF   |       |

| 0x0108  | FPROT         | R<br>W     | FPOPEN | RNV6   | FPHDIS | FPHS1  | FPHS0  | FPLDIS  | FPLS1   | FPLS0   |       |

|         |               | R          |        | 0      | 0      | 0      |        |         |         |         |       |

| 0x0109  | 0x0109 DFPROT | 109 DFPROT | W      | DPOPEN |        |        |        | DPS3    | DPS2    | DPS1    | DPS0  |

| 0x010A  | FCCOBHI       | R          | CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10  | CCOB9   | CCOB8   |       |

| 0,010/1 | 10000111      | W          | 000010 | 000014 | 000010 | 000012 | COODIN | 000010  |         |         |       |

| 0x010B  | FCCOBLO       | R<br>W     | CCOB7  | CCOB6  | CCOB5  | CCOB4  | ССОВЗ  | CCOB2   | CCOB1   | CCOB0   |       |

| 0x010C  | FRSV1         | R          | 0      | 0      | 0      | 0      | 0      | 0       | 0       | 0       |       |

| UXUTUC  | FROVI         | W          |        |        |        |        |        |         |         |         |       |

S12P-Family Reference Manual, Rev. 1.13