Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 6K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-TFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p128j0mftr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.7.3 Detailed Signal Descriptions

## 1.7.3.1 EXTAL, XTAL — Oscillator Pins

EXTAL and XTAL are the crystal driver and external clock pins. On reset all the device clocks are derived from the internal reference clock. XTAL is the oscillator output.

## 1.7.3.2 RESET — External Reset Pin

The  $\overline{\text{RESET}}$  pin is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset. The  $\overline{\text{RESET}}$  pin has an internal pull-up device.

### 1.7.3.3 TEST — Test Pin

This input only pin is reserved for factory test. This pin has an internal pull-down device.

#### NOTE

The TEST pin must be tied to  $V_{SSX}$  in all applications.

### 1.7.3.4 BKGD / MODC — Background Debug and Mode Pin

The BKGD/MODC pin is used as a pseudo-open-drain pin for the background debug communication. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of RESET. The BKGD pin has an internal pull-up device.

### 1.7.3.5 PAD[9:0] / AN[9:0] — Port AD Input Pins of ATD

PAD[9:0] are general-purpose input or output pins and analog inputs AN[9:0] of the analog-to-digital converter ATD.

## 1.7.3.6 PA[7:0] — Port A I/O Pins

PA[7:0] are general-purpose input or output pins.

### 1.7.3.7 PB[7:0] — Port B I/O Pins

PB[7:0] are general-purpose input or output pins.

### 1.7.3.8 **PE7** — Port E I/O Pin 7 / ECLKX2

PE7 is a general-purpose input or output pin. An internal pull-up is enabled during reset. It can be configured to output ECLKX2.

### 1.7.3.9 PE[6:5] — Port E I/O Pin 6-5

PE[6:5] are a general-purpose input or output pins.

## 1.7.3.30 PT4 / IOC4 / PWM4 — Port T I/O Pin 4

PT4 is a general-purpose input or output pin. It can be configured as timer (TIM) channel 4 or pulse width modulator (PWM) output 4.

## 1.7.3.31 PT[3:1] / IOC[3:1] — Port T I/O Pin [3:1]

PT[3:1] are a general-purpose input or output pins. They can be configured as timer (TIM) channels 3-1.

## 1.7.3.32 PT0 / IOC0 / PWM0 — Port T I/O Pin 0

PT0 is a general-purpose input or output pin. It can be configured as timer (TIM) channel 0 or pulse width modulator (PWM) output 0.

## 1.7.4 Power Supply Pins

MC9S12P-Family power and ground pins are described below.

Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible.

#### NOTE

All  $V_{SS}$  pins must be connected together in the application.

### 1.7.4.1 VDDX[2:1], VSSX[2:1] — Power and Ground Pins for I/O Drivers

External power and ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VDDX pins are connected together internally. All VSSX pins are connected together internally.

#### 1.7.4.2 VDDR — Power Pin for Internal Voltage Regulator

Power supply input to the internal voltage regulator.

#### 1.7.4.3 VSS3 — Core Ground Pin

The voltage supply of nominally 1.8V is derived from the internal voltage regulator. The return current path is through the VSS3 pin. No static external loading of these pins is permitted.

#### 1.7.4.4 VDDA, VSSA — Power Supply Pins for ATD and Voltage Regulator

These are the power supply and ground input pins for the analog-to-digital converter and the voltage regulator.

### 1.7.4.5 VRH, VRL — ATD Reference Voltage Input Pins

VRH and VRL are the reference voltage input pins for the analog-to-digital converter.

S12P-Family Reference Manual, Rev. 1.13

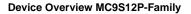

Figure 2-11. PIM Reserved Register

1. Read: Always reads 0x00 Write: Unimplemented

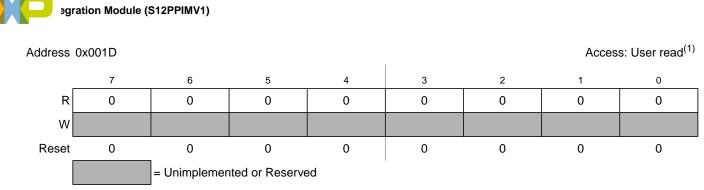

# 2.3.14 IRQ Control Register (IRQCR)

#### Figure 2-12. IRQ Control Register (IRQCR)

1. Read: See individual bit descriptions below. Write: See individual bit descriptions below.

#### Table 2-13. IRQCR Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IRQE  | IRQ select edge sensitive only—<br>Special mode: Read or write anytime.<br>Normal mode: Read anytime, write once.                                                                                                                                                            |

|            | <ul> <li>1 IRQ pin configured to respond only to falling edges. Falling edges on the IRQ pin will be detected anytime IRQE=1 and will be cleared only upon a reset or the servicing of the IRQ interrupt.</li> <li>0 IRQ pin configured for low level recognition</li> </ul> |

| 6<br>IRQEN | IRQ enable—<br>Read or write anytime.                                                                                                                                                                                                                                        |

|            | 1 IRQ pin is connected to interrupt logic<br>0 IRQ pin is disconnected from interrupt logic                                                                                                                                                                                  |

## 2.3.15 PIM Reserved Register

This register is reserved for factory testing of the PIM module and is not available in normal operation. Writing to this register when in special modes can alter the pin functionality.

#### Jund Debug Module (S12SBDMV1)

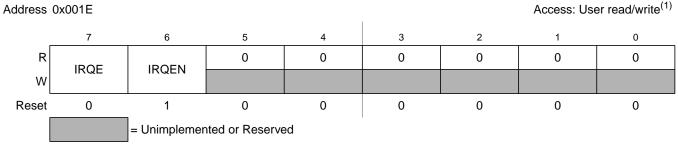

earlier. Synchronization between the host and target is established in this manner at the start of every bit time.

Figure 5-7 shows an external host transmitting a logic 1 and transmitting a logic 0 to the BKGD pin of a target system. The host is asynchronous to the target, so there is up to a one clock-cycle delay from the host-generated falling edge to where the target recognizes this edge as the beginning of the bit time. Ten target clock cycles later, the target senses the bit level on the BKGD pin. Internal glitch detect logic requires the pin be driven high no later that eight target clock cycles after the falling edge for a logic 1 transmission.

Since the host drives the high speedup pulses in these two cases, the rising edges look like digitally driven signals.

Figure 5-7. BDM Host-to-Target Serial Bit Timing

The receive cases are more complicated. Figure 5-8 shows the host receiving a logic 1 from the target system. Since the host is asynchronous to the target, there is up to one clock-cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target. The host holds the BKGD pin low long enough for the target to recognize it (at least two target clock cycles). The host must release the low drive before the target drives a brief high speedup pulse seven target clock cycles after the perceived start of the bit time. The host should sample the bit level about 10 target clock cycles after it started the bit time.

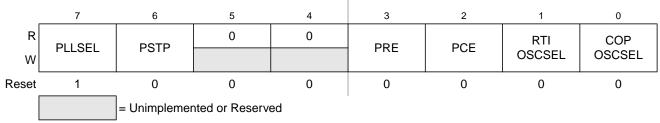

### 7.3.2.6 S12CPMU Clock Select Register (CPMUCLKS)

This register controls S12CPMU clock selection.

#### Figure 7-9. S12CPMU Clock Select Register (CPMUCLKS)

#### Read: Anytime

Write:

- 1. Only possible when PROT=0 (CPMUPROT register).

- 2. All bits anytime in Special Modes.

- 3. PLLSEL, PSTP, PRE, PCE, RTIOSCSEL: Anytime in Normal Mode.

- 4. COPOSCSEL: Anytime in normal mode until CPMUCOP write once has taken place. If COPOSCSEL was cleared by UPOSC=0 (entering Full Stop Mode with COPOSCSEL=1 or insufficient OSCCLK quality), then COPOSCSEL can be set once again.

After writing CPMUCLKS register, it is strongly recommended to read back CPMUCLKS register to make sure that write of PLLSEL, RTIOSCSEL and COPOSCSEL was successful.

| Table 7-5 | . CPMUCLKS | Descriptions |

|-----------|------------|--------------|

|-----------|------------|--------------|

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7         | PLL Select Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PLLSEL    | This bit selects the PLLCLK as source of the System Clocks (Core Clock and Bus Clock).<br>PLLSEL can only be set to 0, if UPOSC=1.<br>UPOSC= 0 sets the PLLSEL bit.<br>Entering Full Stop Mode sets the PLLSEL bit.<br>0 System clocks are derived from OSCCLK if oscillator is up (UPOSC=1, $f_{bus} = f_{osc} / 2$ .<br>1 System clocks are derived from PLLCLK, $f_{bus} = f_{PLL} / 2$ .                                                                                                                                                                                                                                                                                                                                                                                          |

| 6<br>PSTP | <ul> <li>Pseudo Stop Bit This bit controls the functionality of the oscillator during Stop Mode. 0 Oscillator is disabled in Stop Mode (Full Stop Mode). 1 Oscillator continues to run in Stop Mode (Pseudo Stop Mode), option to run RTI and COP. Note: Pseudo Stop Mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption. Note: When starting up the external oscillator (either by programming OSCE bit to 1 or on exit from Full Stop Mode with OSCE bit is already 1) the software must wait for a minimum time equivalent to the startup-time of the external oscillator t<sub>UPOSC</sub> before entering Pseudo Stop Mode.</li></ul> |

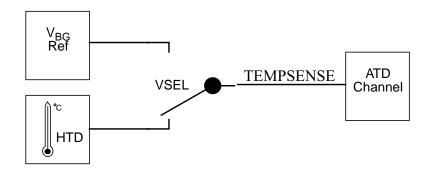

#### Figure 7-16. Voltage Access Select

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>VSEL | Voltage Access Select Bit — If set, the bandgap reference voltage $V_{BG}$ can be accessed internally (i.e.<br>multiplexed to an internal Analog to Digital Converter channel). If not set, the die temperature proportional<br>voltage $V_{HT}$ of the temperature sense can be accessed internally. See device level specification for connectivity.<br>0 An internal temperature proportional voltage $V_{HT}$ can be accessed internally.<br> |

| 3<br>HTE  | <ul> <li>High Temperature Enable Bit — This bit enables the high temperature sensor.</li> <li>0 The temperature sense is disabled.</li> <li>1 The temperature sense is enabled.</li> </ul>                                                                                                                                                                                                                                                        |

| 2<br>HTDS | <ul> <li>High Temperature Detect Status Bit — This read-only status bit reflects the temperature. status. Writes have no effect.</li> <li>0 Junction Temperature is below level T<sub>HTID</sub> or RPM.</li> <li>1 Junction Temperature is above level T<sub>HTIA</sub> and FPM.</li> </ul>                                                                                                                                                      |

| 1<br>HTIE | High Temperature Interrupt Enable Bit         0 Interrupt request is disabled.         1 Interrupt will be requested whenever HTIF is set.                                                                                                                                                                                                                                                                                                        |

| 0<br>HTIF | <ul> <li>High Temperature Interrupt Flag — HTIF — High Temperature Interrupt Flag</li> <li>HTIF is set to 1 when HTDS status bit changes. This flag can only be cleared by writing a 1.</li> <li>Writing a 0 has no effect. If enabled (HTIE=1), HTIF causes an interrupt request.</li> <li>0 No change in HTDS bit.</li> <li>1 HTDS bit has changed.</li> </ul>                                                                                  |

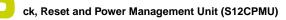

#### Figure 7-19. Waveform selected on API\_EXTCLK pin (APIEA=1, APIFE=1)

Freescale's Scalable Controller Area Network (S12MSCANV3)

| Register<br>Name |        | Bit 7 | 6   | 5   | 4   | 3    | 2    | 1    | Bit0 |

|------------------|--------|-------|-----|-----|-----|------|------|------|------|

| 0x00X4<br>DSR0   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X5<br>DSR1   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X6<br>DSR2   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X7<br>DSR3   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X8<br>DSR4   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X9<br>DSR5   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00XA<br>DSR6   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00XB<br>DSR7   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| DLR              | R<br>W |       |     |     |     | DLC3 | DLC2 | DLC1 | DLC0 |

#### Figure 8-24. Receive/Transmit Message Buffer — Extended Identifier Mapping (continued)

= Unused, always read 'x'

#### Read:

- For transmit buffers, anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

- For receive buffers, only when RXF flag is set (see Section 8.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)").

Write:

- a) the 14 most significant bits of the extended identifier plus the SRR and IDE bits of CAN 2.0B messages or

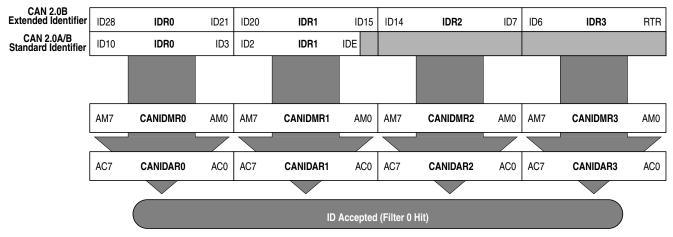

- b) the 11 bits of the standard identifier, the RTR and IDE bits of CAN 2.0A/B messages. Figure 8-41 shows how the first 32-bit filter bank (CANIDAR0–CANIDA3, CANIDMR0–3CANIDMR) produces filter 0 and 1 hits. Similarly, the second filter bank (CANIDAR4–CANIDAR7, CANIDMR4–CANIDMR7) produces filter 2 and 3 hits.

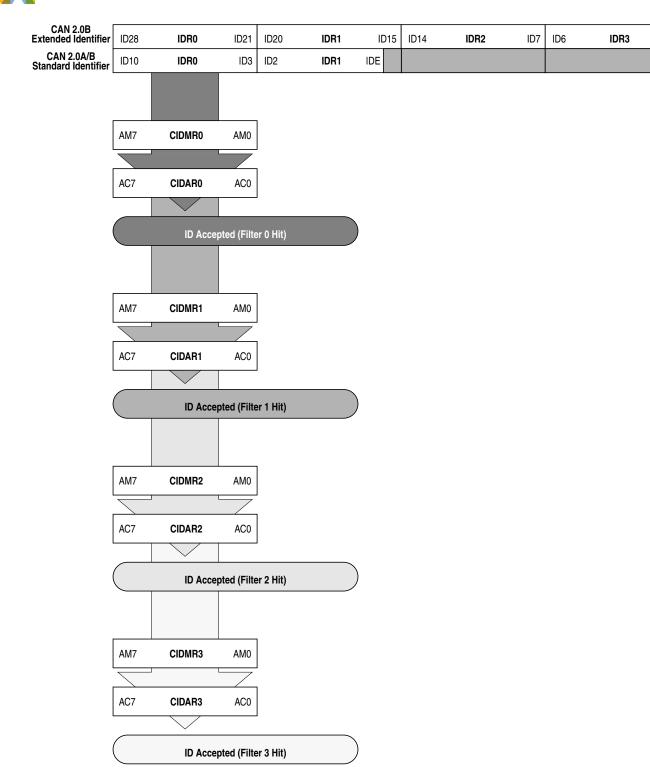

- Eight identifier acceptance filters, each to be applied to the first 8 bits of the identifier. This mode implements eight independent filters for the first 8 bits of a CAN 2.0A/B compliant standard identifier or a CAN 2.0B compliant extended identifier. Figure 8-42 shows how the first 32-bit filter bank (CANIDAR0–CANIDAR3, CANIDMR0–CANIDMR3) produces filter 0 to 3 hits. Similarly, the second filter bank (CANIDAR4–CANIDAR7, CANIDMR4–CANIDMR7) produces filter 4 to 7 hits.

- Closed filter. No CAN message is copied into the foreground buffer RxFG, and the RXF flag is never set.

Figure 8-40. 32-bit Maskable Identifier Acceptance Filter

Ile's Scalable Controller Area Network (S12MSCANV3)

RTR

## 9.4.1 Analog Sub-Block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies  $V_{DDA}$  and  $V_{SSA}$  allow to isolate noise of other MCU circuitry from the analog sub-block.

### 9.4.1.1 Sample and Hold Machine

The Sample and Hold (S/H) Machine accepts analog signals from the external world and stores them as capacitor charge on a storage node.

During the sample process the analog input connects directly to the storage node.

The input analog signals are unipolar and must fall within the potential range of  $V_{SSA}$  to  $V_{DDA}$ .

During the hold process the analog input is disconnected from the storage node.

#### 9.4.1.2 Analog Input Multiplexer

The analog input multiplexer connects one of the 10 external analog input channels to the sample and hold machine.

### 9.4.1.3 Analog-to-Digital (A/D) Machine

The A/D Machine performs analog to digital conversions. The resolution is program selectable at either 8 or 10 or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the stored analog sample potential with a series of digitally generated analog potentials. By following a binary search algorithm, the A/D machine locates the approximating potential that is nearest to the sampled potential.

When not converting the A/D machine is automatically powered down.

Only analog input signals within the potential range of  $V_{RL}$  to  $V_{RH}$  (A/D reference potentials) will result in a non-railed digital output code.

## 9.4.2 Digital Sub-Block

This subsection explains some of the digital features in more detail. See Section 9.3.2, "Register Descriptions" for all details.

#### 9.4.2.1 External Trigger Input

The external trigger feature allows the user to synchronize ATD conversions to the external environment events rather than relying on software to signal the ATD module when ATD conversions are to take place. The external trigger signal (out of reset ATD channel 9, configurable in ATDCTL1) is programmable to

#### Pulse-Width Modulator (PWM8B6CV1) Block Description

|        | ase + 0x001D |   |   |   |   |   |   |       |

|--------|--------------|---|---|---|---|---|---|-------|

|        | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

| R<br>W | Bit 7        | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

Figure 10-32. PWM Channel Duty Registers (PWMDTY5)

Read: anytime

Write: anytime

#### 10.3.2.15 PWM Shutdown Register (PWMSDN)

The PWMSDN register provides for the shutdown functionality of the PWM module in the emergency cases.

Module Base + 0x00E ~~~~~~~~~~

|       | 7                           | 6 | 5        | 4      | 3 | 2      | 1        | 0       |

|-------|-----------------------------|---|----------|--------|---|--------|----------|---------|

| R     | PWMIF                       |   |          | PWMLVL | 0 | PWM5IN | PWM5INL  | PWM5ENA |

| W     |                             |   | PWMRSTRT |        |   |        | FVINDINL |         |

| Reset | 0                           | 0 | 0        | 0      | 0 | 0      | 0        | 0       |

|       | = Unimplemented or Reserved |   |          |        |   |        |          |         |

Figure 10-33. PWM Shutdown Register (PWMSDN)

Read: anytime

Write: anytime

#### Table 10-10. PWMSDN Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PWMIF    | <ul> <li>PWM Interrupt Flag — Any change from passive to asserted (active) state or from active to passive state will be flagged by setting the PWMIF flag = 1. The flag is cleared by writing a logic 1 to it. Writing a 0 has no effect.</li> <li>0 No change on PWM5IN input.</li> <li>1 Change on PWM5IN input</li> </ul> |

| 6<br>PWMIE    | <ul> <li>PWM Interrupt Enable — If interrupt is enabled an interrupt to the CPU is asserted.</li> <li>0 PWM interrupt is disabled.</li> <li>1 PWM interrupt is enabled.</li> </ul>                                                                                                                                            |

| 5<br>PWMRSTRT | <b>PWM Restart</b> — The PWM can only be restarted if the PWM channel input 5 is deasserted. After writing a logic 1 to the PWMRSTRT bit (trigger event) the PWM channels start running after the corresponding counter passes next "counter = 0" phase.                                                                      |

|               | Also, if the PWM5ENA bit is reset to 0, the PWM do not start before the counter passes 0x0000.                                                                                                                                                                                                                                |

|               | The bit is always read as 0.                                                                                                                                                                                                                                                                                                  |

| 4<br>PWMLVL   | <ul> <li>PWM Shutdown Output Level — If active level as defined by the PWM5IN input, gets asserted all enabled PWM channels are immediately driven to the level defined by PWMLVL.</li> <li>0 PWM outputs are forced to 0</li> <li>1 PWM outputs are forced to 1.</li> </ul>                                                  |

#### NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

## 11.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

Figure 11-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

#### NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

# 11.5 Initialization/Application Information

### 11.5.1 Reset Initialization

See Section 11.3.2, "Register Descriptions".

## 11.5.2 Modes of Operation

#### 11.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 11.4.5.2, "Character Transmission".

### 11.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

new byte can be written to the SCIDRH/L for transmission.Clear TDRE by reading SCI status register 1 with TDRE set and then writing to SCI data register low (SCIDRL).

#### 11.5.3.1.2 TC Description

The TC interrupt is set by the SCI when a transmission has been completed. Transmission is completed when all bits including the stop bit (if transmitted) have been shifted out and no data is queued to be transmitted. No stop bit is transmitted when sending a break character and the TC flag is set (providing there is no more data queued for transmission) when the break character has been shifted out. A TC interrupt indicates that there is no transmission in progress. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL).TC is cleared automatically when data, preamble, or break is queued and ready to be sent.

#### 11.5.3.1.3 RDRF Description

The RDRF interrupt is set when the data in the receive shift register transfers to the SCI data register. A RDRF interrupt indicates that the received data has been transferred to the SCI data register and that the byte can now be read by the MCU. The RDRF interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

#### 11.5.3.1.4 OR Description

The OR interrupt is set when software fails to read the SCI data register before the receive shift register receives the next frame. The newly acquired data in the shift register will be lost in this case, but the data already in the SCI data registers is not affected. The OR interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

#### 11.5.3.1.5 IDLE Description

The IDLE interrupt is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1) appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).

#### 11.5.3.1.6 RXEDGIF Description

The RXEDGIF interrupt is set when an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD pin is detected. Clear RXEDGIF by writing a "1" to the SCIASR1 SCI alternative status register 1.

#### 11.5.3.1.7 BERRIF Description

The BERRIF interrupt is set when a mismatch between the transmitted and the received data in a single wire application like LIN was detected. Clear BERRIF by writing a "1" to the SCIASR1 SCI alternative status register 1. This flag is also cleared if the bit error detect feature is disabled.

### 11.5.3.1.8 BKDIF Description

The BKDIF interrupt is set when a break signal was received. Clear BKDIF by writing a "1" to the SCIASR1 SCI alternative status register 1. This flag is also cleared if break detect feature is disabled.

## 11.5.4 Recovery from Wait Mode

The SCI interrupt request can be used to bring the CPU out of wait mode.

# 11.5.5 Recovery from Stop Mode

An active edge on the receive input can be used to bring the CPU out of stop mode.

## 13.3 Memory Map and Registers

This section describes the memory map and registers for the Flash module. Read data from unimplemented memory space in the Flash module is undefined. Write access to unimplemented or reserved memory space in the Flash module will be ignored by the Flash module.

## 13.3.1 Module Memory Map

The S12 architecture places the P-Flash memory between global addresses  $0x2_0000$  and  $0x3_FFFF$  as shown in Table 13-2. The P-Flash memory map is shown in Figure 13-2.

| Global Address      | Size<br>(Bytes) | Description                                                             |

|---------------------|-----------------|-------------------------------------------------------------------------|

| 0x2_0000 – 0x3_FFFF | 128 K           | P-Flash Block<br>Contains Flash Configuration Field<br>(see Table 13-3) |

#### Table 13-2. P-Flash Memory Addressing

The FPROT register, described in Section 13.3.2.9, can be set to protect regions in the Flash memory from accidental program or erase. Three separate memory regions, one growing upward from global address 0x3\_8000 in the Flash memory (called the lower region), one growing downward from global address 0x3\_FFFF in the Flash memory (called the higher region), and the remaining addresses in the Flash memory, can be activated for protection. The Flash memory addresses covered by these protectable regions are shown in the P-Flash memory map. The higher address region is mainly targeted to hold the boot loader code since it covers the vector space. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field as described in Table 13-3.

Table 13-3. Flash Configuration Field

| Global Address                   | Size<br>(Bytes) | Description                                                                                                                                                        |

|----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x3_FF00-0x3_FF07                | 8               | Backdoor Comparison Key<br>Refer to Section 13.4.5.11, "Verify Backdoor Access Key Command," and<br>Section 13.5.1, "Unsecuring the MCU using Backdoor Key Access" |

| 0x3_FF08-0x3_FF0B <sup>(1)</sup> | 4               | Reserved                                                                                                                                                           |

| 0x3_FF0C <sup>1</sup>            | 1               | P-Flash Protection byte.<br>Refer to Section 13.3.2.9, "P-Flash Protection Register (FPROT)"                                                                       |

| 0x3_FF0D <sup>1</sup>            | 1               | D-Flash Protection byte.<br>Refer to Section 13.3.2.10, "D-Flash Protection Register (DFPROT)"                                                                     |

| 0x3_FF0E <sup>1</sup>            | 1               | Flash Nonvolatile byte<br>Refer to Section 13.3.2.16, "Flash Option Register (FOPT)"                                                                               |

| 0x3_FF0F <sup>1</sup>            | 1               | Flash Security byte<br>Refer to Section 13.3.2.2, "Flash Security Register (FSEC)"                                                                                 |

1. 0x3FF08-0x3\_FF0F form a Flash phrase and must be programmed in a single command write sequence. Each byte in the 0x3\_FF08 - 0x3\_FF0B reserved field should be programmed to 0xFF.

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 13-27)                      |  |  |  |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or D-Flash memory is protected                       |  |  |  |  |

| MGSTAT1  | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |

Table 13-50. Unsecure Flash Command Error Handling

#### 13.4.5.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 13-9). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 13-3). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0C             | Not required |

| 001         | Key 0            |              |

| 010         | Key 1            |              |

| 011         | Key 2            |              |

| 100         | Key 3            |              |

Table 13-51. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

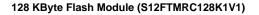

#### 14.1.3 Block Diagrams

Figure 14-1. TIM16B8CV2 Block Diagram

odule (TIM16B8CV2) Block Description

# 14.6.4 Timer Overflow Interrupt (TOF)

This active high output will be asserted by the module to request a timer overflow interrupt to be serviced by the system controller.

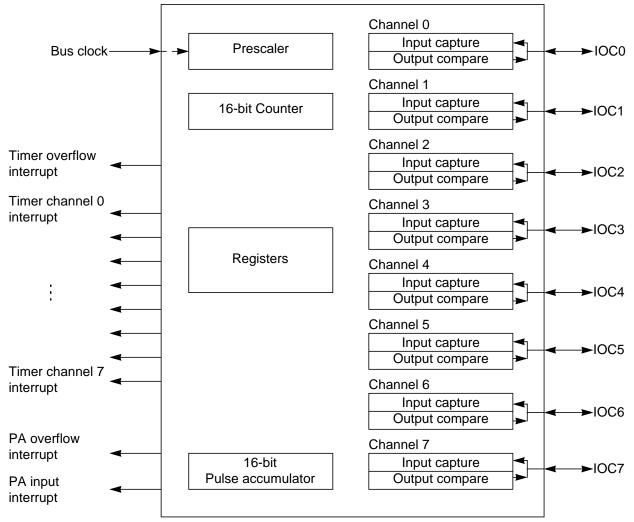

#### **Package Information**

S12P-Family Reference Manual, Rev. 1.13