#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                 |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 32MHz                                                                 |

| Connectivity               | CANbus, SCI, SPI                                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 49                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p64j0clh |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Device Overview MC9S12P-Family**

# NP

## 1.12 COP Configuration

The COP time-out rate bits CR[2:0] and the WCOP bit in the CPMUCOP register at address 0x003C are loaded from the Flash register FOPT. See Table 1-13 and Table 1-14 for coding. The FOPT register is loaded from the Flash configuration field byte at global address 0x3\_FF0E during the reset sequence.

| NV[2:0] in<br>FOPT Register | CR[2:0] in<br>COPCTL Register |  |  |  |

|-----------------------------|-------------------------------|--|--|--|

| 000                         | 111                           |  |  |  |

| 001                         | 110                           |  |  |  |

| 010                         | 101                           |  |  |  |

| 011                         | 100                           |  |  |  |

| 100                         | 011                           |  |  |  |

| 101                         | 010                           |  |  |  |

| 110                         | 001                           |  |  |  |

| 111                         | 000                           |  |  |  |

### Table 1-14. Initial WCOP Configuration

| NV[3] in<br>FOPT Register | WCOP in<br>COPCTL Register |  |  |  |

|---------------------------|----------------------------|--|--|--|

| 1                         | 0                          |  |  |  |

| 0                         | 1                          |  |  |  |

## 1.13 ATD External Trigger Input Connection

The ATD module includes external trigger inputs ETRIG0 and ETRIG1. The external trigger allows the user to synchronize ATD conversion to external trigger events. Table 1-15 shows the connection of the external trigger inputs.

| External Trigger<br>Input | Connectivity  |

|---------------------------|---------------|

| ETRIG0                    | PWM channel 1 |

| ETRIG1                    | PWM channel 3 |

Consult the ATD section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

### Memory Map Control (S12PMMCV1)

CALL/RTC instructions should only be used when needed. The JSR and RTS instructions can be used to access subroutines that are already present in the local CPU memory map (i.e. in the same page in the program memory page window for example). However calling a function located in a different page requires usage of the CALL instruction. The function must be terminated by the RTC instruction. Because the RTC instruction restores contents of the PPAGE register from the stack, functions terminated with the RTC instruction must be called using the CALL instruction even when the correct page is already present in the memory map. This is to make sure that the correct PPAGE value will be present on stack at the time of the RTC instruction execution.

## Chapter 5 Background Debug Module (S12SBDMV1) Revision History

| Revision Number   | Date                                                              |             | Summary of Changes                      |  |

|-------------------|-------------------------------------------------------------------|-------------|-----------------------------------------|--|

| s12s_bdm.01.00.00 | 08.Feb.2006                                                       | General     | First version of S12SBDMV1              |  |

| s12s_bdm.01.00.02 | 02 09.Feb.2006 General Updated register address information & Blo |             |                                         |  |

| s12s_bdm.01.00.12 | 10.May.2006                                                       | 5.3.2/5-134 | Removed CLKSW bit and description       |  |

| s12s_bdm.01.01.01 | 20.Sep.2007                                                       | General     | Added conditional text for S12P family  |  |

| 1.02              | 1.02 08.Apr.2009 General                                          |             | Minor text corrections following review |  |

| 1.03              | 14.May.2009                                                       |             | Internal Conditional text only          |  |

| 1.04              | 30.Nov.2009                                                       |             | Internal Conditional text only          |  |

## 5.1 Introduction

This section describes the functionality of the background debug module (BDM) sub-block of the HCS12S core platform.

The background debug module (BDM) sub-block is a single-wire, background debug system implemented in on-chip hardware for minimal CPU intervention. All interfacing with the BDM is done via the BKGD pin.

The BDM has enhanced capability for maintaining synchronization between the target and host while allowing more flexibility in clock rates. This includes a sync signal to determine the communication rate and a handshake signal to indicate when an operation is complete. The system is backwards compatible to the BDM of the S12 family with the following exceptions:

- TAGGO command not supported by S12SBDM

- External instruction tagging feature is part of the DBG module

- S12SBDM register map and register content modified

- Family ID readable from BDM ROM at global address 0x3\_FF0F in active BDM (value for devices with HCS12S core is 0xC2)

- Clock switch removed from BDM (CLKSW bit removed from BDMSTS register)

S12P-Family Reference Manual, Rev. 1.13

## 5.1.1 Features

The BDM includes these distinctive features:

- Single-wire communication with host development system

- Enhanced capability for allowing more flexibility in clock rates

- SYNC command to determine communication rate

- GO\_UNTIL command

- Hardware handshake protocol to increase the performance of the serial communication

- Active out of reset in special single chip mode

- Nine hardware commands using free cycles, if available, for minimal CPU intervention

- Hardware commands not requiring active BDM

- 14 firmware commands execute from the standard BDM firmware lookup table

- Software control of BDM operation during wait mode

- When secured, hardware commands are allowed to access the register space in special single chip mode, if the Flash erase tests fail.

- Family ID readable from BDM ROM at global address 0x3\_FF0F in active BDM (value for devices with HCS12S core is 0xC2)

- BDM hardware commands are operational until system stop mode is entered

## 5.1.2 Modes of Operation

BDM is available in all operating modes but must be enabled before firmware commands are executed. Some systems may have a control bit that allows suspending the function during background debug mode.

## 5.1.2.1 Regular Run Modes

All of these operations refer to the part in run mode and not being secured. The BDM does not provide controls to conserve power during run mode.

Normal modes

General operation of the BDM is available and operates the same in all normal modes.

• Special single chip mode

In special single chip mode, background operation is enabled and active out of reset. This allows programming a system with blank memory.

## 5.1.2.2 Secure Mode Operation

If the device is in secure mode, the operation of the BDM is reduced to a small subset of its regular run mode operation. Secure operation prevents access to Flash other than allowing erasure. For more information please see Section 5.4.1, "Security".

## 5.1.2.3 Low-Power Modes

The BDM can be used until stop mode is entered. When CPU is in wait mode all BDM firmware commands as well as the hardware BACKGROUND command cannot be used and are ignored. In this case the CPU can not enter BDM active mode, and only hardware read and write commands are available. Also the CPU can not enter a low power mode (stop or wait) during BDM active mode.

In stop mode the BDM clocks are stopped. When BDM clocks are disabled and stop mode is exited, the BDM clocks will restart and BDM will have a soft reset (clearing the instruction register, any command in progress and disable the ACK function). The BDM is now ready to receive a new command.

## 5.1.3 Block Diagram

Host Serial Data System BKGD 16-Bit Shift Register Interface Control Register Block Address **Bus Interface** Data TRACE and Instruction Code Control Logic Control and BDMAC<sup>-</sup> Execution Clocks **ENBDM** Standard BDM Firmware LOOKUP TABLE SDV Secured BDM Firmware LOOKUP TABLE UNSEC **BDMSTS** Register

A block diagram of the BDM is shown in Figure 5-1.

## 5.2 External Signal Description

A single-wire interface pin called the background debug interface (BKGD) pin is used to communicate with the BDM system. During reset, this pin is a mode select input which selects between normal and special modes of operation. After reset, this pin becomes the dedicated serial interface pin for the background debug mode. The communication rate of this pin is based on the settings for the VCO clock (CPMUSYNR). The BDM clock frequency is always VCO clock frequency divided by 8. After reset the BDM clock is based on the reset values of the CPMUSYNR register (4 MHz). When modifying the VCO

enabled just for the READ\_BD and WRITE\_BD access cycle. This allows the BDM to access BDM locations unobtrusively, even if the addresses conflict with the application memory map.

| Table 5-4. Hardware Commands |

|------------------------------|

|------------------------------|

| Command       | Opcode<br>(hex) | Data                              | Description                                                                                                                          |  |  |

|---------------|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BACKGROUND    | 90              | None                              | Enter background mode if BDM is enabled. If enabled, an ACK will be issued when the part enters active background mode.              |  |  |

| ACK_ENABLE    | D5              | None                              | Enable Handshake. Issues an ACK pulse after the command is executed.                                                                 |  |  |

| ACK_DISABLE   | D6              | None                              | Disable Handshake. This command does not issue an ACK pulse.                                                                         |  |  |

| READ_BD_BYTE  | E4              | 16-bit address<br>16-bit data out | ······································                                                                                               |  |  |

| READ_BD_WORD  | EC              | 16-bit address<br>16-bit data out |                                                                                                                                      |  |  |

| READ_BYTE     | E0              | 16-bit address<br>16-bit data out |                                                                                                                                      |  |  |

| READ_WORD     | E8              | 16-bit address<br>16-bit data out | ······································                                                                                               |  |  |

| WRITE_BD_BYTE | C4              | 16-bit address<br>16-bit data in  | Write to memory with standard BDM firmware lookup table in map.<br>Odd address data on low byte; even address data on high byte.     |  |  |

| WRITE_BD_WORD | СС              | 16-bit address<br>16-bit data in  | Write to memory with standard BDM firmware lookup table in map.<br>Must be aligned access.                                           |  |  |

| WRITE_BYTE    | C0              | 16-bit address<br>16-bit data in  | Write to memory with standard BDM firmware lookup table out of map.<br>Odd address data on low byte; even address data on high byte. |  |  |

| WRITE_WORD    | C8              | 16-bit address<br>16-bit data in  | Write to memory with standard BDM firmware lookup table out of map.<br>Must be aligned access.                                       |  |  |

NOTE:

If enabled, ACK will occur when data is ready for transmission for all BDM READ commands and will occur after the write is complete for all BDM WRITE commands.

## 5.4.4 Standard BDM Firmware Commands

BDM firmware commands are used to access and manipulate CPU resources. The system must be in active BDM to execute standard BDM firmware commands, see Section 5.4.2, "Enabling and Activating BDM". Normal instruction execution is suspended while the CPU executes the firmware located in the standard BDM firmware lookup table. The hardware command BACKGROUND is the usual way to activate BDM.

As the system enters active BDM, the standard BDM firmware lookup table and BDM registers become visible in the on-chip memory map at 0x3\_FF00–0x3\_FFFF, and the CPU begins executing the standard BDM firmware. The standard BDM firmware watches for serial commands and executes them as they are received.

The firmware commands are shown in Table 5-5.

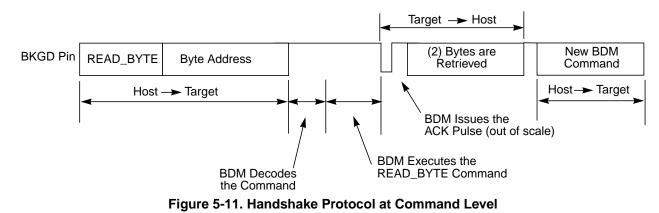

Figure 5-11 shows the ACK handshake protocol in a command level timing diagram. The READ\_BYTE instruction is used as an example. First, the 8-bit instruction opcode is sent by the host, followed by the address of the memory location to be read. The target BDM decodes the instruction. A bus cycle is grabbed (free or stolen) by the BDM and it executes the READ\_BYTE operation. Having retrieved the data, the BDM issues an ACK pulse to the host controller, indicating that the addressed byte is ready to be retrieved. After detecting the ACK pulse, the host initiates the byte retrieval process. Note that data is sent in the form of a word and the host needs to determine which is the appropriate byte based on whether the address was odd or even.

Differently from the normal bit transfer (where the host initiates the transmission), the serial interface ACK handshake pulse is initiated by the target MCU by issuing a negative edge in the BKGD pin. The hardware handshake protocol in Figure 5-10 specifies the timing when the BKGD pin is being driven, so the host

should follow this timing constraint in order to avoid the risk of an electrical conflict in the BKGD pin.

## NOTE

The only place the BKGD pin can have an electrical conflict is when one side is driving low and the other side is issuing a speedup pulse (high). Other "highs" are pulled rather than driven. However, at low rates the time of the speedup pulse can become lengthy and so the potential conflict time becomes longer as well.

The ACK handshake protocol does not support nested ACK pulses. If a BDM command is not acknowledge by an ACK pulse, the host needs to abort the pending command first in order to be able to issue a new BDM command. When the CPU enters wait or stop while the host issues a hardware command (e.g., WRITE\_BYTE), the target discards the incoming command due to the wait or stop being detected. Therefore, the command is not acknowledged by the target, which means that the ACK pulse will not be issued in this case. After a certain time the host (not aware of stop or wait) should decide to abort any possible pending ACK pulse in order to be sure a new command can be issued. Therefore, the protocol provides a mechanism in which a command, and its corresponding ACK, can be aborted.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ARM     | <ul> <li>Arm Bit — The ARM bit controls whether the DBG module is armed. This bit can be set and cleared by user software and is automatically cleared on completion of a debug session, or if a breakpoint is generated with tracing not enabled. On setting this bit the state sequencer enters State1.</li> <li>0 Debugger disarmed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>TRIG    | Immediate Trigger Request Bit — This bit when written to 1 requests an immediate trigger independent of state sequencer status. When tracing is complete a forced breakpoint may be generated depending upon DBGBRK and BDM bit settings. This bit always reads back a 0. Writing a 0 to this bit has no effect. If the DBGTCR_TSOURCE bit is clear no tracing is carried out. If tracing has already commenced using BEGIN trigger alignment, it continues until the end of the tracing session as defined by the TALIGN bit, thus TRIG has no affect. In secure mode tracing is disabled and writing to this bit cannot initiate a tracing session. The session is ended by setting TRIG and ARM simultaneously. 0 Do not trigger until the state sequencer enters the Final State. 1 Trigger immediately |

| 4<br>BDM     | <ul> <li>Background Debug Mode Enable — This bit determines if a breakpoint causes the system to enter Background Debug Mode (BDM) or initiate a Software Interrupt (SWI). If this bit is set but the BDM is not enabled by the ENBDM bit in the BDM module, then breakpoints default to SWI.</li> <li>0 Breakpoint to Software Interrupt if BDM inactive. Otherwise no breakpoint.</li> <li>1 Breakpoint to BDM, if BDM enabled. Otherwise breakpoint to SWI</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| 3<br>DBGBRK  | <ul> <li>S12SDBG Breakpoint Enable Bit — The DBGBRK bit controls whether the debugger will request a breakpoint on reaching the state sequencer Final State. If tracing is enabled, the breakpoint is generated on completion of the tracing session. If tracing is not enabled, the breakpoint is generated immediately.</li> <li>0 No Breakpoint generated</li> <li>1 Breakpoint generated</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1–0<br>COMRV | <b>Comparator Register Visibility Bits</b> — These bits determine which bank of comparator register is visible in the 8-byte window of the S12SDBG module address map, located between 0x0028 to 0x002F. Furthermore these bits determine which register is visible at the address 0x0027. See Table 6-4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Table 6-3. DBGC1 Field Descriptions

### Table 6-4. COMRV Encoding

| COMRV | Visible Comparator | Visible Register at 0x0027 |  |  |

|-------|--------------------|----------------------------|--|--|

| 00    | Comparator A       | DBGSCR1                    |  |  |

| 01    | Comparator B       | DBGSCR2                    |  |  |

| 10    | Comparator C       | DBGSCR3                    |  |  |

| 11    | None               | DBGMFR                     |  |  |

## 6.3.2.2 Debug Status Register (DBGSR)

Address: 0x0021

|       | 7                           | 6 | 5 | 4 | 3 | 2    | 1    | 0    |  |

|-------|-----------------------------|---|---|---|---|------|------|------|--|

| R     | TBF                         | 0 | 0 | 0 | 0 | SSF2 | SSF1 | SSF0 |  |

| W     |                             |   |   |   |   |      |      |      |  |

| Reset |                             | 0 | 0 | 0 | 0 | 0    | 0    | 0    |  |

| POR   | 0                           | 0 | 0 | 0 | 0 | 0    | 0    | 0    |  |

|       | = Unimplemented or Reserved |   |   |   |   |      |      |      |  |

### Figure 6-4. Debug Status Register (DBGSR)

S12P-Family Reference Manual, Rev. 1.13

| TCTRIM[3:0] | IRC1M indicative relative TC variation | IRC1M indicative frequency drift for relative TC variation |  |  |  |  |

|-------------|----------------------------------------|------------------------------------------------------------|--|--|--|--|

| 0000        | 0 (nominal TC of the IRC1M)            | 0%                                                         |  |  |  |  |

| 0001        | -0.54%                                 | -0.8%                                                      |  |  |  |  |

| 0010        | -1.08%                                 | -1.6%                                                      |  |  |  |  |

| 0011        | -1.63%                                 | -2.4%                                                      |  |  |  |  |

| 0100        | -2.20%                                 | -3.2%                                                      |  |  |  |  |

| 0101        | -2.77%                                 | -4.0%                                                      |  |  |  |  |

| 0110        | -3.33%                                 | -4.8%                                                      |  |  |  |  |

| 0111        | -3.91%                                 | -5.5%                                                      |  |  |  |  |

| 1000        | 0 (nominal TC of the IRC1M)            | 0%                                                         |  |  |  |  |

| 1001        | +0.54%                                 | +0.8%                                                      |  |  |  |  |

| 1010        | +1.07%                                 | +1.6%                                                      |  |  |  |  |

| 1011        | +1.59%                                 | +2.4%                                                      |  |  |  |  |

| 1100        | +2.11%                                 | +3.2%                                                      |  |  |  |  |

| 1101        | +2.62%                                 | +4.0%                                                      |  |  |  |  |

| 1110        | +3.12%                                 | +4.8%                                                      |  |  |  |  |

| 1111        | +3.62%                                 | +5.5%                                                      |  |  |  |  |

Table 7-21. TC trimming of the IRC1M frequency at ambient temperature

### NOTE

Since the IRC1M frequency is not a linear function of the temperature, but more like a parabola, the above relative TC variation is only an indication and should be considered with care.

Be aware that the output frequency vary with TC trimming, A frequency trimming correction is therefore necessary. The values provided in Table 7-21 are typical values at ambient temperature which can vary from device to device.

The use of the filter function is only possible if the VCOCLK-to-OSCCLK ratio divided by two (( $f_{VCO} / f_{OSC}$ )/2) is an integer number. This integer value must be written to the OSCFILT[4:0] bits.

If enabled, the oscillator filter is sampling the incoming oscillator clock signal (EXTAL) with the VCOCLK frequency.

Using VCOCLK, a time window is defined during which an edge of the OSCCLK is expected. In case of OSCBW = 1 the width of this window is three VCOCLK cycles, if the OSCBW = 0 it is one VCOCLK cycle.

The noise detection is active for certain combinations of OSCFILT[4:0] and OSCBW bit settings as shown in Table 7-24

| OSCFILT[4:0] | OSCBW | Detection | Filter   |

|--------------|-------|-----------|----------|

| 0            | х     | disabled  | disabled |

| 1            | х     | disabled  | active   |

| 2 or 3       | 0     | active    | active   |

|              | 1     | disabled  | active   |

| >=4          | х     | active    | active   |

### Table 7-24. Noise Detection Settings

## NOTE

If the VCOCLK frequency is higher than 25 MHz the wide bandwidth must be selected (OSCBW = 1).

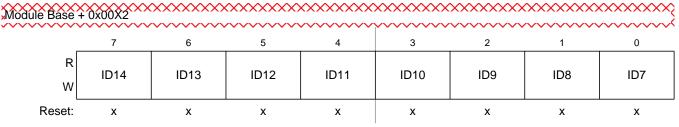

## 8.3.3.1.1 IDR0–IDR3 for Extended Identifier Mapping

| Module Base + 0x00X0 |      |      |      |      |      |      |      |      |  |

|----------------------|------|------|------|------|------|------|------|------|--|

|                      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

| R<br>W               | ID28 | ID27 | ID26 | ID25 | ID24 | ID23 | ID22 | ID21 |  |

| Reset:               | x    | x    | x    | x    | х    | x    | x    | x    |  |

Figure 8-26. Identifier Register 0 (IDR0) — Extended Identifier Mapping

| Field            | Description                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>ID[28:21] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

####

| _      | 7    | 6    | 5    | 4        | 3        | 2    | 1    | 0    |

|--------|------|------|------|----------|----------|------|------|------|

| R<br>W | ID20 | ID19 | ID18 | SRR (=1) | IDE (=1) | ID17 | ID16 | ID15 |

| Reset: | х    | x    | x    | х        | х        | x    | x    | х    |

Figure 8-27. Identifier Register 1 (IDR1) — Extended Identifier Mapping

### Table 8-28. IDR1 Register Field Descriptions — Extended

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7-5<br>ID[20:18] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an dentifier is defined to be highest for the smallest binary number.                                                                                                                                          |  |  |  |  |  |  |  |

| 4<br>SRR         | <b>Substitute Remote Request</b> — This fixed recessive bit is used only in extended format. It must be set to 1 by the user for transmission buffers and is stored as received on the CAN bus for receive buffers.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 3<br>IDE         | <ul> <li>ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.</li> <li>0 Standard format (11 bit)</li> <li>1 Extended format (29 bit)</li> </ul> |  |  |  |  |  |  |  |

| 2-0<br>ID[17:15] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                                         |  |  |  |  |  |  |  |

Figure 8-28. Identifier Register 2 (IDR2) — Extended Identifier Mapping

| Field    | Description                                                                                                       |   |

|----------|-------------------------------------------------------------------------------------------------------------------|---|

| 7-0      | Extended Format Identifier — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the   | 1 |

| ID[14:7] | most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an |   |

|          | identifier is defined to be highest for the smallest binary number.                                               |   |

## Module Base + 0x00X3

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | RTR |

| Reset: | х   | х   | х   | х   | х   | х   | х   | х   |

### Figure 8-29. Identifier Register 3 (IDR3) — Extended Identifier Mapping

### Table 8-30. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                      |

| 0<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul> |

| Register<br>Name               |        | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

|--------------------------------|--------|-------|------------|----------------|-------|-------|-------|-------|-------|

| 0x0000<br>PWME                 | R<br>W | 0     | 0          | PWME5          | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |

| 0x0001<br>PWMPOL               | R<br>W | 0     | 0          | PPOL5          | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |

| 0x0002<br>PWMCLK               | R<br>W | 0     | 0          | PCLK5          | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |

| 0x0003<br>PWMPRCLK             | R<br>W | 0     | PCKB2      | PCKB1          | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |

| 0x0004<br>PWMCAE               | R<br>W | 0     | 0          | CAE5           | CAE4  | CAE2  | CAE2  | CAE1  | CAE0  |

| 0x0005<br>PWMCTL               | R<br>W | 0     | CON45      | CON23          | CON01 | PSWAI | PFRZ  | 0     | 0     |

| 0x0006<br>PWMTST               | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x0007<br>PWMPRSC              | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <mark>0x0008</mark><br>PWMSCLA | R<br>W | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0009<br>PWMSCLB              | R<br>W | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| 0x000A<br>PWMSCNTA             | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x000B<br>PWMSCNTB             | R<br>W | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000C</u>                  | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT0                        | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000D</u>                  | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT1                        | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| 0x000E                         | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT2                        | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

| <u>0x000F</u>                  | R      | Bit 7 | 6          | 5              | 4     | 3     | 2     | 1     | Bit 0 |

| PWMCNT3                        | W      | 0     | 0          | 0              | 0     | 0     | 0     | 0     | 0     |

|                                | [      |       | = Unimpler | nented or Rese | erved |       |       |       |       |

Figure 10-2. PWM Register Summary

### Table 10-3. PWMPOL Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PPOL3 | Pulse Width Channel 3 Polarity0PWM channel 3 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 3 output is high at the beginning of the period, then goes low when the duty count is reached. |

| 2<br>PPOL2 | Pulse Width Channel 2 Polarity0PWM channel 2 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 2 output is high at the beginning of the period, then goes low when the duty count is reached. |

| 1<br>PPOL1 | Pulse Width Channel 1 Polarity0PWM channel 1 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 1 output is high at the beginning of the period, then goes low when the duty count is reached. |

| 0<br>PPOL0 | Pulse Width Channel 0 Polarity0PWM channel 0 output is low at the beginning of the period, then goes high when the duty count is reached1PWM channel 0 output is high at the beginning of the period, then goes low when the duty count is reached.  |

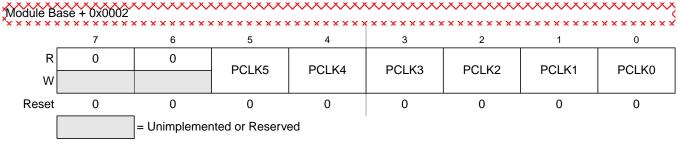

## 10.3.2.3 PWM Clock Select Register (PWMCLK)

Each PWM channel has a choice of two clocks to use as the clock source for that channel as described below.

### Figure 10-5. PWM Clock Select Register (PWMCLK)

Read: anytime

### Write: anytime

### NOTE

Register bits PCLK0 to PCLK5 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

### /idth Modulator (PWM8B6CV1) Block Description

due to the synchronization of PWMEx and the clock source. An exception to this is when channels are concatenated. Refer to Section 10.4.2.7, "PWM 16-Bit Functions," for more detail.

### NOTE

The first PWM cycle after enabling the channel can be irregular.

On the front end of the PWM timer, the clock is enabled to the PWM circuit by the PWMEx bit being high. There is an edge-synchronizing circuit to guarantee that the clock will only be enabled or disabled at an edge. When the channel is disabled (PWMEx = 0), the counter for the channel does not count.

## 10.4.2.2 PWM Polarity

Each channel has a polarity bit to allow starting a waveform cycle with a high or low signal. This is shown on the block diagram as a mux select of either the Q output or the  $\overline{Q}$  output of the PWM output flip-flop. When one of the bits in the PWMPOL register is set, the associated PWM channel output is high at the beginning of the waveform, then goes low when the duty count is reached. Conversely, if the polarity bit is 0, the output starts low and then goes high when the duty count is reached.

## 10.4.2.3 PWM Period and Duty

Dedicated period and duty registers exist for each channel and are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to 0x0000)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period and duty registers will go directly to the latches as well as the buffer.

A change in duty or period can be forced into effect "immediately" by writing the new value to the duty and/or period registers and then writing to the counter. This forces the counter to reset and the new duty and/or period values to be latched. In addition, because the counter is readable it is possible to know where the count is with respect to the duty value and software can be used to make adjustments.

### NOTE

When forcing a new period or duty into effect immediately, an irregular PWM cycle can occur.

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time.

## 10.4.2.4 PWM Timer Counters

Each channel has a dedicated 8-bit up/down counter which runs at the rate of the selected clock source (reference Figure 10-34 for the available clock sources and rates). The counter compares to two registers, a duty register and a period register as shown in Figure 10-35. When the PWM counter matches the duty register the output flip-flop changes state causing the PWM waveform to also change state. A match

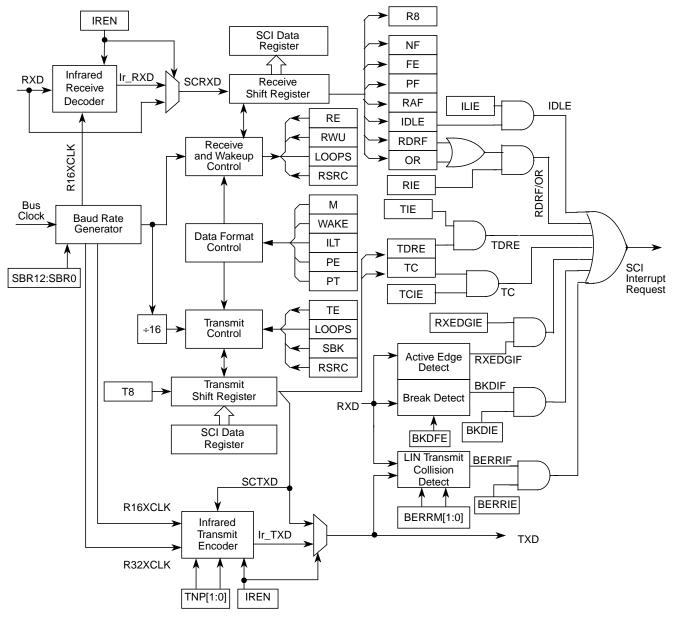

Figure 11-14. Detailed SCI Block Diagram

## 11.4.1 Infrared Interface Submodule

This module provides the capability of transmitting narrow pulses to an IR LED and receiving narrow pulses and transforming them to serial bits, which are sent to the SCI. The IrDA physical layer specification defines a half-duplex infrared communication link for exchange data. The full standard includes data rates up to 16 Mbits/s. This design covers only data rates between 2.4 Kbits/s and 115.2 Kbits/s.

The infrared submodule consists of two major blocks: the transmit encoder and the receive decoder. The SCI transmits serial bits of data which are encoded by the infrared submodule to transmit a narrow pulse

### Table 12-4. SPICR2 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>XFRW    | <b>Transfer Width</b> — This bit is used for selecting the data transfer width. If 8-bit transfer width is selected, SPIDRL becomes the dedicated data register and SPIDRH is unused. If 16-bit transfer width is selected, SPIDRH and SPIDRL form a 16-bit data register. Please refer to Section 12.3.2.4, "SPI Status Register (SPISR) for information about transmit/receive data handling and the interrupt flag clearing mechanism. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state. 0 8-bit Transfer Width (n = 8) <sup>(1)</sup> 1 16-bit Transfer Width (n = 16) <sup>1</sup> |

| 4<br>MODFEN  | <ul> <li>Mode Fault Enable Bit — This bit allows the MODF failure to be detected. If the SPI is in master mode and MODFEN is cleared, then the SS port pin is not used by the SPI. In slave mode, the SS is available only as an input regardless of the value of MODFEN. For an overview on the impact of the MODFEN bit on the SS port pin configuration, refer to Table 12-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 SS port pin is not used by the SPI.</li> <li>1 SS port pin with MODF feature.</li> </ul>                                                  |

| 3<br>BIDIROE | <ul> <li>Output Enable in the Bidirectional Mode of Operation — This bit controls the MOSI and MISO output buffer of the SPI, when in bidirectional mode of operation (SPC0 is set). In master mode, this bit controls the output buffer of the MOSI port, in slave mode it controls the output buffer of the MISO port. In master mode, with SPC0 set, a change of this bit will abort a transmission in progress and force the SPI into idle state.</li> <li>Output buffer disabled.</li> <li>Output buffer enabled.</li> </ul>                                                                                                                          |

| 1<br>SPISWAI | <ul> <li>SPI Stop in Wait Mode Bit — This bit is used for power conservation while in wait mode.</li> <li>SPI clock operates normally in wait mode.</li> <li>Stop SPI clock generation when in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0<br>SPC0    | Serial Pin Control Bit 0 — This bit enables bidirectional pin configurations as shown in Table 12-5. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### Table 12-5. Bidirectional Pin Configurations

| Pin Mode                 | SPC0 | BIDIROE   | MISO                 | MOSI                 |  |  |  |  |  |  |  |

|--------------------------|------|-----------|----------------------|----------------------|--|--|--|--|--|--|--|

| Master Mode of Operation |      |           |                      |                      |  |  |  |  |  |  |  |

| Normal                   | 0    | Master In | Master Out           |                      |  |  |  |  |  |  |  |

| Bidirectional            | 1    | 0         | MISO not used by SPI | Master In            |  |  |  |  |  |  |  |

|                          |      | 1         |                      | Master I/O           |  |  |  |  |  |  |  |

|                          |      | Sla       | ve Mode of Operation |                      |  |  |  |  |  |  |  |

| Normal 0                 |      | Х         | Slave Out            | Slave In             |  |  |  |  |  |  |  |

| Bidirectional 1 0        |      | 0         | Slave In             | MOSI not used by SPI |  |  |  |  |  |  |  |

|                          |      | 1         | Slave I/O            |                      |  |  |  |  |  |  |  |

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|--|

| 000         | 0x0A                                                                                                                     | Global address [17:16] to identify<br>P-Flash block to be erased |  |  |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 13.1.2.1 for the P-Flash sector size. |                                                                  |  |  |  |  |  |  |

Table 13-47. Erase P-Flash Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 13-27)                      |  |  |

|          | ACCERR    | Set if an invalid global address [17:16] is supplied                                |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 13-48. Erase P-Flash Sector Command Error Handling

## 13.4.5.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

Table 13-49. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |  |

|-------------|------------------|--------------|--|--|--|--|

| 000         | 0x0B             | Not required |  |  |  |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

Read: Anytime but will always return 0x0000 (1 state is transient)

### Write: Anytime

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FOC[7:0] | <ul> <li>Force Output Compare Action for Channel 7:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set.</li> <li>Note: A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. If forced output compare on any channel occurs at the same time as the successful output compare then forced output compare action will take precedence and interrupt flag won't get set.</li> </ul> |

## 14.3.2.3 Output Compare 7 Mask Register (OC7M)

## Module Base + 0x0002

| ~~~~~  | ~~~~~ |       | ~~~~~ | ~~~~~ | ~~~~~ | ~~~~~ | ~~~~~ |       |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 14-8. Output Compare 7 Mask Register (OC7M)

Read: Anytime

Write: Anytime

### Table 14-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

## 0x001A-0x001B Part ID Registers

| Address | Name    |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|---------|---|-------|-------|-------|-------|-------|-------|-------|-------|--|

| 0x001A  | PARTIDH |   | R     |       |       |       | PAR   | TIDH  | _     |       |  |

|         |         | W |       |       |       |       |       |       |       |       |  |

| 0x001B  | PARTIDL |   | R     |       |       |       | PAR   | TIDL  |       |       |  |

|         |         | W |       |       |       |       |       |       |       |       |  |

## 0x001C-0x001F Port Intergartion Module (PIM) Map 3 of 4

| Address | Name       |           | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

|---------|------------|-----------|-------|--------|-------|-------|-------|-------|-------|-------|---|

| 0x001C  | ECLKCTL    | R<br>W    | NECLK | NCLKX2 | DIV16 | EDIV4 | EDIV3 | EDIV2 | EDIV1 | EDIV0 |   |

| 0x001D  | Reserved   | Percented | R     | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

|         |            | W         |       |        |       |       |       |       |       |       |   |

| 0x001E  | IRQCR      | R         | IRQE  | IRQEN  | 0     | 0     | 0     | 0     | 0     | 0     |   |

| UXUUTE  | Ingon      | W         |       |        |       |       |       |       |       |       |   |

| 0x001F  | Percentred | R         | 0     | 0      | 0     | 0     | 0     | 0     | 0     | 0     |   |

| UXUUTF  | Reserved   | W         |       |        |       |       |       |       |       |       |   |

### 0x0020-0x002F Debug Module (S12SDBG) Map

| Address       | Name    |             | Bit 7  | Bit 6     | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1 | Bit 0  |

|---------------|---------|-------------|--------|-----------|--------|--------|---------|--------|-------|--------|

| 0x0020        | DBGC1   | R<br>W      | ARM    | 0<br>TRIG | 0      | BDM    | DBGBRK  | 0      | COMRV |        |

| 0x0021        | DBGSR   | R           | TBF    | 0         | 0      | 0      | 0       | SSF2   | SSF1  | SSF0   |

| 0x0022        | DBGTCR  | W<br>R<br>W | 0      | TSOURCE   | 0      | 0      | TRCMOD  |        | 0     | TALIGN |

| 0x0023        | DBGC2   | R           | 0      | 0         | 0      | 0      | 0       | 0      | ABCM  |        |

|               |         | W           | Dit 45 | Dit 4.4   | Dit 40 | Dit 40 | Dit 44  | Dit 40 |       |        |

| 0x0024        | DBGTBH  | R<br>W      | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8  |

| 0x0025        | DBGTBL  | R<br>W      | Bit 7  | Bit 6     | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1 | Bit 0  |

| 0x0026        | DBGCNT  | R           | TBF    | 0         | CNT    |        |         |        |       |        |

|               |         | W           |        |           |        |        |         |        |       |        |

| 0x0027        | DBGSCRX | R           | 0      | 0         | 0      | 0      | SC3 SC2 | SC2    | SC1   | SC0    |

|               |         | W           |        | -         |        | -      |         |        |       |        |

| 0x0027        | DBGMFR  | R           | 0      | 0         | 0      | 0      | 0       | MC2    | MC1   | MC0    |

| 0x0028<br>(1) | DBGACTL | W<br>R<br>W | SZE    | SZ        | TAG    | BRK    | RW      | RWE    | 0     | COMPE  |

| 0x0028<br>(2) | DBGBCTL | R<br>W      | SZE    | SZ        | TAG    | BRK    | RW      | RWE    | 0     | COMPE  |