Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                 |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 32MHz                                                                 |

| Connectivity               | CANbus, SCI, SPI                                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-TFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p96j0mft |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Dverview MC9S12P-Family**

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wakeup

- Break detect and transmit collision detect supporting LIN

### **1.3.12** Serial Peripheral Interface Module (SPI)

- Configurable 8- or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or slave mode

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

### 1.3.13 Analog-to-Digital Converter Module (ATD)

- 10-channel, 12-bit analog-to-digital converter

- 3 us single conversion time

- 8-/10-/12-bit resolution

- Left or right justified result data

- Internal oscillator for conversion in stop modes

- Wakeup from low power modes on analog comparison > or <= match

- Continuous conversion mode

- Multiple channel scans

- Pins can also be used as digital I/O

### 1.3.14 On-Chip Voltage Regulator (VREG)

- Linear voltage regulator with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR) circuit

- Low-voltage reset (LVR)

- High temperature sensor

### 1.3.15 Background Debug (BDM)

- Non-intrusive memory access commands

- Supports in-circuit programming of on-chip nonvolatile memory

# 1.7.4.6 VSSPLL — Ground Pin for PLL

This pin provides ground for the oscillator and the phased-locked loop. The voltage supply of nominally 1.8V is derived from the internal voltage regulator.

# 1.7.4.7 Power and Ground Connection Summary

| Mnemonic  | Nominal<br>Voltage | Description                                                                                                                                                                                                      |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDR      | 5.0 V              | External power supply to internal voltage regulator                                                                                                                                                              |

| VDDX[2:1] | 5.0 V              | External power and ground, supply to pin                                                                                                                                                                         |

| VSSX[2:1] | 0 V                | drivers                                                                                                                                                                                                          |

| VDDA      | 5.0 V              | Operating voltage and ground for the                                                                                                                                                                             |

| VSSA      | 0 V                | analog-to-digital converters and the<br>reference for the internal voltage regulator,<br>allows the supply voltage to the A/D to be<br>bypassed independently.                                                   |

| VRL       | 0 V                | Reference voltages for the analog-to-digital                                                                                                                                                                     |

| VRH       | 5.0 V              | converter.                                                                                                                                                                                                       |

| VSS3      | 0V                 | Internal power and ground generated by internal regulator for the internal core.                                                                                                                                 |

| VSSPLL    | 0V                 | Provides operating voltage and ground for<br>the phased-locked loop. This allows the<br>supply voltage to the PLL to be bypassed<br>independently. Internal power and ground<br>generated by internal regulator. |

Table 1-9. Power and Ground Connection Summary

# **1.8 System Clock Description**

For the system clock description please refer to chapter Chapter 7, "S12 Clock, Reset and Power Management Unit (S12CPMU).

# 1.9 Modes of Operation

The MCU can operate in different modes. These are described in 1.9.1 Chip Configuration Summary.

The MCU can operate in different power modes to facilitate power saving when full system performance is not required. These are described in 1.9.2 Low Power Operation.

Some modules feature a software programmable option to freeze the module status whilst the background debug module is active to facilitate debugging.

| Register<br>Name | Bit 7                       | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |  |  |  |  |

|------------------|-----------------------------|---|---|---|---|---|---|-------|--|--|--|--|

| 0x027C           | R 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0     |  |  |  |  |

| Reserved         | W                           |   |   |   |   |   |   |       |  |  |  |  |

| <u>0x027D</u>    | R 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0     |  |  |  |  |

| Reserved         | W                           |   |   |   |   |   |   |       |  |  |  |  |

| 0x027E           | R 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0     |  |  |  |  |

| Reserved         | w                           |   |   |   |   |   |   |       |  |  |  |  |

| 0x027F           | R 0                         | 0 | 0 | 0 | 0 | 0 | 0 | 0     |  |  |  |  |

| Reserved         | w                           |   |   |   |   |   |   |       |  |  |  |  |

|                  | = Unimplemented or Reserved |   |   |   |   |   |   |       |  |  |  |  |

#### 2.3.2 **Register Descriptions**

The following table summarizes the effect of the various configuration bits, i.e. data direction (DDR), output level (IO), reduced drive (RDR), pull enable (PE), pull select (PS) on the pin function and pull device activity.

The configuration bit PS is used for two purposes:

- 1. Configure the sensitive interrupt edge (rising or falling), if interrupt is enabled.

- 2. Select either a pull-up or pull-down device if PE is active.

#### 1. Read: Anytime

Write:Never, writes to this register have no effect.

#### Table 2-22. PTIS Register Field Descriptions

| Field | Description                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0   | <b>Port S input data</b> —                                                                                                                          |

| PTIS  | A read always returns the buffered input state of the associated pin. It can be used to detect overload or short circuit conditions on output pins. |

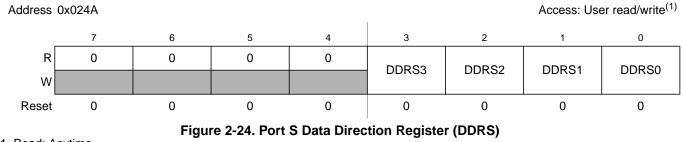

# 2.3.26 Port S Data Direction Register (DDRS)

1. Read: Anytime Write: Anytime

#### Table 2-23. DDRS Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-2<br>DDRS | Port S data direction—<br>This bit determines whether the associated pin is an input or output.                                                                                                                                                                  |

|             | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

| 1<br>DDRS   | Port S data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|             | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

| 0<br>DDRS   | Port S data direction—<br>This bit determines whether the associated pin is an input or output.<br>Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. In this case the<br>data direction bit will not change. |

|             | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                              |

#### Memory Map Control (S12PMMCV1)

CALL/RTC instructions should only be used when needed. The JSR and RTS instructions can be used to access subroutines that are already present in the local CPU memory map (i.e. in the same page in the program memory page window for example). However calling a function located in a different page requires usage of the CALL instruction. The function must be terminated by the RTC instruction. Because the RTC instruction restores contents of the PPAGE register from the stack, functions terminated with the RTC instruction must be called using the CALL instruction even when the correct page is already present in the memory map. This is to make sure that the correct PPAGE value will be present on stack at the time of the RTC instruction execution.

This information is being provided so that the MCU integrator will be aware that such a conflict could occur.

The hardware handshake protocol is enabled by the ACK\_ENABLE and disabled by the ACK\_DISABLE BDM commands. This provides backwards compatibility with the existing POD devices which are not able to execute the hardware handshake protocol. It also allows for new POD devices, that support the hardware handshake protocol, to freely communicate with the target device. If desired, without the need for waiting for the ACK pulse.

The commands are described as follows:

- ACK\_ENABLE enables the hardware handshake protocol. The target will issue the ACK pulse when a CPU command is executed by the CPU. The ACK\_ENABLE command itself also has the ACK pulse as a response.

- ACK\_DISABLE disables the ACK pulse protocol. In this case, the host needs to use the worst case delay time at the appropriate places in the protocol.

The default state of the BDM after reset is hardware handshake protocol disabled.

All the read commands will ACK (if enabled) when the data bus cycle has completed and the data is then ready for reading out by the BKGD serial pin. All the write commands will ACK (if enabled) after the data has been received by the BDM through the BKGD serial pin and when the data bus cycle is complete. See Section 5.4.3, "BDM Hardware Commands" and Section 5.4.4, "Standard BDM Firmware Commands" for more information on the BDM commands.

The ACK\_ENABLE sends an ACK pulse when the command has been completed. This feature could be used by the host to evaluate if the target supports the hardware handshake protocol. If an ACK pulse is issued in response to this command, the host knows that the target supports the hardware handshake protocol. If the target does not support the hardware handshake protocol the ACK pulse is not issued. In this case, the ACK\_ENABLE command is ignored by the target since it is not recognized as a valid command.

The BACKGROUND command will issue an ACK pulse when the CPU changes from normal to background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO command will issue an ACK pulse when the CPU exits from background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO\_UNTIL command is equivalent to a GO command with exception that the ACK pulse, in this case, is issued when the CPU enters into background mode. This command is an alternative to the GO command and should be used when the host wants to trace if a breakpoint match occurs and causes the CPU to enter active background mode. Note that the ACK is issued whenever the CPU enters BDM, which could be caused by a breakpoint match or by a BGND instruction being executed. The ACK pulse related to this command could be aborted using the SYNC command.

The TRACE1 command has the related ACK pulse issued when the CPU enters background active mode after one instruction of the application program is executed. The ACK pulse related to this command could be aborted using the SYNC command.

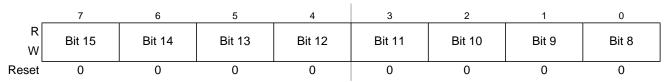

#### Table 6-28. DBGADH Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits[15:8] | <ul> <li>Comparator Data High Compare Bits— The Comparator data high compare bits control whether the selected comparator compares the data bus bits [15:8] to a logic one or logic zero. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparator A. Data bus comparisons are only performed if the TAG bit in DBGACTL is clear.</li> <li>0 Compare corresponding data bit to a logic zero</li> <li>1 Compare corresponding data bit to a logic one</li> </ul> |

### 6.3.2.8.6 Debug Comparator Data Low Register (DBGADL)

Address: 0x002D

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 6-20. Debug Comparator Data Low Register (DBGADL)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG not armed.

#### Table 6-29. DBGADL Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits[7:0] | <b>Comparator Data Low Compare Bits</b> — The Comparator data low compare bits control whether the selected comparator compares the data bus bits [7:0] to a logic one or logic zero. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparator A. Data bus comparisons are only performed if the TAG bit in DBGACTL is clear 0 Compare corresponding data bit to a logic zero 1 Compare corresponding data bit to a logic one |

### 6.3.2.8.7 Debug Comparator Data High Mask Register (DBGADHM)

Address: 0x002E

#### Figure 6-21. Debug Comparator Data High Mask Register (DBGADHM)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG not armed.

ck, Reset and Power Management Unit (S12CPMU)

# 7.3 Memory Map and Registers

This section provides a detailed description of all registers accessible in the S12CPMU.

### 7.3.1 Module Memory Map

The S12CPMU registers are shown in Figure 7-3.

| Addres<br>s | Name                  |        | Bit 7  | 6          | 5             | 4             | 3     | 2          | 1             | Bit 0         |  |  |

|-------------|-----------------------|--------|--------|------------|---------------|---------------|-------|------------|---------------|---------------|--|--|

| 0x0034      | CPMU<br>SYNR          | R<br>W | VCOFR  | Q[1:0]     |               | SYNDIV[5:0]   |       |            |               |               |  |  |

| 0x0035      | CPMU<br>REFDIV        | R<br>W | REFFR  | Q[1:0]     | 0             | 0 REFDIV[3:0] |       |            |               |               |  |  |

| 0x0036      | CPMU<br>POSTDIV       | R<br>W | 0      | 0          | 0             |               |       | POSTDIV[4: | :0]           |               |  |  |

| 0x0037      | CPMUFLG               | R<br>W | RTIF   | PORF       | LVRF          | LOCKIF        | LOCK  | ILAF       | OSCIF         | UPOSC         |  |  |

| 0x0038      | CPMUINT               | R<br>W | RTIE   | 0          | 0             | LOCKIE        | 0     | 0          | OSCIE         | 0             |  |  |

| 0x0039      | CPMUCLKS              | R<br>W | PLLSEL | PSTP       | 0             | 0             | PRE   | PCE        | RTI<br>OSCSEL | COP<br>OSCSEL |  |  |

| 0x003A      | CPMUPLL               | R<br>W | 0      | 0          | FM1           | FM0           | 0     | 0          | 0             | 0             |  |  |

| 0x003B      | CPMURTI               | R<br>W | RTDEC  | RTR6       | RTR5          | RTR4          | RTR3  | RTR2       | RTR1          | RTR0          |  |  |

| 0x003C      | CPMUCOP               | R<br>W | WCOP   | RSBCK      | 0<br>WRTMASK  | 0             | 0     | CR2        | CR1           | CR0           |  |  |

| 0x003D      | RESERVED<br>CPMUTEST0 | R<br>W | 0      | 0          | 0             | 0             | 0     | 0          | 0             | 0             |  |  |

| 0x003E      | RESERVED<br>CPMUTEST1 | R<br>W | 0      | 0          | 0             | 0             | 0     | 0          | 0             | 0             |  |  |

| 0x003F      | CPMU                  | R      | 0      | 0          | 0             | 0             | 0     | 0          | 0             | 0             |  |  |

| 0,00001     | ARMCOP                | W      | Bit 7  | Bit 6      | Bit 5         | Bit 4         | Bit 3 | Bit 2      | Bit 1         | Bit 0         |  |  |

| 0x02F0      | CPMU<br>HTCTL         | R<br>W | 0      | 0          | VSEL          | 0             | HTE   | HTDS       | HTIE          | HTIF          |  |  |

| 0x02F1      | CPMU<br>LVCTL         | R<br>W | 0      | 0          | 0             | 0             | 0     | LVDS       | LVIE          | LVIF          |  |  |

| 0x02F2      | CPMU<br>APICTL        | R<br>W | APICLK | 0          | 0             | APIES         | APIEA | APIFE      | APIE          | APIF          |  |  |

|             |                       |        |        | = Unimplen | nented or Res | erved         |       |            |               | J             |  |  |

Figure 7-3. CPMU Register Summary

S12P-Family Reference Manual, Rev. 1.13

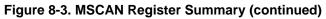

le's Scalable Controller Area Network (S12MSCANV3)

| Register<br>Name            |        | Bit 7  | 6                                                          | 5             | 4            | 3             | 2           | 1      | Bit 0  |  |  |  |

|-----------------------------|--------|--------|------------------------------------------------------------|---------------|--------------|---------------|-------------|--------|--------|--|--|--|

| 0x000E                      | R      | RXERR7 | RXERR6                                                     | RXERR5        | RXERR4       | RXERR3        | RXERR2      | RXERR1 | RXERR0 |  |  |  |

| CANRXERR                    | W      |        |                                                            |               |              |               |             |        |        |  |  |  |

| 0x000F                      | R      | TXERR7 | TXERR6                                                     | TXERR5        | TXERR4       | TXERR3        | TXERR2      | TXERR1 | TXERR0 |  |  |  |

| CANTXERR                    | W      |        |                                                            |               |              |               |             |        |        |  |  |  |

| 0x0010–0x0013<br>CANIDAR0–3 | R<br>W | AC7    | AC6                                                        | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |  |  |

| 0x0014–0x0017<br>CANIDMRx   | R<br>W | AM7    | AM6                                                        | AM5           | AM4          | AM3           | AM2         | AM1    | AMO    |  |  |  |

| 0x0018-0x001B<br>CANIDAR4-7 | R<br>W | AC7    | AC6                                                        | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |  |  |

| 0x001C-0x001F<br>CANIDMR4-7 | R<br>W | AM7    | AM6                                                        | AM5           | AM4          | AM3           | AM2         | AM1    | AM0    |  |  |  |

| 0x0020–0x002F<br>CANRXFG    | R<br>W |        | See                                                        | Section 8.3.3 | , "Programme | er's Model of | Message Sto | rage"  |        |  |  |  |

| 0x0030–0x003F<br>CANTXFG    | R<br>W |        | See Section 8.3.3, "Programmer's Model of Message Storage" |               |              |               |             |        |        |  |  |  |

|                             |        |        | = Unimplen                                                 | nented or Re  | served       |               |             |        |        |  |  |  |

# 8.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

### 8.3.2.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

Freescale's Scalable Controller Area Network (S12MSCANV3)

| Register<br>Name |        | Bit 7 | 6   | 5   | 4   | 3    | 2    | 1    | Bit0 |

|------------------|--------|-------|-----|-----|-----|------|------|------|------|

| 0x00X4<br>DSR0   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X5<br>DSR1   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X6<br>DSR2   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X7<br>DSR3   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X8<br>DSR4   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00X9<br>DSR5   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00XA<br>DSR6   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| 0x00XB<br>DSR7   | R<br>W | DB7   | DB6 | DB5 | DB4 | DB3  | DB2  | DB1  | DB0  |

| DLR              | R<br>W |       |     |     |     | DLC3 | DLC2 | DLC1 | DLC0 |

#### Figure 8-24. Receive/Transmit Message Buffer — Extended Identifier Mapping (continued)

= Unused, always read 'x'

#### Read:

- For transmit buffers, anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

- For receive buffers, only when RXF flag is set (see Section 8.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)").

Write:

#### Pulse-Width Modulator (PWM8B6CV1) Block Description

Module Base + 0x0017

| ~~~~   | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | ~~~~~~ | ~~~~~~ |   | ~~~~~~~ | ~~~~~~~ | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |       |

|--------|-----------------------------------------|--------|--------|---|---------|---------|-----------------------------------------|-------|

|        | 7                                       | 6      | 5      | 4 | 3       | 2       | 1                                       | 0     |

| R<br>W | Bit 7                                   | 6      | 5      | 4 | 3       | 2       | 1                                       | Bit 0 |

| Reset  | 0                                       | 0      | 0      | 0 | 0       | 0       | 0                                       | 0     |

Figure 10-26. PWM Channel Period Registers (PWMPER5)

Read: anytime

Write: anytime

### 10.3.2.14 PWM Channel Duty Registers (PWMDTYx)

There is a dedicated duty register for each channel. The value in this register determines the duty of the associated PWM channel. The duty value is compared to the counter and if it is equal to the counter value a match occurs and the output changes state.

The duty registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to 0x0000)

- The channel is disabled

In this way, the output of the PWM will always be either the old duty waveform or the new duty waveform, not some variation in between. If the channel is not enabled, then writes to the duty register will go directly to the latches as well as the buffer.

#### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active duty due to the double buffering scheme.

Reference Section 10.4.2.3, "PWM Period and Duty," for more information.

### NOTE

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time. If the polarity bit is 1, the output starts high and then goes low when the duty count is reached, so the duty registers contain a count of the high time. If the polarity bit is 0, the output starts low and then goes high when the duty count is reached, so the duty registers contain a count of the low time.

To calculate the output duty cycle (high time as a % of period) for a particular channel:

- Polarity = 0 (PPOLx = 0) Duty cycle = [(PWMPERx PWMDTYx)/PWMPERx] \* 100%

- Polarity = 1 (PPOLx = 1) Duty cycle = [PWMDTYx / PWMPERx] \* 100%

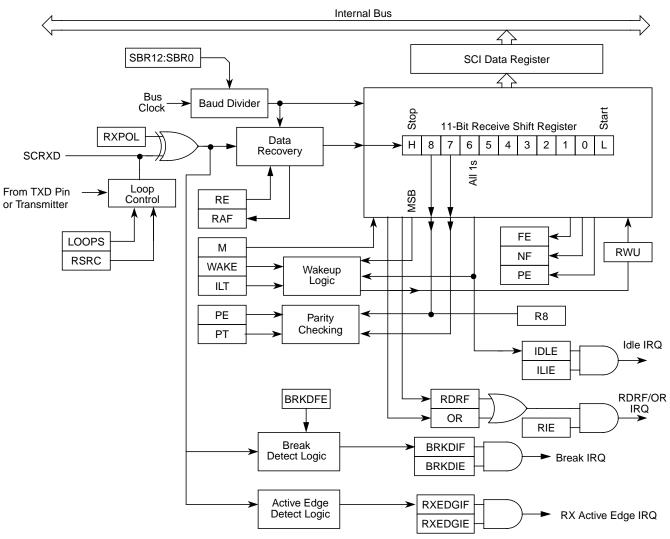

# 11.4.6 Receiver

Figure 11-20. SCI Receiver Block Diagram

### 11.4.6.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

### 11.4.6.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the RXD pin. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set,

### Table 12-2. SPICR1 Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — The $\overline{SS}$ output feature is enabled only in master mode, if MODFEN is set, by asserting the SSOE as shown in Table 12-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                              |

| 0<br>LSBFE | <ul> <li>LSB-First Enable — This bit does not affect the position of the MSB and LSB in the data register. Reads and writes of the data register always have the MSB in the highest bit position. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Data is transferred most significant bit first.</li> <li>1 Data is transferred least significant bit first.</li> </ul> |

Table 12-3. SS Input / Output Selection

| MODFEN | SSOE | Master Mode                | Slave Mode |

|--------|------|----------------------------|------------|

| 0      | 0    | SS not used by SPI         | SS input   |

| 0      | 1    | SS not used by SPI         | SS input   |

| 1      | 0    | SS input with MODF feature | SS input   |

| 1      | 1    | SS is slave select output  | SS input   |

# 12.3.2.2 SPI Control Register 2 (SPICR2)

Module Base +0x0001

| 00000 | 0000000 | 0000000                     | 00000000 |        |         | 0000000 | 00000000 | 00000000 |  |  |  |

|-------|---------|-----------------------------|----------|--------|---------|---------|----------|----------|--|--|--|

|       | 7       | 6                           | 5        | 4      | 3       | 2       | 1        | 0        |  |  |  |

| R     | 0       | XFRW                        | 0        | MODFEN | BIDIROE | 0       | SPISWAI  | SPC0     |  |  |  |

| W     |         |                             |          |        | DIDINOL |         |          | 0100     |  |  |  |

| Reset | 0       | 0                           | 0        | 0      | 0       | 0       | 0        | 0        |  |  |  |

|       |         | = Unimplemented or Reserved |          |        |         |         |          |          |  |  |  |

|       |         |                             |          |        |         |         |          |          |  |  |  |

Figure 12-4. SPI Control Register 2 (SPICR2)

### Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

drive the MOSI and SCK lines. In this case, the SPI immediately switches to slave mode, by clearing the MSTR bit and also disables the slave output buffer MISO (or SISO in bidirectional mode). So the result is that all outputs are disabled and SCK, MOSI, and MISO are inputs. If a transmission is in progress when the mode fault occurs, the transmission is aborted and the SPI is forced into idle state.

This mode fault error also sets the mode fault (MODF) flag in the SPI status register (SPISR). If the SPI interrupt enable bit (SPIE) is set when the MODF flag becomes set, then an SPI interrupt sequence is also requested.

When a write to the SPI data register in the master occurs, there is a half SCK-cycle delay. After the delay, SCK is started within the master. The rest of the transfer operation differs slightly, depending on the clock format specified by the SPI clock phase bit, CPHA, in SPI control register 1 (see Section 12.4.3, "Transmission Formats").

### NOTE

A change of the bits CPOL, CPHA, SSOE, LSBFE, XFRW, MODFEN, SPC0, or BIDIROE with SPC0 set, SPPR2-SPPR0 and SPR2-SPR0 in master mode will abort a transmission in progress and force the SPI into idle state. The remote slave cannot detect this, therefore the master must ensure that the remote slave is returned to idle state.

# 12.4.2 Slave Mode

The SPI operates in slave mode when the MSTR bit in SPI control register 1 is clear.

• Serial clock

In slave mode, SCK is the SPI clock input from the master.

• MISO, MOSI pin

In slave mode, the function of the serial data output pin (MISO) and serial data input pin (MOSI) is determined by the SPC0 bit and BIDIROE bit in SPI control register 2.

•  $\overline{SS}$  pin

The  $\overline{SS}$  pin is the slave select input. Before a data transmission occurs, the  $\overline{SS}$  pin of the slave SPI must be low.  $\overline{SS}$  must remain low until the transmission is complete. If  $\overline{SS}$  goes high, the SPI is forced into idle state.

The  $\overline{SS}$  input also controls the serial data output pin, if  $\overline{SS}$  is high (not selected), the serial data output pin is high impedance, and, if  $\overline{SS}$  is low, the first bit in the SPI data register is driven out of the serial data output pin. Also, if the slave is not selected ( $\overline{SS}$  is high), then the SCK input is ignored and no internal shifting of the SPI shift register occurs.

Although the SPI is capable of duplex operation, some SPI peripherals are capable of only receiving SPI data in a slave mode. For these simpler devices, there is no serial data out pin.

### NOTE

When peripherals with duplex capability are used, take care not to simultaneously enable two receivers whose serial outputs drive the same system slave's serial data output line.

# A.1.10 Supply Currents

This section describes the current consumption characteristics of the device as well as the conditions for the measurements.

### A.1.10.1 Measurement Conditions

Run current is measured on VDDR pin. It does not include the current to drive external loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC1M trimmed to 1MHz. The bus frequency is 32MHz and the CPU frequency is 64MHz. Table A-8., Table A-9. and Table A-10. show the configuration of the CPMU module and the peripherals for Run, Wait and Stop current measurement.

| CPMU REGISTER | Bit settings/Conditions                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------|

| CPMUCLKS      | PLLSEL=0, PSTP=1,<br>PRE=PCE=RTIOSCSEL=COPOSCSEL=1                                                  |

| CPMUOSC       | OSCE=1, External Square wave on EXTAL $\rm f_{EXTAL}$ =16MHz, $\rm V_{IH}$ = 1.8V, $\rm V_{IL}$ =0V |

| CPMURTI       | RTDEC=0, RTR[6:4]=111, RTR[3:0]=1111;                                                               |

| CPMUCOP       | WCOP=1, CR[2:0]=111                                                                                 |

Table A-8. CPMU Configuration for Pseudo Stop Current Measurement

| Table A-9. CPUM Configuration for Run/Wait | t and Full Stop Current Measurement |

|--------------------------------------------|-------------------------------------|

|--------------------------------------------|-------------------------------------|

| CPMU REGISTER | Bit settings/Conditions                                                   |  |  |  |  |

|---------------|---------------------------------------------------------------------------|--|--|--|--|

| CPMUSYNR      | VCOFRQ[1:0]=01,SYNDIV[5:0] = 32                                           |  |  |  |  |

| CPMUPOSTDIV   | POSTDIV[4:0]=0,                                                           |  |  |  |  |

| CPMUCLKS      | PLLSEL=1                                                                  |  |  |  |  |

| CPMUOSC       | OSCE=0,<br>Reference clock for PLL is $f_{ref}=f_{irc1m}$ trimmed to 1MHz |  |  |  |  |

| Al            | PI settings for STOP current measurement                                  |  |  |  |  |

| CPMUAPICTL    | APIEA=0, APIFE=1, APIE=0                                                  |  |  |  |  |

| CPMUAPITR     | trimmed to 10Khz                                                          |  |  |  |  |

| CPMUAPIRH/RL  | set to \$FFFF                                                             |  |  |  |  |

### NOTE

All values shown in Table A-19 are preliminary and subject to further characterization.

| Conditions are shown in Table A-4 unless otherwise noted |                                                                                                                                                               |                                                                                                                            |                     |     |                     |     |        |  |  |  |  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|-----|--------|--|--|--|--|

| Num                                                      | С                                                                                                                                                             | Rating                                                                                                                     | Symbol              | Min | Тур                 | Max | Unit   |  |  |  |  |

|                                                          | Program Flash Arrays                                                                                                                                          |                                                                                                                            |                     |     |                     |     |        |  |  |  |  |

| 1                                                        | I C Data retention at an average junction temperature of $T_{Javg} = t_{NVMRET}$ 20 $100^{(2)}$ - $85^{\circ}C^{(1)}$ after up to 10,000 program/erase cycles |                                                                                                                            |                     |     |                     |     |        |  |  |  |  |

| 2                                                        | С                                                                                                                                                             | Program Flash number of program/erase cycles (-40°C $\leq$ tj $\leq$ 150°C)                                                | n <sub>FLPE</sub>   | 10K | 100K <sup>(3)</sup> | _   | Cycles |  |  |  |  |

|                                                          |                                                                                                                                                               | Data Flash Array                                                                                                           |                     |     |                     |     |        |  |  |  |  |

| 3                                                        | С                                                                                                                                                             | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 50,000 program/erase cycles  | t <sub>NVMRET</sub> | 5   | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 4                                                        | С                                                                                                                                                             | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles  | t <sub>NVMRET</sub> | 10  | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 5                                                        | С                                                                                                                                                             | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after less than 100 program/erase cycles | t <sub>NVMRET</sub> | 20  | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 6                                                        | С                                                                                                                                                             | Data Flash number of program/erase cycles (-40°C $\leq$ tj $\leq$ 150°C)                                                   | n <sub>FLPE</sub>   | 50K | 500K <sup>3</sup>   | _   | Cycles |  |  |  |  |

#### Table A-19. NVM Reliability Characteristics

1. T<sub>Javg</sub> does not exceed 85°C in a typical temperature profile over the lifetime of a consumer, industrial or automotive application.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines Typical Data Retention, please refer to Engineering Bulletin EB618

3. Spec table quotes typical endurance evaluated at 25°C for this product family. For additional information on how Freescale defines Typical Endurance, please refer to Engineering Bulletin EB619.

# A.4 Phase Locked Loop

### A.4.1 Jitter Definitions

With each transition of the feedback clock, the deviation from the reference clock is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-2.

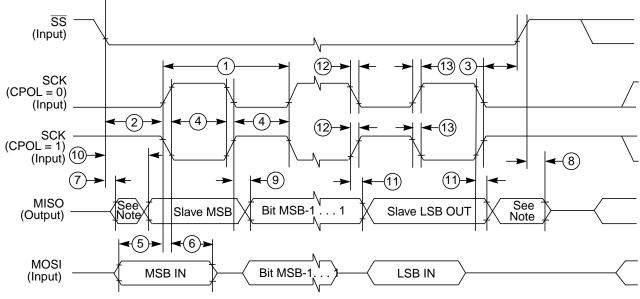

In Table A-27 the timing characteristics for master mode are listed.

| Num | С | Characteristic                                   | Symbol            | Min    | Тур | Max  | Unit             |

|-----|---|--------------------------------------------------|-------------------|--------|-----|------|------------------|

| 1   | D | SCK frequency                                    | f <sub>sck</sub>  | 1/2048 |     | 1/2  | f <sub>bus</sub> |

| 1   | D | SCK period                                       | t <sub>sck</sub>  | 2      | _   | 2048 | t <sub>bus</sub> |

| 2   | D | Enable lead time                                 | t <sub>lead</sub> |        | 1/2 |      | t <sub>sck</sub> |

| 3   | D | Enable lag time                                  | t <sub>lag</sub>  | _      | 1/2 | _    | t <sub>sck</sub> |

| 4   | D | Clock (SCK) high or low time                     | t <sub>wsck</sub> |        | 1/2 | _    | t <sub>sck</sub> |

| 5   | D | Data setup time (inputs)                         | t <sub>su</sub>   | 8      |     |      | ns               |

| 6   | D | Data hold time (inputs)                          | t <sub>hi</sub>   | 8      | —   | _    | ns               |

| 9   | D | Data valid after SCK edge                        | t <sub>vsck</sub> |        | —   | 29   | ns               |

| 10  | D | Data valid after $\overline{SS}$ fall (CPHA = 0) | t <sub>vss</sub>  |        |     | 15   | ns               |

| 11  | D | Data hold time (outputs)                         | t <sub>ho</sub>   | 20     | —   | _    | ns               |

| 12  | D | Rise and fall time inputs                        | t <sub>rfi</sub>  | _      |     | 8    | ns               |

| 13  | D | Rise and fall time outputs                       | t <sub>rfo</sub>  | _      | _   | 8    | ns               |

### A.11.2 Slave Mode

In Figure A-7 the timing diagram for slave mode with transmission format CPHA = 0 is depicted.

NOTE: Not defined

Figure A-7. SPI Slave Timing (CPHA = 0)

### 0x0034-0x003F Clock Reset and Power Management (CPMU) Map

| Address | Name      |         | Bit 7     | Bit 6 | Bit 5  | Bit 4        | Bit 3         | Bit 2 | Bit 1   | Bit 0  |  |      |

|---------|-----------|---------|-----------|-------|--------|--------------|---------------|-------|---------|--------|--|------|

| 0x0038  | CPMUINT   | R       | RTIE      | 0     | 0      | LOCKIE       | 0             | 0     | OSCIE   | 0      |  |      |

| 070030  |           | W       |           |       |        | LOOKIL       |               |       |         |        |  |      |

| 0x0039  | CPMUCLKS  | R       | PLLSEL    | PSTP  | 0      | 0            | PRE           | PCE   | RTIOSCS | COPOSC |  |      |

| 070039  | CI WOOLKS | W       | TLLOLL    | 1.011 |        |              | FNL           | TOL   | EL      | SEL    |  |      |

| 0x003A  | CPMUPLL   | R       | 0         | 0     | FM1    | FM0          | 0             | 0     | 0       | 0      |  |      |

| 00003A  | CFMOFLL   | W       |           |       |        | FIND         |               |       |         |        |  |      |

| 0x003B  | CPMURTI   | R       | RTDEC     | RTR6  | RTR5   | RTR4         | RTR3          | RTR2  | RTR1    | RTR0   |  |      |

| 0X003D  | CFINIORTI | CFMURTI | 5 CFMURII | W     | RIDEC  | KIN0         | RTR3          | N1N4  | NIN3    | NINZ   |  | NINU |

|         |           | R       |           |       | 0      | 0            | 0             |       |         |        |  |      |

| 0x003C  | CPMUCOP   | W       | WCOP      | RSBCK | WRTMAS |              |               | CR2   | CR1     | CR0    |  |      |

|         |           |         |           |       | K      |              |               |       |         |        |  |      |

| 0x003D  | Reserved  | R       | 0         | 0     | 0      | 0            | 0             | 0     | 0       | 0      |  |      |

| 07003D  | Reserved  | W       |           |       | R      | leserved For | r Factory Tes | st    |         |        |  |      |

| 0x003E  | Reserved  | R       | 0         | 0     | 0      | 0            |               | 0     | 0       | 0      |  |      |

| UXUUJE  | Reserved  | W       |           |       | R      | leserved For | r Factory Tes | st    |         |        |  |      |

| 0x003F  | CPMU      | R       | 0         | 0     | 0      | 0            | 0             | 0     | 0       | 0      |  |      |

| 0X003F  | ARMCOP    | W       | Bit 7     | 6     | 5      | 4            | 3             | 2     | 1       | Bit 0  |  |      |

### 0x0040-0x006F Timer Module (TIM) Map

| Address | Name  |        | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x0040  | TIOS  | R<br>W | IOS7   | IOS6  | IOS5  | IOS4  | IOS3  | IOS2  | IOS1  | IOS0  |

| 0x0041  | CFORC | R      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0X0041  | CFORC | W      | FOC7   | FOC6  | FOC5  | FOC4  | FOC3  | FOC2  | FOC1  | FOC0  |

| 0x0042  | OC7M  | R<br>W | OC7M7  | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| 0x0043  | OC7D  | R<br>W | OC7D7  | OC7D6 | OC7D5 | OC7D4 | OC7D3 | OC7D2 | OC7D1 | OC7D0 |

| 0x0044  | TCNTH | R      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 070044  |       | W      |        |       |       |       |       |       |       |       |

| 0x0045  | TCNTL | R      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|         |       | W      |        |       |       |       |       |       |       |       |

| 0x0046  | TSCR1 | R<br>W | TEN    | TSWAI | TSFRZ | TFFCA | PRNT  | 0     | 0     | 0     |

| 0x0047  | ΤΤΟΥ  | R<br>W | TOV7   | TOV6  | TOV5  | TOV4  | TOV3  | TOV2  | TOV1  | TOV0  |

| 0x0048  | TCTL1 | R<br>W | OM7    | OL7   | OM6   | OL6   | OM5   | OL5   | OM4   | OL4   |

| 0x0049  | TCTL2 | R<br>W | OM3    | OL3   | OM2   | OL2   | OM1   | OL1   | OM0   | OL0   |

| 0x004A  | TCTL3 | R<br>W | EDG7B  | EDG7A | EDG6B | EDG6A | EDG5B | EDG5A | EDG4B | EDG4A |

| 0x004B  | TCTL4 | R<br>W | EDG3B  | EDG3A | EDG2B | EDG2A | EDG1B | EDG1A | EDG0B | EDG0A |

S12P-Family Reference Manual, Rev. 1.13