#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                           |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | SPI                                                                |

| Peripherals                | LED, LVD, POR, WDT                                                 |

| Number of I/O              | 13                                                                 |

| Program Memory Size        | 3.8KB (3.8K x 8)                                                   |

| Program Memory Type        | EPROM, UV                                                          |

| EEPROM Size                | 128 x 8                                                            |

| RAM Size                   | 128 x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | A/D 7x8b                                                           |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                    |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 20-CDIP (0.300", 7.62mm) Window                                    |

| Supplier Device Package    | -                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62e60cf1 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

|        |                                                           | Doci | ument |

|--------|-----------------------------------------------------------|------|-------|

|        |                                                           |      | age   |

|        |                                                           |      |       |

| 4.1    |                                                           |      |       |

|        | 4.1.1 Operating Modes                                     |      |       |

|        | <ul><li>4.1.2 Safe I/O State Switching Sequence</li></ul> |      |       |

|        | 4.1.4 SPI Alternate function Option                       |      |       |

| 4.2    |                                                           |      |       |

|        | 4.2.1 Timer Operation                                     |      | 44    |

|        | 4.2.2 Timer Interrupt                                     |      |       |

|        | 4.2.3 Application Notes                                   | •    | 44    |

|        | 4.2.4 Timer Registers                                     |      |       |

| 4.3    | AUTO-RELOAD TIMER                                         |      |       |

|        | 4.3.1 AR Timer Description                                |      |       |

|        | 4.3.2 Timer Operating Modes   4.3.3 AR Timer Registers    |      |       |

| 44     | A/D CONVERTER (ADC)                                       |      |       |

|        | 4.4.1 Application Notes                                   |      |       |

| 4.5    | SERIAL PERIPHERAL INTERFACE (SPI)                         |      |       |

| -      | 4.5.1 SPI Registers                                       |      |       |

| 4.6    | SPI TIMING DIAGRAMS                                       |      |       |

| 5 SOF  | TWARE                                                     | !    | 59    |

| 5.1    | ST6 ARCHITECTURE                                          |      | 59    |

| 5.2    | ADDRESSING MODES                                          | !    | 59    |

| 5.3    | INSTRUCTION SET                                           | (    | 60    |

| 6 ELEC | CTRICAL CHARACTERISTICS                                   |      | 65    |

| 6.1    | ABSOLUTE MAXIMUM RATINGS                                  |      | 65    |

| 6.2    | RECOMMENDED OPERATING CONDITIONS                          | (    | 66    |

| 6.3    | DC ELECTRICAL CHARACTERISTICS                             | (    | 67    |

| 6.4    | AC ELECTRICAL CHARACTERISTICS                             | (    | 68    |

| 6.5    | A/D CONVERTER CHARACTERISTICS                             | (    | 69    |

| 6.6    | TIMER CHARACTERISTICS                                     |      | 69    |

|        | SPI CHARACTERISTICS                                       |      |       |

| 6.8    | ARTIMER ELECTRICAL CHARACTERISTICS                        | (    | 69    |

| 7 GEN  | ERAL INFORMATION                                          |      | 75    |

| 7.1    | PACKAGE MECHANICAL DATA                                   |      | 75    |

| 7.2    | ORDERING INFORMATION                                      |      | 76    |

\_\_\_\_\_

57

### **1 GENERAL DESCRIPTION**

#### **1.1 INTRODUCTION**

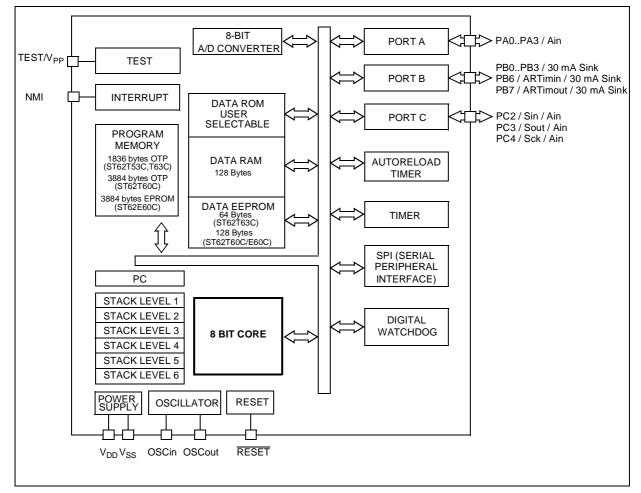

The ST62T53C, ST62T60C, ST62T63C and ST62E60C devices are low cost members of the ST62xx 8-bit HCMOS family of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST62E60C is the erasable EPROM version of the ST62T60C device, which may be used to emulate the ST62T53C, ST62T60C and ST62T63C devices, as well as the respective ST6253C, ST6260B and ST6263B ROM devices.

OTP and EPROM devices are functionally identical. The ROM based versions offer the same functionality selecting as ROM options the options defined in the programmable option byte of the OTP/ EPROM versions.

OTP devices offer all the advantages of user programmability at low cost, which make them the ideal choice in a wide range of applications where frequent code changes, multiple code versions or last minute programmability are required.

These compact low-cost devices feature a Timer comprising an 8-bit counter and a 7-bit programmable prescaler, an 8-bit Auto-Reload Timer, EEPROM data capability (except ST62T53C), a serial port communication interface, an 8-bit A/D Converter with 7 analog inputs and a Digital Watchdog timer, making them well suited for a wide range of automotive, appliance and industrial applications.

#### Figure 1. Block Diagram

57

### MEMORY MAP (Cont'd)

### 1.3.3 Data Space

Data Space accommodates all the data necessary for processing the user program. This space comprises the RAM resource, the processor core and peripheral registers, as well as read-only data such as constants and look-up tables in OTP/ EPROM.

#### 1.3.3.1 Data ROM

All read-only data is physically stored in program memory, which also accommodates the Program Space. The program memory consequently contains the program code to be executed, as well as the constants and look-up tables required by the application.

The Data Space locations in which the different constants and look-up tables are addressed by the processor core may be thought of as a 64-byte window through which it is possible to access the read-only data stored in OTP/EPROM.

#### 1.3.3.2 Data RAM/EEPROM

In ST62T53C, T60C, T63C and ST62E60C devices, the data space includes 60 bytes of RAM, the accumulator (A), the indirect registers (X), (Y), the short direct registers (V), (W), the I/O port registers, the peripheral data and control registers, the interrupt option register and the Data ROM Window register (DRW register).

Additional RAM and EEPROM pages can also be addressed using banks of 64 bytes located between addresses 00h and 3Fh.

#### 1.3.4 Stack Space

Stack space consists of six 12-bit registers which are used to stack subroutine and interrupt return addresses, as well as the current program counter contents.

| Table 1. Additional | <b>RAM/EEPROM Banks</b> |

|---------------------|-------------------------|

|---------------------|-------------------------|

| Device        | RAM          | EEPROM       |  |

|---------------|--------------|--------------|--|

| ST62T53C      | 1 x 64 bytes | -            |  |

| ST62T60C/E60C | 1 x 64 bytes | 2 x 64 bytes |  |

| ST62T63C      | 1 x 64 bytes | 1 x 64 bytes |  |

# Table 2ST62T53C, T60C, T63C and ST62E60C Data Memory Space

|                                              | -            |

|----------------------------------------------|--------------|

| RAM and EEPROM                               | 000h         |

| RAM and EEPROM                               | 03Fh         |

|                                              | 040h         |

| DATA ROM WINDOW AREA                         |              |

|                                              | 07Fh         |

| X REGISTER                                   | 080h         |

| Y REGISTER                                   | 081h         |

| V REGISTER                                   | 082h         |

| W REGISTER                                   | 083h         |

|                                              | 084h         |

| DATA RAM 60 BYTES                            | 0BFh         |

| PORT A DATA REGISTER                         | 0C0h         |

| PORT B DATA REGISTER                         | 0C1h         |

| PORT C DATA REGISTER                         | 0C2h         |

| RESERVED                                     | 0C3h         |

| PORT A DIRECTION REGISTER                    | 0C4h         |

| PORT B DIRECTION REGISTER                    | 0C5h         |

| PORT C DIRECTION REGISTER                    | 0C6h         |

| RESERVED                                     | 0C0h         |

|                                              |              |

| INTERRUPT OPTION REGISTER                    | 0C8h*        |

| DATA ROM WINDOW REGISTER                     | 0C9h*        |

| RESERVED                                     | 0CAh         |

|                                              | 0CBh         |

| PORT A OPTION REGISTER                       | 0CCh         |

| PORT B OPTION REGISTER                       | 0CDh         |

| PORT C OPTION REGISTER                       | 0CEh         |

| RESERVED                                     | 0CFh         |

| A/D DATA REGISTER                            | 0D0h         |

| A/D CONTROL REGISTER                         | 0D1h         |

| TIMER PRESCALER REGISTER                     | 0D2h         |

| TIMER COUNTER REGISTER                       | 0D3h         |

| TIMER STATUS CONTROL REGISTER                | 0D4h         |

| AR TIMER MODE CONTROL REGISTER               | 0D5h         |

| AR TIMER STATUS/CONTROL REGISTER1            | 0D6h         |

| AR TIMER STATUS/CONTROL REGISTER2            | 0D7h         |

| WATCHDOG REGISTER                            | 0D8h         |

| AR TIMER RELOAD/CAPTURE REGISTER             | 0D9h         |

| AR TIMER COMPARE REGISTER                    | 0DAh         |

| AR TIMER LOAD REGISTER                       | 0DRh         |

| OSCILLATOR CONTROL REGISTER                  | 0DCh         |

| MISCELLANEOUS                                | 0DDh         |

| MIGGELLANLOOD                                | 0DDh<br>0DEh |

| RESERVED                                     | 0DEh<br>0DFh |

| SPI DATA REGISTER                            | -            |

|                                              | 0E0h         |

| SPI DIVIDER REGISTER<br>SPI MODE REGISTER    | 0E1h         |

| SPI MODE REGISTER                            | 0E2h         |

| RESERVED                                     | 0E3h         |

|                                              | 0E7h         |

| DATA RAM/EEPROM REGISTER                     | 0E8h*        |

| RESERVED                                     | 0E9h         |

| EEPROM CONTROL REGISTER<br>(except ST62T53C) | 0EAh         |

|                                              | 0EBh         |

| RESERVED                                     | 0FEh         |

| ACCUMULATOR                                  | 0FFh         |

| * WRITE ONLY REGISTER                        | -            |

\* WRITE ONLY REGISTER

#### MEMORY MAP (Cont'd)

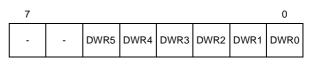

#### 1.3.5 Data Window Register (DWR)

The Data read-only memory window is located from address 0040h to address 007Fh in Data space. It allows direct reading of 64 consecutive bytes located anywhere in program memory, between address 0000h and 0FFFh (top memory address depends on the specific device). All the program memory can therefore be used to store either instructions or read-only data. Indeed, the window can be moved in steps of 64 bytes along the program memory by writing the appropriate code in the Data Window Register (DWR).

The DWR can be addressed like any RAM location in the Data Space, it is however a write-only register and therefore cannot be accessed using singlebit operations. This register is used to position the 64-byte read-only data window (from address 40h to address 7Fh of the Data space) in program memory in 64-byte steps. The effective address of the byte to be read as data in program memory is obtained by concatenating the 6 least significant bits of the register address given in the instruction (as least significant bits) and the content of the DWR register (as most significant bits), as illustrated in Figure 6 below. For instance, when addressing location 0040h of the Data Space, with 0 loaded in the DWR register, the physical location addressed in program memory is 00h. The DWR register is not cleared on reset, therefore it must be written to prior to the first access to the Data readonly memory window area.

#### Data Window Register (DWR)

Address: 0C9h — Write Only

#### Bits 6, 7 = Not used.

Bit 5-0 = **DWR6-DWR0**: *Data read-only memory Window Register Bits.* These are the Data readonly memory Window bits that correspond to the upper bits of the data read-only memory space.

**Caution:** This register is undefined on reset. Neither read nor single bit instructions may be used to address this register.

**Note:** Care is required when handling the DWR register as it is write only. For this reason, the DWR contents should not be changed while executing an interrupt service routine, as the service routine cannot save and then restore the register's previous contents. If it is impossible to avoid writing to the DWR during the interrupt service routine, an image of the register must be saved in a RAM location, and each time the program writes to the DWR, it must also write to the image register. The image register must be written first so that, if an interrupt occurs between the two instructions, the DWR is not affected.

13 12 11 10 9 8 7 6 | 5 4 3 2 1 0 PROGRAM SPACE ADDRESS DATA ROM READ WINDOW REGISTER 6 5 4 3 2 1 0 CONTENTS 5 4 3 2 1 0 DATA SPACE ADDRESS (DWR) 40h-7Fh IN INSTRUCTION Example: 0 0 1 0 0 DWR=28h DATA SPACE ADDRESS 0 0 0 1 1 59h ROM 0 0 0 0 0 0 0 1 1 ADDRESS:A19h VR01573C

Figure 6Data read-only memory Window Memory Addressing

#### MEMORY MAP (Cont'd)

1.3.6 Data RAM/EEPROM Bank Register (DRBR)

Address: E8h — Write only

<u>ا ۲</u>ک

|  | - | DRBR<br>4 | - | - | DRBR<br>1 | DRBR<br>0 |

|--|---|-----------|---|---|-----------|-----------|

|--|---|-----------|---|---|-----------|-----------|

Bit 7-5 = These bits are not used

Bit 4 - DRBR4. This bit, when set, selects RAM Page 2.

Bit 3-2 - Reserved. These bits are not used.

Bit 1 - DRBR1. This bit, when set, selects EEPROM Page 1, when available.

Bit 0 - DRBR0. This bit, when set, selects EEPROM Page 0, when available.

The selection of the bank is made by programming the Data RAM Bank Switch register (DRBR register) located at address E8h of the Data Space according to Table 1. No more than one bank should be set at a time.

The DRBR register can be addressed like a RAM Data Space at the address E8h; nevertheless it is a write only register that cannot be accessed with single-bit operations. This register is used to select the desired 64-byte RAM/EEPROM bank of the Data Space. The bank number has to be loaded in the DRBR register and the instruction has to point

to the selected location as if it was in bank 0 (from 00h address to 3Fh address).

This register is not cleared during the MCU initialization, therefore it must be written before the first access to the Data Space bank region. Refer to the Data Space description for additional information. The DRBR register is not modified when an interrupt or a subroutine occurs.

#### Notes :

Care is required when handling the DRBR register as it is write only. For this reason, it is not allowed to change the DRBR contents while executing interrupt service routine, as the service routine cannot save and then restore its previous content. If it is impossible to avoid the writing of this register in interrupt service routine, an image of this register must be saved in a RAM location, and each time the program writes to DRBR it must write also to the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DRBR is not affected.

In DRBR Register, only 1 bit must be set. Otherwise two or more pages are enabled in parallel, producing errors.

Care must also be taken not to change the E<sup>2</sup>PROM page (when available) when the parallel writing mode is set for the E<sup>2</sup>PROM, as defined in EECTL register.

| DRBR  | ST62T53C ST62T60C/E60C |               | ST62T63C      |  |

|-------|------------------------|---------------|---------------|--|

| 00    | None                   | None          | None          |  |

| 01    | Not Available          | EEPROM Page 0 | EEPROM Page 0 |  |

| 02    | Not Available          | EEPROM Page 1 | Not Available |  |

| 08    | Not Available          | Not Available | Not Available |  |

| 10h   | RAM Page 2             | RAM Page 2    | RAM Page 2    |  |

| other | Reserved               | Reserved      | Reserved      |  |

Table 3Data RAM Bank Register Set-up

#### DIGITAL WATCHDOG (Cont'd)

These instructions test the C bit and Reset the MCU (i.e. disable the Watchdog) if the bit is set (i.e. if the Watchdog is active), thus disabling the Watchdog.

In all modes, a minimum of 28 instructions are executed after activation, before the Watchdog can generate a Reset. Consequently, user software should load the watchdog counter within the first 27 instructions following Watchdog activation (software mode), or within the first 27 instructions executed following a Reset (hardware activation).

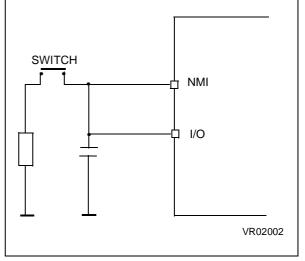

It should be noted that when the GEN bit is low (interrupts disabled), the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

**S**

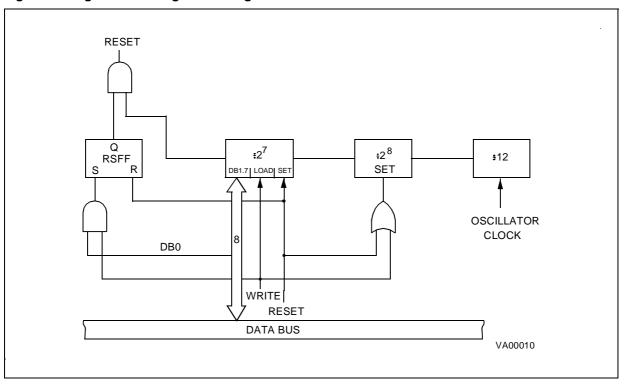

Figure 20. Digital Watchdog Block Diagram

#### INTERRUPTS (Cont'd)

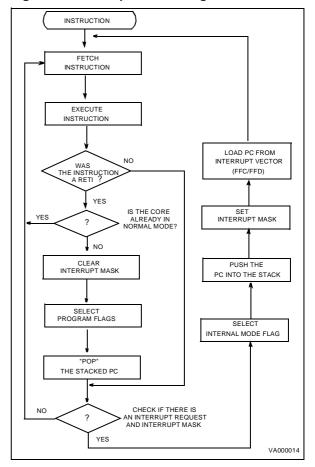

#### 3.4.2 Interrupt Procedure

The interrupt procedure is very similar to a call procedure, indeed the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event, the user cannot know the context and the time at which it occurred. As a result, the user should save all Data space registers which may be used within the interrupt routines. There are separate sets of processor flags for normal, interrupt and non-maskable interrupt modes, which are automatically switched and so do not need to be saved.

The following list summarizes the interrupt procedure:

#### MCU

- The interrupt is detected.

- The C and Z flags are replaced by the interrupt flags (or by the NMI flags).

- The PC contents are stored in the first level of the stack.

- The normal interrupt lines are inhibited (NMI still active).

- The first internal latch is cleared.

- The associated interrupt vector is loaded in the PC.

**WARNING:** In some circumstances, when a maskable interrupt occurs while the ST6 core is in NORMAL mode and especially during the execution of an "ldi IOR, 00h" instruction (disabling all maskable interrupts): if the interrupt arrives during the first 3 cycles of the "ldi" instruction (which is a 4-cycle instruction) the core will switch to interrupt mode BUT the flags CN and ZN will NOT switch to the interrupt pair CI and ZI.

#### User

- User selected registers are saved within the interrupt service routine (normally on a software stack).

- The source of the interrupt is found by polling the interrupt flags (if more than one source is associated with the same vector).

- The interrupt is serviced.

- Return from interrupt (RETI)

### МСИ

Automatically the MCU switches back to the normal flag set (or the interrupt flag set) and pops the previous PC value from the stack.

The interrupt routine usually begins by the identifying the device which generated the interrupt request (by polling). The user should save the registers which are used within the interrupt routine in a software stack. After the RETI instruction is executed, the MCU returns to the main routine.

#### Figure 21. Interrupt Processing Flow Chart

Á7/

#### INTERRUPTS (Cont'd)

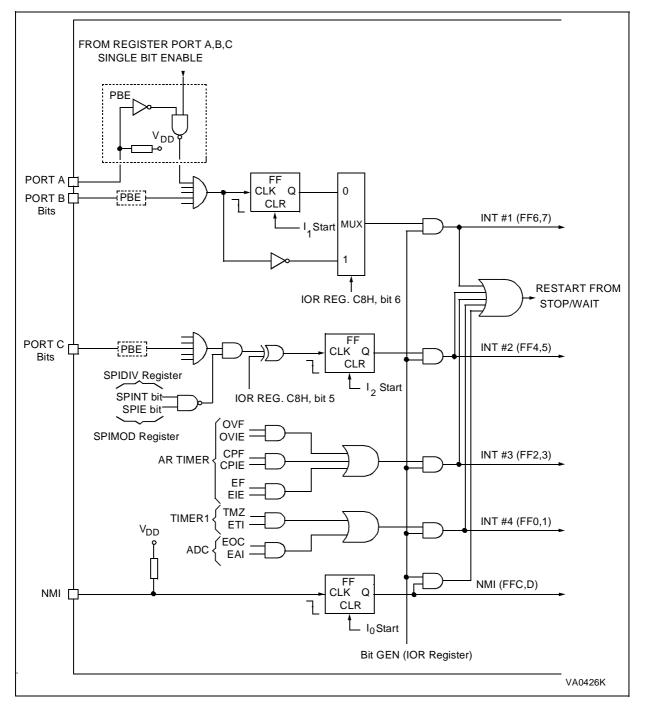

#### Figure 22. Interrupt Block Diagram

57

#### I/O PORTS (Cont'd)

#### 4.1.2 Safe I/O State Switching Sequence

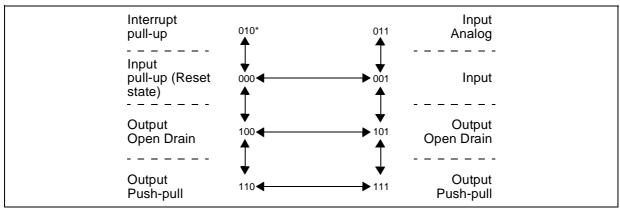

Switching the I/O ports from one state to another should be done in a sequence which ensures that no unwanted side effects can occur. The recommended safe transitions are illustrated in Figure 24. All other transitions are potentially risky and should be avoided when changing the I/O operating mode, as it is most likely that undesirable sideeffects will be experienced, such as spurious interrupt generation or two pins shorted together by the analog multiplexer.

Single bit instructions (SET, RES, INC and DEC) should be used with great caution on Ports Data registers, since these instructions make an implicit read and write back of the entire register. In port input mode, however, the data register reads from the input pins directly, and not from the data register latches. Since data register information in input mode is used to set the characteristics of the input pin (interrupt, pull-up, analog input), these may be unintentionally reprogrammed depending on the state of the input pins. As a general rule, it is better to limit the use of single bit instructions on data registers to when the whole (8-bit) port is in output mode. In the case of inputs or of mixed inputs and

outputs, it is advisable to keep a copy of the data register in RAM. Single bit instructions may then be used on the RAM copy, after which the whole copy register can be written to the port data register:

SET bit, datacopy LD a, datacopy LD DRA, a

**Warning:** Care must also be taken to not use instructions that act on a whole port register (INC, DEC, or read operations) when all 8 bits are not available on the device. Unavailable bits must be masked by software (AND instruction).

The WAIT and STOP instructions allow the ST62xx to be used in situations where low power consumption is needed. The lowest power consumption is achieved by configuring I/Os in input mode with well-defined logic levels.

The user must take care not to switch outputs with heavy loads during the conversion of one of the analog inputs in order to avoid any disturbance to the conversion.

#### Figure 24. Diagram showing Safe I/O State Transitions

Á7/

### I/O PORTS (Cont'd) Table 11I/O Port Option Selections

| MODE                                                  | AVAILABLE ON <sup>(1)</sup>            | SCHEMATIC |  |  |  |  |

|-------------------------------------------------------|----------------------------------------|-----------|--|--|--|--|

| Input                                                 | PA0-PA3<br>PB0-PB3, PB6-PB7<br>PC2-PC4 | Data in   |  |  |  |  |

| Input<br>with pull up                                 | PA0-PA3<br>PB0-PB3, PB6-PB7<br>PC2-PC4 | Data in   |  |  |  |  |

| Input<br>with pull up<br>with interrupt               | PA0-PA3<br>PB0-PB3, PB6-PB7<br>PC2-PC4 | Data in   |  |  |  |  |

| Analog Input                                          | PA0-PA3<br>PC2-PC4                     | ADC       |  |  |  |  |

| Open drain output<br>5mA<br>Open drain output<br>30mA | PA0-PA3<br>PC2-PC4<br>PB0-PB3, PB6-PB7 | Data out  |  |  |  |  |

| Push-pull output<br>5mA<br>Push-pull output<br>30mA   | PA0-PA3<br>PC2-PC4<br>PB0-PB3, PB6-PB7 | Data out  |  |  |  |  |

**Note 1.** Provided the correct configuration has been selected.

TIMER (Cont'd)

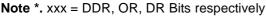

#### 4.2.1 Timer Operation

The Timer prescaler is clocked by the prescaler clock input ( $f_{INT} \div 12$ ).

The user can select the desired prescaler division ratio through the PS2, PS1, PS0 bits. When the TCR count reaches 0, it sets the TMZ bit in the TSCR. The TMZ bit can be tested under program control to perform a timer function whenever it goes high.

### 4.2.2 Timer Interrupt

When the counter register decrements to zero with the ETI (Enable Timer Interrupt) bit set to one, an interrupt request associated with Interrupt Vector #4 is generated. When the counter decrements to zero, the TMZ bit in the TSCR register is set to one.

#### 4.2.3 Application Notes

TMZ is set when the counter reaches zero; however, it may also be set by writing 00h in the TCR register or by setting bit 7 of the TSCR register. The TMZ bit must be cleared by user software when servicing the timer interrupt to avoid undesired interrupts when leaving the interrupt service routine. After reset, the 8-bit counter register is loaded with 0FFh, while the 7-bit prescaler is loaded with 07Fh, and the TSCR register is cleared. This means that the Timer is stopped (PSI="0") and the timer interrupt is disabled.

**۲/**

#### Figure 27. Timer Working Principle

### AUTO-RELOAD TIMER (Cont'd)

57

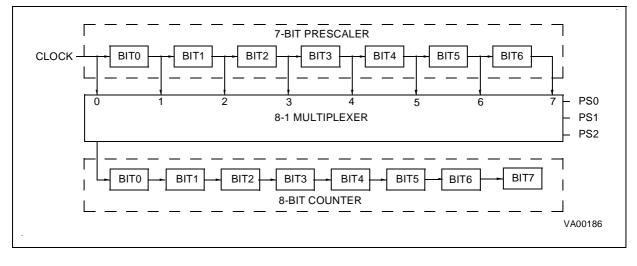

### Figure 28. AR Timer Block Diagram

#### AUTO-RELOAD TIMER (Cont'd)

**Capture Mode with PWM Generation**. In this mode, the AR counter operates as a free running 8-bit counter fed by the prescaler output. The counter is incremented on every clock rising edge.

An 8-bit capture operation from the counter to the ARRC register is performed on every active edge on the ARTIMin pin, when enabled by Edge Control bits SL0, SL1 in the ARSC1 register. At the same time, the External Flag, EF, in the ARSC0 register is set and an external interrupt request is generated if the External Interrupt Enable bit, EIE, in the ARMC register, is set. The EF flag must be reset by user software.

Each ARTC overflow sets ARTIMout, while a match between the counter and ARCP (Compare Register) resets ARTIMout and sets the compare flag, CPF. A compare interrupt request is generated if the related compare interrupt enable bit, CPIE, is set. A PWM signal is generated on ARTI-Mout. The CPF flag must be reset by user software.

The frequency of the generated signal is determined by the prescaler setting. The duty cycle is determined by the ARCP register.

Initialization and reading of the counter are identical to the auto-reload mode (see previous description).

Enabling and selection of clock sources is controlled by the CC0 and CC1 bits in the AR Status Control Register, ARSC1.

The prescaler division ratio is selected by programming the PS0, PS1 and PS2 bits in the ARSC1 Register.

In Capture mode, the allowed clock sources are the internal clock and the internal clock divided by 3; the external ARTIMin input pin should not be used as a clock source.

Capture Mode with Reset of counter and prescaler, and PWM Generation. This mode is identical to the previous one, with the difference that a capture condition also resets the counter and the prescaler, thus allowing easy measurement of the time between two captures (for input period measurement on the ARTIMin pin).

**Load on External Input**. The counter operates as a free running 8-bit counter fed by the prescaler.

the count is incremented on every clock rising edge.

Each counter overflow sets the ARTIMout pin. A match between the counter and ARCP (Compare Register) resets the ARTIMout pin and sets the compare flag, CPF. A compare interrupt request is generated if the related compare interrupt enable bit, CPIE, is set. A PWM signal is generated on ARTIMout. The CPF flag must be reset by user software.

Initialization of the counter is as described in the previous paragraph. In addition, if the external AR-TIMin input is enabled, an active edge on the input pin will copy the contents of the ARRC register into the counter, whether the counter is running or not.

#### Notes:

The allowed AR Timer clock sources are the following:

| AR Timer Mode      | Clock Sources                                   |

|--------------------|-------------------------------------------------|

| Auto-reload mode   | f <sub>INT</sub> , f <sub>INT/3</sub> , ARTIMin |

| Capture mode       | f <sub>INT</sub> , f <sub>INT/3</sub>           |

| Capture/Reset mode | f <sub>INT</sub> , f <sub>INT/3</sub>           |

| External Load mode | f <sub>INT</sub> , f <sub>INT/3</sub>           |

The clock frequency should not be modified while the counter is counting, since the counter may be set to an unpredictable value. For instance, the multiplexer setting should not be modified while the counter is counting.

Loading of the counter by any means (by auto-reload, through ARLR, ARRC or by the Core) resets the prescaler at the same time.

Care should be taken when both the Capture interrupt and the Overflow interrupt are used. Capture and overflow are asynchronous. If the capture occurs when the Overflow Interrupt Flag, OVF, is high (between counter overflow and the flag being reset by software, in the interrupt routine), the External Interrupt Flag, EF, may be cleared simultaneusly without the interrupt being taken into account.

The solution consists in resetting the OVF flag by writing 06h in the ARSC0 register. The value of EF is not affected by this operation. If an interrupt has occured, it will be processed when the MCU exits from the interrupt routine (the second interrupt is latched).

57

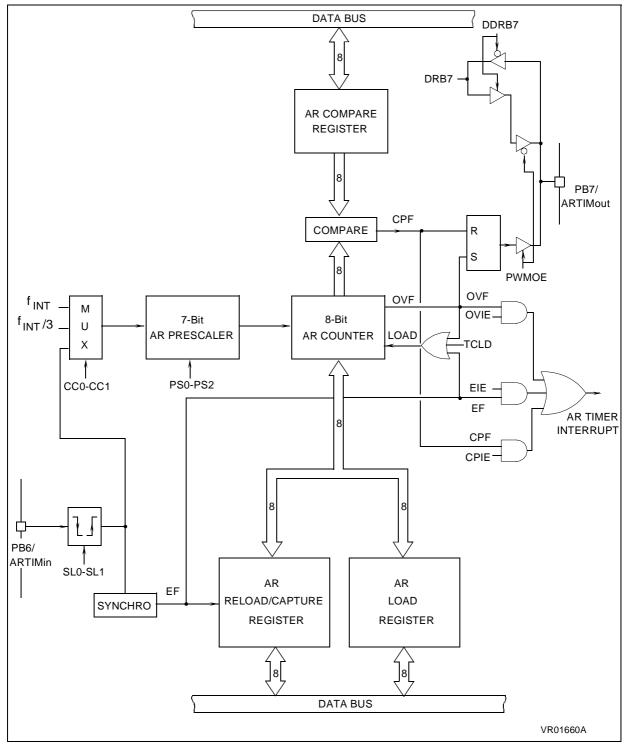

#### 4.5 SERIAL PERIPHERAL INTERFACE (SPI)

The SPI peripheral is an optimized synchronous serial interface with programmable transmission modes and master/slave capabilities supporting a wide range of industry standard SPI specifications. The SPI interface may also implement asynchronous data transfer, in which case processor overhead is limited to data transfer from or to the shift register on an interrupt driven basis.

The SPI may be controlled by simple user software to perform serial data exchange with lowcost external memory, or with serially controlled peripherals to drive displays, motors or relays.

The SPI's shift register is simultaneously fed by the Sin pin and feeds the Sout pin, thus transmission and reception are essentially the same process. Suitable setting of the number of bits in the data frame can allow filtering of unwanted leading data bits in the incoming data stream.

The SPI comprises an 8-bit Data/Shift Register, DSR, a Divide register, DIV, a Mode Control Register MOD, and a Miscellaneous register, MISCR.

The SPI may be operated either in Master mode or in Slave mode.

Master mode is defined by the synchronous serial clock being supplied by the MCU, by suitably programming the clock divider (DIV register). Slave mode is defined by the serial clock being supplied externally on the SCK pin by the external Master device.

For maximum versatility the SPI may be programmed to sample data either on the rising or on the falling edge of SCK, with or without phase shift (clock Polarity and Phase selection).

The Sin, Sout and SCK signals are connected as alternate I/O pin functions.

For serial input operation, Sin must be configured as an input. For serial output operation, Sout is selected as an output by programming Bit 0 of the Miscellaneous Register: clearing this bit will set the pin as a standard I/O line, while setting the bit will select the Sout function.

An interrupt request may be associated with the end of a transmission or reception cycle; this is defined by programming the number of bits in the data frame and by enabling the interrupt. This request is associated with interrupt vector #2, and can be masked by programming the SPIE bit of the MOD register. Since the SPI interrupt is "ORed" with the port interrupt source, an interrupt flag bit is available in the DIV register allowing discrimination of the interrupt request.

<u>ل</u>رک

Figure 31. SPI Block Diagram

### SERIAL PERIPHERAL INTERFACE SPI (Cont'd) SPI DIV Register (DIV)

Address: E1h — Read/Write Reset status: 00h

| 7     |      |      |      |      |     |     | 0   |

|-------|------|------|------|------|-----|-----|-----|

| SPINT | DOV6 | DIV5 | DIV4 | DIV3 | CD2 | CD1 | CD0 |

The SPIDIV register defines the transmission rate and frame format and contains the interrupt flag.

Bits CD0-CD2, DIV3-DIV6 are read/write while SPINT can be read and cleared only. Write access is not allowed if SPRUN in the MOD register is set.

Bit 7 = **SPINT**: Interrupt Flag. If SPIE bit=1, SPINT is automatically set to one by the SPI at the end of a transmission or reception and an interrupt request can be generated depending on the state of the interrupt mask bit in the MOD control register. This bit is write and read and must be cleared by user software at the end of the interrupt service routine.

Bit 6-3 = **DIV6-DIV3**: Burst Mode Bit Clock Period Selection. Define the number of shift register bits that are transmitted or received in a frame. The available selections are listed in Table 16. The normal maximum setting is 8 bits, since the shift register is 8 bits wide. Note that by setting a greater number of bits, in conjunction with the SPIN bit in the MOD register, unwanted data bits may be filtered from the data stream.

Bit 2-0 = **CD2-CD0**: Base/Bit Clock Rate Selection. Define the division ratio between the core clock ( $f_{INT}$  divided by 13) and the clock supplied to the Shift Register in Master mode.

Table 15. Base/Bit Clock Ratio Selection

|   | CD2-C | D0 | Divide Ratio (decimal) |

|---|-------|----|------------------------|

| 0 | 0     | 0  | Divide by 1            |

| 0 | 0     | 1  | Divide by 2            |

| 0 | 1     | 0  | Divide by 4            |

| 0 | 1     | 1  | Divide by 8            |

| 1 | 0     | 0  | Divide by 16           |

| 1 | 0     | 1  | Divide by 32           |

| 1 | 1     | 0  | Divide by 64           |

| 1 | 1     | 1  | Divide by 256          |

**Note:** For example, when an 8MHz CPU clock is used, asynchronous operation at 9600 Baud is possible (8MHz/13/64). Other Baud rates are available by proportionally selecting division factors depending on CPU clock frequency.

Data setup time on Sin is typically 250ns min, while data hold time is typically 50ns min.

|   | DIV | 6-DIV3 | 3 | Number of bits sent       |  |  |  |  |  |  |

|---|-----|--------|---|---------------------------|--|--|--|--|--|--|

| 0 | 0   | 0      | 0 | Reserved (not to be used) |  |  |  |  |  |  |

| 0 | 0   | 0      | 1 | 1                         |  |  |  |  |  |  |

| 0 | 0   | 1      | 0 | 2                         |  |  |  |  |  |  |

| 0 | 0   | 1      | 1 | 3                         |  |  |  |  |  |  |

| 0 | 1   | 0      | 0 | 4                         |  |  |  |  |  |  |

| 0 | 1   | 0      | 1 | 5                         |  |  |  |  |  |  |

| 0 | 1   | 1      | 0 | 6                         |  |  |  |  |  |  |

| 0 | 1   | 1      | 1 | 7                         |  |  |  |  |  |  |

| 1 | 0   | 0      | 0 | 8                         |  |  |  |  |  |  |

| 1 | 0   | 0      | 1 | 9)                        |  |  |  |  |  |  |

| 1 | 0   | 1      | 0 | 10                        |  |  |  |  |  |  |

| 1 | 0   | 1      | 1 | 11 Refer to the           |  |  |  |  |  |  |

| 1 | 1   | 0      | 0 | 12   description of the   |  |  |  |  |  |  |

| 1 | 1   | 0      | 1 | 13   DIV6-DIV3 bits in    |  |  |  |  |  |  |

| 1 | 1   | 1      | 0 | 14   the DIV Register     |  |  |  |  |  |  |

| 1 | 1   | 1      | 1 | 15 <i>J</i>               |  |  |  |  |  |  |

### SPI Data/Shift Register (SPIDSR)

Address: E0h — Read/Write Reset status: XXh

| 7  |    |    |    |    |    |    |    |  |  |  |

|----|----|----|----|----|----|----|----|--|--|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

SPIDSR is read/write, however write access is not allowed if the SPRUN bit of Mode Control register is set to one.

Data is sampled into SPDSR on the SCK edge determined by the CPOL and CPHA bits. The affect of these setting is shown in the following diagrams.

The Shift Register transmits and receives the Most Significant Bit first.

Bit 7-0 = **DSR7-DSR0**: *Data Bits.* These are the SPI shift register data bits.

#### Miscellaneous Register (MISCR)

Address: DDh — Write only

Reset status: xxxxxxb

| 7 |   |   |   |   |   |   | 0  |  |

|---|---|---|---|---|---|---|----|--|

| - | - | - | - | - | - | - | D0 |  |

#### Bit 7-1 = **D7-D1**: *Reserved*.

Bit 0 = D0: *Bit 0.* This bit, when set, selects the Sout pin as the SPI output line. When this bit is cleared, Sout acts as a standard I/O line.

### ST62T53C/T60C/T63C ST62E60C

#### Opcode Map Summary (Continued)

| LOW       | -        | _           |   |           |     |   | _           |     | _            |   | -        |            |   | _          |   | _          |              | _          | LOW       |

|-----------|----------|-------------|---|-----------|-----|---|-------------|-----|--------------|---|----------|------------|---|------------|---|------------|--------------|------------|-----------|

| н         |          | 8<br>1000   |   | 9<br>1001 |     |   | A<br>1010   |     | В<br>1011    |   | C<br>110 | 0          |   | D<br>1101  |   | Е<br>1110  |              | F<br>1111  | н         |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        | 4 | LDI        | 2 | JRC        | 4            | LD         |           |

| 0<br>0000 |          | е           |   | abc       |     |   | е           |     | b0,rr        |   | е        |            |   | rr,nn      |   | е          |              | a,(y)      | 0<br>0000 |

| 0000      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 3 | imm        | 1 | prc        | 1            | ind        | 0000      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | DEC        | 2 | JRC        | 4            | LD         | -         |

| 1<br>0001 |          | е           |   | abc       |     |   | е           |     | b0,rr        |   | е        |            |   | х          |   | е          |              | a,rr       | 1<br>0001 |

| 0001      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | sd         | 1 | prc        | 2            | dir        | 0001      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        | 4 | COM        | 2 | JRC        | 4            | CP         |           |

| 2         |          | е           |   | abc       |     |   | е           |     | b4,rr        |   | е        |            |   | а          |   | е          |              | a,(y)      | 2         |

| 0010      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        |   |            | 1 | prc        | 1            | ind        | 0010      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | LD         | 2 | JRC        | 4            | CP         |           |

| 3         |          | е           |   | abc       | -   |   | е           |     | b4,rr        | е |          | -          |   | x,a        |   | е          |              | a,rr       | 3         |

| 0011      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | sd         | 1 | prc        | 2            | dir        | 0011      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        | 2 | RETI       | 2 | JRC        | 4            | ADD        |           |

| 4         | -        | e           | • | abc       | 01  | - | e           | · · | b2,rr        | - | е        | 0112       | - | 11211      | - | e          | · ·          | a,(y)      | 4         |

| 0100      | 1        | pcr         | 2 | ubo       | ext | 1 | pcr         | 2   | b.d          | 1 | Ŭ        | pcr        | 1 | inh        | 1 | prc        | 1            | ind        | 0100      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | DEC        | 2 | JRC        | 4            | ADD        |           |

| 5         | 2        | e           | 4 | abc       | JF  | 2 | e           | 4   | b2,rr        | 2 | е        | JI         | 4 | y DEC      | 2 | e          | 4            | a,rr       | 5         |

| 0101      | 1        |             | 2 | auc       | ext | 1 | -           | 2   | b2,11<br>b.d | 1 | e        | nor        | 1 |            | 1 |            | 2            | a,n<br>dir | 0101      |

|           | 2        | pcr<br>JRNZ |   |           | JP  | 2 | pcr<br>JRNC | 2   | RES          | 2 |          | pcr<br>JRZ | 1 | sd<br>STOP | 1 | prc<br>JRC |              | INC        |           |

| 6         | 2        |             | 4 |           | JP  | 2 |             | 4   |              | 2 |          | JRZ        | 2 | 510P       | 2 |            | 4            |            | 6         |

| 0110      |          | е           | ~ | abc       |     |   | е           |     | b6,rr        |   | е        |            |   | I.         |   | е          |              | (y)        | 0110      |

|           | 1        | pcr         | 2 |           | ext |   | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | inh        | 1 | prc        | -            | ind        |           |

| 7         | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | LD         | 2 | JRC        | 4            | INC        | 7         |

| 0111      |          | е           | _ | abc       |     |   | е           | _   | b6,rr        |   | е        |            |   | y,a        |   | е          | _            | rr         | 0111      |

|           | 1        | pcr         | 2 |           | ext |   | pcr         | 2   | b.d          |   |          | pcr        | 1 | sd         | 1 | prc        | _            | dir        |           |

| 8         | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        |   |            | 2 | JRC        | 4            | LD         | 8         |

| 1000      |          | е           |   | abc       |     |   | е           |     | b1,rr        |   | е        |            |   | #          |   | е          |              | (y),a      | 1000      |

|           | 1        | pcr         | 2 |           | ext |   | pcr         | 2   | b.d          | 1 |          | pcr        |   |            | 1 | prc        | 1            | ind        |           |

| 9         | 2        | RNZ         | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | DEC        | 2 | JRC        | 4            | LD         | 9         |

| 1001      |          | е           |   | abc       |     |   | е           |     | b1,rr        |   | е        |            |   | v          |   | е          |              | rr,a       | 1001      |

|           | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | sd         | 1 | prc        | 2            | dir        |           |

| •         | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        | 4 | RCL        | 2 | JRC        | 4            | AND        |           |

| A<br>1010 |          | е           |   | abc       |     |   | е           |     | b5,rr        |   | е        |            |   | а          |   | е          |              | a,(y)      | A<br>1010 |

| 1010      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | inh        | 1 | prc        | 1            | ind        | 1010      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | LD         | 2 | JRC        | 4            | AND        | -         |

| В<br>1011 |          | е           |   | abc       |     |   | е           |     | b5,rr        |   | е        |            |   | v,a        |   | е          |              | a,rr       | В<br>1011 |

|           | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | sd         | 1 | prc        | 2            | dir        |           |

| •         | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          | 2 |          | JRZ        | 2 | RET        | 2 | JRC        | 4            | SUB        | -         |

| C<br>1100 |          | е           |   | abc       |     |   | е           |     | b3,rr        |   | е        |            |   |            |   | е          |              | a,(y)      | C<br>1100 |

| 1100      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 |          | pcr        | 1 | inh        | 1 | prc        | 1            | ind        | 1100      |

| _         | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | DEC        | 2 | JRC        | 4            | SUB        |           |

| D         |          | е           |   | abc       |     |   | е           |     | b3,rr        |   | е        |            |   | W          |   | е          |              | a,rr       | D         |

| 1101      | 1        | pcr         | 2 |           | ext | 1 | pcr         | 2   | b.d          | 1 | -        | pcr        | 1 | sd         | 1 | prc        | 2            | dir        | 1101      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | RES          |   |          | JRZ        | 2 | WAIT       | 2 | JRC        | 4            | DEC        |           |

| E         | -        | e           | • | abc       |     | - | e           | ·   | b7,rr        | - | е        |            | - |            | - | e          | <sup>.</sup> | (y)        | E         |

| 1110      | 1        | pcr         | 2 | 400       | ext | 1 | pcr         | 2   | b.d          | 1 | U        | pcr        | 1 | inh        | 1 | prc        | 1            | ind        | 1110      |

|           | 2        | JRNZ        | 4 |           | JP  | 2 | JRNC        | 4   | SET          | 2 |          | JRZ        | 4 | LD         | 2 | JRC        | 4            | DEC        |           |

| F         | <b>–</b> | e           | + | abc       | JF  | - | e           | 1   | b7,rr        | 2 | е        |            | + | w,a        | 2 | e          | 1            | rr         | F         |

| 1111      | 1        | e<br>pcr    | 2 | auc       | ext | 1 |             | 2   | b.d          | 1 | е        | nor        | 1 | w,a<br>sd  | 1 |            | 2            | dir        | 1111      |

|           | 1        | per         | 2 |           | EXI | 1 | pcr         | 2   | D.0          |   |          | pcr        | 1 | 50         |   | prc        | 2            | ulf        |           |

#### Abbreviations for Addressing Modes: Legend:

- Direct Short Direct dir sd imm Immediate inh Inherent Extended ext b.d Bit Direct Bit Test

- Indicates Illegal Instructions 5 Bit Displacement 3 Bit Address #

- е b

rr

- 1byte dataspace address 1 byte immediate data 12 bit address nn

- abc

- 8 bit Displacement ee

- bt pcr ind Program Counter Relative

- Indirect

Cycle Mnemonic 2 JRC Operand е 1 prc Bytes Addressing Mode

64/84

## **6 ELECTRICAL CHARACTERISTICS**

#### **6.1 ABSOLUTE MAXIMUM RATINGS**

This product contains devices to protect the inputs against damage due to high static voltages, however it is advisable to take normal precaution to avoid application of any voltage higher than the specified maximum rated voltages.

For proper operation it is recommended that  $V_I$  and  $V_O$  be higher than  $V_{SS}$  and lower than  $V_{DD}$ . Reliability is enhanced if unused inputs are connected to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ).

**Power Considerations**. The average chip-junction temperature, Tj, in Celsius can be obtained from:

Tj=TA + PD x RthJA

Where:TA = Ambient Temperature.

RthJA =Package thermal resistance (junction-to ambient).

PD = Pint + Pport.

Pint =IDD x VDD (chip internal power).

Pport =Port power dissipation (determined by the user).

| Symbol           | Parameter                                   | Value                                                         | Unit |

|------------------|---------------------------------------------|---------------------------------------------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                              | -0.3 to 7.0                                                   | V    |

| VI               | Input Voltage                               | V <sub>SS</sub> - 0.3 to V <sub>DD</sub> + 0.3 <sup>(1)</sup> | V    |

| Vo               | Output Voltage                              | V <sub>SS</sub> - 0.3 to V <sub>DD</sub> + 0.3 <sup>(1)</sup> | V    |

| IV <sub>DD</sub> | Total Current into V <sub>DD</sub> (source) | 80                                                            | mA   |

| IV <sub>SS</sub> | Total Current out of V <sub>SS</sub> (sink) | 100                                                           | mA   |

| Tj               | Junction Temperature                        | 150                                                           | °C   |

| T <sub>STG</sub> | Storage Temperature                         | -60 to 150                                                    | °C   |

Notes:

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- (1) Within these limits, clamping diodes are guarantee to be not conductive. Voltages outside these limits are authorised as long as injection current is kept within the specification.

### DC ELECTRICAL CHARACTERISTICS (Cont'd)

$(T_A = -40 \text{ to } +85^{\circ}\text{C} \text{ unless otherwise specified}))$

| Symbol          | Parameter                                                        | Test Conditions                                                                                                                                                                                         | Min.                   | Min. Typ. Max. |                          | Unit |  |

|-----------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|--------------------------|------|--|

| V <sub>up</sub> | LVD Threshold in power-on                                        |                                                                                                                                                                                                         | V <sub>dn</sub> +50 mV | 4.1            | 4.3                      | V    |  |

| V <sub>dn</sub> | LVD threshold in powerdown                                       |                                                                                                                                                                                                         | 3.6                    | 3.8            | V <sub>up</sub> -50 mV   | V    |  |

|                 | Low Level Output Voltage<br>All Output pins                      | $V_{DD}$ = 5.0V; $I_{OL}$ = +10µA<br>$V_{DD}$ = 5.0V; $I_{OL}$ = + 5mA<br>$V_{DD}$ = 5.0V; $I_{OL}$ = + 10mAv                                                                                           |                        |                | 0.1<br>0.8<br>1.2        |      |  |

| V <sub>OL</sub> | Low Level Output Voltage<br>30 mA Sink I/O pins                  | $ \begin{array}{l} V_{DD}{=}\;5.0V; \ I_{OL}{=}\;{+}10\mu A \\ V_{DD}{=}\;5.0V; \ I_{OL}{=}\;{+}10m A \\ V_{DD}{=}\;5.0V; \ I_{OL}{=}\;{+}20m A \\ V_{DD}{=}\;5.0V; \ I_{OL}{=}\;{+}30m A \end{array} $ |                        |                | 0.1<br>0.8<br>1.3<br>2.0 | V    |  |

| V <sub>OH</sub> | High Level Output Voltage<br>All Output pins                     | V <sub>DD</sub> = 5.0V; I <sub>OH</sub> = -10µA<br>V <sub>DD</sub> = 5.0V; I <sub>OH</sub> = -5.0mA                                                                                                     | 4.9<br>3.5             |                |                          | V    |  |

| I <sub>DD</sub> | Supply Current in STOP<br>Mode, with LVD disabled <sup>(*)</sup> | I <sub>LOAD</sub> =0mA<br>V <sub>DD</sub> =5.0V                                                                                                                                                         |                        |                | 10                       | μΑ   |  |

Note:

(\*) All Peripherals in stand-by.

### **6.4 AC ELECTRICAL CHARACTERISTICS**

$(T_A = -40 \text{ to } +125^{\circ}\text{C} \text{ unless otherwise specified})$

| Symbol            | Parameter                                                                    | Test Conditions                                                                            |                          | Unit                     |                        |                                 |

|-------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------|--------------------------|------------------------|---------------------------------|

| Symbol            | Parameter                                                                    | Test Conditions                                                                            | Min.                     | Тур.                     | Max.                   | Unit                            |

| t <sub>REC</sub>  | Supply Recovery Time <sup>(1)</sup>                                          |                                                                                            | 100                      |                          |                        | ms                              |

| T <sub>WEE</sub>  | EEPROM Write Time                                                            | $ \begin{array}{l} T_A = 25^\circ C \\ T_A = 85^\circ C \\ T_A = 125^\circ C \end{array} $ |                          | 5<br>10<br>20            | 10<br>20<br>30         | ms                              |

| Endurance<br>(2)  | EEPROM WRITE/ERASE Cycle                                                     | Q <sub>A</sub> L <sub>OT</sub> Acceptance (25°C)                                           | 300,000                  | 1 million                |                        | cycles                          |

| Retention         | EEPROM Data Retention                                                        | T <sub>A</sub> = 55°C                                                                      | 10                       |                          |                        | years                           |

| f <sub>LFAO</sub> | Internal frequency with LFAO active                                          |                                                                                            | 200                      | 400                      | 800                    | kHz                             |

| f <sub>OSG</sub>  | Internal Frequency with OSG enabled <sup>2)</sup>                            | $V_{DD} = 3V$<br>$V_{DD} = 3.6V$<br>$V_{DD} = 4.5V$<br>$V_{DD} = 6V$                       | 1<br>1<br>2<br>2         |                          | f <sub>OSC</sub>       | MHz                             |

|                   | Internal frequency with PC oscilla                                           | VDD=5.0V (Except 626xB ROM)<br>R=47kΩ<br>R=100kΩ<br>R=470kΩ                                | 4<br>2.7<br>800          | 5<br>3.2<br>850          | 5.8<br>3.5<br>900      | MHz<br>MHz<br>kHz               |

| f <sub>RC</sub>   | Internal frequency with RC oscilla-<br>tor and OSG disabled <sup>2) 3)</sup> | VDD=5.0V (626xB ROM)<br>R=10kΩ<br>R=27kΩ<br>R=67kΩ<br>R=100kΩ                              | 6.3<br>4.7<br>2.8<br>2.2 | 8.2<br>5.9<br>3.6<br>2.8 | 9.8<br>7<br>4.3<br>3.4 | MHz<br>MHz<br>MHz<br>MHz<br>MHz |

| C <sub>IN</sub>   | Input Capacitance                                                            | All Inputs Pins                                                                            |                          |                          | 10                     | pF                              |

| C <sub>OUT</sub>  | Output Capacitance                                                           | All Outputs Pins                                                                           |                          |                          | 10                     | pF                              |

Notes: 1. Period for which  $V_{DD}$  has to be connected at 0V to allow internal Reset function at next power-up.

3. Measure performed with OSCin pin soldered on PCB, with an around 2pF equivalent capacitance.

<sup>2</sup> An oscillator frequency above 1MHz is recommended for reliable A/D results.

### ST62T53C/T60C/T63C ST62E60C

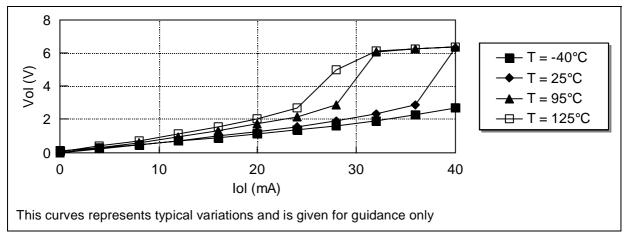

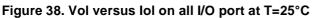

Figure 37. Vol versus IoI on all I/O port at Vdd=5V

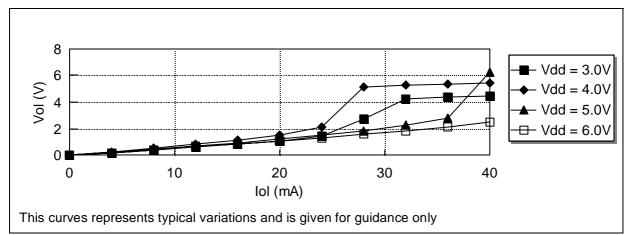

Figure 39. Vol versus lol for High sink (30mA) I/Oports at T=25°C

Notes:

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

©2001 STMicroelectronics - All Rights Reserved.

Purchase of I<sup>2</sup>C Components by STMicroelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

STMicroelectronics Group of Companies

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com