# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                           |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | SPI                                                                |

| Peripherals                | LED, LVD, POR, WDT                                                 |

| Number of I/O              | 13                                                                 |

| Program Memory Size        | 3.8KB (3.8K x 8)                                                   |

| Program Memory Type        | ОТР                                                                |

| EEPROM Size                | 128 x 8                                                            |

| RAM Size                   | 128 x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | A/D 7x8b                                                           |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                     |

| Supplier Device Package    | 20-50                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t60cm3 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MEMORY MAP (Cont'd)

# 1.3.5 Data Window Register (DWR)

The Data read-only memory window is located from address 0040h to address 007Fh in Data space. It allows direct reading of 64 consecutive bytes located anywhere in program memory, between address 0000h and 0FFFh (top memory address depends on the specific device). All the program memory can therefore be used to store either instructions or read-only data. Indeed, the window can be moved in steps of 64 bytes along the program memory by writing the appropriate code in the Data Window Register (DWR).

The DWR can be addressed like any RAM location in the Data Space, it is however a write-only register and therefore cannot be accessed using singlebit operations. This register is used to position the 64-byte read-only data window (from address 40h to address 7Fh of the Data space) in program memory in 64-byte steps. The effective address of the byte to be read as data in program memory is obtained by concatenating the 6 least significant bits of the register address given in the instruction (as least significant bits) and the content of the DWR register (as most significant bits), as illustrated in Figure 6 below. For instance, when addressing location 0040h of the Data Space, with 0 loaded in the DWR register, the physical location addressed in program memory is 00h. The DWR register is not cleared on reset, therefore it must be written to prior to the first access to the Data readonly memory window area.

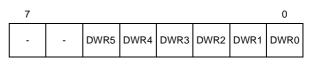

# Data Window Register (DWR)

Address: 0C9h — Write Only

# Bits 6, 7 = Not used.

Bit 5-0 = **DWR6-DWR0**: *Data read-only memory Window Register Bits.* These are the Data readonly memory Window bits that correspond to the upper bits of the data read-only memory space.

**Caution:** This register is undefined on reset. Neither read nor single bit instructions may be used to address this register.

**Note:** Care is required when handling the DWR register as it is write only. For this reason, the DWR contents should not be changed while executing an interrupt service routine, as the service routine cannot save and then restore the register's previous contents. If it is impossible to avoid writing to the DWR during the interrupt service routine, an image of the register must be saved in a RAM location, and each time the program writes to the DWR, it must also write to the image register. The image register must be written first so that, if an interrupt occurs between the two instructions, the DWR is not affected.

13 12 11 10 9 8 7 6 | 5 4 3 2 1 0 PROGRAM SPACE ADDRESS DATA ROM READ WINDOW REGISTER 6 5 4 3 2 1 0 CONTENTS 5 4 3 2 1 0 DATA SPACE ADDRESS (DWR) 40h-7Fh IN INSTRUCTION Example: 0 0 1 0 0 DWR=28h DATA SPACE ADDRESS 0 0 0 1 1 59h ROM 0 0 0 0 0 0 0 1 1 ADDRESS:A19h VR01573C

Figure 6Data read-only memory Window Memory Addressing

# CPU REGISTERS (Cont'd)

However, if the program space contains more than 4096 bytes, the additional memory in program space can be addressed by using the Program Bank Switch register.

The PC value is incremented after reading the address of the current instruction. To execute relative jumps, the PC and the offset are shifted through the ALU, where they are added; the result is then shifted back into the PC. The program counter can be changed in the following ways:

- JP (Jump) instructionPC=Jump address

- CALL instructionPC= Call address

- Relative Branch Instruction.PC= PC +/- offset

- Interrupt PC=Interrupt vector

- Reset PC= Reset vector

- RET & RETI instructionsPC= Pop (stack)

- Normal instructionPC= PC + 1

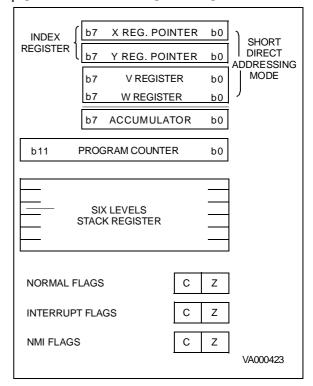

**Flags (C, Z)**. The ST6 CPU includes three pairs of flags (Carry and Zero), each pair being associated with one of the three normal modes of operation: Normal mode, Interrupt mode and Non Maskable Interrupt mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during Normal operation, another pair is used during Interrupt mode (CI, ZI), and a third pair is used in the Non Maskable Interrupt mode (CNMI, ZN-MI).

The ST6 CPU uses the pair of flags associated with the current mode: as soon as an interrupt (or a Non Maskable Interrupt) is generated, the ST6 CPU uses the Interrupt flags (resp. the NMI flags) instead of the Normal flags. When the RETI instruction is executed, the previously used set of flags is restored. It should be noted that each flag set can only be addressed in its own context (Non Maskable Interrupt, Normal Interrupt or Main routine). The flags are not cleared during context switching and thus retain their status.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations; otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction; it also participates in the rotate left instruction.

The Zero flag is set if the result of the last arithmetic or logical operation was equal to zero; otherwise it is cleared.

Switching between the three sets of flags is performed automatically when an NMI, an interrupt or a RETI instructions occurs. As the NMI mode is automatically selected after the reset of the MCU, the ST6 core uses at first the NMI flags.

Stack. The ST6 CPU includes a true LIFO hardware stack which eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level are shifted into the next higher level, while the content of the PC is shifted into the first level (the original contents of the sixth stack level are lost). When a subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is popped back into the previous level. Since the accumulator, in common with all other data space registers, is not stored in this stack, management of these registers should be performed within the subroutine. The stack will remain in its "deepest" position if more than 6 nested calls or interrupts are executed, and consequently the last return address will be lost. It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

# Figure 8. ST6 CPU Programming Mode

# **3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES**

# 3.1 CLOCK SYSTEM

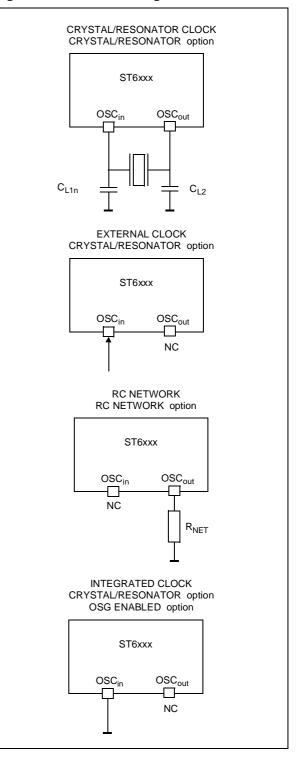

The MCU features a Main Oscillator which can be driven by an external clock, or used in conjunction with an AT-cut parallel resonant crystal or a suitable ceramic resonator, or with an external resistor ( $R_{NET}$ ). In addition, a Low Frequency Auxiliary Oscillator (LFAO) can be switched in for security reasons, to reduce power consumption, or to offer the benefits of a back-up clock system.

The Oscillator Safeguard (OSG) option filters spikes from the oscillator lines, provides access to the LFAO to provide a backup oscillator in the event of main oscillator failure and also automatically limits the internal clock frequency ( $f_{INT}$ ) as a function of V<sub>DD</sub>, in order to guarantee correct operation. These functions are illustrated in Figure 10, Figure 11, Figure 12 and Figure 13.

A programmable divider on  $F_{\rm INT}$  is also provided in order to adjust the internal clock of the MCU to the best power consumption and performance trade-off.

Figure 9 illustrates various possible oscillator configurations using an external crystal or ceramic resonator, an external clock input, an external resistor ( $R_{NET}$ ), or the lowest cost solution using only the LFAO. C<sub>L1</sub> an C<sub>L2</sub> should have a capacitance in the range 12 to 22 pF for an oscillator frequency in the 4-8 MHz range.

The internal MCU clock frequency  $(f_{INT})$  is divided by 12 to drive the Timer, the A/D converter and the Watchdog timer, and by 13 to drive the CPU core, as may be seen in Figure 12.

With an 8 MHz oscillator frequency, the fastest machine cycle is therefore  $1.625\mu s$ .

A machine cycle is the smallest unit of time needed to execute any operation (for instance, to increment the Program Counter). An instruction may require two, four, or five machine cycles for execution.

# 3.1.1 Main Oscillator

The oscillator configuration may be specified by selecting the appropriate option. When the CRYSTAL/ RESONATOR option is selected, it must be used with a quartz crystal, a ceramic resonator or an external signal provided on the OSC in pin. When the RCNET-WORK option is selected, the system clock is generated by an external resistor.

The main oscillator can be turned off (when the OSG ENABLED option is selected) by setting the OSCOFF bit of the ADC Control Register. The Low Frequency Auxiliary Oscillator is automatically started.

**/۲**۸

# Figure 9. Oscillator Configurations

# CLOCK SYSTEM (Cont'd)

Turning on the main oscillator is achieved by resetting the OSCOFF bit of the A/D Converter Control Register or by resetting the MCU. Restarting the main oscillator implies a delay comprising the oscillator start up delay period plus the duration of the software instruction at  $f_{LFAO}$  clock frequency.

# 3.1.2 Low Frequency Auxiliary Oscillator (LFAO)

The Low Frequency Auxiliary Oscillator has three main purposes. Firstly, it can be used to reduce power consumption in non timing critical routines. Secondly, it offers a fully integrated system clock, without any external components. Lastly, it acts as a safety oscillator in case of main oscillator failure.

This oscillator is available when the OSG ENA-BLED option is selected. In this case, it automatically starts one of its periods after the first missing edge from the main oscillator, whatever the reason (main oscillator defective, no clock circuitry provided, main oscillator switched off...).

User code, normal interrupts, WAIT and STOP instructions, are processed as normal, at the reduced  $f_{LFAO}$  frequency. The A/D converter accuracy is decreased, since the internal frequency is below 1MHz.

At power on, the Low Frequency Auxiliary Oscillator starts faster than the Main Oscillator. It therefore feeds the on-chip counter generating the POR delay until the Main Oscillator runs.

The Low Frequency Auxiliary Oscillator is automatically switched off as soon as the main oscillator starts.

# ADCR

Address: 0D1h — Read/Write

| 7    |      |      |      |     |      | 0    |

|------|------|------|------|-----|------|------|

| ADCR | ADCR | ADCR | ADCR | OSC | ADCR | ADCR |

| 7    | 6    | 5    | 4    | OFF | 1    | 0    |

Bit 7-3, 1-0= **ADCR7-ADCR3**, **ADCR1-ADCR0**: *ADC Control Register*. These bits are reserved for ADC Control.

Bit 2 = **OSCOFF**. When low, this bit enables main oscillator to run. The main oscillator is switched off when OSCOFF is high.

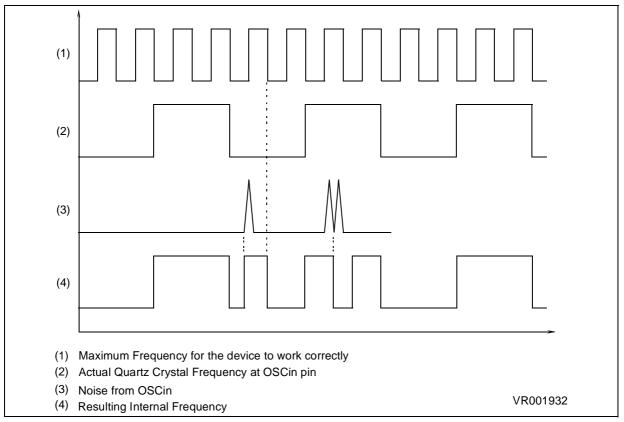

# 3.1.3 Oscillator Safe Guard

The Oscillator Safe Guard (OSG) affords drastically increased operational integrity in ST62xx devices. The OSG circuit provides three basic functions: it filters spikes from the oscillator lines which would result in over frequency to the ST62 CPU; it gives access to the Low Frequency Auxiliary Oscillator (LFAO), used to ensure minimum processing in case of main oscillator failure, to offer reduced power consumption or to provide a fixed frequency low cost oscillator; finally, it automatically limits the internal clock frequency as a function of supply voltage, in order to ensure correct operation even if the power supply should drop.

The OSG is enabled or disabled by choosing the relevant OSG option. It may be viewed as a filter whose cross-over frequency is device dependent.

Spikes on the oscillator lines result in an effectively increased internal clock frequency. In the absence of an OSG circuit, this may lead to an over frequency for a given power supply voltage. The OSG filters out such spikes (as illustrated in Figure 10). In all cases, when the OSG is active, the maximum internal clock frequency,  $f_{INT}$ , is limited to  $f_{OSG}$ , which is supply voltage dependent. This relationship is illustrated in Figure 13.

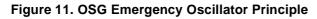

When the OSG is enabled, the Low Frequency Auxiliary Oscillator may be accessed. This oscillator starts operating after the first missing edge of the main oscillator (see Figure 11).

Over-frequency, at a given power supply level, is seen by the OSG as spikes; it therefore filters out some cycles in order that the internal clock frequency of the device is kept within the range the particular device can stand (depending on  $V_{DD}$ ), and below  $f_{OSG}$ : the maximum authorised frequency with OSG enabled.

**Note.** The OSG should be used wherever possible as it provides maximum safety. Care must be taken, however, as it can increase power consumption and reduce the maximum operating frequency to  $f_{OSG}$ .

**Warning**: Care has to be taken when using the OSG, as the internal frequency is defined between a minimum and a maximum value and is not accurate.

For precise timing measurements, it is not recommended to use the OSG and it should not be enabled in applications that use the SPI or the UART.

It should also be noted that power consumption in Stop mode is higher when the OSG is enabled (around  $50\mu A$  at nominal conditions and room temperature).

# CLOCK SYSTEM (Cont'd)

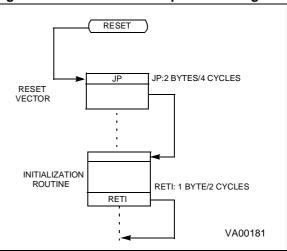

# RESETS (Cont'd) 3.2.6 MCU Initialization Sequence

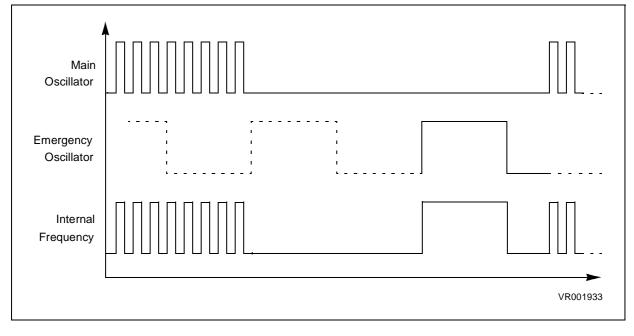

When a reset occurs the stack is reset, the PC is loaded with the address of the Reset Vector (located in program ROM starting at address 0FFEh). A jump to the beginning of the user program must be coded at this address. Following a Reset, the Interrupt flag is automatically set, so that the CPU is in Non Maskable Interrupt mode; this prevents the initialisation routine from being interrupted. The initialisation routine should therefore be terminated by a RETI instruction, in order to revert to normal mode and enable interrupts. If no pending interrupt is present at the end of the initialisation routine, the MCU will continue by processing the instruction immediately following the RETI instruction. If, however, a pending interrupt is present, it will be serviced.

# Figure 16. Reset and Interrupt Processing

Figure 17. Reset Block Diagram

# 3.4 INTERRUPTS

The CPU can manage four Maskable Interrupt sources, in addition to a Non Maskable Interrupt source (top priority interrupt). Each source is associated with a specific Interrupt Vector which contains a Jump instruction to the associated interrupt service routine. These vectors are located in Program space (see Table 7).

When an interrupt source generates an interrupt request, and interrupt processing is enabled, the PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction), which then causes a Jump to the relevant interrupt service routine, thus servicing the interrupt.

Interrupt sources are linked to events either on external pins, or on chip peripherals. Several events can be ORed on the same interrupt source, and relevant flags are available to determine which event triggered the interrupt.

The Non Maskable Interrupt request has the highest priority and can interrupt any interrupt routine at any time; the other four interrupts cannot interrupt each other. If more than one interrupt request is pending, these are processed by the processor core according to their priority level: source #1 has the higher priority while source #4 the lower. The priority of each interrupt source is fixed.

| Interrupt Source    | Priority | Vector Address |

|---------------------|----------|----------------|

| Interrupt source #0 | 1        | (FFCh-FFDh)    |

| Interrupt source #1 | 2        | (FF6h-FF7h)    |

| Interrupt source #2 | 3        | (FF4h-FF5h)    |

| Interrupt source #3 | 4        | (FF2h-FF3h)    |

| Interrupt source #4 | 5        | (FF0h-FF1h)    |

# Table 7. Interrupt Vector Map

# 3.4.1 Interrupt request

All interrupt sources but the Non Maskable Interrupt source can be disabled by setting accordingly the GEN bit of the Interrupt Option Register (IOR). This GEN bit also defines if an interrupt source, including the Non Maskable Interrupt source, can restart the MCU from STOP/WAIT modes.

Interrupt request from the Non Maskable Interrupt source #0 is latched by a flip flop which is automat-

ically reset by the core at the beginning of the nonmaskable interrupt service routine.

Interrupt request from source #1 can be configured either as edge or level sensitive by setting accordingly the LES bit of the Interrupt Option Register (IOR).

Interrupt request from source #2 are always edge sensitive. The edge polarity can be configured by setting accordingly the ESB bit of the Interrupt Option Register (IOR).

Interrupt request from sources #3 & #4 are level sensitive.

In edge sensitive mode, a latch is set when a edge occurs on the interrupt source line and is cleared when the associated interrupt routine is started. So, the occurrence of an interrupt can be stored, until completion of the running interrupt routine before being processed. If several interrupt requests occurs before completion of the running interrupt routine, only the first request is stored.

Storage of interrupt requests is not available in level sensitive mode. To be taken into account, the low level must be present on the interrupt pin when the MCU samples the line after instruction execution.

At the end of every instruction, the MCU tests the interrupt lines: if there is an interrupt request the next instruction is not executed and the appropriate interrupt service routine is executed instead.

| Tab | e 8. | Interrupt | Option | Register | Description |

|-----|------|-----------|--------|----------|-------------|

|-----|------|-----------|--------|----------|-------------|

| GEN    | SET      | Enable all interrupts                            |

|--------|----------|--------------------------------------------------|

| OLN    | CLEARED  | Disable all interrupts                           |

|        | SET      | Rising edge mode on inter-<br>rupt source #2     |

| ESB    | CLEARED  | Falling edge mode on inter-<br>rupt source #2    |

| LES    | SET      | Level-sensitive mode on in-<br>terrupt source #1 |

| LLS    | CLEARED  | Falling edge mode on inter-<br>rupt source #1    |

| OTHERS | NOT USED |                                                  |

# POWER SAVING MODE (Cont'd)

# 3.5.3 Exit from WAIT and STOP Modes

The following paragraphs describe how the MCU exits from WAIT and STOP modes, when an interrupt occurs (not a Reset). It should be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) prior to entering WAIT or STOP mode, as well as on the interrupt type.

Interrupts do not affect the oscillator selection.

#### 3.5.3.1 Normal Mode

If the MCU was in the main routine when the WAIT or STOP instruction was executed, exit from Stop or Wait mode will occur as soon as an interrupt occurs; the related interrupt routine is executed and, on completion, the instruction which follows the STOP or WAIT instruction is then executed, providing no other interrupts are pending.

# 3.5.3.2 Non Maskable Interrupt Mode

If the STOP or WAIT instruction has been executed during execution of the non-maskable interrupt routine, the MCU exits from the Stop or Wait mode as soon as an interrupt occurs: the instruction which follows the STOP or WAIT instruction is executed, and the MCU remains in non-maskable interrupt mode, even if another interrupt has been generated.

#### 3.5.3.3 Normal Interrupt Mode

If the MCU was in interrupt mode before the STOP or WAIT instruction was executed, it exits from STOP or WAIT mode as soon as an interrupt occurs. Nevertheless, two cases must be considered:

If the interrupt is a normal one, the interrupt routine in which the WAIT or STOP mode was entered will be completed, starting with the execution of the instruction which follows the STOP or the WAIT instruction, and the MCU is still in the interrupt mode. At the end of this routine pending interrupts will be serviced in accordance with their priority.

In the event of a non-maskable interrupt, the non-maskable interrupt service routine is processed first, then the routine in which the WAIT or STOP mode was entered will be completed by executing the instruction following the STOP or WAIT instruction. The MCU remains in normal interrupt mode.

# Notes:

To achieve the lowest power consumption during RUN or WAIT modes, the user program must take care of:

- configuring unused I/Os as inputs without pull-up (these should be externally tied to well defined logic levels);

- placing all peripherals in their power down modes before entering STOP mode;

When the hardware activated Watchdog is selected, or when the software Watchdog is enabled, the STOP instruction is disabled and a WAIT instruction will be executed in its place.

If all interrupt sources are disabled (GEN low), the MCU can only be restarted by a Reset. Although setting GEN low does not mask the NMI as an interrupt, it will stop it generating a wake-up signal.

The WAIT and STOP instructions are not executed if an enabled interrupt request is pending.

# I/O PORTS (Cont'd)

# 4.1.2 Safe I/O State Switching Sequence

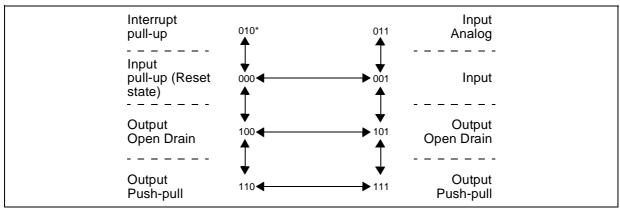

Switching the I/O ports from one state to another should be done in a sequence which ensures that no unwanted side effects can occur. The recommended safe transitions are illustrated in Figure 24. All other transitions are potentially risky and should be avoided when changing the I/O operating mode, as it is most likely that undesirable sideeffects will be experienced, such as spurious interrupt generation or two pins shorted together by the analog multiplexer.

Single bit instructions (SET, RES, INC and DEC) should be used with great caution on Ports Data registers, since these instructions make an implicit read and write back of the entire register. In port input mode, however, the data register reads from the input pins directly, and not from the data register latches. Since data register information in input mode is used to set the characteristics of the input pin (interrupt, pull-up, analog input), these may be unintentionally reprogrammed depending on the state of the input pins. As a general rule, it is better to limit the use of single bit instructions on data registers to when the whole (8-bit) port is in output mode. In the case of inputs or of mixed inputs and

outputs, it is advisable to keep a copy of the data register in RAM. Single bit instructions may then be used on the RAM copy, after which the whole copy register can be written to the port data register:

SET bit, datacopy LD a, datacopy LD DRA, a

**Warning:** Care must also be taken to not use instructions that act on a whole port register (INC, DEC, or read operations) when all 8 bits are not available on the device. Unavailable bits must be masked by software (AND instruction).

The WAIT and STOP instructions allow the ST62xx to be used in situations where low power consumption is needed. The lowest power consumption is achieved by configuring I/Os in input mode with well-defined logic levels.

The user must take care not to switch outputs with heavy loads during the conversion of one of the analog inputs in order to avoid any disturbance to the conversion.

# Figure 24. Diagram showing Safe I/O State Transitions

Á7/

# I/O PORTS (Cont'd)

# 4.1.3 AR Timer Alternate function Option

When bit PWMOE of register ARMC is low, pin AR-TIMout/PB7 is configured as any standard pin of port B through the port registers. When PWMOE is high, ARTIMout/PB7 is the PWM output, independently of the port registers configuration.

ARTIMin/PB6 is connected to the AR Timer input. It is configured through the port registers as any standard pin of port B. To use ARTIMin/PB6 as AR Timer input, it must be configured as input through DDRB.

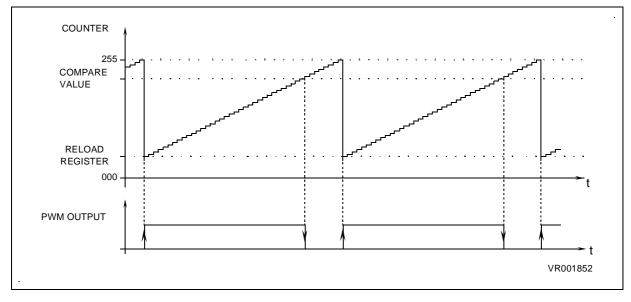

# 4.1.4 SPI Alternate function Option

PC2/PC4 are used as standard I/O as long as bit SPCLK of the SPI Mode Register is kept low. When PC2/Sin is configured as input, it is automatically connected to the SPI shift register input, independent of the state at SPCLK.

PC3/SOUT is configured as SPI push-pull output by setting bit 0 of the Miscellaneous register (address DDh), regardless of the state of Port C registers. PC4/SCK is configured as push-pull output clock (master mode) by programming it as pushpull output through DDRC register and by setting bit SPCLK of the SPI Mode Register.

PC4/SCK is configured as input clock (slave mode) by programming it as input through DDRC register and by clearing bit SPCLK of the SPI Mode Register. With this configuration, PC4 can simultaneously be used as an input.

# TIMER (Cont'd)

A write to the TCR register will predominate over the 8-bit counter decrement to 00h function, i.e. if a write and a TCR register decrement to 00h occur simultaneously, the write will take precedence, and the TMZ bit is not set until the 8-bit counter reaches 00h again. The values of the TCR and the PSC registers can be read accurately at any time.

# 4.2.4 Timer Registers

# Timer Status Control Register (TSCR)

Address: 0D4h - Read/Write

| 7   |     |    |    |     |     |     | 0   |

|-----|-----|----|----|-----|-----|-----|-----|

| TMZ | ETI | D5 | D4 | PSI | PS2 | PS1 | PS0 |

# Bit 7 = TMZ: Timer Zero bit

A low-to-high transition indicates that the timer count register has decrement to zero. This bit must be cleared by user software before starting a new count.

#### Bit 6 = ETI: Enable Timer Interrup

When set, enables the timer interrupt request (vector #4). If ETI=0 the timer interrupt is disabled. If ETI=1 and TMZ=1 an interrupt request is generated.

Bit 5 = D5: Reserved

Must be set to "1".

Bit 4 = **D4**

Do not care.

Bit 3 = **PSI**: Prescaler Initialize Bit

Used to initialize the prescaler and inhibit its counting. When PSI="0" the prescaler is set to 7Fh and the counter is inhibited. When PSI="1" the prescaler is enabled to count downwards. As long as PSI="0" both counter and prescaler are not running.

Bit 2, 1, 0 = **PS2**, **PS1**, **PS0**: *Prescaler Mux. Select.* These bits select the division ratio of the prescaler register.

| Table 12 | . Prescaler | Division | Factors |

|----------|-------------|----------|---------|

|----------|-------------|----------|---------|

| PS2 | PS1 | PS0 | Divided by      |

|-----|-----|-----|-----------------|

| 0   | 0   | 0   | 1               |

| 0   | 0   | 1   | 2               |

| 0   | 1   | 0   | 4               |

| 0   | 1   | 1   | 8               |

| 1   | 0   | 0   | 16              |

| 1   | 0   | 1   | 32              |

| 1   | 1   | 0   | 32<br>64<br>128 |

| 1   | 1   | 1   | 128             |

# Timer Counter Register (TCR)

Address: 0D3h — Read/Write

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7-0 = D7-D0: Counter Bits.

#### **Prescaler Register PSC**

Address: 0D2h — Read/Write

| 7  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

Bit 7 = **D7**: Always read as "0".

Bit 6-0 = D6-D0: Prescaler Bits.

# AUTO-RELOAD TIMER (Cont'd)

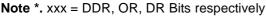

It should be noted that the reload values will also affect the value and the resolution of the duty cycle of PWM output signal. To obtain a signal on ARTI-Mout, the contents of the ARCP register must be greater than the contents of the ARRC register.

The maximum available resolution for the ARTI-Mout duty cycle is:

# Resolution = 1/[255-(ARRC)]

Where ARRC is the content of the Reload/Capture register. The compare value loaded in the Compare Register, ARCP, must be in the range from (ARRC) to 255.

The ARTC counter is initialized by writing to the ARRC register and by then setting the TCLD (Timer Load) and the TEN (Timer Clock Enable) bits in the Mode Control register, ARMC.

Enabling and selection of the clock source is controlled by the CC0, CC1, SL0 and SL1 bits in the Status Control Register, ARSC1. The prescaler division ratio is selected by the PS0, PS1 and PS2 bits in the ARSC1 register.

In Auto-reload Mode, any of the three available clock sources can be selected: Internal Clock, Internal Clock divided by 3 or the clock signal present on the ARTIMin pin.

Figure 29. Auto-reload Timer PWM Function

# SERIAL PERIPHERAL INTERFACE SPI (Cont'd)

# 4.6 SPI Timing Diagrams

57

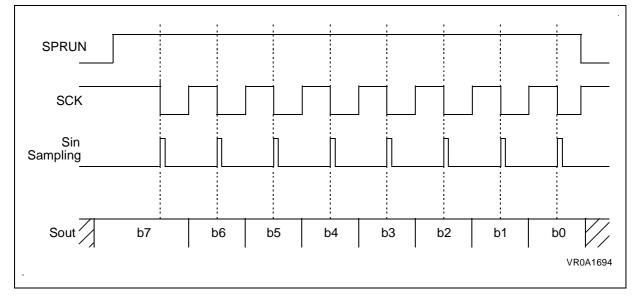

# Figure 32. CPOL = 0 Clock Polarity Normal, CPHA = 0 Phase Selection Normal

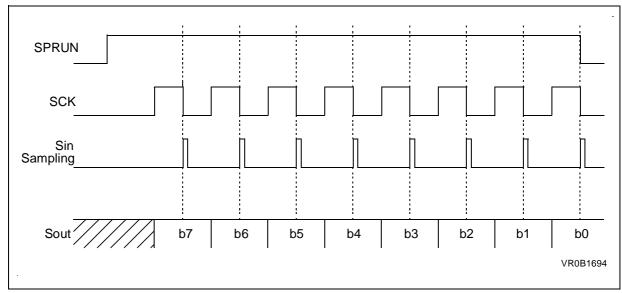

Figure 33. CPOL = 1 Clock Polarity Inverted, CPHA = 0 Phase Selection Normal

# ST62T53C/T60C/T63C ST62E60C

# SERIAL PERIPHERAL INTERFACE SPI (Cont'd)

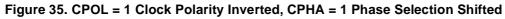

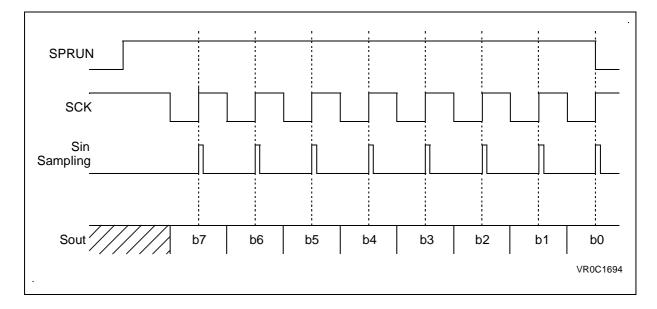

# Figure 34. CPOL = 0 Clock Polarity Normal, CPHA = 1 Phase Selection Shifted

# **5.3 INSTRUCTION SET**

The ST6 core offers a set of 40 basic instructions which, when combined with nine addressing modes, yield 244 usable opcodes. They can be divided into six different types: load/store, arithmetic/logic, conditional branch, control instructions, jump/call, and bit manipulation. The following paragraphs describe the different types.

All the instructions belonging to a given type are presented in individual tables.

# Table 17. Load & Store Instructions

**Load & Store**. These instructions use one, two or three bytes in relation with the addressing mode. One operand is the Accumulator for LOAD and the other operand is obtained from data memory using one of the addressing modes.

For Load Immediate one operand can be any of the 256 data space bytes while the other is always immediate data.

| Instruction | Addressing Mode | Buttoo | Cycles | Flags    |   |  |  |

|-------------|-----------------|--------|--------|----------|---|--|--|

| instruction | Addressing Mode | Bytes  | Cycles | Z        | C |  |  |

| LD A, X     | Short Direct    | 1      | 4      | Δ        | * |  |  |

| LD A, Y     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD A, V     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD A, W     | Short Direct    | 1      | 4      | Δ        | * |  |  |

| LD X, A     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD Y, A     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD V, A     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD W, A     | Short Direct    | 1      | 4      | $\Delta$ | * |  |  |

| LD A, rr    | Direct          | 2      | 4      | $\Delta$ | * |  |  |

| LD rr, A    | Direct          | 2      | 4      | $\Delta$ | * |  |  |

| LD A, (X)   | Indirect        | 1      | 4      | $\Delta$ | * |  |  |

| LD A, (Y)   | Indirect        | 1      | 4      | $\Delta$ | * |  |  |

| LD (X), A   | Indirect        | 1      | 4      | $\Delta$ | * |  |  |

| LD (Y), A   | Indirect        | 1      | 4      | Δ        | * |  |  |

| LDI A, #N   | Immediate       | 2      | 4      | Δ        | * |  |  |

| LDI rr, #N  | Immediate       | 3      | 4      | *        | * |  |  |

#### Notes:

X,Y. Indirect Register Pointers, V & W Short Direct Registers

#. Immediate data (stored in ROM memory)

rr. Data space register

$\Delta$ . Affected

\*. Not Affected

# ST62T53C/T60C/T63C ST62E60C

# Opcode Map Summary (Continued)

|    | LOW       | - | _         |   |           |           |        | _         |    | _           |   | -        |        |   | _         |        | _         |   | _           | LOW       |

|----|-----------|---|-----------|---|-----------|-----------|--------|-----------|----|-------------|---|----------|--------|---|-----------|--------|-----------|---|-------------|-----------|

| ні |           |   | 8<br>1000 |   | 9<br>1001 |           |        | A<br>1010 |    | В<br>1011   |   | C<br>110 | D      |   | D<br>1101 |        | Е<br>1110 |   | F<br>1111   | н         |

|    | -         | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 4 | LDI       | 2      | JRC       | 4 | LD          | -         |

|    | 0<br>0000 |   | е         |   | abc       |           |        | е         |    | b0,rr       |   | е        |        |   | rr,nn     |        | е         |   | a,(y)       | 0<br>0000 |

| Ľ  | 000       | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 3 | imm       | 1      | prc       | 1 | ind         | 0000      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | DEC       | 2      | JRC       | 4 | LD          |           |

|    | 1<br>0001 |   | е         |   | abc       |           |        | е         |    | b0,rr       |   | е        |        |   | х         |        | е         |   | a,rr        | 1<br>0001 |

| Ľ  | 001       | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         | 0001      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 4 | COM       | 2      | JRC       | 4 | CP          |           |

|    | 2         |   | е         |   | abc       | -         |        | е         |    | b4,rr       |   | е        | -      |   | а         |        | е         |   | a,(y)       | 2         |

| C  | 0010      | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    |   |           | 1      | prc       | 1 | ind         | 0010      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | LD        | 2      | JRC       | 4 | CP          |           |

|    | 3         | - | e         | • | abc       | 01        | -      | e         | •  | b4,rr       | e |          | 0112   | • | x,a       | -      | e         | • | a,rr        | 3         |

| C  | 0011      | 1 | pcr       | 2 | abo       | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         | 0011      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 2 | RETI      | 2      | JRC       | 4 | ADD         |           |

|    | 4         | 2 | e         | 4 | abc       | JF        | 2      | e         | 4  | b2,rr       | 2 | е        | JINZ   | 2 |           | 2      | e         | 4 |             | 4         |

| C  | 0100      | 1 |           | 2 | abc       | ovt       | 1      |           | 2  |             | 1 | e        | nor    | 1 | inh       | 1      |           | 1 | a,(y)       | 0100      |

|    |           | 2 | pcr       | 2 |           | ext       | 1<br>2 | pcr       | 2  | b.d         | 2 |          | pcr    | 4 | inh       | 1<br>2 | prc       | 4 | ind         |           |

|    | 5         | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | DEC       | 2      | JRC       | 4 | ADD         | 5         |

| C  | 0101      |   | е         | ~ | abc       |           |        | е         | ~  | b2,rr       |   | е        |        |   | у         |        | е         | ~ | a,rr        | 0101      |

|    |           | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         |           |

|    | 6         | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 2 | STOP      | 2      | JRC       | 4 | INC         | 6         |

| C  | 0110      |   | е         | _ | abc       |           |        | е         |    | b6,rr       |   | е        |        |   |           |        | е         |   | (y)         | 0110      |

|    |           | 1 | pcr       | 2 |           | ext       |        | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | inh       | 1      | prc       | 1 | ind         |           |

|    | 7         | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | LD        | 2      | JRC       | 4 | INC         | 7         |

| C  | 0111      |   | е         |   | abc       |           |        | е         |    | b6,rr       |   | е        |        |   | y,a       |        | е         |   | rr          | 0111      |

|    | -         | 1 | pcr       | 2 |           | ext       |        | pcr       | 2  | b.d         |   |          | pcr    | 1 | sd        | 1      | prc       | - | dir         | -         |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    |   |           | 2      | JRC       | 4 | LD          | 8         |

| 1  | 8<br>1000 |   | е         |   | abc       |           |        | е         |    | b1,rr       |   | е        |        |   | #         |        | е         |   | (y),a       | 1000      |

|    |           | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    |   |           | 1      | prc       | 1 | ind         | 1000      |

|    | •         | 2 | RNZ       | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | DEC       | 2      | JRC       | 4 | LD          |           |

| 1  | 9<br>1001 |   | е         |   | abc       |           |        | е         |    | b1,rr       |   | е        |        |   | v         |        | е         |   | rr,a        | 9<br>1001 |

|    | 001       | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         | 1001      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 4 | RCL       | 2      | JRC       | 4 | AND         |           |

|    | A         |   | е         |   | abc       |           |        | е         |    | b5,rr       |   | е        |        |   | а         |        | е         |   | a,(y)       | A         |

|    | 1010      | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | inh       | 1      | prc       | 1 | ind         | 1010      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | LD        | 2      | JRC       | 4 | AND         |           |

|    | В         |   | e         |   | abc       |           |        | e         |    | b5,rr       | - | е        |        |   | v,a       | -      | e         |   | a,rr        | В         |

| 1  | 1011      | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         | 1011      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | RES         |   |          | JRZ    | 2 | RET       | 2      | JRC       | 4 | SUB         |           |

|    | С         | - | e         |   | abc       | 0.        | -      | e         | 1. | b3,rr       | - | е        | 51 V.L | - |           | 1-     | e         |   | a,(y)       | С         |

| 1  | 100       | 1 | pcr       | 2 | ubb       | ext       | 1      | pcr       | 2  | bo,n<br>b.d | 1 | Ŭ        | pcr    | 1 | inh       | 1      | prc       | 1 | ind         | 1100      |

|    |           | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | DEC       | 2      | JRC       | 4 | SUB         |           |

|    | D         | ~ |           | + | abo       | JF        | -      | e         | 1  | b3,rr       | ~ | ~        |        | 1 | w         | ſ _    |           | 1 |             | D         |

| 1  | 101       | 1 | e         | 2 | abc       | ov+       | 4      |           | 2  | -           | 1 | е        | nor    | 1 |           | 1      | e         | 2 | a,rr<br>dir | 1101      |

|    |           | 1 | pcr       |   |           | ext<br>JP |        | pcr       |    | b.d         |   |          | pcr    | 1 | sd        | 1      | prc       |   |             |           |

|    | Е         | 2 | JRNZ      | 4 |           | J٢        | 2      | JRNC      | 4  | RES         | 2 |          | JRZ    | 2 | WAIT      | 2      | JRC       | 4 | DEC         | Е         |

| 1  | 1110      |   | е         | ~ | abc       |           |        | е         |    | b7,rr       |   | е        |        |   |           |        | е         |   | (y)         | 1110      |

|    |           | 1 | pcr       | 2 |           | ext       |        | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | inh       | 1      | prc       | 1 | ind         |           |

|    | F         | 2 | JRNZ      | 4 |           | JP        | 2      | JRNC      | 4  | SET         | 2 |          | JRZ    | 4 | LD        | 2      | JRC       | 4 | DEC         | F         |

| 1  | г<br>1111 |   | е         |   | abc       |           |        | е         |    | b7,rr       |   | е        |        |   | w,a       |        | е         |   | rr          | 1111      |

|    |           | 1 | pcr       | 2 |           | ext       | 1      | pcr       | 2  | b.d         | 1 |          | pcr    | 1 | sd        | 1      | prc       | 2 | dir         |           |

# Abbreviations for Addressing Modes: Legend:

- Direct Short Direct dir sd imm Immediate inh Inherent Extended ext b.d Bit Direct Bit Test

- Indicates Illegal Instructions 5 Bit Displacement 3 Bit Address #

- е b

rr

- 1byte dataspace address 1 byte immediate data 12 bit address nn

- abc

- 8 bit Displacement ee

- bt pcr ind Program Counter Relative

- Indirect

Cycle Mnemonic 2 JRC Operand е 1 prc Bytes Addressing Mode

64/84

# ST62T53C/T60C/T63C ST62E60C

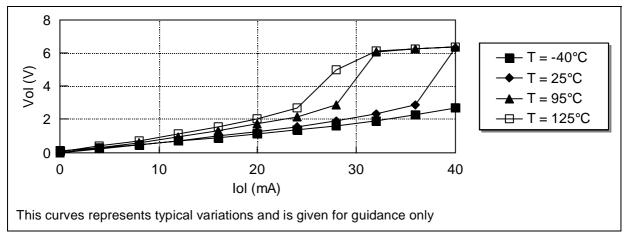

Figure 37. Vol versus IoI on all I/O port at Vdd=5V

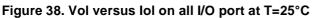

Figure 39. Vol versus lol for High sink (30mA) I/Oports at T=25°C

# **1.3 ORDERING INFORMATION**

The following section deals with the procedure for transfer of customer codes to STMicroelectronics.

#### 1.3.1 Transfer of Customer Code

Customer code is made up of the ROM contents and the list of the selected mask options. The ROM contents are to be sent on diskette, or by electronic means, with the hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected mask options are communicated to STMicroelectronics using the correctly filled OP-TION LIST appended. See page 82.

# **1.3.2 Listing Generation and Verification**

When STMicroelectronics receives the user's ROM contents, a computer listing is generated from it. This listing refers exactly to the mask which will be used to produce the specified MCU. The listing is then returned to the customer who must thoroughly check, complete, sign and return it to STMicroelectronics. The signed listing forms a part of the contractual agreement for the creation of the specific customer mask.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

#### Table 27. ROM Memory Map for ST6260B

| Device Address | Description          |

|----------------|----------------------|

| 0000h-007Fh    | Reserved             |

| 0080h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

# Table 28. ROM Memory Map for ST6253C/63B

| ,              |                      |

|----------------|----------------------|

| Device Address | Description          |

| 0000h-087Fh    | Reserved             |

| 0880h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

| Sales Type                                      | ROM (Bytes) | EEPROM (Bytes) | Temperature Range                              | Package |

|-------------------------------------------------|-------------|----------------|------------------------------------------------|---------|

| ST6253CB1/XXX<br>ST6253CB6/XXX<br>ST6253CB3/XXX | 1826        | -              | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PDIP20  |

| ST6253CM1/XXX<br>ST6253CM6/XXX<br>ST6253CM3/XXX | - 1836      |                | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PSO20   |

| ST6260BB1/XXX<br>ST6260BB6/XXX<br>ST6260BB3/XXX | - 3884      | 128            | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PDIP20  |

| ST6260BM1/XXX<br>ST6260BM6/XXX<br>ST6260BM3/XXX |             |                | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PSO20   |

| ST6263BB1/XXX<br>ST6263BB6/XXX<br>ST6263BB3/XXX | 1836        | 64             | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PDIP20  |

| ST6263BM1/XXX<br>ST6263BM6/XXX<br>ST6263BM3/XXX | 1030        |                | 0 to + 70°C<br>-40 to + 85°C<br>-40 to + 125°C | PSO20   |

# **Table 1. ROM Version Ordering Information**

<u>ل</u>رک

| ST6253C/60B/63B/P53C/P60C/P63C MICROCONTROLLER OPTION LIST |                                                          |                                                           |                                           |  |

|------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------|--|

| Customer:                                                  |                                                          |                                                           |                                           |  |

| Address:                                                   |                                                          |                                                           |                                           |  |

| Contact                                                    |                                                          |                                                           |                                           |  |

| Contact:<br>Phone:                                         |                                                          |                                                           |                                           |  |

| Reference:                                                 |                                                          |                                                           |                                           |  |

|                                                            |                                                          |                                                           |                                           |  |

| STMicroelec                                                | tronics references:                                      |                                                           |                                           |  |

| Device:                                                    | [ ] ST6253C (2 KB)<br>[ ] ST62P53C (2 KB)                | [ ] ST6260B (4 KB)<br>[ ] ST62P60C (4 KB)                 | [ ] ST6263B (2 KB)<br>[ ] ST62P63C (2 KB) |  |

| Package:                                                   |                                                          | [ ] Dual in Line Plastic<br>[ ] Small Outline Plastic wit | h conditioning                            |  |

| Conditioning                                               | option:                                                  | [] Standard (Tube)                                        | [] Tape & Reel                            |  |

| Temperature                                                | -                                                        | [] 0°C to + 70°C                                          | [] - 40°C to + 85°C                       |  |

| -                                                          | -                                                        | [ ] - 40°C to + 125°C                                     |                                           |  |

| Marking:                                                   |                                                          | PSO28 (8 char. m                                          | max):                                     |  |

| Authorized ch                                              | naracters are letters, digit                             | SSOP28 (11 char<br>s, '.', '-', '/' and spaces only.      | : max):                                   |  |

| Oscillator Sat                                             | feguard*:                                                | [] Enabled                                                | [] Disabled                               |  |

| Oscillator Sel                                             | lection:                                                 | [] Quartz crystal / Ceramic<br>[] RC network              | resonator                                 |  |

| Reset Delay:                                               |                                                          | [] 32768 cycle delay                                      | [] 2048 cycle delay                       |  |

| Watchdog Se                                                | election:                                                | [] Software Activation                                    | [] Hardware Activation                    |  |

|                                                            | I-Up at RESET*:                                          | [] Enabled                                                | [] Disabled                               |  |

|                                                            | I-Up at RESET*:                                          | [] Enabled                                                | [] Disabled                               |  |

| External STC                                               | P Mode Control:                                          | [] Enabled                                                | [] Disabled                               |  |

| Readout Prot                                               | tection: FAST                                            |                                                           |                                           |  |

|                                                            | DOM:                                                     | [] Enabled                                                | [] Disabled                               |  |

|                                                            | ROM:                                                     | [] Enabled:                                               |                                           |  |

|                                                            |                                                          |                                                           | by STMicroelectronics                     |  |

|                                                            |                                                          | [] Fuse can be bl                                         | own by the customer                       |  |

|                                                            |                                                          | [] Disabled                                               |                                           |  |

| Low Voltage                                                |                                                          | [] Enabled                                                | [] Disabled                               |  |

| NMI pull-up*:                                              |                                                          | [] Enabled                                                | [] Disabled                               |  |

| ADC Synchro<br>*except on S <sup>-</sup>                   |                                                          | [] Enabled                                                | [] Disabled                               |  |

|                                                            | equency in the applicatior<br>ating Range in the applica | ation:                                                    |                                           |  |

# **2 SUMMARY OF CHANGES**

| Rev. | Main Changes                                                                                                                                                                                                                                                                                      | Date         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.8  | Modification of "Additional Notes for EEPROM Parallel Mode" (p.13)<br>In section 4.2 on page 43: vector #4 instead of vector #3 for the timer interrupt request.<br>Changed f <sub>RC</sub> values in section 6.4 on page 68.<br>Changed Figure 49 on page 74.<br>Changed option list on page 82. | July<br>2001 |