Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                           |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp202-e-mm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

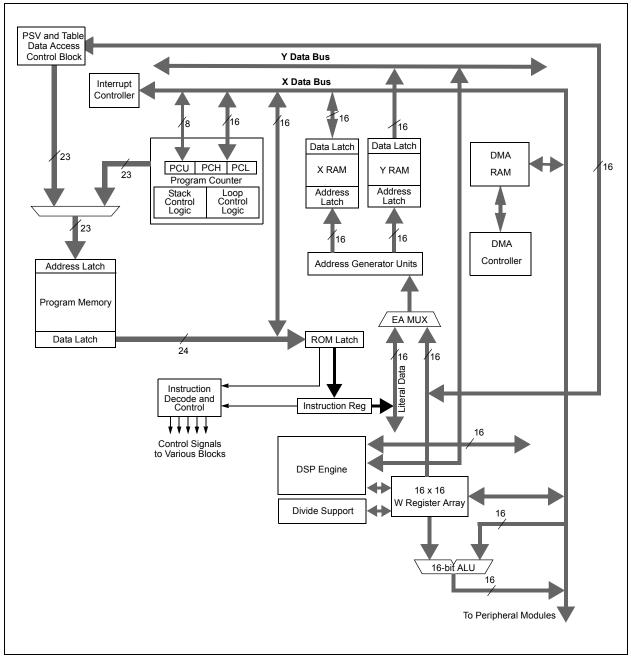

#### 3.4 Special MCU Features

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 CPU CORE BLOCK DIAGRAM

#### 3.6 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0    | R-0 | R/C-0             | R/C-0             | R-0 | R/C-0              | R -0 | R/W-0 |

|--------|-----|-------------------|-------------------|-----|--------------------|------|-------|

| OA     | ОВ  | SA <sup>(1)</sup> | SB <sup>(1)</sup> | OAB | SAB <sup>(4)</sup> | DA   | DC    |

| bit 15 |     |                   |                   |     |                    |      | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|-------------------------|----------------------|-----|-------|-------|-------|-------|

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA  | N     | OV    | Z     | С     |

| bit 7                |                         |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 15 OA: Accumulator A Overflow Status bit

1 = Accumulator A overflowed

0 = Accumulator A has not overflowed

bit 14 **OB:** Accumulator B Overflow Status bit

1 = Accumulator B overflowed

0 = Accumulator B has not overflowed

bit 13 SA: Accumulator A Saturation 'Sticky' Status bit (1)

1 = Accumulator A is saturated or has been saturated at some time

0 = Accumulator A is not saturated

bit 12 **SB:** Accumulator B Saturation 'Sticky' Status bit<sup>(1)</sup>

1 = Accumulator B is saturated or has been saturated at some time

0 = Accumulator B is not saturated

bit 11 OAB: OA || OB Combined Accumulator Overflow Status bit

1 = Accumulators A or B have overflowed

0 = Neither Accumulators A or B have overflowed

bit 10 SAB: SA || SB Combined Accumulator (Sticky) Status bit (4)

1 = Accumulators A or B are saturated or have been saturated at some time in the past

0 = Neither Accumulator A or B are saturated

bit 9 DA: DO Loop Active bit

1 = DO loop in progress

0 = DO loop not in progress

bit 8 **DC:** MCU ALU Half Carry/Borrow bit

1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

Note 1: This bit can be read or cleared (not set).

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

| _         | _    |  |

|-----------|------|--|

|           | J    |  |

|           |      |  |

| Ī         | Ó    |  |

| Ī         | Š    |  |

| `         | 240  |  |

| `         | 242  |  |

|           | 0000 |  |

| `         | 5    |  |

|           | 3    |  |

|           | 3    |  |

|           | 3    |  |

| ノニノン・コーロル | 3    |  |

| TARI F 4-13. | ADC1 REGISTER MAP FOR d | sPIC33F.I64GP202/802    | dsPIC33FJ128GP202/802 AND dsPIC33FJ32GP30          | 12 |

|--------------|-------------------------|-------------------------|----------------------------------------------------|----|

| IADEL TIV.   | ADD INCOIDILINIMAL LONG | 31 10331 30701 202/002. | . 431 10331 3 12001 202/002 AND 431 10331 33201 36 | ,_ |

| File Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7     | Bit 6     | Bit 5 | Bit 4      | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-------------------|--------|---------|--------|-----------|---------|---------|-----------|-----------|-------|------------|--------|--------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        | ADC Data Buffer 0 |        |         |        |           |         |         |           |           |       |            |        | xxxx   |          |         |               |

| AD1CON1   | 0320 | ADON   | _                 | ADSIDL | ADDMABM | _      | AD12B     | FORI    | M<1:0>  | ţ         | SSRC<2:0> |       | _          | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | CFG<2:0           | >      | _       | _      | CSCNA     | CHP     | S<1:0>  | BUFS      | _         |       | SMPI       | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _                 | _      |         | S      | AMC<4:0>  |         |         | ADCS<7:0> |           |       |            |        |        |          | 0000    |               |

| AD1CHS123 | 0326 | _      | _                 | _      | _       | _      | CH123N    | NB<1:0> | CH123SB | _         | _         | _     | _          | _      | CH123N | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                 | _      |         | С      | H0SB<4:0> | •       |         | CH0NA     | _         | _     | CH0SA<4:0> |        |        |          | 0000    |               |

| AD1PCFGL  | 032C | _      | _                 | _      | PCFG12  | PCFG11 | PCFG10    | PCFG9   | _       | _         | _         | PCFG5 | PCFG4      | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _                 | _      | CSS12   | CSS11  | CSS10     | CSS9    | _       | _         | _         | CSS5  | CSS4       | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |                   | _      |         | 1      | _         | 1       | _       |           | _         |       | ı          | _      | 1      | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: ADC1 REGISTER MAP FOR dsPIC33FJ64GP204/804, dsPIC33FJ128GP204/804 AND dsPIC33FJ32GP304

| File Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7     | Bit 6     | Bit 5        | Bit 4 | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-------------------|--------|---------|--------|-----------|---------|---------|-----------|-----------|--------------|-------|--------|--------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        | ADC Data Buffer 0 |        |         |        |           |         |         |           |           |              |       |        | xxxx   |          |         |               |

| AD1CON1   | 0320 | ADON   | _                 | ADSIDL | ADDMABM | _      | AD12B     | FORI    | M<1:0>  |           | SSRC<2:0> |              | _     | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | ٧      | 'CFG<2:0          | >      | _       | _      | CSCNA     | CHP     | S<1:0>  | BUFS      | _         |              | SMP   | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _                 | _      |         | S      | AMC<4:0>  |         |         | ADCS<7:0> |           |              |       |        |        |          | 0000    |               |

| AD1CHS123 | 0326 | _      | _                 | _      | _       | _      | CH123N    | NB<1:0> | CH123SB | _         | _         | _            | _     | _      | CH1231 | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                 | _      |         | CI     | H0SB<4:0> | •       |         | CH0NA     | _         | — CH0SA<4:0> |       |        |        | 0000     |         |               |

| AD1PCFGL  | 032C | _      | _                 | _      | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7     | PCFG6     | PCFG5        | PCFG4 | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _                 | _      | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7      | CSS6      | CSS5         | CSS4  | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      | _                 | _      | _       | _      | _         | _       | _       | _         | _         | _            | _     | _      | 1      | DMABL<2: | 0>      | 0000          |

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: DAC1 REGISTER MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7     | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|----------|-------------|--------|-----------------------------------------------|--------|--------|--------|--------|-------|--------|-----------|-------|--------|-------|-------|--------|-------|--------|---------------|

| DAC1CON  | 03F0        | DACEN  | DACEN — DACSIDL AMPON — — FORM — DACFDIV<6:0> |        |        |        |        |       |        |           |       |        |       |       | 0000   |       |        |               |

| DAC1STAT | 03F2        | LOEN   | _                                             | LMVOEN |        | _      | LITYPE | LFULL | LEMPTY | ROEN      | _     | RMVOEN | _     | _     | RITYPE | RFULL | REMPTY | 0000          |

| DAC1DFLT | 03F4        |        |                                               |        |        |        |        |       | DAC1DF | ELT<15:0> |       |        |       |       |        |       |        | 0000          |

| DAC1RDAT | 03F6        |        | DAC1RDAT<15:0>                                |        |        |        |        |       |        |           |       | 0000   |       |       |        |       |        |               |

| DAC1LDAT | 03F8        |        | DAC1LDAT<15:0>                                |        |        |        |        |       |        |           |       |        | 0000  |       |        |       |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note:

The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (such as [W7 + W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

#### 4.7 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- · The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing assumes priority when active for the X WAGU and X WAGU, Modulo Addressing is disabled. However, Modulo Addressing continues to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

#### **EXAMPLE 5-2: LOADING THE WRITE BUFFERS**

```

; Set up NVMCON for row programming operations

#0x4001, W0 ;

MO NVMCON ; Initialize NVMCON

MOV

; Set up a pointer to the first program memory location to be written

; program memory selected, and writes enabled

MOV #0x0000, W0 ;

MOV W0, TBLPAG ; Initialize PM Page Boundary SFR

MOV #0x6000, W0 ; An example program memory addres

; An example program memory address

; Perform the TBLWT instructions to write the latches

; 0th program word

#LOW WORD 0, W2

MOV

#HIGH BYTE 0, W3

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 1st_program_word

MOV #LOW_WORD_1, W2

MOV

#HIGH BYTE 1, W3

;

; Write PM low word into program latch

TBLWTL W2, [W0]

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 2nd program word

MOV #LOW WORD 2, W2

#HIGH BYTE 2, W3

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 63rd program word

MOV #LOW_WORD 31, W2

#HIGH_BYTE_31, W3

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

```

#### **EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE**

```

DISI

; Block all interrupts with priority <7

; for next 5 instructions

MOV

#0x55, W0

VOM

WO, NVMKEY

; Write the 55 key

MOV

#0xAA, W1

W1, NVMKEY

; Write the AA key

BSET

NVMCON, #WR

; Start the erase sequence

NOP

; Insert two NOPs after the

NOP

; erase command is asserted

```

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

bit 3 ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred

0 = Address error trap has not occurred

bit 2 STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred0 = Stack error trap has not occurred

bit 1 OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

bit 0 **Unimplemented:** Read as '0'

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

bit 2 CMIE: Comparator Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

#### 9.1 CPU Clocking System

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in Section 9.1.4 "PLL Configuration".

The FRC frequency depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 27.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits. FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Configuration Select bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture.

Instruction execution speed or device operating frequency, Fcy, is given by:

## EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 AUXILIARY OSCILLATOR

The Auxiliary Oscillator (AOSC) can be used for peripherals that need to operate at a frequency unrelated to the system clock such as a Digital-to-Analog Converter (DAC).

The Auxiliary Oscillator can use one of the following as its clock source:

- Crystal (XT): Crystal and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the SOCI and SOSCO pins.

- High-Speed Crystal (HS): Crystals in the range of 10 to 40 MHz. The crystal is connected to the SOSCI and SOSCO pins.

- External Clock (EC): External clock signal up to 64 MHz. The external clock signal is directly applied to SOSCI pin.

#### REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | SCK2R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | SDI2R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 SCK2R<4:0>: Assign SPI2 Clock Input (SCK2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

.

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### REGISTER 11-23: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | RP13R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | RP12R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 RP13R<4:0>: Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 11-2 for

peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP12R<4:0>: Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 11-2 for

peripheral function numbers)

#### REGISTER 11-24: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | RP15R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | RP14R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 RP15R<4:0>: Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 11-2 for

peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP14R<4:0>: Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 11-2 for

peripheral function numbers)

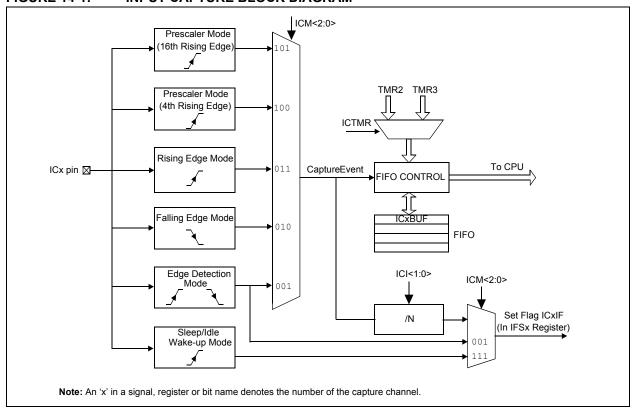

#### 14.0 INPUT CAPTURE

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices support up to four input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to '1' (ICI<1:0> = 00)

FIGURE 14-1: INPUT CAPTURE BLOCK DIAGRAM

#### REGISTER 19-8: CIEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0          | R-0 | R-0 | R-0 | R-0   | R-0 | R-0 | R-0 |

|--------------|-----|-----|-----|-------|-----|-----|-----|

| TERRCNT<7:0> |     |     |     |       |     |     |     |

| bit 15       |     |     |     | bit 8 |     |     |     |

| R-0   | R-0 | R-0 | R-0   | R-0     | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|---------|-----|-----|-------|

|       |     |     | RERRC | NT<7:0> |     |     |       |

| bit 7 |     |     |       |         |     |     | bit 0 |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 19-9: CiCFG1: ECAN™ BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|--------|-------|-------|

| SJW   | <1:0> |       |       | BRP   | 2<5:0> |       |       |

| bit 7 |       |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 SJW<1:0>: Synchronization Jump Width bits

11 = Length is 4 x TQ

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = Length is 1 x TQ

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

11 1111 = TQ = 2 x 64 x 1/FCAN

•

•

00 0010 =  $TQ = 2 \times 3 \times 1/FCAN$

00 0001 = TQ = 2 x 2 x 1/FCAN

00 0000 = TQ = 2 x 1 x 1/FCAN

#### dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

#### REGISTER 19-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

#### REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | as '0'             |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

#### bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

#### 19.6 ECAN Message Buffers

ECAN Message Buffers are part of DMA RAM Memory. They are not ECAN special function registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 19-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| _      | _   | _   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier bits

bit 1 SRR: Substitute Remote Request bit

1 = Message will request remote transmission

0 = Normal message

bit 0 **IDE:** Extended Identifier bit

1 = Message will transmit extended identifier0 = Message will transmit standard identifier

#### BUFFER 19-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | _   | _   | _   | EID17 | EID16 | EID15 | EID14 |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID13 | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0' bit 11-0 **EID<17:6>:** Extended Identifier bits

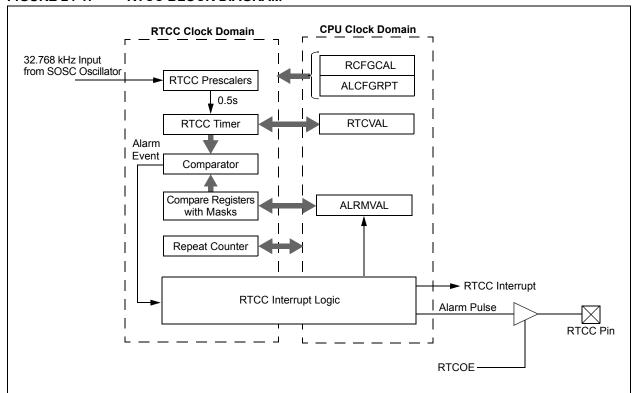

# 24.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices, and its operation. The following are some of the key features of this module:

- · Time: hours, minutes, and seconds

- 24-hour format (military time)

- · Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

FIGURE 24-1: RTCC BLOCK DIAGRAM

#### REGISTER 26-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER (CONTINUED)

bit 2 **BEP:** Byte Enable Polarity bit

1 = Byte enable active-high (PMBE)

0 = Byte enable active-low (PMBE)

bit 1 WRSP: Write Strobe Polarity bit

For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

1 = Write strobe active-high (PMWR)

0 = Write strobe active-low (PMWR)

For Master mode 1 (PMMODE<9:8> = 11):

1 = Enable strobe active-high (PMENB)

0 = Enable strobe active-low (PMENB)

bit 0 RDSP: Read Strobe Polarity bit

For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

1 = Read strobe active-high (PMRD)

$0 = \text{Read strobe active-low } (\overline{PMRD})$

For Master mode 1 (PMMODE<9:8> = 11):

1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

0 = Read/write strobe active-low (PMRD/PMWR)

Note 1: These bits have no effect when their corresponding pins are used as address lines.

#### **TABLE 30-47: COMPARATOR TIMING SPECIFICATIONS**

| AC CHARACTERISTICS |        |                                                       | otherw | vise stat | <b>ed)</b><br>-40°C | ns: 3.0V to 3.6V<br>≤TA ≤+85°C for Industrial<br>≤TA ≤+125°C for Extended |            |

|--------------------|--------|-------------------------------------------------------|--------|-----------|---------------------|---------------------------------------------------------------------------|------------|

| Param<br>No.       | Symbol | Characteristic                                        | Min.   | Тур       | Max.                | Units                                                                     | Conditions |

| 300                | TRESP  | Response Time <sup>(1,2)</sup>                        | _      | 150       | 400                 | ns                                                                        | _          |

| 301                | Тмс2оv | Comparator Mode Change to Output Valid <sup>(1)</sup> | _      | _         | 10                  | μs                                                                        | 1          |

Note 1: Parameters are characterized but not tested.

#### **TABLE 30-48: COMPARATOR MODULE SPECIFICATIONS**

| DC CHARACTERISTICS |        |                                          | Standard Counless oth Operating to | erwise | ture -40°C | ≤Ta ≤+8 | to 3.6V<br>35°C for Industrial<br>125°C for Extended |

|--------------------|--------|------------------------------------------|------------------------------------|--------|------------|---------|------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                           | Min.                               | Тур    | Max.       | Units   | Conditions                                           |

| D300               | VIOFF  | Input Offset Voltage <sup>(1)</sup>      | _                                  | ±10    | _          | mV      |                                                      |

| D301               | VICM   | Input Common Mode Voltage <sup>(1)</sup> | 0                                  | _      | AVDD-1.5V  | V       | _                                                    |

| D302               | CMRR   | Common Mode Rejection Ratio (1)          | -54                                | _      | _          | dB      | _                                                    |

Note 1: Parameters are characterized but not tested.

#### TABLE 30-49: COMPARATOR REFERENCE VOLTAGE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |     |      |       |            |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                    | Min. | Тур | Max. | Units | Conditions |

| VR310              | TSET   | Settling Time <sup>(1)</sup>                                                                                                                                                                                                                      | _    | _   | 10   | μs    |            |

Note 1: Settling time measured while CVRR = 1 and CVR3:CVR0 bits transition from '0000' to '1111'.

#### TABLE 30-50: COMPARATOR REFERENCE VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |           |     |           |       |            |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                    | Min.      | Тур | Max.      | Units | Conditions |

| VRD310             | CVRES  | Resolution                                                                                                                                                                                                                                        | CVRSRC/24 | _   | CVRSRC/32 | LSb   |            |

| VRD311             | CVRAA  | Absolute Accuracy                                                                                                                                                                                                                                 | _         |     | 0.5       | LSb   |            |

| VRD312             | CVRur  | Unit Resistor Value (R)                                                                                                                                                                                                                           | _         | 2k  | _         | Ω     | _          |

<sup>2:</sup> Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

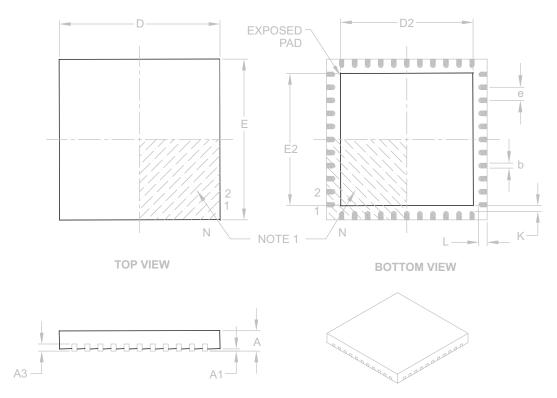

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |                | MILLIMETERS | 3    |

|------------------------|------------------|----------------|-------------|------|

|                        | Dimension Limits | MIN            | NOM         | MAX  |

| Number of Pins         | N                | 44             |             |      |

| Pitch                  | е                |                | 0.65 BSC    |      |

| Overall Height         | A                | 0.80           | 0.90        | 1.00 |

| Standoff               | A1               | 0.00           | 0.02        | 0.05 |

| Contact Thickness      | A3               | 0.20 REF       |             |      |

| Overall Width          | E                |                | 8.00 BSC    |      |

| Exposed Pad Width      | E2               | 6.30           | 6.45        | 6.80 |

| Overall Length         | D                |                | 8.00 BSC    |      |

| Exposed Pad Length     | D2               | 6.30           | 6.45        | 6.80 |

| Contact Width          | b                | 0.25           | 0.30        | 0.38 |

| Contact Length         | L                | 0.30 0.40 0.50 |             |      |

| Contact-to-Exposed Pad | K                | 0.20           | _           | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

### $dsPIC33FJ32GP302/304,\ dsPIC33FJ64GPX02/X04,\ AND\ dsPIC33FJ128GPX02/X04$

| Listen All Messages                               | 230    | AD1CON4 (ADC1 Control 4)                                     | 272 |

|---------------------------------------------------|--------|--------------------------------------------------------------|-----|

| Listen Only                                       | 230    | AD1CSSL (ADC1 Input Scan Select Low) 2                       | 275 |

| Loopback                                          | 230    | AD1PCFGL (ADC1 Port Configuration Low) 2                     | 275 |

| Normal Operation                                  | 230    | CiBUFPNT1 (ECAN Filter 0-3 Buffer Pointer) 2                 | 241 |

| Modulo Addressing                                 | 63     | CiBUFPNT2 (ECAN Filter 4-7 Buffer Pointer) 2                 | 242 |

| Applicability                                     | 64     | CiBUFPNT3 (ECAN Filter 8-11 Buffer Pointer) 2                | 242 |

| Operation Example                                 | 63     | CiBUFPNT4 (ECAN Filter 12-15 Buffer Pointer) 2               | 243 |

| Start and End Address                             | 63     | CiCFG1 (ECAN Baud Rate Configuration 1) 2                    | 239 |

| W Address Register Selection                      | 63     | CiCFG2 (ECAN Baud Rate Configuration 2) 2                    | 240 |

| MPLAB ASM30 Assembler, Linker, Librarian          | 334    | CiCTRL1 (ECAN Control 1)2                                    | 232 |

| MPLAB Integrated Development Environment Software | e 333  | CiCTRL2 (ECAN Control 2)2                                    | 233 |

| MPLAB PM3 Device Programmer                       | 336    | CiEC (ECAN Transmit/Receive Error Count) 2                   | 239 |

| MPLAB REAL ICE In-Circuit Emulator System         | 335    | CiFCTRL (ECAN FIFO Control)                                  | 235 |

| MPLINK Object Linker/MPLIB Object Librarian       | 334    | CiFEN1 (ECAN Acceptance Filter Enable)                       | 241 |

| <br>Ni                                            |        | CiFIFO (ECAN FIFO Status)                                    | 236 |

| N                                                 |        | CiFMSKSEL1 (ECAN Filter 7-0 Mask Selection) 24               |     |

| NVM Module                                        |        | 246                                                          |     |

| Register Map                                      | 60     | CilNTE (ECAN Interrupt Enable)                               | 238 |

| ^                                                 |        | CilNTF (ECAN Interrupt Flag)                                 |     |

| 0                                                 |        | CiRXFnEID (ECAN Acceptance Filter n                          |     |

| Open-Drain Configuration                          | 160    | Extended Identifier)                                         | 245 |

| Output Compare                                    | 203    | CiRXFnSID (ECAN Acceptance Filter n                          |     |

| P                                                 |        | Standard Identifier)                                         | 244 |

| P                                                 |        | CiRXFUL1 (ECAN Receive Buffer Full 1)                        |     |

| Packaging                                         | 407    | CiRXFUL2 (ECAN Receive Buffer Full 2)                        |     |

| Marking                                           | 407    | CiRXMnEID (ECAN Acceptance Filter Mask n                     | 0   |

| Peripheral Module Disable (PMD)                   | 154    | Extended Identifier)                                         | 247 |

| Pinout I/O Descriptions (table)                   |        | CiRXMnSID (ECAN Acceptance Filter Mask n                     |     |

| PMD Module                                        |        | Standard Identifier)                                         | 247 |

| Register Map                                      | 60     | CiRXOVF1 (ECAN Receive Buffer Overflow 1) 2                  |     |

| PORTA                                             |        | CiRXOVF1 (ECAN Receive Buffer Overflow 1) 2                  |     |

| Register Map                                      | 58. 59 | ,                                                            |     |

| PORTB                                             | ,      | CiTRBnSID (ECAN Buffer n Standard Identifier) 29<br>252, 254 | ЭΙ, |

| Register Map                                      | 59     | •                                                            | 250 |

| Power-on Reset (POR)                              |        | CiTRmnCON (ECAN TX/RX Buffer m Control) 2                    |     |

| Power-Saving Features                             |        | CiVEC (ECAN Interrupt Code)                                  |     |

| Clock Frequency and Switching                     |        | CLKDIV (Clock Divisor)                                       |     |

| Program Address Space                             |        | CORCON (Core Control)                                        |     |

| Construction                                      |        | DCICON1 (DCI Control 1)                                      |     |

| Data Access from Program Memory Using             | 00     | DCICON2 (DCI Control 2)                                      |     |

| Program Space Visibility                          | 60     | DCICON3 (DCI Control 3)                                      |     |

| Data Access from Program Memory Using             | 03     | DCISTAT (DCI Status)                                         |     |

| Table Instructions                                | 69     | DMACS0 (DMA Controller Status 0) 1                           |     |

|                                                   |        | DMACS1 (DMA Controller Status 1) 1                           |     |

| Data Access from, Address Generation              |        | DMAxCNT (DMA Channel x Transfer Count) 1                     |     |

| Memory Map                                        | 35     | DMAxCON (DMA Channel x Control) 1                            |     |

| Table Read Instructions                           | 00     | DMAxPAD (DMA Channel x Peripheral Address) 1                 |     |

| TBLRDH                                            |        | DMAxREQ (DMA Channel x IRQ Select) 1                         |     |

| TBLRDL                                            |        | DMAxSTA (DMA Channel x RAM Start Address A). 1               | 134 |

| Visibility Operation                              | 69     | DMAxSTB (DMA Channel x RAM Start Address B). 1               | 134 |

| Program Memory                                    |        | DSADR (Most Recent DMA RAM Address) 1                        | 139 |

| Interrupt Vector                                  |        | I2CxCON (I2Cx Control)2                                      | 216 |

| Organization                                      |        | I2CxMSK (I2Cx Slave Mode Address Mask) 2                     | 220 |

| Reset Vector                                      | 36     | I2CxSTAT (I2Cx Status)2                                      | 218 |

| R                                                 |        | IFS0 (Interrupt Flag Status 0)                               |     |

|                                                   |        | IFS1 (Interrupt Flag Status 1)                               | 105 |

| Reader Response                                   | 432    | IFS2 (Interrupt Flag Status 2)                               | 107 |

| Register Map                                      |        | IFS3 (Interrupt Flag Status 3) 101, 1                        | 108 |

| CRC                                               |        | IFS4 (Interrupt Flag Status 4) 102, 1                        |     |

| Dual Comparator                                   |        | INTCON1 (Interrupt Control 1)                                |     |

| Parallel Master/Slave Port                        |        | INTCON2 (Interrupt Control 2)                                |     |

| Real-Time Clock and Calendar                      | 58     | INTTREG Interrupt Control and Status Register 1              |     |

| Registers                                         |        | IPC0 (Interrupt Priority Control 0)                          |     |

| AD1CHS0 (ADC1 Input Channel 0 Select              | 274    | IPC1 (Interrupt Priority Control 1)                          |     |

| AD1CHS123 (ADC1 Input Channel 1, 2, 3 Select)     | ) 273  | IPC11 (Interrupt Priority Control 11)                        |     |

| AD1CON1 (ADC1 Control 1)                          |        | IPC11 (Interrupt Priority Control 14)                        | 121 |

| AD1CON2 (ADC1 Control 2)                          | 270    | IPC14 (Interrupt Priority Control 14)                        | 122 |

| AD1CON3 (ADC1 Control 3)                          |        | IPC16 (Interrupt Priority Control 16)                        |     |

| •                                                 |        | ii o io (iiiteirupt Filority Contitol 10)                    | د2  |