Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decalis                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp202-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 Special MCU Features

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

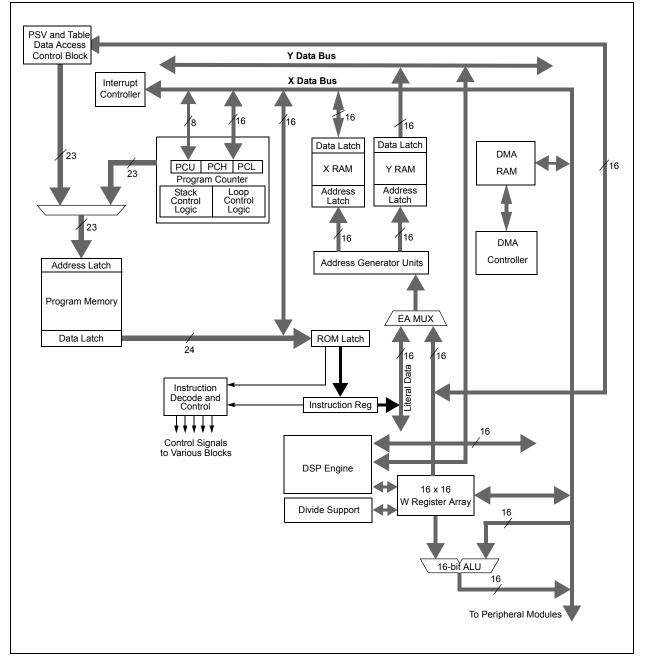

#### FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 CPU CORE BLOCK DIAGRAM

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS70   |  |

|--------|--|

| 292G   |  |

| i-page |  |

| 42     |  |

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8       | Bit 7        | Bit 6    | Bit 5    | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|------------------------------|--------|--------|--------|--------|---------|-------------|--------------|----------|----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |                              |        |        |        |        |         | Working Re  | gister 0     |          |          |                 |              |              |         |       | 0000          |

| WREG1    | 0002        |        |                              |        |        |        |        |         | Working Re  | gister 1     |          |          |                 |              |              |         |       | 0000          |

| WREG2    | 0004        |        |                              |        |        |        |        |         | Working Re  | gister 2     |          |          |                 |              |              |         |       | 0000          |

| WREG3    | 0006        |        |                              |        |        |        |        |         | Working Re  | gister 3     |          |          |                 |              |              |         |       | 0000          |

| WREG4    | 0008        |        |                              |        |        |        |        |         | Working Re  | gister 4     |          |          |                 |              |              |         |       | 0000          |

| WREG5    | 000A        |        |                              |        |        |        |        |         | Working Re  | gister 5     |          |          |                 |              |              |         |       | 0000          |

| WREG6    | 000C        |        |                              |        |        |        |        |         | Working Re  | gister 6     |          |          |                 |              |              |         |       | 0000          |

| WREG7    | 000E        |        |                              |        |        |        |        |         | Working Re  | gister 7     |          |          |                 |              |              |         |       | 0000          |

| WREG8    | 0010        |        |                              |        |        |        |        |         | Working Re  | gister 8     |          |          |                 |              |              |         |       | 0000          |

| WREG9    | 0012        |        |                              |        |        |        |        |         | Working Re  | gister 9     |          |          |                 |              |              |         |       | 0000          |

| WREG10   | 0014        |        |                              |        |        |        |        | ,       | Working Reg | jister 10    |          |          |                 |              |              |         |       | 0000          |

| WREG11   | 0016        |        |                              |        |        |        |        |         | Working Reg | jister 11    |          |          |                 |              |              |         |       | 0000          |

| WREG12   | 0018        |        |                              |        |        |        |        | ,       | Working Reg | jister 12    |          |          |                 |              |              |         |       | 0000          |

| WREG13   | 001A        |        |                              |        |        |        |        |         | Working Reg | jister 13    |          |          |                 |              |              |         |       | 0000          |

| WREG14   | 001C        |        |                              |        |        |        |        |         | Working Reg | jister 14    |          |          |                 |              |              |         |       | 0000          |

| WREG15   | 001E        |        | Working Register 15          |        |        |        |        |         |             |              | 0800     |          |                 |              |              |         |       |               |

| SPLIM    | 0020        |        | Stack Pointer Limit Register |        |        |        |        |         |             |              | XXXX     |          |                 |              |              |         |       |               |

| ACCAL    | 0022        |        | ACCAL                        |        |        |        |        |         |             |              |          | XXXX     |                 |              |              |         |       |               |

| ACCAH    | 0024        |        |                              |        |        |        |        |         | ACCA        | Н            |          |          |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026        |        |                              |        | ACCA<  | 39>    |        |         |             |              |          |          | AC              | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028        |        |                              |        |        |        |        |         | ACCB        | L            |          |          |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A        |        |                              |        |        |        |        |         | ACCB        | Н            |          |          |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C        |        |                              |        | ACCB<  | 39>    |        |         |             |              |          |          | AC              | CBU          |              |         |       | XXXX          |

| PCL      | 002E        |        |                              |        |        |        |        | Program | Counter Lov | w Word Reg   | ister    |          |                 |              |              |         |       | XXXX          |

| PCH      | 0030        | _      |                              | —      |        |        | _      | _       | _           |              |          | Progra   | am Counter      | High Byte F  | Register     |         |       | 0000          |

| TBLPAG   | 0032        | _      |                              | —      | _      |        | —      | _       | —           |              |          | Table    | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034        | _      |                              | —      |        |        | _      | _       | _           |              | Progr    | am Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |                              |        |        |        |        | Repe    | at Loop Cou | nter Registe | r        |          |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038        |        |                              |        |        |        |        |         | DCOUNT<     | :15:0>       |          |          |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A        |        |                              |        |        |        |        | DOST    | TARTL<15:1  | >            |          |          |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C        | _      |                              | _      | _      | _      | _      | _       | _           | _            | _        |          |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E        |        | DOENDL<15:1> 0               |        |        |        |        |         |             |              | XXXX     |          |                 |              |              |         |       |               |

| DOENDH   | 0040        | _      | _                            | _      | _      | _      | _      | _       | _           | _            | _        |          |                 | DOE          | ENDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OB                           | SA     | SB     | OAB    | SAB    | DA      | DC          |              | IPL<2:0> |          | RA              | Ν            | OV           | Z       | С     | 0000          |

| CORCON   | 0044        | _      | _                            | _      | US     | EDT    |        | DL<2:0> |             | SATA         | SATB     | SATDW    | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

© 2007-2012 Microchip Technology Inc.

# TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                              | Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1 |                            |  |  |   |         |  | Bit 0 | All<br>Resets |      |      |  |  |   |      |

|----------|-------------|--------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|---|---------|--|-------|---------------|------|------|--|--|---|------|

| MODCON   | 0046        | XMODEN | YMODEN                              | —                                                                                                                                                                                                | BWM<3:0> YWM<3:0> XWM<3:0> |  |  |   |         |  |       |               |      | 0000 |  |  |   |      |

| XMODSRT  | 0048        |        | XS<15:1>                            |                                                                                                                                                                                                  |                            |  |  |   |         |  | 0     | XXXX          |      |      |  |  |   |      |

| XMODEND  | 004A        |        | XE<15:1>                            |                                                                                                                                                                                                  |                            |  |  |   |         |  |       | 1             | XXXX |      |  |  |   |      |

| YMODSRT  | 004C        |        |                                     |                                                                                                                                                                                                  |                            |  |  | Y | S<15:1> |  |       |               |      |      |  |  | 0 | XXXX |

| YMODEND  | 004E        |        | YE<15:1>                            |                                                                                                                                                                                                  |                            |  |  |   |         |  |       | 1             | XXXX |      |  |  |   |      |

| XBREV    | 0050        | BREN   | BREN XB<14:0>                       |                                                                                                                                                                                                  |                            |  |  |   |         |  |       | XXXX          |      |      |  |  |   |      |

| DISICNT  | 0052        | _      | Disable Interrupts Counter Register |                                                                                                                                                                                                  |                            |  |  |   |         |  |       | XXXX          |      |      |  |  |   |      |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 architecture uses a 24 bit wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### 4.8.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-39 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

### TABLE 4-39: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access                                     | Program Space Address |           |                                    |                    |     |  |  |  |

|--------------------------|--------------------------------------------|-----------------------|-----------|------------------------------------|--------------------|-----|--|--|--|

| Access Type              | Space                                      | <23>                  | <22:16>   | <15>                               | <14:1>             | <0> |  |  |  |

| Instruction Access       | User                                       | 0                     |           | 0                                  |                    |     |  |  |  |

| (Code Execution)         | de Execution) 0xx xxxx xxxx xxxx xxxx xxx0 |                       |           |                                    |                    |     |  |  |  |

| TBLRD/TBLWT              | User                                       | TB                    | LPAG<7:0> |                                    | Data EA<15:0>      |     |  |  |  |

| (Byte/Word Read/Write)   |                                            | 0                     | XXX XXXX  | XXXX XX                            | ****               |     |  |  |  |

|                          | Configuration                              | TBLPAG<7:0>           |           | Data EA<15:0>                      |                    |     |  |  |  |

|                          |                                            | 1                     | XXX XXXX  | XXXX X                             | XXX XXXX XXXX      |     |  |  |  |

| Program Space Visibility | User                                       | 0                     | PSVPAG<7  | <7:0> Data EA<14:0> <sup>(1)</sup> |                    |     |  |  |  |

| (Block Remap/Read)       |                                            | 0                     | XXXX XXXX | ĸ                                  | XXX XXXX XXXX XXXX |     |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

NOTES:

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- bit 3 CF: Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2 Unimplemented: Read as '0'

- bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 39. "Oscillator (Part III)"** (DS70216) in the *"dsPIC33F/PIC24H Family Reference Manual"* (available from the Microchip website) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

| REGISTER      | 9-2: CLKD                  | DIV: CLOCK DI       | VISOR RE           | GISTER <sup>(2)</sup> |                 |                    |           |

|---------------|----------------------------|---------------------|--------------------|-----------------------|-----------------|--------------------|-----------|

| R/W-0         | R/W-0                      | R/W-1               | R/W-1              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| ROI           |                            | DOZE<2:0>           |                    | DOZEN <sup>(1)</sup>  |                 | FRCDIV<2:0>        |           |

| bit 15        |                            |                     |                    |                       |                 |                    | bit 8     |

| R/W-0         | R/W-1                      | U-0                 | R/W-0              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| PLLPC         | ST<1:0>                    | —                   |                    |                       | PLLPRE<4:0      | >                  |           |

| bit 7         |                            |                     |                    |                       |                 |                    | bit C     |

| Legend:       |                            | v = Value set f     | rom Configu        | ration bits on P      | OR              |                    |           |

| R = Readable  | a bit                      | W = Writable b      | -                  |                       | nented bit, rea | d as '0'           |           |

| -n = Value at |                            | '1' = Bit is set    | Л                  | '0' = Bit is cle      |                 |                    |           |

|               | PUR                        | I = DILIS SEL       |                    |                       | areu            | x = Bit is unki    | IOWII     |

| bit 15        | ROI: Recove                | er on Interrupt bit |                    |                       |                 |                    |           |

|               |                            | ts clears the DO    |                    | the processor c       | lock/periphera  | l clock ratio is s | et to 1:1 |

|               |                            | ts have no effect   |                    |                       |                 |                    |           |

| bit 14-12     | DOZE<2:0>:                 | Processor Cloc      | k Reduction        | Select bits           |                 |                    |           |

|               | 111 = Fcy/1                | 28                  |                    |                       |                 |                    |           |

|               | 110 = Fcy/6                |                     |                    |                       |                 |                    |           |

|               | 101 = Fcy/3                |                     |                    |                       |                 |                    |           |

|               | 100 = Fcy/1<br>011 = Fcy/8 |                     |                    |                       |                 |                    |           |

|               | 010 = Fcy/4                |                     |                    |                       |                 |                    |           |

|               | 001 = Fcy/2                |                     |                    |                       |                 |                    |           |

|               | 000 = Fcy/1                |                     |                    |                       |                 |                    |           |

| bit 11        | DOZEN: Doz                 | ze Mode Enable      | bit <sup>(1)</sup> |                       |                 |                    |           |

|               |                            | 2:0> field specifie |                    |                       | ipheral clocks  | and the process    | or clocks |

| bit 10-8      |                            | >: Internal Fast    |                    |                       | S               |                    |           |

|               | 111 <b>= FRC (</b>         | divide by 256       |                    |                       |                 |                    |           |

|               | 110 <b>= FRC c</b>         |                     |                    |                       |                 |                    |           |

|               | 101 <b>= FRC d</b>         |                     |                    |                       |                 |                    |           |

|               | 100 <b>= FRC</b> (         |                     |                    |                       |                 |                    |           |

|               | 011 = FRC o<br>010 = FRC o |                     |                    |                       |                 |                    |           |

|               | 010 = FRC (<br>001 = FRC ( | -                   |                    |                       |                 |                    |           |

|               |                            | divide by 1 (defai  | ult)               |                       |                 |                    |           |

| bit 7-6       |                            | I:0>: PLL VCO C     |                    | er Select bits (al    | so denoted as   | 'N2', PLL posts    | caler)    |

|               | 11 = Output/               |                     |                    |                       |                 | , .                | ,         |

|               | 10 = Reserv                |                     |                    |                       |                 |                    |           |

|               | 01 = Output/               |                     |                    |                       |                 |                    |           |

|               | 00 = Output/               | 2                   |                    |                       |                 |                    |           |

| bit 5         | Unimpleme                  | nted: Read as '0    | ,                  |                       |                 |                    |           |

| bit 4-0       | PLLPRE<4:                  | 0>: PLL Phase D     | etector Inpu       | ıt Divider bits (a    | lso denoted as  | s 'N1', PLL pres   | caler)    |

|               | 11111 <b>= Inp</b>         | ut/33               |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | 00000 <b>= Inp</b>         | ut/2 (default)      |                    |                       |                 |                    |           |

|               | 00001 = Inp                |                     |                    |                       |                 |                    |           |

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

2: This register is reset only on a Power-on Reset (POR).

## 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

#### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0        | R/W-0        | R/W-0             | U-0             | U-0              | U-0              | U-0              | U-0   |

|--------------|--------------|-------------------|-----------------|------------------|------------------|------------------|-------|

| FRMEN        | SPIFSD       | FRMPOL            | —               | —                | —                | —                | _     |

| bit 15       |              |                   |                 |                  |                  |                  | bit 8 |

|              |              |                   |                 |                  |                  |                  |       |

| U-0          | U-0          | U-0               | U-0             | U-0              | U-0              | R/W-0            | U-0   |

| —            |              |                   | —               | —                | —                | FRMDLY           | —     |

| bit 7        |              |                   |                 |                  |                  |                  | bit C |

| Legend:      |              |                   |                 |                  |                  |                  |       |

| R = Readab   | lo hit       | W = Writable      | hit             | II – Unimploy    | mented bit, read | d as '0'         |       |

|              |              |                   |                 | •                |                  |                  |       |

| -n = Value a | TPOR         | '1' = Bit is set  |                 | '0' = Bit is cle | ared             | x = Bit is unkno | own   |

| bit 15       | FRMEN: Fra   | imed SPIx Supp    | ort bit         |                  |                  |                  |       |

|              |              | SPIx support en   |                 | oin used as fram | ne sync pulse ir | nput/output)     |       |

|              | 0 = Framed   | SPIx support dis  | sabled          |                  |                  |                  |       |

| bit 14       | SPIFSD: Fra  | ame Sync Pulse    | Direction Co    | ntrol bit        |                  |                  |       |

|              | •            | ync pulse input   | • •             |                  |                  |                  |       |

|              | 0 = Frame sy | ync pulse outpu   | t (master)      |                  |                  |                  |       |

| bit 13       | FRMPOL: Fi   | rame Sync Puls    | e Polarity bit  |                  |                  |                  |       |

|              |              | ync pulse is acti |                 |                  |                  |                  |       |

|              | 0 = Frame sy | ync pulse is acti | ve-low          |                  |                  |                  |       |

| bit 12-2     | Unimpleme    | nted: Read as '   | 0'              |                  |                  |                  |       |

| bit 1        | FRMDLY: Fr   | ame Sync Pulse    | e Edge Selec    | t bit            |                  |                  |       |

|              | 1 = Frame sy | ync pulse coinci  | des with first  | bit clock        |                  |                  |       |

|              | 0 = Frame sy | ync pulse prece   | des first bit c | lock             |                  |                  |       |

| hit O        |              | ntad. Daad as (   | o'              |                  |                  |                  |       |

# REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

bit 0 **Unimplemented:** Read as '0' This bit must not be set to '1' by the user application.

### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

```

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en532311

```

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| REGISTER   | R 21-3: AD1C0                  | ON3: ADC1 C                     |                 | EGISTER 3            |                 |                 |       |

|------------|--------------------------------|---------------------------------|-----------------|----------------------|-----------------|-----------------|-------|

| R/W-0      | U-0                            | U-0                             | R/W-0           | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

| ADRC       |                                |                                 |                 |                      | SAMC<4:0>(      | 1)              |       |

| bit 15     |                                |                                 |                 |                      |                 |                 | bit   |

| R/W-0      | R/W-0                          | R/W-0                           | R/W-0           | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

|            |                                |                                 | ADCS<           | :7:0> <sup>(2)</sup> |                 |                 |       |

| bit 7      |                                |                                 |                 |                      |                 |                 | bit   |

| Legend:    |                                |                                 |                 |                      |                 |                 |       |

| R = Reada  | ble bit                        | W = Writable b                  | oit             | U = Unimpler         | nented bit, rea | ad as '0'       |       |

| -n = Value | at POR                         | '1' = Bit is set                |                 | '0' = Bit is cle     | ared            | x = Bit is unkr | nown  |

| bit 15     |                                | Conversion Clo                  | ck Source bit   |                      |                 |                 |       |

|            | 1 = ADC inter<br>0 = Clock der | nal RC clock<br>ived from syste | m clock         |                      |                 |                 |       |

| bit 14-13  |                                | ted: Read as '0                 |                 |                      |                 |                 |       |

| bit 12-8   |                                | Auto Sample T                   |                 |                      |                 |                 |       |

| 511 12 0   | 11111 = <b>31</b> T            | -                               |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | 00001 <b>= 1 T</b> A           |                                 |                 |                      |                 |                 |       |

| h:+ 7 0    | 00000 = 0 TA                   |                                 |                 | -+  -:+-( <b>2</b> ) |                 |                 |       |

| bit 7-0    |                                | ADC Conversio                   | on Clock Selec  | Ct Dits -            |                 |                 |       |

|            | •                              | Reserved                        |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | 01000000 =                     | Reserved                        |                 |                      |                 |                 |       |

|            |                                | TCY · (ADCS<7                   | 7:0> + 1) = 64  | • Tcy = Tad          |                 |                 |       |

|            | •                              |                                 | , -             |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | •                              |                                 |                 |                      |                 |                 |       |

|            | 00000010 =                     | TCY · (ADCS<7                   | 7:0> + 1) = 3 · | TCY = TAD            |                 |                 |       |

|            |                                | Тсү · (ADCS<7<br>Тсү · (ADCS<7  |                 |                      |                 |                 |       |

| Note 1:    | This bit only used i           | f AD1CON1<7:                    | 5> (SSRC<2:     | <b>0&gt;) =</b> 111. |                 |                 |       |

|            | This bit is not used           |                                 |                 | ,                    |                 |                 |       |

#### 40010

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# REGISTER 24-6: RTCVAL (WHEN RTCPTR<1:0> = 01): WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x     | R/W-x |

|--------|-----|-----|-----|-----|-------|-----------|-------|

| —      | —   |     |     | —   |       | WDAY<2:0> |       |

| bit 15 |     |     |     |     |       |           | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| _     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### **REGISTER 24-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------|-------------|-------|-------|-------|---------|-------|

| —      |       | MINTEN<2:0> |       |       | MINON | IE<3:0> |       |

| bit 15 |       |             |       |       |       |         | bit 8 |

|        |       |             |       |       |       |         |       |

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|        |       |             |       |       |       |         |       |

| —     | SECTEN<2:0> | SECONE<3:0> |

|-------|-------------|-------------|

| bit 7 |             | bit 0       |

|       |             |             |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |

| bit 7     | Unimplemented: Read as '0'                                                                   |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |

© 2007-2012 Microchip Technology Inc.

| DC CHARACTERISTICS |                                                                                                                             | Standar<br>(unless<br>Operatin                                                                                 | otherwi | se state | ed)  | : <b>3.0V to 3.6V</b><br>≤TA ≤+85°C for Industrial |                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|----------|------|----------------------------------------------------|-----------------------------------------------|

|                    |                                                                                                                             |                                                                                                                |         |          |      | TA ≤+125°C for Extended                            |                                               |

| Param.             | Symbol                                                                                                                      | Characteristic                                                                                                 | Min.    | Тур.     | Max. | Units                                              | Conditions                                    |

|                    |                                                                                                                             | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - RA2, RA7-<br>RA10, RB10, RB11, RB7, RB4,<br>RC3-RC9   | _       | _        | 0.4  | V                                                  | Io∟ ≤3 mA, Vod = 3.3V<br>See <b>Note 1</b>    |

| DO10               | Vol                                                                                                                         | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA0, RA1,<br>RB0-RB3, RB5, RB6, RB8, RB9,             | _       | _        | 0.4  | V                                                  | Io∟ ⊴6 mA, Vod = 3.3V<br>See <b>Note 1</b>    |

|                    |                                                                                                                             | RB12-RB15, RC0-RC2<br><b>Output Low Voltage</b><br>I/O Pins:<br>8x Sink Driver Pins - RA3, RA4                 |         | _        | 0.4  | v                                                  | IoL ≤10 mA, VDD = 3.3V<br>See <b>Note 1</b>   |

|                    |                                                                                                                             | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9 | 2.4     |          |      | V                                                  | Іон ≥ -3 mA, Vod = 3.3V<br>See <b>Note 1</b>  |

| DO20 Voн           | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2 | 2.4                                                                                                            | _       | _        | V    | Іон ≥ -6 mA, Vod = 3.3V<br>See <b>Note 1</b>       |                                               |

|                    |                                                                                                                             | <b>Output High Voltage</b><br>I/O Pins:<br>8x Source Driver Pins - RA4,<br>RA3                                 | 2.4     | _        | _    | V                                                  | IOH ≥ -10 mA, VDD = 3.3V<br>See <b>Note 1</b> |

|                    |                                                                                                                             | Output High Voltage<br>I/O Pins:                                                                               | 1.5     | _        | _    |                                                    | IOH ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>  |

|                    |                                                                                                                             | 2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9                                     | 2.0     | —        | _    | V                                                  | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>  |

|                    |                                                                                                                             |                                                                                                                | 3.0     | _        | _    |                                                    | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>  |

|                    |                                                                                                                             | <b>Output High Voltage</b><br>4x Source Driver Pins - RA0,                                                     | 1.5     | —        | —    |                                                    | Iон ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b> |

| DO20A Voh1         | Vон1                                                                                                                        | RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2                                                        | 2.0     | —        | —    | V                                                  | IOH ≥ -11 mA, VDD = 3.3V<br>See <b>Note 1</b> |

|                    |                                                                                                                             |                                                                                                                | 3.0     | _        | _    |                                                    | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>  |

|                    |                                                                                                                             | Output High Voltage<br>I/O Pins:                                                                               | 1.5     | _        | _    |                                                    | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b> |

|                    |                                                                                                                             | 8x Source Driver Pins - RA3,<br>RA4                                                                            | 2.0     | _        | _    | V                                                  | Юн ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>  |

|                    |                                                                                                                             |                                                                                                                | 3.0     | _        |      |                                                    | Іон ≥ -4 mA, Voo = 3.3V<br>See <b>Note 1</b>  |

#### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

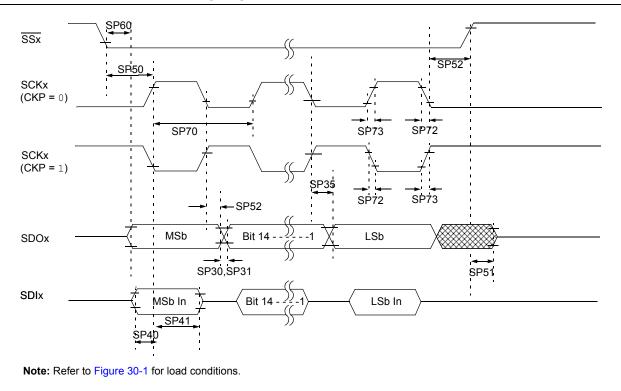

# FIGURE 30-14: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| TABLE 30-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| AC CHARACTERISTICS |            |                            | Standard Op<br>(unless other<br>Operating ten | rwise sta   | a <b>ted)</b><br>e -40°C | ons: 3.0V to 3.6V<br>C $\leq$ TA $\leq$ +85°C for Industrial<br>C $\leq$ TA $\leq$ +125°C for Extended |                                             |

|--------------------|------------|----------------------------|-----------------------------------------------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Param.             | Symbol     | Charac                     | Characteristic                                |             | Max                      | Units                                                                                                  | Conditions                                  |

| IS10               | TLO:SCL    | Clock Low Time             | 100 kHz mode                                  | 4.7         | —                        | μs                                                                                                     | Device must operate at a minimum of 1.5 MHz |

|                    |            |                            | 400 kHz mode                                  | 1.3         | _                        | μs                                                                                                     | Device must operate at a minimum of 10 MHz  |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.5         |                          | μs                                                                                                     | —                                           |

| IS11               | THI:SCL    | Clock High Time            | 100 kHz mode                                  | 4.0         | —                        | μs                                                                                                     | Device must operate at a minimum of 1.5 MHz |

|                    |            |                            | 400 kHz mode                                  | 0.6         | —                        | μs                                                                                                     | Device must operate at a minimum of 10 MHz  |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.5         |                          | μs                                                                                                     | —                                           |

| IS20               | TF:SCL     | SDAx and SCLx              | 100 kHz mode                                  |             | 300                      | ns                                                                                                     | CB is specified to be from                  |

|                    |            | Fall Time                  | 400 kHz mode                                  | 20 + 0.1 Св | 300                      | ns                                                                                                     | 10 to 400 pF                                |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | —           | 100                      | ns                                                                                                     |                                             |

| IS21               | TR:SCL     | SDAx and SCLx              | 100 kHz mode                                  | —           | 1000                     | ns                                                                                                     | CB is specified to be from                  |

|                    |            | Rise Time                  | 400 kHz mode                                  | 20 + 0.1 Св | 300                      | ns                                                                                                     | 10 to 400 pF                                |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | —           | 300                      | ns                                                                                                     |                                             |

| IS25               | TSU:DAT    |                            | 100 kHz mode                                  | 250         |                          | ns                                                                                                     | —                                           |

|                    | Setup Time | 400 kHz mode               | 100                                           | _           | ns                       |                                                                                                        |                                             |

|                    |            | 1 MHz mode <sup>(1)</sup>  | 100                                           |             | ns                       |                                                                                                        |                                             |

| IS26               | THD:DAT    |                            | 100 kHz mode                                  | 0           |                          | μs                                                                                                     | —                                           |

|                    | Hold       | Hold Time                  | 400 kHz mode                                  | 0           | 0.9                      | μs                                                                                                     |                                             |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0           | 0.3                      | μs                                                                                                     |                                             |

| IS30               | TSU:STA    | Start Condition            | 100 kHz mode                                  | 4.7         |                          | μs                                                                                                     | Only relevant for Repeated                  |

|                    |            | Setup Time                 | 400 kHz mode                                  | 0.6         |                          | μs                                                                                                     | Start condition                             |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.25        |                          | μs                                                                                                     |                                             |

| IS31               | THD:STA    | Start Condition            | 100 kHz mode                                  | 4.0         | —                        | μs                                                                                                     | After this period, the first                |

|                    |            | Hold Time                  | 400 kHz mode                                  | 0.6         | —                        | μs                                                                                                     | clock pulse is generated                    |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.25        | —                        | μs                                                                                                     |                                             |

| IS33               | Tsu:sto    | Stop Condition             | 100 kHz mode                                  | 4.7         |                          | μs                                                                                                     | —                                           |

|                    |            | Setup Time                 | 400 kHz mode                                  | 0.6         |                          | μs                                                                                                     |                                             |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.6         |                          | μs                                                                                                     |                                             |

| IS34               | THD:ST     | Stop Condition             | 100 kHz mode                                  | 4000        |                          | ns                                                                                                     |                                             |

|                    | 0          | Hold Time                  | 400 kHz mode                                  | 600         | —                        | ns                                                                                                     |                                             |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 250         |                          | ns                                                                                                     |                                             |

| IS40               | TAA:SCL    | Output Valid<br>From Clock | 100 kHz mode                                  | 0           | 3500                     | ns                                                                                                     |                                             |

|                    |            |                            | 400 kHz mode                                  | 0           | 1000                     | ns                                                                                                     |                                             |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0           | 350                      | ns                                                                                                     |                                             |

| IS45               | TBF:SDA    | Bus Free Time              | 100 kHz mode                                  | 4.7         | —                        | μs                                                                                                     | Time the bus must be free                   |

|                    |            |                            | 400 kHz mode                                  | 1.3         | —                        | μs                                                                                                     | before a new transmission can start         |

|                    |            |                            | 1 MHz mode <sup>(1)</sup>                     | 0.5         | —                        | μs                                                                                                     |                                             |

| IS50               | Св         | Bus Capacitive Lo          | bading                                        | —           | 400                      | pF                                                                                                     | —                                           |

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

|              |        |                                |           | otherwi   | se stateo<br>rature | <b>d)</b><br>-40°C ≤ | : <b>3.0V to 3.6V</b><br>TA ≤+85°C for Industrial<br>TA ≤+125°C for Extended |

|--------------|--------|--------------------------------|-----------|-----------|---------------------|----------------------|------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                 | Min.      | Тур       | Max.                | Units                | Conditions                                                                   |

|              |        | ADC Accuracy (10-bit Mode      | ) – Meas  | urement   | ts with e           | xternal              | VREF+/VREF-                                                                  |

| AD20b        | Nr     | Resolution <sup>(1)</sup>      | 1(        | ) data bi | ts                  | bits                 | —                                                                            |

| AD21b        | INL    | Integral Nonlinearity          | -1.5      | _         | +1.5                | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD22b        | DNL    | Differential Nonlinearity      | > -1      | _         | < 1                 | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD23b        | Gerr   | Gain Error                     | —         | 3         | 6                   | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD24b        | EOFF   | Offset Error                   | —         | 2         | 5                   | LSb                  | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V                             |

| AD25b        | —      | Monotonicity                   | —         | —         | _                   | _                    | Guaranteed                                                                   |

|              |        | ADC Accuracy (10-bit Mode      | e) – Meas | uremen    | ts with ir          | nternal V            | VREF+/VREF-                                                                  |

| AD20b        | Nr     | Resolution <sup>(1)</sup>      | 1(        | ) data bi | ts                  | bits                 | —                                                                            |

| AD21b        | INL    | Integral Nonlinearity          | -1        | —         | +1                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD22b        | DNL    | Differential Nonlinearity      | > -1      | —         | < 1                 | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD23b        | Gerr   | Gain Error                     | 3         | 7         | 15                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD24b        | EOFF   | Offset Error                   | 1.5       | 3         | 7                   | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD25b        | —      | Monotonicity                   |           |           | _                   |                      | Guaranteed                                                                   |

|              |        | Dynamic                        | Performa  | nce (10-  | bit Mode            | e)                   |                                                                              |

| AD30b        | THD    | Total Harmonic Distortion      | _         |           | -64                 | dB                   | —                                                                            |

| AD31b        | SINAD  | Signal to Noise and Distortion | 57        | 58.5      | _                   | dB                   | _                                                                            |

| AD32b        | SFDR   | Spurious Free Dynamic<br>Range | 72        | _         |                     | dB                   | _                                                                            |

| AD33b        | Fnyq   | Input Signal Bandwidth         | _         |           | 550                 | kHz                  | —                                                                            |

| AD34b        | ENOB   | Effective Number of Bits       | 9.16      | 9.4       | _                   | bits                 |                                                                              |

## TABLE 30-43: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

| -            | AC<br>TERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |          |           |           |          |                                                  |  |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-----------|----------|--------------------------------------------------|--|

| Param<br>No. | Symbol          | Characteristic                                                                                                                   | Min      | Тур       | Max       | Units    | Conditions                                       |  |

|              |                 | C Accuracy (10-bit Mode)                                                                                                         | Maggi    | romonto   | with Ex   | tornal V |                                                  |  |

|              | 1               | Resolution <sup>(3)</sup>                                                                                                        |          |           |           | 1        |                                                  |  |

| HAD20b       | Nr              |                                                                                                                                  |          | 0 data bi |           | bits     | —                                                |  |

| HAD21b       | INL             | Integral Nonlinearity                                                                                                            | -3       | _         | 3         | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD22b       | DNL             | Differential Nonlinearity                                                                                                        | > -1     | —         | < 1       | LSb      | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |

| HAD23b       | Gerr            | Gain Error                                                                                                                       | -5       | —         | 6         | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD24b       | EOFF            | Offset Error                                                                                                                     | -1       | —         | 5         | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

|              | AD              | C Accuracy (10-bit Mode)                                                                                                         | – Measu  | irement   | s with In | ternal V | REF+/VREF- <sup>(1)</sup>                        |  |

| HAD20b       | Nr              | Resolution <sup>(3)</sup>                                                                                                        | 1        | 0 data bi | ts        | bits     | _                                                |  |

| HAD21b       | INL             | Integral Nonlinearity                                                                                                            | -2       |           | 2         | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| HAD22b       | DNL             | Differential Nonlinearity                                                                                                        | > -1     |           | < 1       | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| HAD23b       | Gerr            | Gain Error                                                                                                                       | -5       | —         | 15        | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| HAD24b       | EOFF            | Offset Error                                                                                                                     | -1.5     | —         | 7         | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

|              | •               | Dynamic Po                                                                                                                       | erformar | nce (10-l | oit Mode  | (2)      |                                                  |  |

| HAD33b       | Fnyq            | Input Signal Bandwidth                                                                                                           | _        |           | 400       | kHz      | _                                                |  |

# TABLE 31-16: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

**2:** These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.