Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

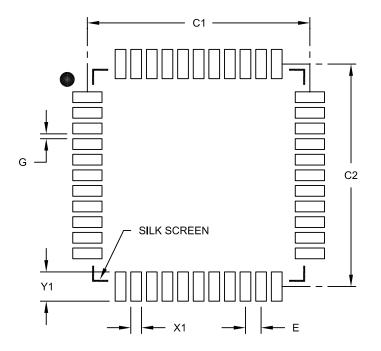

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp202-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

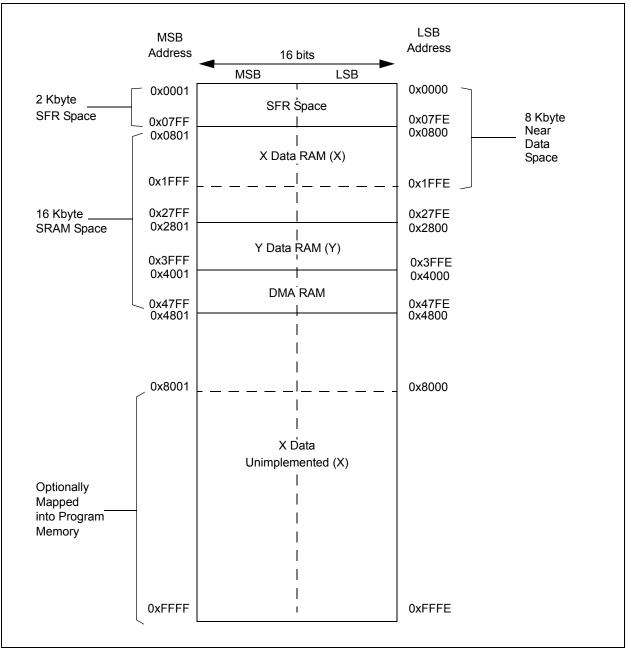

#### FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/ 804 DEVICES WITH 16 KB RAM

#### TABLE 4-7: OUTPUT COMPARE REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|---------------------------|--------|--------|--------|--------|-------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS    | 0180        |        |                           |        |        |        |        | Ou    | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC1R     | 0182        |        | Output Compare 1 Register |        |        |        |        |       |             |             |              |       |       | XXXX   |       |          |       |               |

| OC1CON   | 0184        | _      | _                         | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |                           |        |        |        |        | Ou    | tput Compar | e 2 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC2R     | 0188        |        | Output Compare 2 Register |        |        |        |        |       |             |             |              |       |       | XXXX   |       |          |       |               |

| OC2CON   | 018A        | _      | _                         | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                           |        |        |        |        | Ou    | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |                           |        |        |        |        |       | Output Co   | mpare 3 Re  | egister      |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _                         | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |                           |        |        |        |        | Ou    | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        |                           |        |        |        |        |       | Output Co   | mpare 4 Re  | egister      |       |       |        |       |          |       | XXXX          |

| OC4CON   | 0196        | _      | _                         | OCSIDL | —      | _      | _      | —     | —           | —           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7                        | Bit 6 | Bit 5      | Bit 4        | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|------------------------------|-------|------------|--------------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | -      | _      | -      | —      | _     |                              |       |            | Receive      | Register |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | -     |                              |       |            | Transmit     | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |       | Baud Rate Generator Register |       |            |              |          |       |       | 0000  |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN                         | STREN | ACKDT      | ACKEN        | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT |         | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL                        | I2COV | D_A        | Р            | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      |         | _      | _      |        |        |       |                              |       | Address    | Register     |          |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | -      | _      | -      |        |       |                              |       | Address Ma | ask Register |          |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6   | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|--------|---------|-------|-------------|--------------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _                             | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE   | LPBACK  | ABAUD | URXINV      | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISE | EL<1:0> | ADDEN | RIDLE       | PERR         | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _                             | _        | _      | _      | —      | _     | UTX8  |        |         | U     | ART Transm  | nit Register |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _                             | _        | _      | _      | _      | _     | URX8  |        |         | U     | ART Receive | ed Register  |       |        |       | 0000          |

| U1BRG    | 0228        |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |        |         |       |             | 0000         |       |        |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming open | rations                                 |

|------------------------------------------|-----------------------------------------|

| MOV #0x4001, W0                          | ;                                       |

| MOV W0, NVMCON                           | ; Initialize NVMCON                     |

| ; Set up a pointer to the first program  | memory location to be written           |

| ; program memory selected, and writes er | abled                                   |

| MOV #0x0000, W0                          | ;                                       |

| MOV W0, TBLPAG                           | ; Initialize PM Page Boundary SFR       |

| MOV #0x6000, W0                          | ; An example program memory address     |

| ; Perform the TBLWT instructions to writ | te the latches                          |

| ; Oth program word                       |                                         |

| MOV #LOW WORD 0, W2                      | ;                                       |

| MOV #HIGH_BYTE_0, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| ; 1st_program_word                       |                                         |

| MOV #LOW_WORD_1, W2                      | ;                                       |

| MOV #HIGH_BYTE_1, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| ; 2nd_program_word                       |                                         |

| MOV #LOW_WORD_2, W2                      | ;                                       |

| MOV #HIGH_BYTE_2, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| •                                        |                                         |

| •                                        |                                         |

| •                                        |                                         |

| ; 63rd_program_word                      |                                         |

| MOV #LOW_WORD_31, W2                     | ;                                       |

| MOV #HIGH_BYTE_31, W3                    | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

|                                          |                                         |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

|      |             | ; for next 5 instructions                                                       |

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 | Interrupt Flag Status bit |

|-------|---------------------------------|---------------------------|

|-------|---------------------------------|---------------------------|

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER 8           | -2: DIVIAXI        | REQ: DMA C       | HANNEL X              | IRQ SELECT       | REGISTER         |                 |       |

|----------------------|--------------------|------------------|-----------------------|------------------|------------------|-----------------|-------|

| R/W-0                | U-0                | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0   |

| FORCE <sup>(1)</sup> | _                  | —                | —                     | _                | _                | —               |       |

| bit 15               |                    |                  |                       |                  |                  |                 | bit 8 |

|                      |                    |                  |                       |                  |                  |                 |       |

| U-0                  | R/W-0              | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —                    |                    |                  | I                     | RQSEL6<6:0>      | (2)              |                 |       |

| bit 7                |                    |                  |                       |                  |                  |                 | bit 0 |

|                      |                    |                  |                       |                  |                  |                 |       |

| Legend:              |                    |                  |                       |                  |                  |                 |       |

| R = Readable         | bit                | W = Writable     | bit                   | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at F      | POR                | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkn | own   |

|                      |                    |                  |                       |                  |                  |                 |       |

| bit 15               | FORCE: Force       | e DMA Transfe    | er bit <sup>(1)</sup> |                  |                  |                 |       |

|                      |                    | ngle DMA tran    |                       |                  |                  |                 |       |

|                      | 0 = Automatic      | DMA transfer     | initiation by D       | MA request       |                  |                 |       |

| bit 14-7             | Unimplemen         | ted: Read as '   | כ'                    |                  |                  |                 |       |

| bit 6-0              | IRQSEL<6:0>        | : DMA Periphe    | eral IRQ Num          | ber Select bits  | (2)              |                 |       |

|                      | 1111111 <b>= D</b> | MAIRQ127 sel     | ected to be C         | hannel DMARI     | EQ               |                 |       |

|                      | •                  |                  |                       |                  |                  |                 |       |

|                      | •                  |                  |                       |                  |                  |                 |       |

|                      | 0000000 = D        | MAIRQ0 selec     | ted to be Cha         | nnel DMAREC      | )                |                 |       |

|                      | 0000000 - <b>D</b> |                  |                       |                  | ¢                |                 |       |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

- 2: Refer to Table 7-1 for a complete listing of IRQ numbers for all interrupt sources.

NOTES:

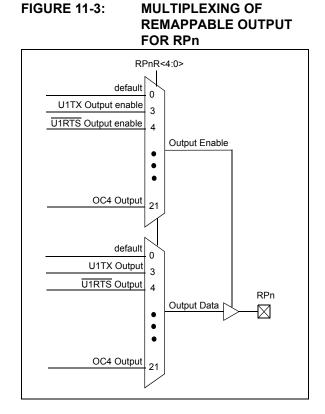

#### 11.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 11-17 through Register 11-29). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

#### Function RPnR<4:0> **Output Name** NULL RPn tied to default port pin 00000 C10UT RPn tied to Comparator1 Output 00001 C2OUT RPn tied to Comparator2 Output 00010 U1TX 00011 RPn tied to UART1 Transmit **U1RTS** 00100 RPn tied to UART1 Ready To Send U2TX RPn tied to UART2 Transmit 00101 U2RTS 00110 RPn tied to UART2 Ready To Send SDO1 RPn tied to SPI1 Data Output 00111 SCK1 01000 RPn tied to SPI1 Clock Output SS1 01001 RPn tied to SPI1 Slave Select Output SDO2 RPn tied to SPI2 Data Output 01010 RPn tied to SPI2 Clock Output SCK2 01011 SS2 RPn tied to SPI2 Slave Select Output 01100 CSDO 01101 RPn tied to DCI Serial Data Output CSCK RPn tied to DCI Serial Clock Output 01110 COFS RPn tied to DCI Frame Sync Output 01111 C1TX 10000 RPn tied to ECAN1 Transmit OC1 RPn tied to Output Compare 1 10010 OC2 RPn tied to Output Compare 2 10011 OC3 RPn tied to Output Compare 3 10100

RPn tied to Output Compare 4

#### TABLE 11-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

10101

OC4

| U-0                 | U-0              | U-0                                   | R/W-0                 | R/W-0              | R/W-0                | R/W-0           | R/W-0                |

|---------------------|------------------|---------------------------------------|-----------------------|--------------------|----------------------|-----------------|----------------------|

| _                   |                  |                                       | DISSCK                | DISSDO             | MODE16               | SMP             | CKE <sup>(1)</sup>   |

| bit 15              |                  |                                       |                       |                    |                      |                 | bit                  |

|                     |                  |                                       |                       |                    |                      |                 |                      |

| R/W-0               | R/W-0            | R/W-0                                 | R/W-0                 | R/W-0              | R/W-0                | R/W-0           | R/W-0                |

| SSEN <sup>(3)</sup> | CKP              | MSTEN                                 |                       | SPRE<2:0>(2        | 2)                   | PPRE            | <1:0> <sup>(2)</sup> |

| bit 7               |                  |                                       |                       |                    |                      |                 | bit                  |

|                     |                  |                                       |                       |                    |                      |                 |                      |

| Legend:             | . <b>L</b> :4    |                                       | L.:4                  |                    |                      | aa (0)          |                      |

| R = Readable        |                  | W = Writable                          |                       | -                  | mented bit, read     |                 |                      |

| -n = Value at I     | POR              | '1' = Bit is set                      |                       | '0' = Bit is cle   | ared                 | x = Bit is unkr | nown                 |

| bit 15-13           | Unimplemer       | nted: Read as '                       | 0'                    |                    |                      |                 |                      |

| bit 12              | •                | able SCKx pin                         |                       | er modes only)     |                      |                 |                      |

|                     | 1 = Internal S   | SPI clock is disa                     | abled, pin fund       |                    |                      |                 |                      |

|                     | 0 = Internal S   | SPI clock is ena                      | bled                  |                    |                      |                 |                      |

| bit 11              |                  | able SDOx pin                         |                       |                    |                      |                 |                      |

|                     |                  | n is not used by<br>n is controlled b |                       | unctions as I/C    | )                    |                 |                      |

| bit 10              | •                | ord/Byte Comm                         |                       | ect hit            |                      |                 |                      |

| bit 10              |                  | ication is word-                      |                       |                    |                      |                 |                      |

|                     |                  | ication is byte-                      |                       |                    |                      |                 |                      |

| bit 9               | SMP: SPIx D      | ata Input Samp                        | ole Phase bit         |                    |                      |                 |                      |

|                     | Master mode      |                                       |                       |                    |                      |                 |                      |

|                     |                  | a sampled at ei<br>a sampled at m     |                       |                    |                      |                 |                      |

|                     | Slave mode:      |                                       |                       |                    |                      |                 |                      |

|                     |                  | e cleared when                        | SPIx is used i        | in Slave mode.     |                      |                 |                      |

| bit 8               | CKE: SPIx C      | lock Edge Sele                        | ct bit <sup>(1)</sup> |                    |                      |                 |                      |

|                     |                  |                                       |                       |                    | clock state to Id    |                 |                      |

|                     |                  |                                       |                       |                    | ock state to activ   | e clock state ( | see bit 6)           |

| bit 7               |                  | Select Enable<br>used for Slave r     |                       | de) <sup>(3)</sup> |                      |                 |                      |

|                     |                  | not used by mo                        |                       | rolled by port fi  | unction              |                 |                      |

| bit 6               | -                | Polarity Select I                     |                       |                    |                      |                 |                      |

|                     | 1 = Idle state   | for clock is a h                      | igh level; activ      |                    |                      |                 |                      |

|                     | 0 = Idle state   | for clock is a lo                     | ow level; activ       | e state is a hig   | h level              |                 |                      |

| bit 5               |                  | ster Mode Enab                        | ole bit               |                    |                      |                 |                      |

|                     | 1 = Master m     |                                       |                       |                    |                      |                 |                      |

|                     | 0 = Slave mo     | ae                                    |                       |                    |                      |                 |                      |

| Note 1: The         | e CKE bit is not | t used in the Fr                      | amed SPI mo           | des. Proaram t     | his bit to '0' for t | the Framed SF   | l modes              |

|                     | RMEN = $1$ ).    |                                       |                       |                    |                      |                 |                      |

| <b>0</b>            |                  |                                       |                       |                    | <i></i>              |                 |                      |

2: Do not set both Primary and Secondary prescalers to the value of 1:1.

3: This bit must be cleared when FRMEN = 1.

## 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit  $(I^2C)$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation.

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly.

#### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, refer to the "*dsPIC33F/PIC24H Family Reference Manual*". Please see the Microchip website (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual chapters.

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | _     | —                | —                | AMSK9           | AMSK8 |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| AMSK7           | AMSK6 | AMSK5            | AMSK4 | AMSK3            | AMSK2            | AMSK1           | AMSK0 |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, read | l as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSKx: Mask for Address Bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

#### 19.2 Frame Types

The ECAN module transmits various types of frames which include data messages, or remote transmission requests initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

- Standard Data Frame: A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID), but not an 18bit Extended Identifier (EID).

- Extended Data Frame: An extended data frame is similar to a standard data frame, but includes an extended identifier as well.

- Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node sends a data frame as a response to this remote request.

• Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

• Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node can generate a maximum of 2 sequential overload frames to delay the start of the next message.

· Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

|               | R-0                     | R-0                    | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0        |

|---------------|-------------------------|------------------------|-------------------------------|------------------|--------------------|-----------------|--------------|

| TXENn         | TXABTn                  | TXLARBn                | TXERRn                        | TXREQn           | RTRENn             | TXnPF           | RI<1:0>      |

| bit 15        | •                       |                        |                               |                  |                    |                 | bit 8        |

|               |                         |                        |                               |                  |                    |                 |              |

| R/W-0         | R-0                     | R-0                    | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0        |

| TXENm         | TXABTm <sup>(1)</sup>   | TXLARBm <sup>(1)</sup> | TXERRm <sup>(1)</sup>         | TXREQm           | RTRENm             | TXmPF           | RI<1:0>      |

| bit 7         |                         |                        |                               |                  |                    |                 | bit          |

|               |                         | O Militable I          | :t. ht. a.a.h. (0)            |                  |                    |                 |              |

| Legend:       | a h:t                   |                        | -                             |                  | n to clear the bit |                 |              |

| R = Readabl   |                         | W = Writable           |                               | •                | nented bit, read   |                 |              |

| -n = Value at | PUR                     | '1' = Bit is set       |                               | '0' = Bit is cle | ared               | x = Bit is unkr | IOWN         |

| bit 15-8      | See Definition          | n for Bits 7-0, C      | ontrols Buffer                | n                |                    |                 |              |

| bit 7         |                         | RX Buffer Selec        |                               |                  |                    |                 |              |

|               |                         | Bn is a transmi        |                               |                  |                    |                 |              |

|               |                         | Bn is a receive        |                               |                  |                    |                 |              |

| bit 6         | TXABTm: Me              | essage Aborted         | l bit <sup>(1)</sup>          |                  |                    |                 |              |

|               | 1 = Message             | -                      |                               |                  |                    |                 |              |

|               | 0 = Message             | completed tran         | smission succ                 | cessfully        |                    |                 |              |

| bit 5         | TXLARBm: N              | Message Lost A         | vrbitration bit <sup>(1</sup> | )                |                    |                 |              |

|               |                         | lost arbitration       |                               |                  |                    |                 |              |

|               | -                       | did not lose arl       |                               | -                |                    |                 |              |

| bit 4         |                         | ror Detected D         |                               |                  |                    |                 |              |

|               |                         | or occurred whi        |                               | . 0              |                    |                 |              |

|               |                         | or did not occu        |                               | ssage was bei    | ng sent            |                 |              |

| bit 3         |                         | essage Send R          | •                             | h:4              | - 11               |                 | <b>f</b>     |

|               | ⊥ = Requests sent       | that a messag          | e de sent. The                | e dit automatica | ally clears when   | i the message i | s successful |

|               |                         | the bit to '0' wh      | ile set request               | s a message a    | abort              |                 |              |

| bit 2         | RTRENm: Au              | uto-Remote Tra         | nsmit Enable                  | bit              |                    |                 |              |

|               | 1 = When a r            | emote transmit         | is received, T                | XREQ will be     | set                |                 |              |

|               | 0 = When a r            | emote transmit         | is received, T                | XREQ will be     | unaffected         |                 |              |

| bit 1-0       | TXmPRI<1:0              | >: Message Tra         | ansmission Pri                | iority bits      |                    |                 |              |

|               | •                       | message priori         | •                             |                  |                    |                 |              |

|               | $1 \cap = High int_{i}$ | ermediate mes          | sage priority                 |                  |                    |                 |              |

|               | 0                       | ermediate mess         |                               |                  |                    |                 |              |

# REGISTER 19-26: CITRmnCON: ECAN™ TX/RX BUFFER m CONTROL REGISTER

The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM. Note:

| BUFFER 19-3             | B: ECAN                     | I™ MESSAGE                    | BUFFER \     | NORD 2           |                  |                 |       |

|-------------------------|-----------------------------|-------------------------------|--------------|------------------|------------------|-----------------|-------|

| R/W-x                   | R/W-x                       | R/W-x                         | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| EID5                    | EID4                        | EID3                          | EID2         | EID1             | EID0             | RTR             | RB1   |

| bit 15                  |                             |                               |              |                  |                  |                 | bit 8 |

| U-0                     | U-0                         | U-0                           | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|                         | —                           | —                             | RB0          | DLC3             | DLC2             | DLC1            | DLC0  |

| bit 7                   |                             |                               |              |                  |                  |                 | bit 0 |

| Legend:<br>R = Readable | hit                         | W = Writable                  | hit          | II = I Inimpler  | mented bit, read | 1 as 'N'        |       |

| -n = Value at POR       |                             | '1' = Bit is set              |              | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

| bit 15-10               | EID<5:0>: E                 | xtended Identifie             | er bits      |                  |                  |                 |       |

| bit 9                   | RTR: Remot                  | e Transmission                | Request bit  |                  |                  |                 |       |

|                         | 1 = Message<br>0 = Normal r | e will request rer<br>nessage | note transmi | ssion            |                  |                 |       |

| hit 0                   | DD1. Dooon                  | rod Dit 1                     |              |                  |                  |                 |       |

| bit 8   | RB1: Reserved Bit 1                             |

|---------|-------------------------------------------------|

|         | User must set this bit to '0' per CAN protocol. |

| bit 7-5 | Unimplemented: Read as '0'                      |

| bit 4   | RB0: Reserved Bit 0                             |

|         | User must set this bit to '0' per CAN protocol. |

| bit 3-0 | DLC<3:0>: Data Length Code bits                 |

#### BUFFER 19-4: ECAN™ MESSAGE BUFFER WORD 3

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                  |       |                  | B     | yte 1             |                 |                 |       |

| bit 15           |       |                  |       |                   |                 |                 | bit 8 |

|                  |       |                  |       |                   |                 |                 |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                  |       |                  | B     | yte 0             |                 |                 |       |

| bit 7            |       |                  |       |                   |                 |                 | bit 0 |

| Legend:          |       |                  |       |                   |                 |                 |       |

| R = Readable bit |       | W = Writable bi  | it    | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at PO | R     | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

Byte 1<15:8>: ECAN™ Message Byte 0 bit 15-8

bit 7-0 Byte 0<7:0>: ECAN Message Byte 1

| U-0          | U-0                                                                                                   | U-0                                                                                 | U-0                                | R/W-0             | R/W-0           | U-0            | R/W-0  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|-------------------|-----------------|----------------|--------|--|--|--|

| _            | _                                                                                                     |                                                                                     | _                                  | BLEN              | N<1:0>          |                | COFSG3 |  |  |  |

| bit 15       | ·                                                                                                     |                                                                                     |                                    |                   |                 |                | bit 8  |  |  |  |

|              |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

| R/W-0        | R/W-0                                                                                                 | R/W-0                                                                               | U-0                                | R/W-0             | R/W-0           | R/W-0          | R/W-0  |  |  |  |

|              | COFSG<2:0>                                                                                            |                                                                                     | —                                  |                   | WS              | <3:0>          |        |  |  |  |

| bit 7        |                                                                                                       |                                                                                     |                                    |                   |                 |                | bit (  |  |  |  |

| Legend:      |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

| R = Readab   | le bit                                                                                                | W = Writable b                                                                      | oit                                | U = Unimplen      | nented bit, rea | d as '0'       |        |  |  |  |

| -n = Value a | t POR                                                                                                 | '1' = Bit is set                                                                    |                                    | '0' = Bit is clea | ared            | x = Bit is unk | nown   |  |  |  |

|              |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

| bit 15-12    | Unimplemen                                                                                            | ted: Read as '0                                                                     | )'                                 |                   |                 |                |        |  |  |  |

| bit 11-10    | BLEN<1:0>:                                                                                            | BLEN<1:0>: Buffer Length Control bits                                               |                                    |                   |                 |                |        |  |  |  |

|              | 11 = Four data words will be buffered between interrupts                                              |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | 10 = Three data words will be buffered between interrupts                                             |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | 01 = Two data                                                                                         | 01 = Two data words will be buffered between interrupts                             |                                    |                   |                 |                |        |  |  |  |

|              | 00 = One dat                                                                                          | a word will be b                                                                    | uffered betw                       | een interrupts    |                 |                |        |  |  |  |

| bit 9        | Unimplemen                                                                                            | ted: Read as 'o                                                                     | )'                                 |                   |                 |                |        |  |  |  |

| bit 8-5      | COFSG<3:0>                                                                                            | : Frame Sync (                                                                      | Generator Co                       | ontrol bits       |                 |                |        |  |  |  |

|              | 1111 <b>= Data</b> 1                                                                                  | frame has 16 w                                                                      | ords                               |                   |                 |                |        |  |  |  |

|              | •                                                                                                     |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | •                                                                                                     |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | •                                                                                                     |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | 0010 <b>= Data</b> 1                                                                                  | frame has 3 wo                                                                      | rds                                |                   |                 |                |        |  |  |  |

|              |                                                                                                       | frame has 2 wo                                                                      |                                    |                   |                 |                |        |  |  |  |

|              | 0000 <b>= Data</b> 1                                                                                  | frame has 1 wo                                                                      | rd                                 |                   |                 |                |        |  |  |  |

| bit 4        | Unimplemen                                                                                            | ted: Read as '0                                                                     | )'                                 |                   |                 |                |        |  |  |  |

|              | WS<3:0>: DCI Data Word Size bits                                                                      |                                                                                     |                                    |                   |                 |                |        |  |  |  |

| bit 3-0      | WS<3:0>: DC                                                                                           | CI Data Word Si                                                                     | ze bits                            |                   |                 |                |        |  |  |  |

|              |                                                                                                       | CI Data Word Si<br>word size is 16                                                  |                                    |                   |                 |                |        |  |  |  |

|              |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              |                                                                                                       |                                                                                     |                                    |                   |                 |                |        |  |  |  |

|              | 1111 = Data<br>•<br>•                                                                                 |                                                                                     | bits                               |                   |                 |                |        |  |  |  |

|              | 1111 = Data<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | word size is 16<br>word size is 5 b<br>word size is 4 b                             | bits<br>its<br>its                 |                   |                 |                |        |  |  |  |

|              | 1111 = Data<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | word size is 16<br>word size is 5 b<br>word size is 4 b<br>i <b>d Selection</b> . D | bits<br>its<br>its<br>o not use. U | nexpected resul   | -               |                |        |  |  |  |

### 22.0 AUDIO DIGITAL-TO-ANALOG CONVERTER (DAC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Audio Digital-to-Analog Converter (DAC) module is a 16-bit Delta-Sigma signal converter designed for audio applications. It has two output channels, left and right to support stereo applications. Each DAC output channel provides three voltage outputs, positive DAC output, negative DAC output, and the midpoint voltage output for the dsPIC33FJ64GP804 and dsPIC33FJ128GP804 The devices. dsPIC33FJ128GP802 dsPIC33FJ64GP802 and devices provide positive DAC output and negative DAC output voltages.

### 22.1 Key Features

- 16-bit resolution (14-bit accuracy)

- Second-Order Digital Delta-Sigma Modulator

- 256 X Over-Sampling Ratio

- 128-Tap FIR Current-Steering Analog Reconstruction Filter

- 100 ksps Maximum Sampling Rate

- User controllable Sample Clock

- Input Frequency 45 kHz max

- · Differential Analog Outputs

- Signal-To-Noise: 90 dB

- 4-deep input Buffer

- 16-bit Processor I/O, and DMA interfaces

#### 22.2 DAC Module Operation

The functional block diagram of the Audio DAC module is shown in Figure 22-1. The Audio DAC module provides a 4-deep data input FIFO buffer for each output channel. If the DMA module and/or the processor cannot provide output data in a timely manner, and the FIFO becomes empty, the DAC accepts data from the DAC Default Data register (DACDFLT). This safety feature is useful for industrial control applications where the DAC output controls an important processor or machinery. The DACDFLT register should be initialized with a "safe" output value. Often the safe output value is either the midpoint value (0x8000) or a zero value (0x0000).

The digital interpolator up-samples the input signals, where the over-sampling ratio is 256x which creates data points between the user supplied data points. The interpolator also includes processing by digital filters to provide "noise shaping" to move the converter noise above 20 kHz (upper limit of the pass band). The output of the interpolator drives the Sigma-Delta modulator. The serial data bit stream from the Sigma-Delta modulator is processed by the reconstruction filter. The differential outputs of the reconstruction filter are amplified by Op Amps to provide the required peak-to-peak voltage swing.

**Note:** The DAC module is designed specifically for audio applications and is not recommended for control type applications.

# 22.3 DAC Output Format

The DAC output data stream can be in a two's complement signed number format or as an unsigned number format.

The Audio DAC module features the ability to accept the 16-bit input data in a two's complement signed number format or as an unsigned number format. The data formatting is controlled by the Data Format Control bit (FORM<8>) in the DAC1CON register. The supported formats are:

- 1 = Signed (two's complement)

- 0 = Unsigned

If the FORM bit is configured for "Unsigned data" then the user input data yields the following behavior:

- 0xFFFF = most positive output voltage

- 0x8000 = mid point output voltage

- 0x7FFF = a value just below the midpoint

- 0x0000 = minimum output voltage

If the FORM bit is configured for "signed data" then the user input data yields the following behavior:

- 0x7FFF = most positive output voltage

- 0x0000 = mid point output voltage

- 0xFFFF = value just below the midpoint

- 0x8000 = minimum output voltage

The Audio DAC provides an analog output proportional to the digital input value. The maximum 100,000 samples per second (100 ksps) update rate provides good quality audio reproduction.

© 2007-2012 Microchip Technology Inc.

#### 23.2 Comparator Control Register

| R/W-0        | U-0                                                    | R/W-0                                                   | R/W-0        | R/W-0              | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

|--------------|--------------------------------------------------------|---------------------------------------------------------|--------------|--------------------|-----------------|------------------------|------------------------|--|--|--|

| CMIDL        | _                                                      | C2EVT                                                   | C1EVT        | C2EN               | C1EN            | C2OUTEN <sup>(1)</sup> | C1OUTEN <sup>(2)</sup> |  |  |  |

| bit 15       |                                                        |                                                         |              | 1                  |                 |                        | bit 8                  |  |  |  |

| R-0          | R-0                                                    | R/W-0                                                   | R/W-0        | R/W-0              | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

| C2OUT        | C10UT                                                  | C2INV                                                   | C1INV        | C2NEG              | C2POS           | C1NEG                  | C1POS                  |  |  |  |

| bit 7        | 01001                                                  | 021111                                                  | Onite        | OZINEO             | 021 00          | Onles                  | bit (                  |  |  |  |

|              |                                                        |                                                         |              |                    |                 |                        |                        |  |  |  |

| Legend:      |                                                        |                                                         |              |                    |                 |                        |                        |  |  |  |

| R = Readab   | le bit                                                 | W = Writable                                            | bit          | U = Unimplem       | nented bit, rea | ad as '0'              |                        |  |  |  |

| -n = Value a | t POR                                                  | '1' = Bit is set                                        |              | '0' = Bit is clea  | ared            | x = Bit is unkr        | iown                   |  |  |  |

| bit 15       | 1 = When de                                            | in Idle Mode b<br>evice enters Idle<br>e normal modul   | e mode, modu |                    | nerate interrup | ots. Module is stil    | ll enabled.            |  |  |  |

| bit 14       | Unimplemer                                             | nted: Read as '                                         | 0'           |                    |                 |                        |                        |  |  |  |

| bit 13       | C2EVT: Comparator 2 Event bit                          |                                                         |              |                    |                 |                        |                        |  |  |  |

|              |                                                        | ator output chai<br>ator output did i                   |              | ates               |                 |                        |                        |  |  |  |

| bit 12       | C1EVT: Comparator 1 Event bit                          |                                                         |              |                    |                 |                        |                        |  |  |  |

|              |                                                        | ator output chai<br>ator output did i                   |              | ates               |                 |                        |                        |  |  |  |

| bit 11       | 1 = Compara                                            | parator 2 Enable<br>ator is enabled<br>ator is disabled | e bit        |                    |                 |                        |                        |  |  |  |

| bit 10       | C1EN: Comparator 1 Enable bit                          |                                                         |              |                    |                 |                        |                        |  |  |  |

|              |                                                        | ator is enabled<br>ator is disabled                     |              |                    |                 |                        |                        |  |  |  |

| bit 9        | C2OUTEN: (                                             | Comparator 2 C                                          | utput Enable | bit <sup>(1)</sup> |                 |                        |                        |  |  |  |

|              |                                                        | ator output is dr<br>ator output is no                  |              |                    |                 |                        |                        |  |  |  |

| bit 8        | C1OUTEN: Comparator 1 Output Enable bit <sup>(2)</sup> |                                                         |              |                    |                 |                        |                        |  |  |  |

|              |                                                        | ator output is dr<br>ator output is no                  |              |                    |                 |                        |                        |  |  |  |

| bit 7        | C2OUT: Con                                             | nparator 2 Outp                                         | ut bit       |                    |                 |                        |                        |  |  |  |

|              | When C2INV                                             |                                                         |              |                    |                 |                        |                        |  |  |  |

|              | 1 = C2 VIN+<br>0 = C2 VIN+                             | -                                                       |              |                    |                 |                        |                        |  |  |  |

|              | 0 02 111                                               |                                                         |              |                    |                 |                        |                        |  |  |  |

|              | When C2INV                                             | ′ = 1:                                                  |              |                    |                 |                        |                        |  |  |  |

|              | When C2INV<br>0 = C2 VIN+<br>1 = C2 VIN+               | > C2 VIN-                                               |              |                    |                 |                        |                        |  |  |  |

#### REGISTER 23-1: CMCON: COMPARATOR CONTROL REGISTER

- **Note 1:** If C2OUTEN = 1, the C2OUT peripheral output must be configured to an available RPx pin. See **Section 11.6 "Peripheral Pin Select"** for more information.

- 2: If C1OUTEN = 1, the C1OUT peripheral output must be configured to an available RPx pin. See Section 11.6 "Peripheral Pin Select" for more information.

| CONFIG BITS           | BSS<2:0> = x11 0K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BSS<2:0> = x01 4K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BSS<2:0> = x00 8K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0> = x11<br>0K  | VS = 256 IW         0x000000h<br>0x0001FEh<br>0x000200h<br>0x0007FEh<br>0x000800h<br>0x003FFEh<br>0x002000h           GS = 21760 IW         0x007FEh<br>0x00800h<br>0x007FFEh<br>0x007FFEh           0x007FFEh<br>0x00800h<br>0x007FFEh           0x007FFEh<br>0x00800h           0x007FFEh           0x007FFEh | VS = 256 IW         0x000000h<br>0x0001FEh<br>0x000200h<br>0x0007FEh<br>0x000800h<br>0x003FFEh<br>0x002000h<br>0x003FFEh<br>0x002000h<br>0x003FFEh<br>0x00400h<br>0x007FFEh<br>0x008000h<br>0x0040FEh           GS = 20992 IW         0x00400h<br>0x003FFEh<br>0x00400h<br>0x007FFEh<br>0x008000h<br>0x0040FEh                                                                                                                                                                                                                                                                 | VS = 256 IW         0x000000h<br>0x0001FEh           BS = 3840 IW         0x000200h<br>0x0007FEh           0x000800h         0x001FFEh           0x001FFEh         0x000800h           0x002000h         0x001FFEh           0x002000h         0x001FFEh           0x002000h         0x00157FEh           0x004000h         0x00400h           0x007FFEh         0x00400h           0x00400H         0x00400h           0x00400H         0x00400h           0x00400H         0x00400h                                          | VS = 256 IW         0x00000h<br>0x0001FEh<br>0x000200h<br>0x0007FEh<br>0x000800h<br>0x001FFEh<br>0x00200h           GS = 13824 IW         0x00400h<br>0x00457FEh<br>0x004000h           GS = 13824 IW         0x0157FEh<br>0x0157FEh                                                                                                                                                                                                                                                                                                                                                           |

| SSS<2:0> = x10<br>4K  | VS = 256 IW         0x000000h<br>0x0001FEh<br>0x000200h<br>0x0007FEh<br>0x000800h<br>0x001FFEh<br>0x002000h<br>0x003FFEh<br>0x002000h<br>0x003FFEh<br>0x004000h<br>0x007FFEh<br>0x004000h<br>0x007FFEh<br>0x008000h<br>0x007FFEh<br>0x008000h           GS = 17920 IW         0x0157FEh<br>0x0157FEh                                                                                                                                                                                                                                        | VS = 256 IW         0x000000h<br>0x0001FEh           BS = 768 IW         0x000200h<br>0x0007FEh           SS = 3072 IW         0x000800h<br>0x003FFEh           0x002000h         0x000400h           0x002000h         0x000400h           0x002000h         0x003FFEh           0x002000h         0x003FFEh           0x004000h         0x003FFEh           0x004000h         0x00400h           0x00400h         0x00400h           0x00400h         0x00400h           0x00400h         0x00400h           0x00400h         0x00400h           0x00400h         0x00400h   | VS = 256 IW         0x000000h<br>0x0001FEh           BS = 3840 IW         0x000200h<br>0x0007FEh           0x000800h         0x001FFEh           0x00200h         0x0007FEh           0x00200h         0x003FFEh           0x004000h         0x004000h           0x007FFEh         0x007FFEh           0x008000h         0x00400h           0x007FFEh         0x00400h           0x00407FFEh         0x00400h           0x007FFEh         0x00400h           0x00407FFEh         0x00407FFEh                                   | VS = 256 IW         0x00000h<br>0x0001FEh           BS = 7936 IW         0x000200h<br>0x0007FEh           0x001FEh         0x0007FEh           0x000800h         0x001FFEh           0x00200h         0x001FFEh           0x00200h         0x001FFEh           0x00200h         0x00200h           0x00200h         0x00200h           0x00200h         0x00400h           0x007FFEh         0x007FFEh           0x004000h         0x00400h           0x00400h         0x00400h           0x00400h         0x007FFEh           0x00400h         0x007FFEh           0x00400h         0x007FFEh |