#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp202-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

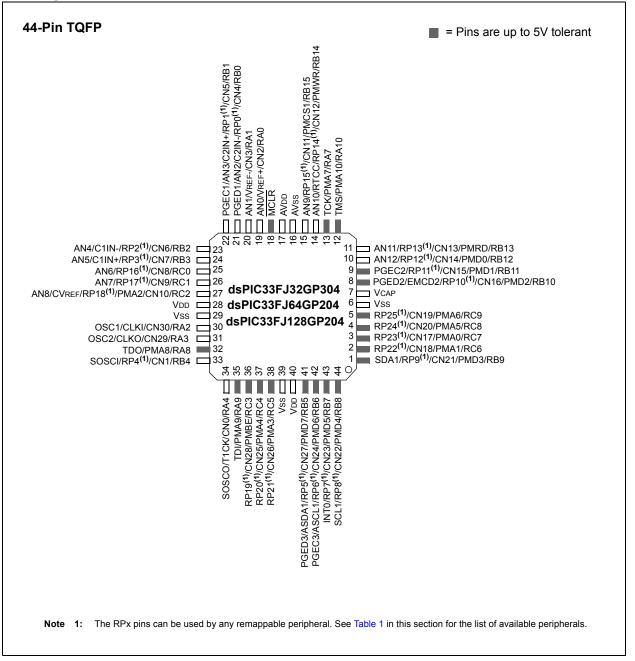

#### Pin Diagrams (Continued)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304, the of dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

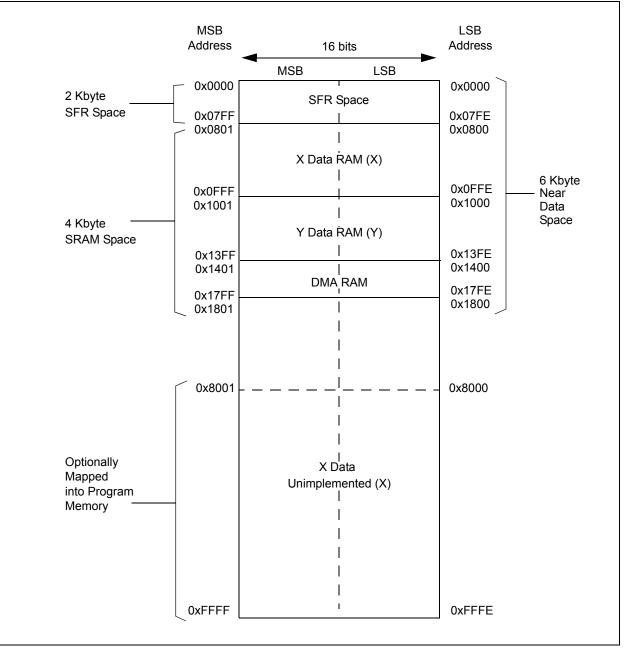

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VREF+/VREF- pins used when external voltage reference for ADC module is implemented

- Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

NOTES:

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                           | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-------|-------------------------------------------------|-------|-------|-------|

|                                    |       |       | PAD   | <15:8>                                          |       |       |       |

| bit 15                             |       |       |       |                                                 |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                           | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | PAD   | )<7:0>                                          |       |       |       |

| bit 7                              |       |       |       |                                                 |       |       | bit 0 |

| Legend:                            |       |       |       |                                                 |       |       |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'              |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       |       | $0^{\circ}$ = Bit is cleared x = Bit is unknown |       |       |       |

## **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0          | U-0                     | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0           |  |  |

|--------------|-------------------------|-------|-------|-------|-------|-------|-----------------|--|--|

| _            | —                       | _     | —     | _     | _     | CNT<  | 9:8> <b>(2)</b> |  |  |

| bit 15 bit 8 |                         |       |       |       |       |       |                 |  |  |

|              |                         |       |       |       |       |       |                 |  |  |

| R/W-0        | R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           |  |  |

|              | CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |                 |  |  |

| bit 7 bit 0  |                         |       |       |       |       |       |                 |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

#### 10.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### 12.2 Timer1 Control Register

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 TON TSIDL bit 15 bit 8 U-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 U-0 TGATE TCKPS<1:0> TSYNC TCS bit 7 bit 0 Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 TON: Timer1 On bit 1 = Starts 16-bit Timer1 0 = Stops 16-bit Timer1 Unimplemented: Read as '0' bit 14 bit 13 TSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12-7 Unimplemented: Read as '0' bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit When TCS = 1: This bit is ignored. When TCS = 0: 1 = Gated time accumulation enabled 0 = Gated time accumulation disabled bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits 11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1 bit 3 Unimplemented: Read as '0' bit 2 TSYNC: Timer1 External Clock Input Synchronization Select bit When TCS = 1: 1 = Synchronize external clock input 0 = Do not synchronize external clock input When TCS = 0: This bit is ignored. bit 1 TCS: Timer1 Clock Source Select bit 1 = External clock from pin T1CK (on the rising edge) 0 = Internal clock (FCY) bit 0 Unimplemented: Read as '0'

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

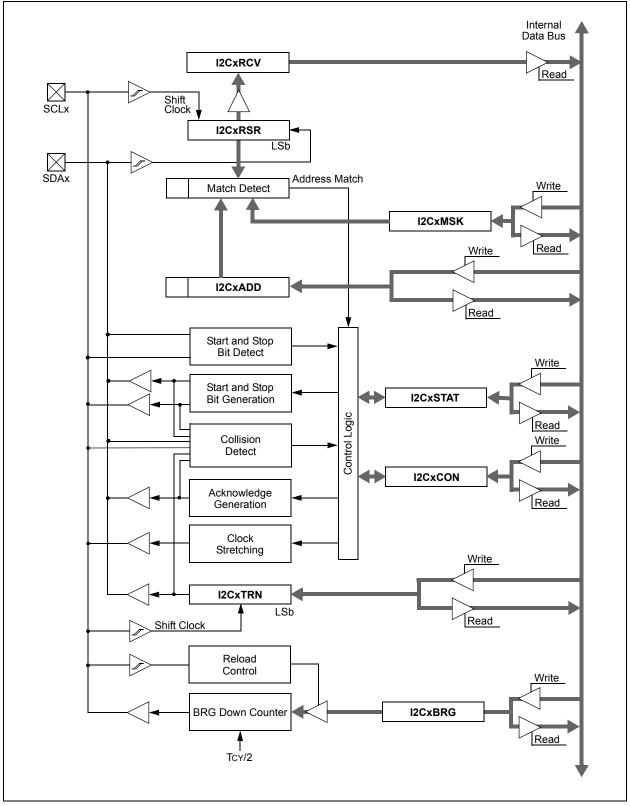

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (x = 1)

#### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

```

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en532311

```

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0          | U-0                                                                                         | U-0                                                              | U-0                         | R/W-0            | R/W-0            | U-0            | R/W-0  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|------------------|------------------|----------------|--------|--|--|--|--|

| _            | _                                                                                           |                                                                  | _                           | BLEN             | N<1:0>           | _              | COFSG3 |  |  |  |  |

| bit 15       | ·                                                                                           |                                                                  |                             |                  |                  |                | bit 8  |  |  |  |  |

|              |                                                                                             |                                                                  |                             |                  |                  |                |        |  |  |  |  |

| R/W-0        | R/W-0                                                                                       | R/W-0                                                            | U-0                         | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | COFSG<2:0>                                                                                  |                                                                  | _                           |                  | WS               | <3:0>          |        |  |  |  |  |

| bit 7        |                                                                                             |                                                                  |                             |                  |                  |                | bit (  |  |  |  |  |

| Legend:      |                                                                                             |                                                                  |                             |                  |                  |                |        |  |  |  |  |

| R = Readab   | le bit                                                                                      | W = Writable b                                                   | bit                         | U = Unimplen     | nented bit, read | d as '0'       |        |  |  |  |  |

| -n = Value a | t POR                                                                                       | '1' = Bit is set                                                 |                             | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|              |                                                                                             |                                                                  |                             |                  |                  |                | -      |  |  |  |  |

| bit 15-12    | Unimplemen                                                                                  | ted: Read as '0                                                  | )'                          |                  |                  |                |        |  |  |  |  |

| bit 11-10    | -                                                                                           | BLEN<1:0>: Buffer Length Control bits                            |                             |                  |                  |                |        |  |  |  |  |

|              | 11 = Four data words will be buffered between interrupts                                    |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 10 = Three data words will be buffered between interrupts                                   |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 01 = Two data words will be buffered between interrupts                                     |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 00 = One data word will be buffered between interrupts                                      |                                                                  |                             |                  |                  |                |        |  |  |  |  |

| bit 9        | Unimplemen                                                                                  | ted: Read as '0                                                  | )'                          |                  |                  |                |        |  |  |  |  |

| bit 8-5      | COFSG<3:0>: Frame Sync Generator Control bits                                               |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 1111 = Data frame has 16 words                                                              |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | •                                                                                           |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | •                                                                                           |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | •                                                                                           |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 0010 = Data frame has 3 words                                                               |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 0001 = Data frame has 2 words                                                               |                                                                  |                             |                  |                  |                |        |  |  |  |  |

|              | 0000 = Data frame has 1 word                                                                |                                                                  |                             |                  |                  |                |        |  |  |  |  |

| bit 4        | Unimplemen                                                                                  | ted: Read as 'C                                                  | )'                          |                  |                  |                |        |  |  |  |  |

|              | WS<3:0>: DC                                                                                 | CI Data Word Si                                                  | ze bits                     |                  |                  |                |        |  |  |  |  |

| bit 3-0      | 1111 = Data word size is 16 bits                                                            |                                                                  |                             |                  |                  |                |        |  |  |  |  |

| bit 3-0      | 1111 <b>= Data</b>                                                                          | word size is 16                                                  | bits                        |                  |                  |                |        |  |  |  |  |

| bit 3-0      | 1111 <b>= Data</b><br>•                                                                     | word size is 16                                                  | bits                        |                  |                  |                |        |  |  |  |  |

| bit 3-0      | 1111 <b>= Data</b><br>•<br>•                                                                | word size is 16                                                  | bits                        |                  |                  |                |        |  |  |  |  |

| bit 3-0      | 1111 = Data<br>•<br>•                                                                       | word size is 16                                                  | bits                        |                  |                  |                |        |  |  |  |  |

| dit 3-0      | •                                                                                           | word size is 16<br>word size is 5 b                              |                             |                  |                  |                |        |  |  |  |  |

| DIT 3-0      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | word size is 5 b<br>word size is 4 b                             | its<br>its                  |                  |                  |                |        |  |  |  |  |

| DIT 3-0      | •<br>•<br>•<br>0100 = Data •<br>0011 = Data •<br>0010 = Invali                              | word size is 5 b<br>word size is 4 b<br>i <b>d Selection</b> . D | its<br>its<br>o not use. Ut | nexpected resu   | -                |                |        |  |  |  |  |

| REGISTER 20 | -5: RSCO | N: DCI RECE | EIVE SLOT C | ONTROL RE | GISTER |        |

|-------------|----------|-------------|-------------|-----------|--------|--------|

|             |          |             |             |           |        | P///_0 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------|------------------------------------|-----------------|-------|-------|

| RSE15                              | RSE14 | RSE13 | RSE12            | RSE11                              | RSE10           | RSE9  | RSE8  |

| bit 15                             |       | ·     |                  |                                    |                 |       | bit 8 |

|                                    |       |       |                  |                                    |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

| RSE7                               | RSE6  | RSE5  | RSE4             | RSE3                               | RSE2            | RSE1  | RSE0  |

| bit 7                              |       | ·     |                  |                                    |                 | •     | bit 0 |

|                                    |       |       |                  |                                    |                 |       |       |

| Legend:                            |       |       |                  |                                    |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | bit              | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared                               | x = Bit is unki | nown  |       |

bit 15-0

RSE<15:0>: Receive Slot Enable bits

1 = CSDI data is received during the individual time slot n

0 = CSDI data is ignored during the individual time slot n

#### REGISTER 20-6: TSCON: DCI TRANSMIT SLOT CONTROL REGISTER

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

| TSE15                                                                  | TSE14 | TSE13 | TSE12           | TSE11                              | TSE10 | TSE9  | TSE8  |

| bit 15                                                                 |       | -     |                 |                                    | •     |       | bit 8 |

|                                                                        |       |       |                 |                                    |       |       |       |

| R/W-0                                                                  | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

| TSE7                                                                   | TSE6  | TSE5  | TSE4            | TSE3                               | TSE2  | TSE1  | TSE0  |

| bit 7                                                                  |       |       |                 |                                    | •     |       | bit 0 |

|                                                                        |       |       |                 |                                    |       |       |       |

| Legend:                                                                |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                                      |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unl |       |       | x = Bit is unkr | nown                               |       |       |       |

bit 15-0

TSE<15:0>: Transmit Slot Enable Control bits

1 = Transmit buffer contents are sent during the individual time slot n

0 = CSDO pin is tri-stated or driven to logic '0', during the individual time slot, depending on the state of the CSDOM bit

## REGISTER 21-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                        |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                      |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software can write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>       |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <ul> <li>1 = ADC conversion cycle is completed.</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when ADC conversion is complete. Software can write '0' to clear</li> <li>DONE status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at start of a new conversion.</li> </ul> |

## 23.2 Comparator Control Register

| R/W-0        | U-0                                                                                                           | R/W-0                                                   | R/W-0        | R/W-0             | R/W-0                   | R/W-0                  | R/W-0                  |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|-------------------|-------------------------|------------------------|------------------------|--|--|--|--|--|--|--|

| CMIDL        | _                                                                                                             | C2EVT                                                   | C1EVT        | C2EN              | C1EN                    | C2OUTEN <sup>(1)</sup> | C1OUTEN <sup>(2)</sup> |  |  |  |  |  |  |  |

| bit 15       |                                                                                                               |                                                         |              |                   |                         |                        | bit 8                  |  |  |  |  |  |  |  |

| R-0          | R-0                                                                                                           | R/W-0                                                   | R/W-0        | R/W-0             | R/W-0                   | R/W-0                  | R/W-0                  |  |  |  |  |  |  |  |

| C2OUT        | C10UT                                                                                                         | C2INV                                                   | C1INV        | C2NEG             | C2POS                   | C1NEG                  | C1POS                  |  |  |  |  |  |  |  |

| bit 7        | 01001                                                                                                         | 021111                                                  | Onite        | OZINEO            | 021 00                  | Onles                  | bit (                  |  |  |  |  |  |  |  |

|              |                                                                                                               |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| Legend:      |                                                                                                               |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                        | W = Writable                                            | bit          | U = Unimplem      | nented bit, rea         | ad as '0'              |                        |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                         | '1' = Bit is set                                        |              | '0' = Bit is clea | ared                    | x = Bit is unkr        | iown                   |  |  |  |  |  |  |  |

| bit 15       | 1 = When de                                                                                                   | in Idle Mode b<br>evice enters Idle<br>e normal modul   | e mode, modu |                   | nerate interrup         | ots. Module is stil    | ll enabled.            |  |  |  |  |  |  |  |

| bit 14       | Unimplemer                                                                                                    | nted: Read as '                                         | 0'           |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 13       | C2EVT: Comparator 2 Event bit                                                                                 |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Comparator output changed states</li> <li>0 = Comparator output did not change states</li> </ul> |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 12       | C1EVT: Comparator 1 Event bit                                                                                 |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Comparator output changed states</li> <li>0 = Comparator output did not change states</li> </ul> |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 11       | 1 = Compara                                                                                                   | parator 2 Enable<br>ator is enabled<br>ator is disabled | e bit        |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 10       | C1EN: Comp                                                                                                    | C1EN: Comparator 1 Enable bit                           |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | <ul><li>1 = Comparator is enabled</li><li>0 = Comparator is disabled</li></ul>                                |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 9        | C2OUTEN: (                                                                                                    | C20UTEN: Comparator 2 Output Enable bit <sup>(1)</sup>  |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              |                                                                                                               | ator output is di<br>ator output is no                  |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 8        | C10UTEN: Comparator 1 Output Enable bit <sup>(2)</sup>                                                        |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              |                                                                                                               | ator output is dr<br>ator output is no                  |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

| bit 7        | C2OUT: Comparator 2 Output bit                                                                                |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              |                                                                                                               | When $C2INV = 0$ :                                      |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | 1 = C2 VIN+ > C2 VIN-0 = C2 VIN+ < C2 VIN-                                                                    |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | 0 02 111                                                                                                      |                                                         |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

|              | When C2INV                                                                                                    | ′ = 1:                                                  |              |                   | 0 = C2 VIN + > C2 VIN - |                        |                        |  |  |  |  |  |  |  |

|              | When C2INV<br>0 = C2 VIN+<br>1 = C2 VIN+                                                                      | > C2 VIN-                                               |              |                   |                         |                        |                        |  |  |  |  |  |  |  |

#### REGISTER 23-1: CMCON: COMPARATOR CONTROL REGISTER

- **Note 1:** If C2OUTEN = 1, the C2OUT peripheral output must be configured to an available RPx pin. See **Section 11.6 "Peripheral Pin Select"** for more information.

- 2: If C1OUTEN = 1, the C1OUT peripheral output must be configured to an available RPx pin. See Section 11.6 "Peripheral Pin Select" for more information.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# REGISTER 24-6: RTCVAL (WHEN RTCPTR<1:0> = 01): WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x     | R/W-x |

|--------|-----|-----|-----|-----|-------|-----------|-------|

| —      | —   |     |     | —   |       | WDAY<2:0> |       |

| bit 15 |     |     |     |     |       |           | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| _     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### **REGISTER 24-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------|-------------|-------|-------|-------|---------|-------|

| —      |       | MINTEN<2:0> |       |       | MINON | IE<3:0> |       |

| bit 15 |       |             |       |       |       |         | bit 8 |

|        |       |             |       |       |       |         |       |

| U-0    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|        |       |             |       |       |       |         |       |

| —     | SECTEN<2:0> | SECONE<3:0> |

|-------|-------------|-------------|

| bit 7 |             | bit 0       |

|       |             |             |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |

| bit 7     | Unimplemented: Read as '0'                                                                   |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |

© 2007-2012 Microchip Technology Inc.

#### 25.4 Programmable CRC Resources

Many useful resources related to Programmable CRC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

#### 25.4.1 KEY RESOURCES

- Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

Most instructions are a single word. Certain doubleword instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| (text)         M           [text]         M           {}         O <n:m>         R           .b         B           .d         D           .S         S           .w         W           Acc         O           AWB         A</n:m> | Description                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| [text]       M         {}       O <n:m>       R         .b       B         .d       D         .S       S         .w       W         Acc       O         AWB       A</n:m>                                                            | leans literal defined by "text"                                                   |

| {}       O <n:m>       R         .b       B         .d       D         .s       S         .w       W         Acc       O         AWB       A</n:m>                                                                                   | leans "content of text"                                                           |

| <n:m>         R           .b         B           .d         D           .S         S           .w         W           Acc         O           AWB         A</n:m>                                                                    | leans "the location addressed by text"                                            |

| .bB.dD.SS.wWAccOAWBA                                                                                                                                                                                                                 | Dptional field or operation                                                       |

| .dD.SS.wWAccOAWBA                                                                                                                                                                                                                    | Register bit field                                                                |

| .S S<br>.w W<br>Acc O<br>AWB A                                                                                                                                                                                                       | Byte mode selection                                                               |

| .w     W       Acc     O       AWB     A                                                                                                                                                                                             | Double-Word mode selection                                                        |

| Acc O<br>AWB A                                                                                                                                                                                                                       | Shadow register select                                                            |

| AWB A                                                                                                                                                                                                                                | Vord mode selection (default)                                                     |

|                                                                                                                                                                                                                                      | Dne of two accumulators {A, B}                                                    |

| bit4 4-                                                                                                                                                                                                                              | ccumulator write back destination address register ∈ {W13, [W13]+ = 2}            |

|                                                                                                                                                                                                                                      | -bit bit selection field (used in word addressed instructions) ∈ {015}            |

| C, DC, N, OV, Z                                                                                                                                                                                                                      | ICU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero              |

| Expr A                                                                                                                                                                                                                               | bsolute address, label or expression (resolved by the linker)                     |

| f Fi                                                                                                                                                                                                                                 | ile register address ∈ {0x00000x1FFF}                                             |

| lit1 1-                                                                                                                                                                                                                              | -bit unsigned literal ∈ {0,1}                                                     |

| lit4 4-                                                                                                                                                                                                                              | -bit unsigned literal ∈ {015}                                                     |

| lit5 5-                                                                                                                                                                                                                              | -bit unsigned literal ∈ {031}                                                     |

| lit8 8-                                                                                                                                                                                                                              | -bit unsigned literal ∈ {0255}                                                    |

| lit10 10                                                                                                                                                                                                                             | 0-bit unsigned literal $\in \{0255\}$ for Byte mode, $\{0:1023\}$ for Word mode   |

| lit14 14                                                                                                                                                                                                                             | 4-bit unsigned literal ∈ {016384}                                                 |

| lit16 16                                                                                                                                                                                                                             | 6-bit unsigned literal ∈ {065535}                                                 |

| lit23 23                                                                                                                                                                                                                             | 3-bit unsigned literal ∈ {08388608}; LSb must be '0'                              |

| None Fi                                                                                                                                                                                                                              | ield does not require an entry, can be blank                                      |

| OA, OB, SA, SB D                                                                                                                                                                                                                     | OSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate       |

| PC P                                                                                                                                                                                                                                 | Program Counter                                                                   |

| Slit10 10                                                                                                                                                                                                                            | 0-bit signed literal ∈ {-512511}                                                  |

| Slit16 16                                                                                                                                                                                                                            |                                                                                   |

| Slit6 6-                                                                                                                                                                                                                             | 6-bit signed literal ∈ {-3276832767}                                              |

| Wb B                                                                                                                                                                                                                                 | b-bit signed literal $\in \{-32/6832/67\}$<br>-bit signed literal $\in \{-1616\}$ |

| Wd D                                                                                                                                                                                                                                 |                                                                                   |

|                                                                                                                                                                                                                                      | -bit signed literal ∈ {-1616}                                                     |

| Wm,Wn D                                                                                                                                                                                                                              | -bit signed literal ∈ {-1616}<br>Base W register ∈ {W0W15}                        |

## 31.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0 "Electrical Characteristics"** for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 30.0 "Electrical Characteristics**" is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                   | 40°C to +150°C       |

|---------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                             | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                              | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>   | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} < 3.0V^{(5)}$   | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} \ge 3.0V^{(5)}$ | 0.3V to 5.6V         |

| Maximum current out of Vss pin                                                  |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                     | 60 mA                |

| Maximum junction temperature                                                    | +155°C               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                   |                      |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                   | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                   | 8 mA                 |

| Maximum current sunk by all ports combined                                      | 70 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                    | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGCx, and PGDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

NOTES:

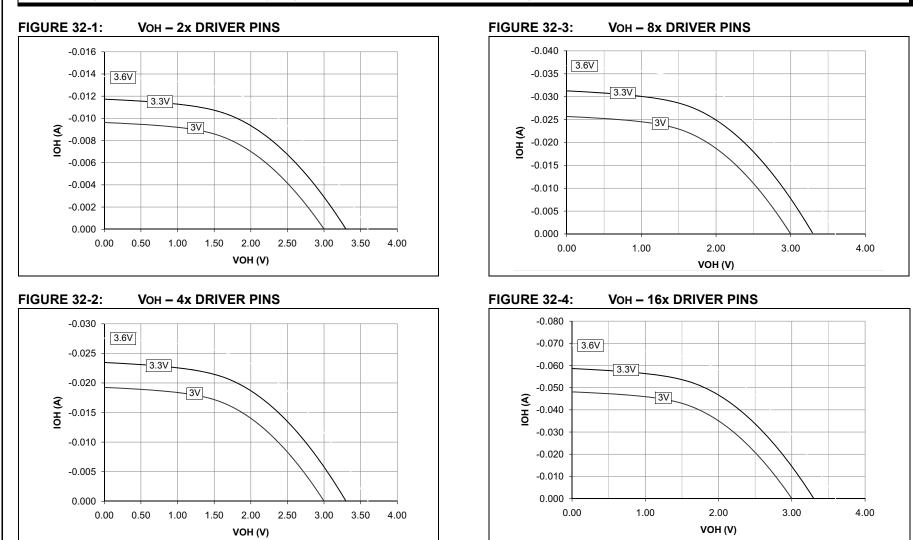

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820