Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp202t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

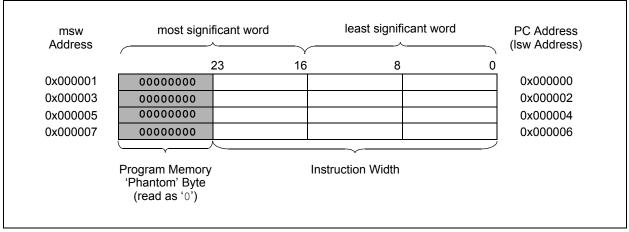

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| TABLE 4     | 4-5:        | TIMEF                                                                                        | R REGIS                                                    | TER MA                                      | ٨P     |        |        |              |              |                |              |       |        |       |       |       |       |               |

|-------------|-------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|--------|--------|--------|--------------|--------------|----------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15                                                                                       | Bit 14                                                     | Bit 13                                      | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |                                                                                              |                                                            |                                             |        |        |        |              | Timer1       | Register       |              |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |                                                                                              |                                                            |                                             |        |        |        |              | Period F     | Register 1     |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON                                                                                          | _                                                          | - TSIDL TGATE TCKPS<1:0> - TSYNC TCS - 0000 |        |        |        |              |              |                |              |       |        | 0000  |       |       |       |               |

| TMR2        | 0106        |                                                                                              |                                                            |                                             |        |        |        |              | Timer2       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |                                                                                              | Timer3 Holding Register (for 32-bit timer operations only) |                                             |        |        |        |              |              |                |              |       | XXXX   |       |       |       |       |               |

| TMR3        | 010A        |                                                                                              | Timer3 Register 000                                        |                                             |        |        |        |              |              |                |              |       | 0000   |       |       |       |       |               |

| PR2         | 010C        |                                                                                              | Period Register 2 FF.                                      |                                             |        |        |        |              |              |                |              |       | FFFF   |       |       |       |       |               |

| PR3         | 010E        |                                                                                              |                                                            |                                             |        |        |        |              | Period F     | Register 3     |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON                                                                                          | _                                                          | TSIDL                                       | _      | _      | _      | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112        | TON                                                                                          |                                                            | TSIDL                                       |        |        |        | _            | —            | —              | TGATE        | TCKP  | S<1:0> | —     | _     | TCS   | —     | 0000          |

| TMR4        | 0114        |                                                                                              |                                                            |                                             |        |        |        |              | Timer4       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |                                                                                              |                                                            |                                             |        |        | Tin    | ner5 Holding | Register (fo | r 32-bit timeı | operations o | only) |        |       |       |       |       | XXXX          |

| TMR5        | 0118        |                                                                                              |                                                            |                                             |        |        |        |              | Timer5       | Register       |              |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |                                                                                              |                                                            |                                             |        |        |        |              | Period F     | Register 4     |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |                                                                                              |                                                            |                                             |        |        |        |              | Period F     | Register 5     |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON                                                                                          |                                                            | TSIDL                                       |        |        |        | _            | _            | -              | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON                                                                                          |                                                            | TSIDL                                       |        |        |        | _            | _            | -              | TGATE        | TCKP  | S<1:0> | —     | —     | TCS   | _     | 0000          |

| Legend:     | x = un      | known value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                                                            |                                             |        |        |        |              |              |                |              |       |        |       |       |       |       |               |

# TABLE 4-6: INPUT CAPTURE REGISTER MAP

|             |             |        | •/                                             |        |        | · •••• |        |       |            |              |       |       |       |       |       |          |       |               |

|-------------|-------------|--------|------------------------------------------------|--------|--------|--------|--------|-------|------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF      | 0140        |        | Input 1 Capture Register                       |        |        |        |        |       |            |              |       |       | XXXX  |       |       |          |       |               |

| IC1CON      | 0142        | —      | - ICSIDL ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> 00 |        |        |        |        |       |            | 0000         |       |       |       |       |       |          |       |               |

| IC2BUF      | 0144        |        | Input 2 Capture Register                       |        |        |        |        |       |            |              |       |       | XXXX  |       |       |          |       |               |

| IC2CON      | 0146        | —      |                                                | ICSIDL | —      |        | -      |       |            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF      | 0158        |        |                                                |        |        |        |        |       | Input 7 Ca | pture Regist | er    |       |       |       |       |          |       | XXXX          |

| IC7CON      | 015A        | —      | _                                              | ICSIDL | —      |        |        |       |            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF      | 015C        |        | Input 8Capture Register                        |        |        |        |        |       |            |              |       | XXXX  |       |       |       |          |       |               |

| IC8CON      | 015E        | —      |                                                | ICSIDL | —      |        | _      |       |            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

|             |             |        |                                                |        |        |        |        |       |            |              |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-16: DMA REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14 | Bit 13         | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8  | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|----------------|--------|--------|--------|--------------------------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| DMA5PAD   | 03C4 |        |        |                |        |        |        | PAD<15:0> 000            |        |           |        |        |        |           |        | 0000   |        |               |

| DMA5CNT   | 03C6 | _      | _      | _              |        | _      | —      |                          |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA6CON   | 03C8 | CHEN   | SIZE   | DIR            | HALF   | NULLW  | —      | AMODE<1:0> MODE<1:0> 000 |        |           |        |        |        |           | 0000   |        |        |               |

| DMA6REQ   | 03CA | FORCE  | _      | _              |        | _      | —      | _                        | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA6STA   | 03CC |        |        |                |        |        |        |                          | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6STB   | 03CE |        |        |                |        |        |        |                          | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA6PAD   | 03D0 |        |        | PAD<15:0> 0000 |        |        |        |                          |        |           |        |        |        |           |        |        |        |               |

| DMA6CNT   | 03D2 | _      | _      | _              |        | _      | —      |                          |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN   | SIZE   | DIR            | HALF   | NULLW  | —      | _                        | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE  | _      | _              |        | _      | —      | _                        | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |        |        |                |        |        |        |                          | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |        |        |                |        |        |        |                          | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |        |        |                |        |        |        |                          | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | _      | _      | _              |        | _      | —      |                          |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7 | PWCOL6 | PWCOL5         | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1                   | PWCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 | -      | _      |                | —      |        | LSTCH  | 1<3:0>                   |        | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000          |

| DSADR     | 03E4 |        |        |                |        |        |        |                          | DS     | ADR<15:0> |        |        |        |           |        |        |        | 0000          |

|           |      |        |        |                |        |        |        |                          |        |           |        |        |        |           |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit                                      |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Flag Status bit                                              |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| REGISTER 7      | 7-31: INTTR       | EG: INTERR                             | UPT CONTI     | ROL AND STA       | ATUS REGI       | STER            |       |

|-----------------|-------------------|----------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| U-0             | U-0               | U-0                                    | U-0           | R-0               | R-0             | R-0             | R-0   |

| _               | —                 | —                                      | _             |                   | ILF             | <3:0>           |       |

| bit 15          |                   |                                        |               |                   |                 |                 | bit 8 |

| U-0             | R-0               | R-0                                    | R-0           | R-0               | R-0             | R-0             | R-0   |

| _               |                   |                                        |               | VECNUM<6:0        | >               |                 |       |

| bit 7           |                   |                                        |               |                   |                 |                 | bit C |

|                 |                   |                                        |               |                   |                 |                 |       |

| Legend:         |                   |                                        |               |                   |                 |                 |       |

| R = Readable    | e bit             | W = Writable                           | bit           | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at I | POR               | '1' = Bit is set                       |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12       | Unimplomon        | ted: Read as '                         | <b>`</b>      |                   |                 |                 |       |

|                 | -                 |                                        |               | -1                |                 |                 |       |

| bit 11-8        |                   | w CPU Interru                          | -             | el bits           |                 |                 |       |

|                 | 1111 <b>= CPU</b> | Interrupt Priorit                      | y Level is 15 |                   |                 |                 |       |

|                 | •                 |                                        |               |                   |                 |                 |       |

|                 | •                 |                                        |               |                   |                 |                 |       |

|                 |                   | Interrupt Priorit<br>Interrupt Priorit |               |                   |                 |                 |       |

| bit 7           |                   | •                                      | •             |                   |                 |                 |       |

|                 | Unimplemen        | ted: Read as '                         | 0.            |                   |                 |                 |       |

0111111 = Interrupt Vector pending is number 135

0000001 = Interrupt Vector pending is number 9 0000000 = Interrupt Vector pending is number 8

•

#### REGISTER 11-17: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                                         | U-0 | U-0              | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |  |

|---------------------------------------------|-----|------------------|-------|-----------------------------------------|------------------------------------|-------|-------|--|--|--|

| _                                           | _   | —                |       |                                         | RP1R<4:0>                          |       |       |  |  |  |

| bit 15                                      |     | ·                |       |                                         |                                    |       | bit 8 |  |  |  |

|                                             |     |                  |       |                                         |                                    |       |       |  |  |  |

| U-0                                         | U-0 | U-0              | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |  |

|                                             |     | —                |       |                                         | RP0R<4:0>                          | •     |       |  |  |  |

| bit 7                                       |     |                  |       |                                         |                                    |       | bit 0 |  |  |  |

|                                             |     |                  |       |                                         |                                    |       |       |  |  |  |

| Legend:                                     |     |                  |       |                                         |                                    |       |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimp |     |                  |       | U = Unimpler                            | U = Unimplemented bit, read as '0' |       |       |  |  |  |

| -n = Value at P                             | OR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |  |  |  |

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-18: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 11-2 for peripheral function numbers)

# 15.3 Output Compare Control Register

# REGISTER 15-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0                                                                        | U-0                                                                                                         | R/W-0                                                                                                                               | U-0            | U-0              | U-0             | U-0       | U-0   |  |  |  |  |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------|-------|--|--|--|--|--|

| —                                                                          | —                                                                                                           | OCSIDL                                                                                                                              | —              | —                | —               | —         |       |  |  |  |  |  |

| bit 15                                                                     |                                                                                                             |                                                                                                                                     |                |                  |                 |           | bit 8 |  |  |  |  |  |

|                                                                            |                                                                                                             |                                                                                                                                     |                |                  |                 |           |       |  |  |  |  |  |

| U-0                                                                        | U-0                                                                                                         | U-0                                                                                                                                 | R-0 HC         | R/W-0            | R/W-0           | R/W-0     | R/W-0 |  |  |  |  |  |

|                                                                            | —                                                                                                           | —                                                                                                                                   | OCFLT          | OCTSEL           |                 | OCM<2:0>  |       |  |  |  |  |  |

| bit 7                                                                      |                                                                                                             |                                                                                                                                     |                |                  |                 |           | bit C |  |  |  |  |  |

| Legend:                                                                    |                                                                                                             | HC = Cleared ir                                                                                                                     | n Hardware     | HS = Set in H    | lardware        |           |       |  |  |  |  |  |

| R = Readab                                                                 | le bit                                                                                                      | W = Writable bi                                                                                                                     | t              | U = Unimpler     | nented bit, rea | id as '0' |       |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                                             |                                                                                                                                     |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             |                                                                                                                                     |                |                  |                 |           |       |  |  |  |  |  |

| bit 15-14                                                                  | Unimplemen                                                                                                  | nted: Read as '0'                                                                                                                   | 1              |                  |                 |           |       |  |  |  |  |  |

| bit 13                                                                     | OCSIDL: Sto                                                                                                 | p Output Compa                                                                                                                      | re in Idle Mod | e Control bit    |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul> |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            | •                                                                                                           | -                                                                                                                                   | -              | in CPU Idle mo   | ode             |           |       |  |  |  |  |  |

| bit 12-5                                                                   | -                                                                                                           | nted: Read as '0'                                                                                                                   |                |                  |                 |           |       |  |  |  |  |  |

| bit 4                                                                      | -                                                                                                           | /I Fault Condition                                                                                                                  |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | ult condition has<br>Fault condition h                                                                                              |                | ared in hardwar  | e only)         |           |       |  |  |  |  |  |

|                                                                            | • • • • • • • • • • • • • • • • • • • •                                                                     | ly used when O                                                                                                                      |                | 1.)              |                 |           |       |  |  |  |  |  |

| bit 3                                                                      |                                                                                                             | ,<br>Itput Compare Ti                                                                                                               |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | the clock source                                                                                                                    |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            | 0 = Timer2 is                                                                                               | the clock source                                                                                                                    | e for Compare  | x                |                 |           |       |  |  |  |  |  |

| bit 2-0                                                                    | OCM<2:0>: (                                                                                                 | Output Compare                                                                                                                      | Mode Select I  | oits             |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | mode on OCx, F                                                                                                                      |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | mode on OCx, F<br>ze OCx pin low, g                                                                                                 |                |                  |                 | ain       |       |  |  |  |  |  |

|                                                                            |                                                                                                             | ze OCx pin low, g                                                                                                                   |                |                  |                 | JIII      |       |  |  |  |  |  |

|                                                                            |                                                                                                             | are event toggles                                                                                                                   |                | e calbar bares ( |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             | ze OCx pin high,                                                                                                                    |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            | 001 = Initialize OCx pin low, compare event forces OCx pin high<br>000 = Output compare channel is disabled |                                                                                                                                     |                |                  |                 |           |       |  |  |  |  |  |

|                                                                            |                                                                                                             |                                                                                                                                     |                |                  | ringii          |           |       |  |  |  |  |  |

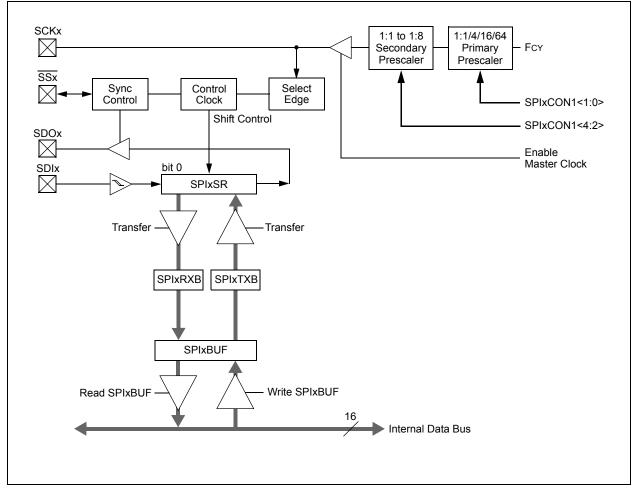

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. the of dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- <u>SCK</u>x (shift clock input or output)

- SSx (active-low slave select).

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

| R/W-0        | R/W-0        | R/W-0             | U-0             | U-0              | U-0              | U-0                    | U-0   |  |

|--------------|--------------|-------------------|-----------------|------------------|------------------|------------------------|-------|--|

| FRMEN        | SPIFSD       | FRMPOL            | —               | —                | —                | _                      |       |  |

| bit 15       |              |                   |                 |                  |                  |                        | bit 8 |  |

|              |              |                   |                 |                  |                  |                        |       |  |

| U-0          | U-0          | U-0               | U-0             | U-0              | U-0              | R/W-0                  | U-0   |  |

| —            |              |                   | —               | —                | —                | FRMDLY                 | —     |  |

| bit 7        |              |                   |                 |                  |                  |                        | bit C |  |

| Legend:      |              |                   |                 |                  |                  |                        |       |  |

| R = Readab   | lo hit       | W = Writable      | hit             | II – Unimploy    | monted bit read  | d as '0'               |       |  |

|              |              |                   |                 | •                |                  | ented bit, read as '0' |       |  |

| -n = Value a | TPOR         | '1' = Bit is set  |                 | '0' = Bit is cle | ared             | x = Bit is unkno       | own   |  |

| bit 15       | FRMEN: Fra   | imed SPIx Supp    | ort bit         |                  |                  |                        |       |  |

|              |              | SPIx support en   |                 | oin used as fram | ne sync pulse ir | nput/output)           |       |  |

|              | 0 = Framed   | SPIx support dis  | sabled          |                  |                  |                        |       |  |

| bit 14       | SPIFSD: Fra  | ame Sync Pulse    | Direction Co    | ntrol bit        |                  |                        |       |  |

|              | •            | ync pulse input   | • •             |                  |                  |                        |       |  |

|              | 0 = Frame sy | ync pulse outpu   | t (master)      |                  |                  |                        |       |  |

| bit 13       | FRMPOL: Fi   | rame Sync Puls    | e Polarity bit  |                  |                  |                        |       |  |

|              |              | ync pulse is acti |                 |                  |                  |                        |       |  |

|              | 0 = Frame sy | ync pulse is acti | ve-low          |                  |                  |                        |       |  |

| bit 12-2     | Unimpleme    | nted: Read as '   | 0'              |                  |                  |                        |       |  |

| bit 1        | FRMDLY: Fr   | ame Sync Pulse    | e Edge Selec    | t bit            |                  |                        |       |  |

|              | 1 = Frame sy | ync pulse coinci  | des with first  | bit clock        |                  |                        |       |  |

|              | 0 = Frame sy | ync pulse prece   | des first bit c | lock             |                  |                        |       |  |

| hit O        |              | ntad. Daad as (   | o'              |                  |                  |                        |       |  |

# REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

bit 0 **Unimplemented:** Read as '0' This bit must not be set to '1' by the user application.

| R/W-0         | U-0                           | R/W-0                                    | R/W-1 HC                                           | R/W-0                        | R/W-0                   | R/W-0                       | R/W-0        |

|---------------|-------------------------------|------------------------------------------|----------------------------------------------------|------------------------------|-------------------------|-----------------------------|--------------|

| I2CEN         | _                             | I2CSIDL                                  | SCLREL                                             | IPMIEN                       | A10M                    | DISSLW                      | SMEN         |

| bit 15        |                               |                                          |                                                    |                              |                         | ·                           | bit 8        |

| R/W-0         | R/W-0                         | R/W-0                                    | R/W-0 HC                                           | R/W-0 HC                     | R/W-0 HC                | R/W-0 HC                    | R/W-0 HC     |

| GCEN          | STREN                         | ACKDT                                    | ACKEN                                              | RCEN                         | PEN                     | RSEN                        | SEN          |

| bit 7         | SITCEN                        | ACRET                                    | ACKEN                                              | ROEN                         | I LIN                   | ROLIN                       | bit (        |

|               |                               |                                          |                                                    | 1                            |                         |                             |              |

| Legend:       |                               | •                                        | mented bit, read                                   |                              |                         |                             |              |

| R = Readable  |                               | W = Writable                             |                                                    | HS = Set in h                |                         | HC = Cleared                |              |

| -n = Value at | POR                           | '1' = Bit is se                          | t                                                  | '0' = Bit is cle             | ared                    | x = Bit is unkr             | IOWN         |

| bit 15        | 12CEN: 12Cx                   | Enable bit                               |                                                    |                              |                         |                             |              |

|               |                               |                                          | le and configure<br>ile. All l <sup>2</sup> C™ pir |                              |                         | as serial port pir<br>tions | าร           |

| bit 14        | Unimplemer                    | ted: Read as                             | ʻ0 <b>'</b>                                        |                              |                         |                             |              |

| bit 13        | I2CSIDL: Sto                  | p in Idle Mode                           | bit                                                |                              |                         |                             |              |

|               |                               |                                          | eration when de<br>tion in Idle mod                |                              | n Idle mode             |                             |              |

| bit 12        | SCLREL: SC                    | Lx Release Co                            | ontrol bit (when                                   | operating as                 | l <sup>2</sup> C slave) |                             |              |

|               | 1 = Release<br>0 = Hold SCL   | SCLx clock<br>₋x clock low (cl           | ock stretch)                                       |                              |                         |                             |              |

|               | If STREN = 1                  | <u>:</u>                                 | -                                                  | tiate stretch a              | nd write '1' to re      | elease clock). H            | ardware clea |

|               | •                             |                                          | nission. Hardwa                                    |                              |                         | ,                           |              |

|               | If STREN = 0                  |                                          |                                                    |                              |                         |                             |              |

|               | Bit is R/S (i.e transmission. |                                          | only write '1' to                                  | o release cloc               | k). Hardware cl         | ear at beginning            | g of slave   |

| bit 11        | IPMIEN: Inte                  | lligent Peripher                         | ral Managemer                                      | nt Interface (IP             | MI) Enable bit          |                             |              |

|               | 1 = IPMI mod<br>0 = IPMI mod  |                                          | all addresses A                                    | cknowledged                  |                         |                             |              |

| bit 10        | A10M: 10-bit                  | Slave Address                            | s bit                                              |                              |                         |                             |              |

|               |                               | ) is a 10-bit slav<br>) is a 7-bit slave |                                                    |                              |                         |                             |              |

| bit 9         | DISSLW: Dis                   | able Slew Rate                           | e Control bit                                      |                              |                         |                             |              |

|               |                               | control disable<br>control enable        |                                                    |                              |                         |                             |              |

| bit 8         | SMEN: SMB                     | us Input Levels                          | s bit                                              |                              |                         |                             |              |

|               |                               | O pin threshold<br>MBus input th         | ls compliant wi<br>resholds                        | th SMBus spe                 | cification              |                             |              |

| bit 7         |                               |                                          | e bit (when ope                                    | rating as I <sup>2</sup> C s | slave)                  |                             |              |

|               | 1 = Enable in<br>(module i    |                                          | general call ac                                    | •                            | ,                       | RSR                         |              |

| bit 6         |                               |                                          | h Enable bit (wi                                   | hon operating                | $ac l^2 C alove)$       |                             |              |

|               | SINCH SUL                     |                                          | i Litable bit (Wi                                  | nen operating                | as i U Slave)           |                             |              |

|               | Llood in achi                 | unction with SC                          |                                                    |                              |                         |                             |              |

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                                      |

|       | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                     |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

#### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

```

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en532311

```

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0           | U-0            | U-0                                 | U-0              | U-0               | U-0                | U-0             | U-0   |

|---------------|----------------|-------------------------------------|------------------|-------------------|--------------------|-----------------|-------|

| _             | _              | _                                   | _                | —                 | _                  | _               | _     |

| bit 15        |                |                                     |                  |                   |                    |                 | bit 8 |

|               |                |                                     |                  |                   |                    |                 |       |

| R/W-0         | R/W-0          | R/W-0                               | U-0              | R/W-0             | R/W-0              | R/W-0           | R/W-0 |

| IVRIE         | WAKIE          | ERRIE                               |                  | FIFOIE            | RBOVIE             | RBIE            | TBIE  |

| bit 7         |                |                                     |                  |                   |                    |                 | bit ( |

| Legend:       |                | C = Writable b                      | oit. but only '( | )' can be writter | n to clear the bit |                 |       |

| R = Readabl   | e bit          | W = Writable                        |                  |                   | mented bit, read   |                 |       |

| -n = Value at |                | '1' = Bit is set                    |                  | '0' = Bit is cle  |                    | x = Bit is unkr | iown  |

|               |                |                                     |                  |                   |                    |                 |       |

| bit 15-8      | Unimplemer     | nted: Read as '                     | )'               |                   |                    |                 |       |

| bit 7         | IVRIE: Invalio | d Message Rec                       | eived Interru    | pt Enable bit     |                    |                 |       |

|               |                | Request Enable                      |                  |                   |                    |                 |       |

|               |                | Request not en                      |                  |                   |                    |                 |       |

| bit 6         |                | Wake-up Activi                      |                  | lag bit           |                    |                 |       |

|               |                | Request Enable                      |                  |                   |                    |                 |       |

| L:1 F         |                | Request not en                      |                  |                   |                    |                 |       |

| bit 5         |                | Interrupt Enab                      |                  |                   |                    |                 |       |

|               |                | Request Enable<br>Request not en    |                  |                   |                    |                 |       |

| bit 4         | -              |                                     |                  |                   |                    |                 |       |

|               | -              | nted: Read as '(                    |                  | a hit             |                    |                 |       |

| bit 3         |                | D Almost Full Inf<br>Request Enable |                  | ebit              |                    |                 |       |

|               |                | Request not en                      |                  |                   |                    |                 |       |

| bit 2         | -              | Buffer Overflov                     |                  | nable bit         |                    |                 |       |

|               |                | Request Enable                      |                  |                   |                    |                 |       |

|               | 0 = Interrupt  | Request not en                      | abled            |                   |                    |                 |       |

| bit 1         | RBIE: RX Bu    | iffer Interrupt Er                  | able bit         |                   |                    |                 |       |

|               |                | Request Enable                      |                  |                   |                    |                 |       |

|               |                | Request not en                      |                  |                   |                    |                 |       |

| bit 0         |                | ffer Interrupt En                   |                  |                   |                    |                 |       |

|               |                | Request Enable                      |                  |                   |                    |                 |       |

|               | 0 = interrupt  | Request not en                      | apied            |                   |                    |                 |       |

### 22.5 DAC Resources

Many useful resources related to DAC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

#### 22.5.1 KEY RESOURCES

- Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 26.2 PMP Control Registers

# REGISTER 26-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-------|---------|---------|--------|--------|--------|

| PMPEN  | _   | PSIDL | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN | PTRDEN |

| bit 15 |     |       |         |         |        |        | bit 8  |

| R/W-0 | R/W-0 | R/W-0 <sup>(1)</sup> | U-0 | R/W-0 <sup>(1)</sup> | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------------------|-----|----------------------|-------|-------|-------|

| CSF1  | CSF0  | ALP                  | —   | CS1P                 | BEP   | WRSP  | RDSP  |

| bit 7 |       |                      |     |                      |       |       | bit 0 |

| Legend:       |                                                                                     |                                                                                           |                                    |

|---------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------|

| R = Readabl   | e bit W = Writable I                                                                | Dit U = Unimplemented b                                                                   | bit, read as '0'                   |

| -n = Value at | POR '1' = Bit is set                                                                | '0' = Bit is cleared                                                                      | x = Bit is unknown                 |

| bit 15        | <b>PMPEN:</b> Parallel Master Por<br>1 = PMP enabled<br>0 = PMP disabled, no off-ch |                                                                                           |                                    |

| bit 14        | Unimplemented: Read as '0                                                           |                                                                                           |                                    |

| bit 13        | PSIDL: Stop in Idle Mode bit                                                        |                                                                                           |                                    |

|               | •                                                                                   | ration when device enters Idle mode                                                       | 9                                  |

| bit 12-11     | ADRMUX1:ADRMUX0: Add                                                                | ress/Data Multiplexing Selection bits                                                     | <sub>S</sub> (1)                   |

|               |                                                                                     | e multiplexed on PMD<7:0> pins<br>s are multiplexed on PMD<7:0> pi<br>ar on separate pins | ns, upper 3 bits are multiplexed o |

| bit 10        | PTBEEN: Byte Enable Port I                                                          | Enable bit (16-bit Master mode)                                                           |                                    |

|               | <ul><li>1 = PMBE port enabled</li><li>0 = PMBE port disabled</li></ul>              |                                                                                           |                                    |

| bit 9         | PTWREN: Write Enable Stro                                                           | be Port Enable bit                                                                        |                                    |

|               | <ul><li>1 = PMWR/PMENB port ena</li><li>0 = PMWR/PMENB port dis</li></ul>           |                                                                                           |                                    |

| bit 8         | PTRDEN: Read/Write Strobe                                                           |                                                                                           |                                    |

|               | 1 = PMRD/PMWR port enable<br>0 = PMRD/PMWR port disa                                |                                                                                           |                                    |

| bit 7-6       | CSF1:CSF0: Chip Select Fu                                                           | nction bits                                                                               |                                    |

|               | 11 = Reserved<br>10 = PMCS1 functions as ch<br>0x = PMCS1 functions as ac           | •                                                                                         |                                    |

| bit 5         | ALP: Address Latch Polarity                                                         | bit <sup>(1)</sup>                                                                        |                                    |

|               | 1 = Active-high (PMALL and<br>0 = Active-low (PMALL and                             |                                                                                           |                                    |

| bit 4         | Unimplemented: Read as '0                                                           | ,                                                                                         |                                    |

| bit 3         | CS1P: Chip Select 1 Polarity                                                        | bit <sup>(1)</sup>                                                                        |                                    |

|               | 1 = Active-high (PMCS1/PM<br>0 = Active-low (PMCS1/PM                               |                                                                                           |                                    |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

#### 29.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 29.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 29.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 29.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

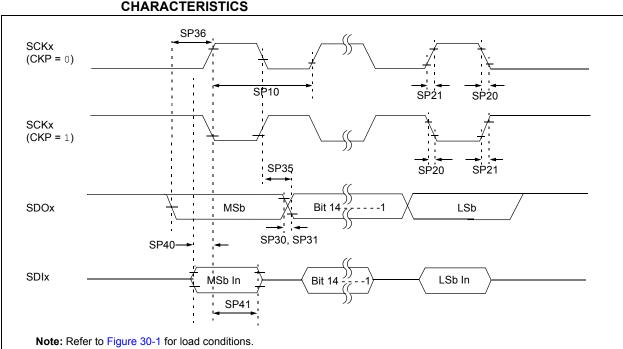

# FIGURE 30-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                                                          |                                               | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |   |     |       |                               |  |

|--------------------|----------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------|-------------------------------|--|

| Param<br>No.       | <sup>1</sup> Symbol Characteristic <sup>(1)</sup> Min Ty |                                               |                                                                                                                                                                                          |   | Max | Units | Conditions                    |  |

| SP10               | TscP                                                     | Maximum SCK Frequency                         | _                                                                                                                                                                                        | _ | 9   | MHz   | See Note 3                    |  |

| SP20               | TscF                                                     | SCKx Output Fall Time                         | —                                                                                                                                                                                        | — | _   | ns    | See parameter DO32 and Note 4 |  |