Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp204-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304, the of dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VREF+/VREF- pins used when external voltage reference for ADC module is implemented

- Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| File Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-------------------|--------|---------|--------|-----------|---------|---------|-----------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        | ADC Data Buffer 0 |        |         |        |           |         |         |           |           |       | XXXX  |        |          |          |         |               |

| AD1CON1   | 0320 | ADON   | —                 | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>  | :         | SSRC<2:0> |       | _     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | CFG<2:0           | >      | _       | _      | CSCNA     | CHP     | S<1:0>  | BUFS      | _         |       | SMPI  | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | —                 | _      |         | S      | AMC<4:0>  |         |         | ADCS<7:0> |           |       |       |        |          | 0000     |         |               |

| AD1CHS123 | 0326 | _      | _                 | _      | _       | —      | CH123N    | IB<1:0> | CH123SB | _         | _         | _     | _     | _      | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                 | _      |         | C      | H0SB<4:0> | >       |         | CH0NA     | —         | —     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _                 | _      | PCFG12  | PCFG11 | PCFG10    | PCFG9   | _       | _         | _         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _                 | _      | CSS12   | CSS11  | CSS10     | CSS9    | _       | _         | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 |        | _                 |        | _       | _      | _         | _       | _       |           | _         | _     |       | _      | [        | DMABL<2: | 0>      | 0000          |

## TABLE 4-13: ADC1 REGISTER MAP FOR dsPIC33FJ64GP202/802, dsPIC33FJ128GP202/802 AND dsPIC33FJ32GP302

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: ADC1 REGISTER MAP FOR dsPIC33FJ64GP204/804, dsPIC33FJ128GP204/804 AND dsPIC33FJ32GP304

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4 | Bit 3   | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|-----------|---------|---------|--------------|-----------|-------|-------|---------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |           |         | ADC Da  | ata Buffer 0 |           |       |       |         |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   |          | ADSIDL | ADDMABM |        | AD12B     | FOR     | M<1:0>  | :            | SSRC<2:0> |       | —     | SIMSAM  | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       |        | CSCNA     | CHP     | S<1:0>  | BUFS         | —         |       | SMP   | <3:0>   |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   |          |        |         | S      | AMC<4:0>  |         |         |              |           |       | ADCS  | \$<7:0> |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N    | NB<1:0> | CH123SB | _            | _         | _     | _     | _       | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | С      | H0SB<4:0> | >       |         | CH0NA        | _         | _     |       | С       | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      |          |        | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7        | PCFG6     | PCFG5 | PCFG4 | PCFG3   | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      |          |        | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7         | CSS6      | CSS5  | CSS4  | CSS3    | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          |        | _       | —      |           |         | —       | _            | —         | —     | —     | —       | [        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: DAC1 REGISTER MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14         | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7     | Bit 6 | Bit 5  | Bit 4 | Bit 3      | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|----------|-------------|--------|----------------|---------|--------|--------|--------|-------|--------|-----------|-------|--------|-------|------------|--------|-------|--------|---------------|

| DAC1CON  | 03F0        | DACEN  | —              | DACSIDL | AMPON  | —      | _      | —     | FORM   | —         |       |        | D     | ACFDIV<6:( | )>     |       |        | 0000          |

| DAC1STAT | 03F2        | LOEN   | —              | LMVOEN  | _      | _      | LITYPE | LFULL | LEMPTY | ROEN      | -     | RMVOEN | _     | _          | RITYPE | RFULL | REMPTY | 0000          |

| DAC1DFLT | 03F4        |        |                |         |        |        |        |       | DAC1DF | LT<15:0>  |       |        |       |            |        |       |        | 0000          |

| DAC1RDAT | 03F6        |        |                |         |        |        |        |       | DAC1RE | DAT<15:0> |       |        |       |            |        |       |        | 0000          |

| DAC1LDAT | 03F8        |        | DAC1LDAT<15:0> |         |        |        |        |       |        |           |       |        | 0000  |            |        |       |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit                                      |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Flag Status bit                                              |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

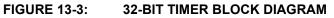

## 13.3 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

### 13.3.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

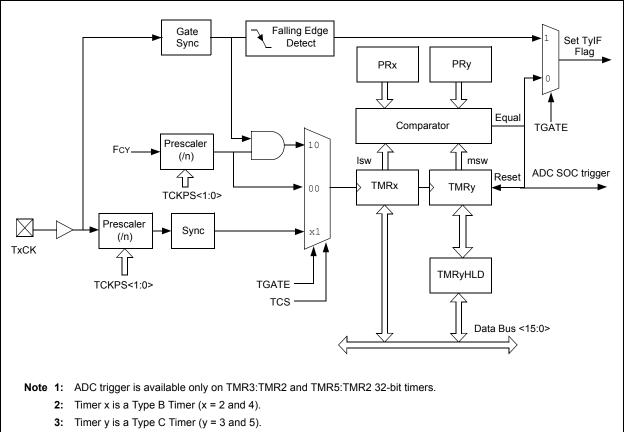

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN 2.0, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-bit or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or two stop bits

- Hardware flow control option with UxCTS and UxRTS pins

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In First-Out (FIFO) Transmit Data buffer

- · 4-deep FIFO Receive Data buffer

- · Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- · A separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- Support for sync and break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 18-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

## FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# BUFFER 19-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x              | R/W-x |  |

|-------------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

|                   |       |                  | B     | /te 3            |                 |                    |       |  |

| bit 15            |       |                  |       |                  |                 |                    | bit 8 |  |

|                   |       |                  |       |                  |                 |                    |       |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x              | R/W-x |  |

|                   |       |                  | B     | /te 2            |                 |                    |       |  |

| bit 7             |       |                  |       |                  |                 |                    | bit 0 |  |

| Legend:           |       |                  |       |                  |                 |                    |       |  |

| R = Readable b    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | ad as '0'          |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |

bit 15-8 Byte 3<15:8>: ECAN™ Message Byte 3

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2

### BUFFER 19-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | Byt   | ie 5  |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x             | R/W-x |

|-----------------|-------|------------------|-------|-------------------|-----------------|-------------------|-------|

|                 |       |                  | By    | te 4              |                 |                   |       |

| bit 7           |       |                  |       |                   |                 |                   | bit 0 |

| Legend:         |       |                  |       |                   |                 |                   |       |

| R = Readable b  | bit   | W = Writable b   | it    | U = Unimplem      | ented bit, read | d as '0'          |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red             | x = Bit is unknow | ı     |

bit 15-8 Byte 5<15:8>: ECAN™ Message Byte 5

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4

| n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is clea |                 | x = Bit is unkr | nown  |

|-----------------------------------|-------|--------------|-------|-------------------|-----------------|-----------------|-------|

| R = Readable                      | bit   | W = Writable | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| Legend:                           |       |              |       |                   |                 |                 |       |

|                                   |       |              |       |                   |                 |                 |       |

| bit 7                             |       |              |       |                   |                 |                 | bit ( |

|                                   |       |              | ADD   | R<7:0>            |                 |                 |       |

| R/W-0                             | R/W-0 | R/W-0        | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| bit 15                            |       |              |       |                   |                 |                 | bit 8 |

|                                   | 031   |              |       | ADDF              | <13.0>          |                 | 1.11  |

| ADDR15                            | CS1   |              |       |                   | <13:8>          |                 |       |

| R/W-0                             | R/W-0 | R/W-0        | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| bit 15   | ADDR15: Parallel Port Destination Address bits       |

|----------|------------------------------------------------------|

| bit 14   | CS1: Chip Select 1 bit                               |

|          | 1 = Chip select 1 is active                          |

|          | 0 = Chip select 1 is inactive                        |

| bit 13-0 | ADDR13:ADDR0: Parallel Port Destination Address bits |

## REGISTER 26-4: PMAEN: PARALLEL PORT ENABLE REGISTER

| U-0    | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0                     | R/W-0 |

|--------|--------|-----|-----|-----|-------|---------------------------|-------|

| —      | PTEN14 | —   | —   | —   | F     | PTEN<10:8> <sup>(1)</sup> | )     |

| bit 15 |        |     |     |     |       |                           | bit 8 |

| R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------------------|-------|-------|-------|-------|-------|-------|-------|

| PTEN<7:2> <sup>(1)</sup> |       |       |       |       |       |       | <1:0> |

| bit 7                    |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | PTEN14: PMCS1 Strobe Enable bit                                                                                                                  |

|           | <ul> <li>1 = PMA14 functions as either PMA&lt;14&gt; bit or PMCS1</li> <li>0 = PMA14 pin functions as port I/O</li> </ul>                        |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                       |

| bit 10-2  | PTEN<10:2>: PMP Address Port Enable bits <sup>(1)</sup>                                                                                          |

|           | <ul><li>1 = PMA&lt;10:2&gt; function as PMP address lines</li><li>0 = PMA&lt;10:2&gt; function as port I/O</li></ul>                             |

| bit 1-0   | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                        |

|           | <ul> <li>1 = PMA1 and PMA0 function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA1 and PMA0 pads functions as port I/O</li> </ul> |

Note 1: Devices with 28 pins do not have PMA<10:2>.

| TABLE 27-2: dsPIC CONFIGURATION BITS DESCRIPTION |                    |             |                                                                                                                                                              |  |  |  |  |

|--------------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                                        | Register           | RTSP Effect | Description                                                                                                                                                  |  |  |  |  |

| BWRP                                             | FBS                | Immediate   | Boot Segment Program Flash Write Protection<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                        |  |  |  |  |

| BSS<2:0>                                         | FBS                | Immediate   | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                       |  |  |  |  |

|                                                  |                    |             | Boot space is 1K Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at<br>0x0007FE                     |  |  |  |  |

|                                                  |                    |             | 010 = High security; boot program Flash segment ends at<br>0x0007FE                                                                                          |  |  |  |  |

|                                                  |                    |             | Boot space is 4K Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at<br>0x001FFE                    |  |  |  |  |

|                                                  |                    |             | 001 = High security; boot program Flash segment ends at<br>0x001FFE                                                                                          |  |  |  |  |

|                                                  |                    |             | Boot space is 8K Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at<br>0x003FFE                     |  |  |  |  |

|                                                  |                    |             | 000 = High security; boot program Flash segment ends at<br>0x003FFE                                                                                          |  |  |  |  |

| RBS<1:0> <sup>(1)</sup>                          | FBS                | Immediate   | Boot Segment RAM Code Protection Size<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 bytes<br>01 = Boot RAM is 256 bytes                                |  |  |  |  |

| SWRP <sup>(1)</sup>                              | FSS <sup>(1)</sup> | Immediate   | 00 = Boot RAM is 1024 bytes<br>Secure Segment Program Flash Write-Protect bit<br>1 = Secure Segment can bet written<br>0 = Secure Segment is write-protected |  |  |  |  |

| SSS<2:0> <sup>(1)</sup>                          | FSS <sup>(1)</sup> | Immediate   | Secure Segment Program Flash Code Protection Size<br>(Secure segment is not implemented on 32K devices)<br>X11 = No Secure program flash segment             |  |  |  |  |

|                                                  |                    |             | Secure space is 4K IW less BS<br>110 = Standard security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                              |  |  |  |  |

|                                                  |                    |             | 010 = High security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                                                                   |  |  |  |  |

|                                                  |                    |             | Secure space is 8K IW less BS<br>101 = Standard security; secure program flash segment starts at<br>End of BS, ends at 0x003FFE                              |  |  |  |  |

|                                                  |                    |             | 001 = High security; secure program flash segment starts at<br>End of BS, ends at 0x003FFE                                                                   |  |  |  |  |

|                                                  |                    |             | Secure space is 16K IW less BS<br>100 = Standard security; secure program flash segment starts at<br>End of BS, ends at 007FFEh                              |  |  |  |  |

|                                                  |                    |             | 000 = High security; secure program flash segment starts at<br>End of BS, ends at 0x007FFE                                                                   |  |  |  |  |

| TABLE 27-2: | dsPIC CONFIGURATION BITS DESCRIPTION |

|-------------|--------------------------------------|

|             |                                      |

**Note 1:** This Configuration register is not available on dsPIC33FJ32GP302/304 devices.

| TADLE 30-7:                     |                        | <b>ACTERIS</b> | 1103: 50%   |                                                 | CURREN                   | I (IPD)                                                            |  |  |

|---------------------------------|------------------------|----------------|-------------|-------------------------------------------------|--------------------------|--------------------------------------------------------------------|--|--|

| DC CHARACI                      | TERISTICS              |                | (unless oth | Dperating Content<br>Derwise state<br>Dermature | e <b>d)</b><br>-40°C ≤TA | <b>0V to 3.6V</b><br>≤+85°C for Industrial<br>≤+125°C for Extended |  |  |

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup> | Max            | Units       | Units Conditions                                |                          |                                                                    |  |  |

| Power-Down                      | Current (IPD)          | (1)            |             |                                                 |                          |                                                                    |  |  |

| DC60d                           | 24                     | 68             | μΑ          | -40°C                                           |                          |                                                                    |  |  |

| DC60a                           | 28                     | 87             | μA          | +25°C                                           | 2 2 1                    | Base Power-Down Current <sup>(3,4)</sup>                           |  |  |

| DC60b                           | 124                    | 292            | μA          | +85°C                                           | 3.3V                     | Base Power-Down Currents?                                          |  |  |

| DC60c                           | 350                    | 1000           | μA          | +125°C                                          |                          |                                                                    |  |  |

| DC61d                           | 8                      | 13             | μA          | -40°C                                           |                          |                                                                    |  |  |

| DC61a                           | 10                     | 15             | μA          | +25°C                                           | 3.3V                     | Watchdog Timer Current: ΔIWDT <sup>(3,5)</sup>                     |  |  |

| DC61b                           | 12                     | 20             | μA          | +85°C                                           | 3.3V                     |                                                                    |  |  |

| DC61c                           | 13                     | 25             | μA          | +125°C                                          | 1                        |                                                                    |  |  |

Note 1: IPD (Sleep) current is measured as follows:

CPU core is off (i.e., Sleep mode), oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

• CLKO is configured as an I/O input pin in the Configuration word

· All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD, WDT and FSCM are disabled, all peripheral modules are disabled (PMDx bits are all '1's)

- RTCC is disabled

- · JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.

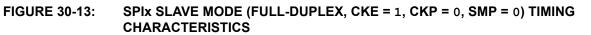

| AC CHARAG            | CTERISTICS                               | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature-40°C ≤TA ≤+85°C for Indust<br>-40°C ≤TA ≤+125°C for Exte |                                            |     |     |     |  |

|----------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex)                                                                                                            | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-29                              | —                                                                                                                                                      | —                                          | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | —                                        | Table 30-30                                                                                                                                            | —                                          | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-31                                                                                                                                            | —                                          | 0   | 0,1 | 1   |  |

| 15 MHz               | _                                        | —                                                                                                                                                      | Table 30-32                                | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                                                                                                                                      | Table 30-33                                | 1   | 1   | 0   |  |

| 15 MHz               | _                                        |                                                                                                                                                        | Table 30-34                                | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | —                                                                                                                                                      | Table 30-35                                | 0   | 0   | 0   |  |

### TABLE 30-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

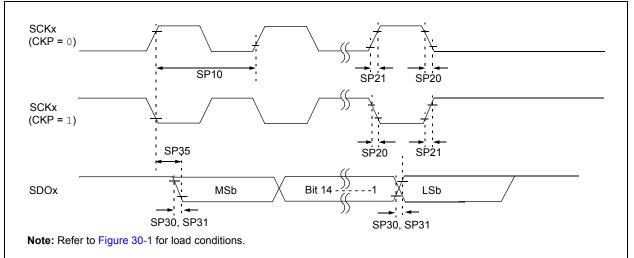

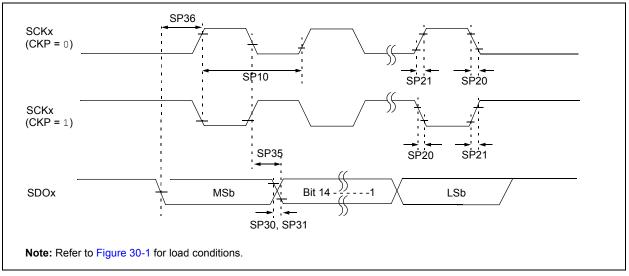

# FIGURE 30-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

# FIGURE 30-10: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 1) TIMING CHARACTERISTICS

© 2007-2012 Microchip Technology Inc.

| AC CHARACTERISTICS |                       |                                              | (unless | d Operatir<br>otherwise<br>g tempera | <b>stated)</b><br>iture -4 | 0°C ≤Ta : | <b>0V to 3.6V</b><br>≤+85°C for Industrial<br>≤+125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|---------|--------------------------------------|----------------------------|-----------|--------------------------------------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min     | Тур <sup>(2)</sup>                   | Max                        | Units     | Conditions                                                         |

| SP10               | TscP                  | Maximum SCK Frequency                        | —       | _                                    | 15                         | MHz       | See Note 3                                                         |

| SP20               | TscF                  | SCKx Output Fall Time                        | -       | —                                    | _                          | ns        | See parameter DO32<br>and Note 4                                   |

| SP21               | TscR                  | SCKx Output Rise Time                        | —       | —                                    |                            | ns        | See parameter DO31 and Note 4                                      |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | _       | —                                    | _                          | ns        | See parameter DO32 and Note 4                                      |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | _       | —                                    | _                          | ns        | See parameter DO31 and Note 4                                      |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —       | 6                                    | 20                         | ns        | _                                                                  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30      | _                                    | _                          | ns        | —                                                                  |

## TABLE 30-29: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHARACTERISTICS |        |                                |           | otherwi   | se stateo<br>rature | <b>d)</b><br>-40°C ≤ | : <b>3.0V to 3.6V</b><br>TA ≤+85°C for Industrial<br>TA ≤+125°C for Extended |

|--------------------|--------|--------------------------------|-----------|-----------|---------------------|----------------------|------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                 | Min.      | Тур       | Max.                | Units                | Conditions                                                                   |

|                    |        | ADC Accuracy (10-bit Mode      | ) – Meas  | urement   | ts with e           | xternal              | VREF+/VREF-                                                                  |

| AD20b              | Nr     | Resolution <sup>(1)</sup>      | 1(        | ) data bi | ts                  | bits                 | —                                                                            |

| AD21b              | INL    | Integral Nonlinearity          | -1.5      | _         | +1.5                | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD22b              | DNL    | Differential Nonlinearity      | > -1      | _         | < 1                 | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD23b              | Gerr   | Gain Error                     | —         | 3         | 6                   | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                             |

| AD24b              | EOFF   | Offset Error                   | —         | 2         | 5                   | LSb                  | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V                             |

| AD25b              | —      | Monotonicity                   | —         | —         | _                   | _                    | Guaranteed                                                                   |

|                    |        | ADC Accuracy (10-bit Mode      | e) – Meas | uremen    | ts with ir          | nternal V            | VREF+/VREF-                                                                  |

| AD20b              | Nr     | Resolution <sup>(1)</sup>      | 1(        | ) data bi | ts                  | bits                 | —                                                                            |

| AD21b              | INL    | Integral Nonlinearity          | -1        | —         | +1                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD22b              | DNL    | Differential Nonlinearity      | > -1      | —         | < 1                 | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD23b              | Gerr   | Gain Error                     | 3         | 7         | 15                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD24b              | EOFF   | Offset Error                   | 1.5       | 3         | 7                   | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                                |

| AD25b              | —      | Monotonicity                   |           |           | _                   |                      | Guaranteed                                                                   |

|                    |        | Dynamic                        | Performa  | nce (10-  | bit Mode            | e)                   |                                                                              |

| AD30b              | THD    | Total Harmonic Distortion      | _         |           | -64                 | dB                   | —                                                                            |

| AD31b              | SINAD  | Signal to Noise and Distortion | 57        | 58.5      | _                   | dB                   | _                                                                            |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range | 72        | _         |                     | dB                   | _                                                                            |

| AD33b              | Fnyq   | Input Signal Bandwidth         | _         |           | 550                 | kHz                  | —                                                                            |

| AD34b              | ENOB   | Effective Number of Bits       | 9.16      | 9.4       | _                   | bits                 |                                                                              |

## TABLE 30-43: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

# 31.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0 "Electrical Characteristics"** for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 30.0 "Electrical Characteristics**" is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(5)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(5)}$      | -0.3V to 5.6V        |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     |                      |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sunk by all ports combined                                        |                      |

| Maximum current sourced by all ports combined <sup>(2)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGCx, and PGDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

| TABLE 31-17: | ADC CONVERSION | 12-BIT MODE | ) TIMING REQUIREMENTS |

|--------------|----------------|-------------|-----------------------|

|--------------|----------------|-------------|-----------------------|

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |                  |          |     |       |            |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-----|-------|------------|

| Param<br>No.          | Symbol | Characteristic                                                                                                                   | Min              | Тур      | Мах | Units | Conditions |

| Clock Parameters      |        |                                                                                                                                  |                  |          |     |       |            |

| 1                     |        |                                                                                                                                  |                  |          |     |       |            |

| HAD50                 | Tad    | ADC Clock Period <sup>(1)</sup>                                                                                                  | 147              | _        | _   | ns    | —          |

| HAD50                 | TAD    |                                                                                                                                  | 147<br>version R | <br>late | _   | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

## TABLE 31-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |     |     |     |       |            |  |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.          | Symbol | Characteristic                                                                                                                   | Min | Тур | Max | Units | Conditions |  |

| Clock Parameters      |        |                                                                                                                                  |     |     |     |       |            |  |

| HAD50                 | Tad    | ADC Clock Period <sup>(1)</sup>                                                                                                  | 104 | —   |     | ns    | —          |  |

| Conversion Rate       |        |                                                                                                                                  |     |     |     |       |            |  |

| HAD56                 | FCNV   | Throughput Rate <sup>(1)</sup>                                                                                                   | _   | —   | 800 | Ksps  | _          |  |

Note 1: These parameters are characterized but not tested in manufacturing.

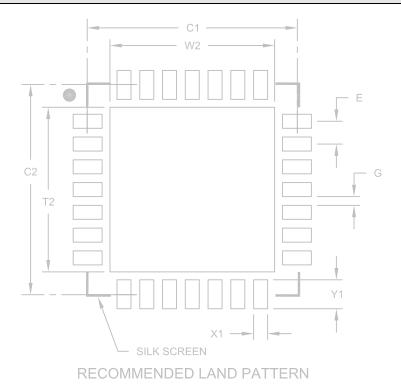

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension Limits           |             | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.70 |

| Optional Center Pad Length | T2          |      |          | 4.70 |

| Contact Pad Spacing        | C1          |      | 6.00     |      |

| Contact Pad Spacing        | C2          |      | 6.00     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.40 |

| Contact Pad Length (X28)   | Y1          |      |          | 0.85 |

| Distance Between Pads      | G           | 0.25 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

## Revision C (May 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

The other changes are referenced by their respective section in the following table.

#### TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                              | Update Description                                                                                                                          |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, 16-bit Digital<br>Signal Controllers                                    | Updated all pin diagrams to denote the pin voltage tolerance (see " <b>Pin Diagrams</b> ").                                                 |

|                                                                                           | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                                      |

| Section 1.0 "Device Overview"                                                             | Updated AVDD in the PINOUT I/O Descriptions (see Table 1-1).                                                                                |

|                                                                                           | Added Peripheral Pin Select (PPS) capability column to Pinout I/O Descriptions (see Table 1-1).                                             |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Digital Signal<br>Controllers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Digital Signal Controllers.                     |

| Section 3.0 "CPU"                                                                         | Updated CPU Core Block Diagram with a connection from the DSP Engine to the Y Data Bus (see Figure 3-1).                                    |

|                                                                                           | Vertically extended the X and Y Data Bus lines in the DSP Engine Block Diagram (see Figure 3-3).                                            |

| Section 4.0 "Memory Organization"                                                         | Updated Reset value for CORCON in the CPU Core Register Map (see Table 4-1).                                                                |

|                                                                                           | Updated the Reset values for IPC14 and IPC15 and removed the FLTA1IE bit (IEC3) from the Interrupt Controller Register Map (see Table 4-4). |

|                                                                                           | Updated bit locations for RPINR25 in the Peripheral Pin Select Input Register Map (see Table 4-21).                                         |

|                                                                                           | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 4-33).                                                     |

| Section 5.0 "Flash Program<br>Memory"                                                     | Updated <b>Section 5.3 "Programming Operations"</b> with programming time formula.                                                          |

| Section 9.0 "Oscillator<br>Configuration"                                                 | Updated the Oscillator System Diagram and added Note 2 (see Figure 9-1).                                                                    |

| Comgulation                                                                               | Added Note 1 and Note 2 to the OSCON register (see Register 9-1).                                                                           |

|                                                                                           | Updated default bit values for DOZE<2:0> and FRCDIV<2:0> in the Clock Divisor (CLKDIV) Register (see Register 9-2).                         |

|                                                                                           | Added a paragraph regarding FRC accuracy at the end of <b>Section 9.1.1</b> "System Clock Sources".                                         |

|                                                                                           | Added Note 3 to Section 9.2.2 "Oscillator Switching Sequence".                                                                              |

|                                                                                           | Added Note 1 to the FRC Oscillator Tuning (OSCTUN) Register (see Register 9-4).                                                             |

| Section Name                                 | Update Description                                                                                                                                                                 |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical<br>Characteristics" | Updated Typical values for Thermal Packaging Characteristics (see Table 30-3).                                                                                                     |

|                                              | Updated Min and Max values for parameter DC12 (RAM Data Retention Voltage) and added Note 4 (see Table 30-4).                                                                      |

|                                              | Updated Power-Down Current Max values for parameters DC60b and DC60c (see Table 30-7).                                                                                             |

|                                              | Updated Characteristics for I/O Pin Input Specifications and added parameter DI21 (see Table 30-9).                                                                                |

|                                              | Updated Program Memory values for parameters 136, 137, and 138<br>(renamed to 136a, 137a, and 138a), added parameters 136b, 137b, and<br>138b, and added Note 2 (see Table 30-12). |

|                                              | Added parameter OS42 (Gм) to the External Clock Timing Requirements (see Table 30-16).                                                                                             |

|                                              | Updated Watchdog Timer Time-out Period parameter SY20 (see Table 30-21).                                                                                                           |

|                                              | Updated the IREF Current Drain parameter AD08 (see Table 30-37).                                                                                                                   |

|                                              | Updated parameters AD30a, AD31a, AD32a, AD33a, and AD34a (see<br>Table 30-38)                                                                                                      |

|                                              | Updated parameters AD30b, AD31b, AD32b, AD33b, and AD34b (see Table 30-39)                                                                                                         |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)