Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp204-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.5 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

#### 3.5.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# TABLE 4-10: UART2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                                 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------------------------------------|--------|----------|--------|--------|--------|-------|-------|--------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230        | UARTEN                                 | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE   | LPBACK  | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232        | UTXISEL1                               | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISI | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234        | _                                      | _      | —        | _      | —      | _      | _     | UTX8  |        |         | U     | ART Transn | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236        | — — — — — — URX8 UART Receive Register |        |          |        |        |        |       |       |        |         | 0000  |            |              |       |        |       |               |

| U2BRG    | 0238        | Baud Rate Generator Prescaler          |        |          |        |        |        |       |       |        |         |       | 0000       |              |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: SPI1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|------------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL | —      | _      | —      |            |             |              | SPIROV   | —     | -     | _         |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | —      | —      | _          | _           | _            | _        | —     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Red | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-12: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                    | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|-------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | -                                         | SPISIDL | _      | —      | —      |       | —     |       | SPIROV | _     | -     | —         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _                                         | -       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD                                    | FRMPOL  | _      | _      | —      | _     | _     | _     | _      | _     | —     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        |        | SPI2 Transmit and Receive Buffer Register |         |        |        |        |       |       |       |        |       | 0000  |           |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12  | Bit 11              | Bit 10    | Bit 9   | Bit 8   | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|---------|--------|---------|---------------------|-----------|---------|---------|-------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |         |        |         |                     |           |         | ADC Da  | ta Buffer 0 |           |       |       |        |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   | —       | ADSIDL | ADDMABM | _                   | AD12B     | FOR     | M<1:0>  | :           | SSRC<2:0> |       | _     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | CFG<2:0 | >      | _       | _                   | CSCNA     | CHP     | S<1:0>  | BUFS        | —         |       | SMPI  | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | —       | _      |         | SAMC<4:0> ADCS<7:0> |           |         |         |             |           |       | 0000  |        |          |          |         |               |

| AD1CHS123 | 0326 | _      | _       | _      | _       | —                   | CH123N    | IB<1:0> | CH123SB | _           | _         | _     | _     | _      | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _       | _      |         | C                   | H0SB<4:0> | >       |         | CH0NA       | —         | —     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _       | _      | PCFG12  | PCFG11              | PCFG10    | PCFG9   | _       | _           | —         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _       | _      | CSS12   | CSS11               | CSS10     | CSS9    | _       | _           | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 |        | _       |        | _       | _                   | _         | _       | _       |             | _         | —     |       | _      | [        | DMABL<2: | 0>      | 0000          |

#### TABLE 4-13: ADC1 REGISTER MAP FOR dsPIC33FJ64GP202/802, dsPIC33FJ128GP202/802 AND dsPIC33FJ32GP302

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: ADC1 REGISTER MAP FOR dsPIC33FJ64GP204/804, dsPIC33FJ128GP204/804 AND dsPIC33FJ32GP304

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|-----------|---------|---------|--------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |           |         | ADC Da  | ata Buffer 0 |           |       |       |        |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   |          | ADSIDL | ADDMABM |        | AD12B     | FOR     | M<1:0>  | :            | SSRC<2:0> |       | —     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       |        | CSCNA     | CHP     | S<1:0>  | BUFS         | —         |       | SMP   | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   |          |        |         | S      | AMC<4:0>  |         |         | ADCS<7:0>    |           |       |       |        |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N    | NB<1:0> | CH123SB | _            | _         | _     | _     | _      | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | С      | H0SB<4:0> | >       |         | CH0NA        | _         | _     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      |          |        | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7        | PCFG6     | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      |          |        | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7         | CSS6      | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          |        | _       | —      |           |         | —       | _            | —         | —     | —     | —      | [        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: DAC1 REGISTER MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7     | Bit 6 | Bit 5  | Bit 4 | Bit 3      | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-------|--------|-----------|-------|--------|-------|------------|--------|-------|--------|---------------|

| DAC1CON  | 03F0        | DACEN  | —      | DACSIDL | AMPON  | —      | _      | —     | FORM   | —         |       |        | D     | ACFDIV<6:( | )>     |       |        | 0000          |

| DAC1STAT | 03F2        | LOEN   | —      | LMVOEN  | _      | _      | LITYPE | LFULL | LEMPTY | ROEN      | -     | RMVOEN | _     | _          | RITYPE | RFULL | REMPTY | 0000          |

| DAC1DFLT | 03F4        |        |        |         |        |        |        |       | DAC1DF | LT<15:0>  |       |        |       |            |        |       |        | 0000          |

| DAC1RDAT | 03F6        |        |        |         |        |        |        |       | DAC1RE | DAT<15:0> |       |        |       |            |        |       |        | 0000          |

| DAC1LDAT | 03F8        |        |        |         |        |        |        |       | DAC1LD | AT<15:0>  |       |        |       |            |        |       |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER      | 7-6: IFS1:    | INTERRUPT                            | FLAG STAT           | US REGISTE       | ER 1            |                 |         |

|---------------|---------------|--------------------------------------|---------------------|------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0         | R/W-0                                | R/W-0               | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| U2TXIF        | U2RXIF        | INT2IF                               | T5IF                | T4IF             | OC4IF           | OC3IF           | DMA2IF  |

| bit 15        |               |                                      |                     |                  |                 |                 | bit 8   |

| R/W-0         | R/W-0         | U-0                                  | R/W-0               | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| IC8IF         | IC7IF         |                                      | INT1IF              | CNIF             | CMIF            | MI2C1IF         | SI2C1IF |

| bit 7         |               |                                      |                     |                  |                 |                 | bit (   |

| Legend:       |               |                                      |                     |                  |                 |                 |         |

| R = Readable  | e bit         | W = Writable                         | e bit               | U = Unimpler     | nented bit, rea | d as '0'        |         |

| -n = Value at | POR           | '1' = Bit is se                      | t                   | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |

|               |               |                                      |                     |                  |                 |                 |         |

| bit 15        | U2TXIF: UA    | RT2 Transmitte                       | er Interrupt Flag   | g Status bit     |                 |                 |         |

|               |               | t request has or                     |                     |                  |                 |                 |         |

| bit 14        | •             | t request has no                     |                     | Yetus hit        |                 |                 |         |

| DIL 14        |               | RT2 Receiver<br>t request has or     |                     |                  |                 |                 |         |

|               |               | t request has no                     |                     |                  |                 |                 |         |

| bit 13        | INT2IF: Exte  | ernal Interrupt 2                    | Flag Status bit     | t                |                 |                 |         |

|               |               | t request has o                      |                     |                  |                 |                 |         |

|               |               | t request has no                     |                     |                  |                 |                 |         |

| bit 12        |               | 5 Interrupt Flag                     |                     |                  |                 |                 |         |

|               |               | t request has or<br>t request has no |                     |                  |                 |                 |         |

| bit 11        |               | 4 Interrupt Flag                     |                     |                  |                 |                 |         |

|               |               | t request has o                      |                     |                  |                 |                 |         |

|               | 0 = Interrupt | t request has no                     | ot occurred         |                  |                 |                 |         |

| bit 10        | •             | out Compare C                        |                     | upt Flag Status  | bit             |                 |         |

|               |               | t request has or<br>t request has no |                     |                  |                 |                 |         |

| bit 9         |               | out Compare C                        |                     | upt Flag Status  | bit             |                 |         |

|               | •             | t request has or<br>t request has no |                     |                  |                 |                 |         |

| bit 8         | -             | MA Channel 2 [                       |                     | complete Interr  | upt Flag Status | s bit           |         |

|               |               | t request has o                      |                     |                  | apt ing claim   |                 |         |

|               | 0 = Interrupt | t request has no                     | ot occurred         |                  |                 |                 |         |

| bit 7         | •             | Capture Chann                        | •                   | lag Status bit   |                 |                 |         |

|               |               | t request has or<br>t request has no |                     |                  |                 |                 |         |

| bit 6         | IC7IF: Input  | Capture Chann                        | nel 7 Interrupt F   | ag Status bit    |                 |                 |         |

|               |               | t request has or<br>t request has no |                     |                  |                 |                 |         |

| bit 5         | Unimpleme     | nted: Read as                        | <b>'</b> 0 <b>'</b> |                  |                 |                 |         |

| bit 4         | INT1IF: Exte  | ernal Interrupt 1                    | Flag Status bit     | t                |                 |                 |         |

|               |               | t request has o                      |                     |                  |                 |                 |         |

|               |               | t request has no                     |                     |                  |                 |                 |         |

| bit 3         |               | Change Notific                       | -                   | Flag Status bit  |                 |                 |         |

|               |               | t request has or<br>t request has no |                     |                  |                 |                 |         |

|               |               |                                      |                     |                  |                 |                 |         |

# REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

## 7.6 Interrupt Setup Procedures

#### 7.6.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level depends on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.6.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development tool suite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program re-enters the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.6.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.6.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 devices can manage power consumption in four ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake up.

## 10.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode PWRSAV #IDLE MODE ; Put the device into IDLE mode

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                    |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                              |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.</li> <li>Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as $l^2C$ master)                                                                                                                                                        |

|       | 1 = Enables Receive mode for $l^2C$ . Hardware clear at end of eighth bit of master receive data byte<br>0 = Receive sequence not in progress                                                                            |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                        |

|       | 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence<br>0 = Stop condition not in progress                                                                                   |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                             |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                     |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                             |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                              |

|       | <ul><li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li><li>0 = Start condition not in progress</li></ul>                                                         |

# 18.3 UART Control Registers

# REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN   | <1:0> |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|-------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7    |        |          |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | <ul> <li>UARTEN: UARTx Enable bit<sup>(1)</sup></li> <li>1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN&lt;1:0&gt;</li> <li>0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption minimal</li> </ul>                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                           |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = IrDA<sup>®</sup> encoder and decoder enabled</li> <li>0 = IrDA<sup>®</sup> encoder and decoder disabled</li> </ul>                                                                                                                                                                                                                                                                 |

| bit 11  | <b>RTSMD:</b> Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = <u>UxRTS</u> pin in Simplex mode<br>0 = UxRTS pin in Flow Control mode                                                                                                                                                                                                                                                                                                                      |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up enabled</li> </ul>                                                                                                                                                                                                       |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                          |

|         | 1 = Enable Loopback mode<br>0 = Loopback mode is disabled                                                                                                                                                                                                                                                                                                                                       |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul>                                                                                                                                                           |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

# 23.1 Comparator Resources

Many useful resources related to Comparators are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en532311                                        |

#### 23.1.1 KEY RESOURCES

- Section 34. "Comparator" (DS70212)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### 25.5 Programmable CRC Registers

#### **CRCCON: CRC CONTROL REGISTER** REGISTER 25-1: R/W-0 U-0 U-0 R-0 R-0 R-0 R-0 R-0 CSIDL VWORD<4:0> \_ bit 15 bit 8 R/W-0 R-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 CRCFUL CRCMPT CRCGO PLEN<3:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 CSIDL: CRC Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12-8 VWORD<4:0>: Pointer Value bits Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> is greater than 7, or 16 when PLEN<3:0> is less than or equal to 7. bit 7 **CRCFUL:** FIFO Full bit 1 = FIFO is full 0 = FIFO is not full bit 6 **CRCMPT:** FIFO Empty bit 1 = FIFO is empty 0 = FIFO is not empty bit 5 Unimplemented: Read as '0' bit 4 CRCGO: Start CRC bit 1 = Start CRC serial shifter 0 = Turn off CRC serial shifter after FIFO is empty bit 3-0 PLEN<3:0>: Polynomial Length bits Denotes the length of the polynomial to be generated minus 1.

# REGISTER 26-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER (CONTINUED)

| bit 2 | <b>BEP:</b> Byte Enable Polarity bit<br>1 = Byte enable active-high (PMBE)<br>0 = Byte enable active-low (PMBE) |

|-------|-----------------------------------------------------------------------------------------------------------------|

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                 |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00, 01, 10):                                                   |

|       | 1 = Write strobe active-high (PMWR)                                                                             |

|       | 0 = Write strobe active-low (PMWR)                                                                              |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                           |

|       | 1 = Enable strobe active-high (PMENB)                                                                           |

|       | $0 = \text{Enable strobe active-low } (\overline{\text{PMENB}})$                                                |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                  |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00, 01, 10):                                                   |

|       | 1 = Read strobe active-high (PMRD)                                                                              |

|       | 0 = Read strobe active-low (PMRD)                                                                               |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                           |

|       | 1 = Read/write strobe active-high (PMRD/PMWR)                                                                   |

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** These bits have no effect when their corresponding pins are used as address lines.

| REGISTER | 26-5: PMSTA | T: PARALLI | EL PORT ST | ATUS REGI | STER |      |       |

|----------|-------------|------------|------------|-----------|------|------|-------|

| R-0      | R/W-0, HS   | U-0        | U-0        | R-0       | R-0  | R-0  | R-0   |

| IBF      | IBOV        |            | _          | IB3F      | IB2F | IB1F | IB0F  |

| bit 15   |             |            |            |           |      |      | bit 8 |

|          |             |            |            |           |      |      |       |

| R-1      | R/W-0, HS   | U-0        | U-0        | R-1       | R-1  | R-1  | R-1   |

| bit 7             |                       |                       | bit 0              |

|-------------------|-----------------------|-----------------------|--------------------|

|                   |                       |                       |                    |

| Legend:           | HS = Hardware Set bit |                       |                    |

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared  | x = Bit is unknown |

OB3E

OB2E

| bit 15    | IBF: Input Buffer Full Status bit                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ol> <li>All writable input buffer registers are full</li> </ol>                                                                                                          |

|           | 0 = Some or all of the writable input buffer registers are empty                                                                                                          |

| bit 14    | IBOV: Input Buffer Overflow Status bit                                                                                                                                    |

|           | <ul> <li>1 = A write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul>                            |

| bit 13-12 | Unimplemented: Read as '0'                                                                                                                                                |

| bit 11-8  | IB3F:IB0F: Input Buffer x Status Full bits                                                                                                                                |

|           | <ul> <li>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)</li> <li>0 = Input buffer does not contain any unread data</li> </ul> |

| bit 7     | OBE: Output Buffer Empty Status bit                                                                                                                                       |

|           | 1 = All readable output buffer registers are empty                                                                                                                        |

|           | 0 = Some or all of the readable output buffer registers are full                                                                                                          |

| bit 6     | OBUF: Output Buffer Underflow Status bits                                                                                                                                 |

|           | 1 = A read occurred from an empty output byte register (must be cleared in software)                                                                                      |

|           | 0 = No underflow occurred                                                                                                                                                 |

| bit 5-4   | Unimplemented: Read as '0'                                                                                                                                                |

| bit 3-0   | OB3E:OB0E: Output Buffer x Status Empty bit                                                                                                                               |

|           | 1 = Output buffer is empty (writing data to the buffer will clear this bit)                                                                                               |

|           | 0 = Output buffer contains data that has not been transmitted                                                                                                             |

|           |                                                                                                                                                                           |

OBE

OBUF

OB0E

OB1E

# **30.1 DC Characteristics**

#### TABLE 30-1: OPERATING MIPS VS. VOLTAGE

|                |                         |                       | Max MIPS                                                                    |

|----------------|-------------------------|-----------------------|-----------------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts) | Temp Range<br>(in °C) | dsPIC33FJ32GP302/304,<br>dsPIC33FJ64GPX02/X04, and<br>dsPIC33FJ128GPX02/X04 |

| _              | 3.0-3.6V <sup>(1)</sup> | -40°C to +85°C        | 40                                                                          |

|                | 3.0-3.6V <sup>(1)</sup> | -40°C to +125°C       | 40                                                                          |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 30-11 for the minimum and maximum BOR values.

# TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                            | Symbol | Min              | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------------|--------|------------------|-------------|------|------|

| Industrial Temperature Devices                                                                    |        |                  |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40              | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40              | —           | +85  | °C   |

| Extended Temperature Devices                                                                      |        |                  |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40              | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                               |        | -40              | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ | PD     | PD PINT + PI/O \ |             | W    |      |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)           |        |                  |             |      |      |

| Maximum Allowed Power Dissipation                                                                 | PDMAX  | (                | TJ — TA)/θJ | IA   | W    |

## TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Мах | Unit | Note |

|------------------------------------------|--------|-----|-----|------|------|

| Package Thermal Resistance, 44-pin QFN   | θja    | 30  | _   | °C/W | 1    |

| Package Thermal Resistance, 44-pin TFQP  | θја    | 40  | _   | °C/W | 1    |

| Package Thermal Resistance, 28-pin SPDIP | θја    | 45  | _   | °C/W | 1    |

| Package Thermal Resistance, 28-pin SOIC  | θја    | 50  | _   | °C/W | 1    |

| Package Thermal Resistance, 28-pin QFN-S | θја    | 30  | —   | °C/W | 1    |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# 31.1 High Temperature DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                             |                              | Max MIPS                                                                    |  |  |

|----------------|-----------------------------|------------------------------|-----------------------------------------------------------------------------|--|--|

| Characteristic | VDD Range<br>(in Volts)     | Temperature Range<br>(in °C) | dsPIC33FJ32GP302/304,<br>dsPIC33FJ64GPX02/X04, and<br>dsPIC33FJ128GPX02/X04 |  |  |

|                | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +150°C              | 20                                                                          |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized.

## TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min             | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|-----|------|------|

| High Temperature Devices                                                                                                                                                               |        |                 |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40             | _   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40             | _   | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O     |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax  | (TJ - TA)/θJA Μ |     | W    |      |

#### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                |                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |     |     |   |                 |

|--------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|-----------------|

| Parameter<br>No.   | Symbol         | Characteristic | Min Typ Max Units Conditions                                                                                                                             |     |     |   | Conditions      |

| Operating V        | Voltage        |                |                                                                                                                                                          |     |     |   |                 |

| HDC10              | Supply Voltage |                |                                                                                                                                                          |     |     |   |                 |

|                    | Vdd            | _              | 3.0                                                                                                                                                      | 3.3 | 3.6 | V | -40°C to +150°C |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS (     |         |      | (unless oth | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |      |                                               |  |

|--------------------------|---------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------|--|

| Parameter<br>No.         | Typical | Мах  | Units       | Conditions                                                                                                                      |      |                                               |  |

| Power-Down Current (IPD) |         |      |             |                                                                                                                                 |      |                                               |  |

| HDC60e                   | 250     | 2000 | μA          | +150°C                                                                                                                          | 3.3V | Base Power-Down Current <sup>(1,3)</sup>      |  |

| HDC61c                   | 3       | 5    | μΑ          | +150°C                                                                                                                          | 3.3V | Watchdog Timer Current: $\Delta IWDT^{(2,4)}$ |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 31-5: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERISTICS |                        |     | (unless oth   | nerwise s | ,          |      | <b>V</b><br>or High Temperature |

|--------------------|------------------------|-----|---------------|-----------|------------|------|---------------------------------|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах | Doze<br>Ratio | Units     | Conditions |      |                                 |

| HDC72a             | 39                     | 45  | 1:2           | mA        |            |      |                                 |

| HDC72f             | 18                     | 25  | 1:64          | mA        | +150°C     | 3.3V | 20 MIPS                         |

| HDC72g             | 18                     | 25  | 1:128         | mA        |            |      |                                 |

**Note 1:** Parameters with Doze ratios of 1:2 and 1:64 are characterized, but are not tested in manufacturing.

# **Revision D (November 2009)**

The revision includes the following global update:

• Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                      | Update Description                                                                                                                                                                                           |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Digital Signal Controllers"             | Added information on high temperature operation (see <b>"Operating Range:</b> ").                                                                                                                            |

| Section 11.0 "I/O Ports"                                          | Changed the reference to digital-only pins to 5V tolerant pins in the second paragraph of <b>Section 11.2</b> " <b>Open-Drain Configuration</b> ".                                                           |

| Section 18.0 "Universal Asynchronous Receiver Transmitter (UART)" | Updated the two baud rate range features to: 10 Mbps to 38 bps at 40 MIPS.                                                                                                                                   |

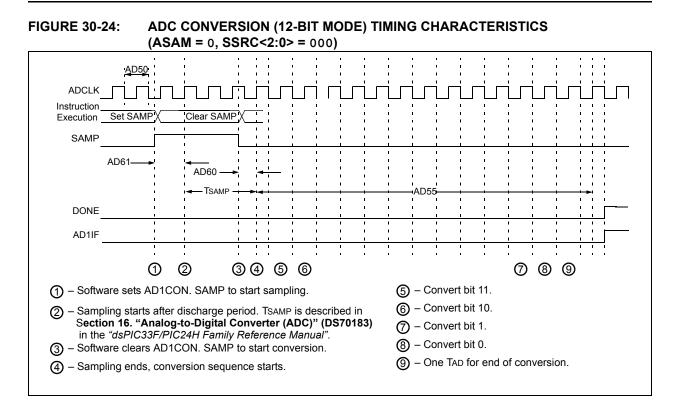

| Section 21.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"    | Updated the ADC block diagrams (see Figure 21-1 and Figure 21-2).                                                                                                                                            |

| Section 22.0 "Audio Digital-to-Analog<br>Converter (DAC)"         | Removed last sentence of the first paragraph in the section.<br>Added a shaded note to <b>Section 22.2 "DAC Module Operation"</b> .<br>Updated Figure 22-2: "Audio DAC Output for Ramp Input<br>(Unsigned)". |

| Section 27.0 "Special Features"                                   | Updated the second paragraph and removed the fourth paragraph in <b>Section 27.1 "Configuration Bits"</b> .<br>Updated the Device Configuration Register Map (see Table 27-1).                               |

| Section 30.0 "Electrical Characteristics"                         | Updated the Absolute Maximum Ratings for high temperature and added Note 4.<br>Removed parameters DI26, DI28, and DI29 from the I/O Pin Input Specifications (see Table 30-9).                               |

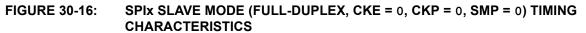

|                                                                   | Updated the SPIx Module Slave Mode (CKE = 1) Timing<br>Characteristics (see Figure 30-12).                                                                                                                   |

|                                                                   | Removed Table 30-43: Audio DAC Module Specifications. Original contents were updated and combined with Table 30-42 of the same name.                                                                         |

| Section 31.0 "High Temperature Electrical Characteristics"        | Added new chapter with high temperature specifications.                                                                                                                                                      |

| "Product Identification System"                                   | Added the "H" definition for high temperature.                                                                                                                                                               |

# Revision F (August 2011)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

## TABLE A-5: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                 |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the Recommendation Minimum Connection (see Figure 2-1).                                                                    |

| Section 27.0 "Special Features"                                                     | Added Note 3 to the Connections for the On-chip Voltage Regulator diagram (see Figure 27-1).                                       |

| Section 30.0 "Electrical Characteristics"                                           | Removed Voltage on VCAP with respect to Vss from the Absolute Maximum Ratings.                                                     |

|                                                                                     | Removed Note 3 and parameter DC10 (VCORE) from the DC Temperature and Voltage Specifications (see Table 30-4).                     |

|                                                                                     | Updated the Characteristics definition and Conditions for parameter BO10 in the Electrical Characteristics: BOR (see Table 30-11). |

|                                                                                     | Added Note 1 to the Internal Voltage Regulator Specifications (see Table 30-13).                                                   |

# **Revision G (April 2012)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 9.2 "Oscillator Resources" and Section 21.4 "ADC Helpful Tips".

All other major changes are referenced by their respective section in the following table.

#### TABLE A-6: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                                     |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Added two new tables:<br>• Crystal Recommendations (see Table 2-1)                                                                                     |

|                                                                                     | Resonator Recommendations (see Table 2-2)                                                                                                              |

| Section 30.0 "Electrical Characteristics"                                           | Updated parameters DO10 and DO20 and removed parameters<br>DO16 and DO26 in the DC Characteristics: I/O Pin Output<br>Specifications (see Table 30-10) |