Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 13x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp204t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0                            | U-0                                    | R/W-0                             | R/W-0                        | R-0             | R-0              | R-0         |

|-----------------|--------------------------------|----------------------------------------|-----------------------------------|------------------------------|-----------------|------------------|-------------|

| _               | _                              |                                        | US                                | EDT <sup>(1)</sup>           |                 | DL<2:0>          |             |

| pit 15          |                                | ·                                      |                                   |                              |                 |                  | bit 8       |

| R/W-0           | D/M/ O                         |                                        | R/W-0                             |                              |                 | R/W-0            |             |

| SATA            | R/W-0<br>SATB                  | R/W-1<br>SATDW                         | ACCSAT                            | R/C-0<br>IPL3 <sup>(2)</sup> | R/W-0<br>PSV    | R/W-0            | R/W-0<br>IF |

| bit 7           | SAID                           | SAIDW                                  | ACCSAT                            | IFL3' /                      | F3V             | RND              | bit         |

| Legend:         |                                | C = Clear on                           | y bit                             |                              |                 |                  |             |

| R = Readable    | e bit                          | W = Writable                           | bit                               | -n = Value at                | -               | '1' = Bit is set |             |

| 0' = Bit is cle | ared                           | ʻx = Bit is unk                        | nown                              | U = Unimplen                 | nented bit, rea | ad as '0'        |             |

| bit 15-13       | Unimplemer                     | nted: Read as                          | 0'                                |                              |                 |                  |             |

| bit 12          | •                              | Itiply Unsigned                        |                                   | ol bit                       |                 |                  |             |

|                 |                                | ine multiplies a                       | -                                 |                              |                 |                  |             |

|                 | •                              | ine multiplies a                       | •                                 |                              |                 |                  |             |

| bit 11          | EDT: Early D                   | O Loop Termina                         | ation Control b                   | it <sup>(1)</sup>            |                 |                  |             |

|                 | 1 = Terminate<br>0 = No effect | e executing DO                         | loop at end of                    | current loop ite             | eration         |                  |             |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                           | Level Status bi                   | its                          |                 |                  |             |

|                 | 111 <b>= 7</b> do <b>k</b>     | oops active                            |                                   |                              |                 |                  |             |

|                 | •                              |                                        |                                   |                              |                 |                  |             |

|                 | •<br>001 = 1 DO lo             | oon active                             |                                   |                              |                 |                  |             |

|                 | 000 = 0 DO lo                  | •                                      |                                   |                              |                 |                  |             |

| bit 7           | SATA: ACCA                     | Saturation En                          | able bit                          |                              |                 |                  |             |

|                 |                                | ator A saturatio<br>ator A saturatio   |                                   |                              |                 |                  |             |

| bit 6           | SATB: ACCE                     | 3 Saturation En                        | able bit                          |                              |                 |                  |             |

|                 |                                | ator B saturatio<br>ator B saturatio   |                                   |                              |                 |                  |             |

| bit 5           | SATDW: Dat                     | a Space Write                          | from DSP Eng                      | ine Saturation               | Enable bit      |                  |             |

|                 |                                | ce write satura<br>ce write satura     |                                   |                              |                 |                  |             |

| bit 4           | ACCSAT: Ac                     | cumulator Satu                         | ration Mode S                     | elect bit                    |                 |                  |             |

|                 |                                | iration (super s<br>iration (normal    |                                   |                              |                 |                  |             |

| bit 3           |                                | nterrupt Priority                      |                                   |                              |                 |                  |             |

|                 |                                | rrupt priority le<br>rrupt priority le | 0                                 |                              |                 |                  |             |

| bit 2           | PSV: Program                   | m Space Visibil                        | ity in Data Spa                   | ice Enable bit               |                 |                  |             |

|                 |                                | space visible in                       |                                   |                              |                 |                  |             |

| L:1 1           | •                              | space not visit                        | •                                 | ce                           |                 |                  |             |

| bit 1           |                                | ing Mode Sele                          |                                   | d                            |                 |                  |             |

|                 | 0 = Unbiased                   | conventional) ro<br>d (convergent)     | rounding enab                     | led                          |                 |                  |             |

| bit 0           | -                              | Fractional Mu                          | -                                 |                              |                 |                  |             |

|                 | 1 = Integer m                  | node enabled for                       | or DSP multiply<br>d for DSP mult |                              |                 |                  |             |

**Note 1:** This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

# TABLE 4-16: DMA REGISTER MAP

| File Name | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3       | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|------|-----------|-----------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-------------|-------|-------|--------|---------------|

| DMA0CON   | 0380 | CHEN      | SIZE      | DIR    | HALF   | NULLW  |        | _     | —     | _        |       | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA0REQ   | 0382 | FORCE     | _         |        |        | _      |        |       | —     |          |       |       | I      | IRQSEL<6:0> | >     |       |        | 0000          |

| DMA0STA   | 0384 |           |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0STB   | 0386 |           |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0PAD   | 0388 |           |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0CNT   | 038A | _         | _         |        |        | _      |        |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA1CON   | 038C | CHEN      | SIZE      | DIR    | HALF   | NULLW  |        |       | —     |          |       | AMOD  | E<1:0> | —           |       | MODE  | =<1:0> | 0000          |

| DMA1REQ   | 038E | FORCE     | _         |        |        | _      |        |       | —     |          |       |       | I      | IRQSEL<6:0> | >     |       |        | 0000          |

| DMA1STA   | 0390 |           |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA1STB   | 0392 |           | STB<15:0> |        |        |        |        |       |       | 0000     |       |       |        |             |       |       |        |               |

| DMA1PAD   | 0394 |           |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA1CNT   | 0396 | _         | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA2CON   | 0398 | CHEN      | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA2REQ   | 039A | FORCE     | _         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA2STA   | 039C |           | STA<15:0> |        |        |        |        |       |       | 0000     |       |       |        |             |       |       |        |               |

| DMA2STB   | 039E |           | STB<15:0> |        |        |        |        |       |       | 0000     |       |       |        |             |       |       |        |               |

| DMA2PAD   | 03A0 | PAD<15:0> |           |        |        |        |        |       | 0000  |          |       |       |        |             |       |       |        |               |

| DMA2CNT   | 03A2 | _         | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA3CON   | 03A4 | CHEN      | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | _           | _     | MODE  | <1:0>  | 0000          |

| DMA3REQ   | 03A6 | FORCE     | Ι         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA3STA   | 03A8 |           |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3STB   | 03AA |           |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3PAD   | 03AC |           |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3CNT   | 03AE | _         | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA4CON   | 03B0 | CHEN      | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA4REQ   | 03B2 | FORCE     | Ι         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA4STA   | 03B4 |           |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4STB   | 03B6 |           |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4PAD   | 03B8 |           |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4CNT   | 03BA | _         | _         | _      | _      | _      | _      |       |       |          |       | CN    | [<9:0> |             |       |       |        | 0000          |

| DMA5CON   | 03BC | CHEN      | SIZE      | DIR    | HALF   | NULLW  | _      | —     | _     | —        | —     | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA5REQ   | 03BE | FORCE     | _         | —      | _      |        | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA5STA   | 03C0 | ľ         |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA5STB   | 03C2 |           |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-16: DMA REGISTER MAP (CONTINUED)

|           |      |        |              |           | (0011  |        | /         |            |        |           |        |        |        |           |        |        |        |               |

|-----------|------|--------|--------------|-----------|--------|--------|-----------|------------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14       | Bit 13    | Bit 12 | Bit 11 | Bit 10    | Bit 9      | Bit 8  | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| DMA5PAD   | 03C4 |        |              | PAD<15:0> |        |        |           |            |        |           | 0000   |        |        |           |        |        |        |               |

| DMA5CNT   | 03C6 | _      | _            | _         |        | _      | _         | — CNT<9:0> |        |           |        |        |        | 0000      |        |        |        |               |

| DMA6CON   | 03C8 | CHEN   | SIZE         | DIR       | HALF   | NULLW  | —         | _          | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA6REQ   | 03CA | FORCE  | _            | _         |        | _      | —         | _          | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA6STA   | 03CC |        | STA<15:0> 00 |           |        |        |           |            |        | 0000      |        |        |        |           |        |        |        |               |

| DMA6STB   | 03CE |        | STB<15:0>    |           |        |        |           |            | 0000   |           |        |        |        |           |        |        |        |               |

| DMA6PAD   | 03D0 |        |              |           |        |        | PAD<15:0> |            |        |           |        |        | 0000   |           |        |        |        |               |

| DMA6CNT   | 03D2 | _      | _            | _         |        | _      | —         |            |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN   | SIZE         | DIR       | HALF   | NULLW  | —         | _          | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE  | _            | _         |        | _      | —         | _          | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |        |              |           |        |        |           |            | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |        |              |           |        |        |           |            | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |        |              |           |        |        |           |            | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | _      | _            | _         |        | _      | —         |            |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7 | PWCOL6       | PWCOL5    | PWCOL4 | PWCOL3 | PWCOL2    | PWCOL1     | PWCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 |        | _            |           | —      |        | LSTCH     | 1<3:0>     |        | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000          |

| DSADR     | 03E4 |        |              |           |        |        |           |            | DS     | ADR<15:0> |        |        |        |           |        |        |        | 0000          |

|           |      |        |              |           |        |        |           |            |        |           |        |        |        |           |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

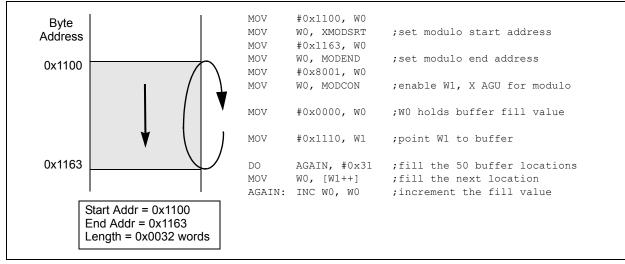

# 4.6 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0

POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### FIGURE 7-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 INTERRUPT VECTOR TABLE

|                                   |                                      | -               |                                                        |

|-----------------------------------|--------------------------------------|-----------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction             | 0x000000        |                                                        |

|                                   | Reset – GOTO Address                 | 0x000002        |                                                        |

|                                   | Reserved                             | 0x000004        |                                                        |

|                                   | Oscillator Fail Trap Vector          |                 |                                                        |

|                                   | Address Error Trap Vector            | _               |                                                        |

|                                   | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000014        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | Interrupt Vector 52                  | 0x00007C        | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53                  | 0x00007E        |                                                        |

| ity                               | Interrupt Vector 54                  | 0x000080        |                                                        |

| Decreasing Natural Order Priority | ~                                    | 7               |                                                        |

| Ē.                                | ~                                    |                 |                                                        |

| de                                | ~                                    |                 |                                                        |

| ō                                 | Interrupt Vector 116                 | 0x0000FC        |                                                        |

| a                                 | Interrupt Vector 117                 | 0x0000FE        |                                                        |

| atu                               | Reserved                             | 0x000100        |                                                        |

| Ž                                 | Reserved                             | 0x000102        |                                                        |

| ing                               | Reserved                             |                 |                                                        |

| eas                               | Oscillator Fail Trap Vector          |                 |                                                        |

| SC                                | Address Error Trap Vector            |                 |                                                        |

| ĕ                                 | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 | 7                                                      |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000114        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 1               |                                                        |

|                                   | ~                                    |                 | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                  | 0x00017C        |                                                        |

|                                   | Interrupt Vector 53                  | 0x00017E        |                                                        |

|                                   | Interrupt Vector 54                  | 0x000180        |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 7               |                                                        |

|                                   | ~                                    | ]               |                                                        |

|                                   | Interrupt Vector 116                 | ]               |                                                        |

| Ļ                                 | Interrupt Vector 117                 | 0x0001FE        |                                                        |

| V                                 | Start of Code                        | 0x000200        |                                                        |

|                                   |                                      | _               |                                                        |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

| Note 1: Se                        | ee Table 7-1 for the list of impleme | ented interrupt | vectors.                                               |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

| U-0                    | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0          | U-0              | R/W-1            | R/W-0            | R/W-0   |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|------------------|------------------|------------------|---------|--|--|--|--|

| _                      |                                                                                                                                         | T4IP<2:0>                               |                | —                |                  | OC4IP<2:0>       |         |  |  |  |  |

| bit 15                 |                                                                                                                                         |                                         |                |                  |                  |                  | bit     |  |  |  |  |

| U-0                    | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0          | U-0              | R/W-1            | R/W-0            | R/W-0   |  |  |  |  |

|                        | N/W-1                                                                                                                                   | OC3IP<2:0>                              | N/W-0          |                  | N/W-1            | DMA2IP<2:0>      | N/ VV-U |  |  |  |  |

| bit 7                  |                                                                                                                                         |                                         |                |                  |                  |                  | bit (   |  |  |  |  |

| Logondi                |                                                                                                                                         |                                         |                |                  |                  |                  |         |  |  |  |  |

| Legend:<br>R = Readabl | le bit                                                                                                                                  | W = Writable t                          | oit            | U = Unimple      | mented bit, rea  | ad as '0'        |         |  |  |  |  |

| -n = Value at          |                                                                                                                                         | '1' = Bit is set                        |                | '0' = Bit is cle |                  | x = Bit is unkno | own     |  |  |  |  |

|                        |                                                                                                                                         |                                         |                |                  |                  |                  |         |  |  |  |  |

| bit 15                 | Unimpleme                                                                                                                               | ented: Read as '0                       | )'             |                  |                  |                  |         |  |  |  |  |

| bit 14-12              | T4IP<2:0>:                                                                                                                              | Timer4 Interrupt                        | Priority bits  |                  |                  |                  |         |  |  |  |  |

|                        | 111 = Interr                                                                                                                            | upt is priority 7 (h                    | nighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | 001 = Interr                                                                                                                            | upt is priority 1                       |                |                  |                  |                  |         |  |  |  |  |

|                        | 000 <b>= Interr</b>                                                                                                                     | upt source is disa                      | abled          |                  |                  |                  |         |  |  |  |  |

| bit 11                 | Unimpleme                                                                                                                               | ented: Read as '0                       | )'             |                  |                  |                  |         |  |  |  |  |

| bit 10-8               | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits                                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | 111 = Interr                                                                                                                            | rupt is priority 7 (h                   | nighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        |                                                                                                                                         | upt is priority 1                       |                |                  |                  |                  |         |  |  |  |  |

| L:1 7                  |                                                                                                                                         | upt source is disa                      |                |                  |                  |                  |         |  |  |  |  |

| bit 7                  | -                                                                                                                                       | ented: Read as '0                       |                |                  |                  |                  |         |  |  |  |  |

| bit 6-4                | <b>OC3IP&lt;2:0&gt;:</b> Output Compare Channel 3 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       | upt is phonity 7 (i                     | lighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        |                                                                                                                                         | upt is priority 1<br>upt source is disa | abled          |                  |                  |                  |         |  |  |  |  |

| bit 3                  |                                                                                                                                         | ented: Read as '0                       |                |                  |                  |                  |         |  |  |  |  |

| bit 2-0                | -                                                                                                                                       | 0>: DMA Channe                          |                | unsfer Complete  | e Interrupt Prio | ritv bits        |         |  |  |  |  |

|                        |                                                                                                                                         | rupt is priority 7 (h                   |                |                  |                  | ,                |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •                                                                                                                                       |                                         |                |                  |                  |                  |         |  |  |  |  |

|                        | •<br>001 = Interr                                                                                                                       | upt is priority 1                       |                |                  |                  |                  |         |  |  |  |  |

|                        |                                                                                                                                         | upt source is disa                      |                |                  |                  |                  |         |  |  |  |  |

#### DECISTED 7-21. IDCA- INTERDURT DRIOPITY CONTROL DECISTER A

| U-0         | U-0                                                                                              | U-0                                                                                                    | U-0             | R-1               | R-1              | R-1             | R-1   |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _           | _                                                                                                | _                                                                                                      | _               |                   | LSTC             | H<3:0>          |       |  |  |  |  |  |

| oit 15      | ·                                                                                                |                                                                                                        |                 |                   |                  |                 | bit   |  |  |  |  |  |

|             |                                                                                                  |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| R-0         | R-0                                                                                              | R-0                                                                                                    | R-0             | R-0               | R-0              | R-0             | R-0   |  |  |  |  |  |

| PPST7       | PPST6                                                                                            | PPST5                                                                                                  | PPST4           | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |  |

| pit 7       |                                                                                                  |                                                                                                        |                 |                   |                  |                 | bit   |  |  |  |  |  |

| _egend:     |                                                                                                  |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| R = Readab  | le bit                                                                                           | W = Writable                                                                                           | bit             | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |  |

| n = Value a | t POR                                                                                            | '1' = Bit is se                                                                                        | t               | '0' = Bit is clea |                  | x = Bit is unki | nown  |  |  |  |  |  |

|             |                                                                                                  |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| bit 15-12   | Unimplemen                                                                                       |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 11-8    |                                                                                                  |                                                                                                        | nannel Active I |                   |                  |                 |       |  |  |  |  |  |

|             | 1111 = No DI<br>1110-1000 =                                                                      |                                                                                                        | as occurred sir | ice system Res    | et               |                 |       |  |  |  |  |  |

|             |                                                                                                  |                                                                                                        | as by DMA Cl    | nannel 7          |                  |                 |       |  |  |  |  |  |

|             | 0111 = Last data transfer was by DMA Channel 7<br>0110 = Last data transfer was by DMA Channel 6 |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0101 = Last data transfer was by DMA Channel 5                                                   |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0100 = Last data transfer was by DMA Channel 4                                                   |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0011 = Last data transfer was by DMA Channel 3<br>0010 = Last data transfer was by DMA Channel 2 |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0010 = Last data transfer was by DMA Channel 2<br>0001 = Last data transfer was by DMA Channel 1 |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0000 = Last data transfer was by DMA Channel 0                                                   |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 7       |                                                                                                  |                                                                                                        | -               |                   |                  |                 |       |  |  |  |  |  |

|             |                                                                                                  | <b>PPST7:</b> Channel 7 Ping-Pong Mode Status Flag bit<br>1 = DMA7STB register selected                |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0 = DMA7STA                                                                                      | •                                                                                                      |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 6       | PPST6: Chan                                                                                      | ST6: Channel 6 Ping-Pong Mode Status Flag bit                                                          |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 1 = DMA6STE<br>0 = DMA6STA                                                                       | U U                                                                                                    |                 |                   |                  |                 |       |  |  |  |  |  |

| bit 5       | PPST5: Chan                                                                                      | inel 5 Ping-Po                                                                                         | ng Mode Statu   | is Flag bit       |                  |                 |       |  |  |  |  |  |

|             |                                                                                                  | PPST5: Channel 5 Ping-Pong Mode Status Flag bit<br>1 = DMA5STB register selected                       |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0 = DMA5STA                                                                                      |                                                                                                        |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 4       | PPST4: Chan                                                                                      | inel 4 Ping-Po                                                                                         | ng Mode Statu   | ıs Flag bit       |                  |                 |       |  |  |  |  |  |

|             | 1 = DMA4STE                                                                                      | •                                                                                                      |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 0 = DMA4STA                                                                                      | -                                                                                                      |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 3       |                                                                                                  | -                                                                                                      | ng Mode Statu   | is Flag bit       |                  |                 |       |  |  |  |  |  |

|             |                                                                                                  | 1 = DMA3STB register selected                                                                          |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 2       |                                                                                                  | <ul> <li>DMA3STA register selected</li> <li>PPST2: Channel 2 Ping-Pong Mode Status Flag bit</li> </ul> |                 |                   |                  |                 |       |  |  |  |  |  |

|             |                                                                                                  | -                                                                                                      | -               | is Flag bit       |                  |                 |       |  |  |  |  |  |

|             | 1 = DMA2STE<br>0 = DMA2STA                                                                       | •                                                                                                      |                 |                   |                  |                 |       |  |  |  |  |  |

| oit 1       |                                                                                                  | ST1: Channel 1 Ping-Pong Mode Status Flag bit                                                          |                 |                   |                  |                 |       |  |  |  |  |  |

|             | 1 = DMA1STE                                                                                      | -                                                                                                      | -               | ie i i i g i i i  |                  |                 |       |  |  |  |  |  |

|             | 0 = DMA1STA                                                                                      | -                                                                                                      |                 |                   |                  |                 |       |  |  |  |  |  |

| bit 0       | PPST0: Chan                                                                                      | -                                                                                                      |                 | e Elaa bit        |                  |                 |       |  |  |  |  |  |

|             |                                                                                                  |                                                                                                        | ng moue olait   | IS Flay DIL       |                  |                 |       |  |  |  |  |  |

| JILU        | 1 = DMA0STE                                                                                      | -                                                                                                      | -               | is Flag bit       |                  |                 |       |  |  |  |  |  |

| TABLE 9-1. CONFIGURATION                         | BIT VALUES FOR C  |             | ·          |             |

|--------------------------------------------------|-------------------|-------------|------------|-------------|

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | XX          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | XX          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1           |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary         | XX          | 100        | 1           |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -           |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -           |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1           |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _           |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | -           |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1           |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | XX          | 001        | 1           |

| Fast RC Oscillator (FRC)                         | Internal          | XX          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources related to the Oscillator are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

#### 9.2.1 KEY RESOURCES

- Section 39. "Oscillator (Part III)" (DS70216)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0          | U-0                                         | U-0                               | R/W-1           | R/W-1                                | R/W-1           | R/W-1     | R/W-1 |  |  |

|--------------|---------------------------------------------|-----------------------------------|-----------------|--------------------------------------|-----------------|-----------|-------|--|--|

| —            | _                                           | _                                 |                 |                                      | CSCKR<4:0       | >         |       |  |  |

| pit 15       |                                             |                                   |                 |                                      |                 |           | bit 8 |  |  |

| U-0          | U-0                                         | U-0                               | R/W-1           | R/W-1                                | R/W-1           | R/W-1     | R/W-1 |  |  |

| _            | — — — CSDIR<4:0>                            |                                   |                 |                                      |                 |           |       |  |  |

| oit 7        |                                             |                                   |                 |                                      |                 |           | bit ( |  |  |

|              |                                             |                                   |                 |                                      |                 |           |       |  |  |

| Legend:      |                                             |                                   |                 |                                      |                 |           |       |  |  |

| R = Readab   | le bit                                      | W = Writable I                    | oit             | U = Unimplen                         | nented bit, rea | d as '0'  |       |  |  |

| -n = Value a | n = Value at POR '1' = Bit is set           |                                   |                 | '0' = Bit is cleared x = Bit is unki |                 |           |       |  |  |

|              | 11001 = Inpu<br>•<br>•<br>•<br>00001 = Inpu | ut tied to RP25<br>ut tied to RP1 |                 |                                      |                 |           |       |  |  |

|              | •                                           | ut tied to RP0                    |                 |                                      |                 |           |       |  |  |

| bit 4-0      | CSDIR<4:0><br>11111 = Inpu<br>11001 = Inpu  |                                   | erial Data Inpu | ut (CSDI) to the                     | e correspondin  | g RPn pin |       |  |  |

# REGISTER 11-14: RPINR24: PERIPHERAL PIN SELECT INPUT REGISTER 24

| R/W-0              | U-0                                                                      | R/W-0                              | U-0                  | U-0                            | U-0             | U-0                | U-0 |  |  |  |  |

|--------------------|--------------------------------------------------------------------------|------------------------------------|----------------------|--------------------------------|-----------------|--------------------|-----|--|--|--|--|

| TON <sup>(2)</sup> | _                                                                        | TSIDL <sup>(1)</sup>               | _                    |                                | _               | _                  | _   |  |  |  |  |

| bit 15             |                                                                          |                                    |                      |                                |                 |                    | bit |  |  |  |  |

| U-0                | R/W-0                                                                    | R/W-0                              | R/W-0                | U-0                            | U-0             | R/W-0              | U-0 |  |  |  |  |

|                    | TGATE <sup>(2)</sup>                                                     | TCKPS                              | <1:0> <sup>(2)</sup> | —                              |                 | TCS <sup>(2)</sup> |     |  |  |  |  |

| bit 7              |                                                                          |                                    |                      |                                |                 |                    | bit |  |  |  |  |

| Legend:            |                                                                          |                                    |                      |                                |                 |                    |     |  |  |  |  |

| R = Readab         | ole bit                                                                  | W = Writable I                     | bit                  | U = Unimplen                   | nented bit, rea | d as '0'           |     |  |  |  |  |

| -n = Value a       | it POR                                                                   | '1' = Bit is set                   |                      | '0' = Bit is clea              | ared            | x = Bit is unkno   | own |  |  |  |  |

|                    |                                                                          | o (2)                              |                      |                                |                 |                    |     |  |  |  |  |

| bit 15             | TON: Timery                                                              |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    | 1 = Starts 16-bit Timerx<br>0 = Stops 16-bit Timerx                      |                                    |                      |                                |                 |                    |     |  |  |  |  |

| bit 14             | •                                                                        | Unimplemented: Read as '0'         |                      |                                |                 |                    |     |  |  |  |  |

| bit 13             | TSIDL: Stop i                                                            | n Idle Mode bit                    | (1)                  |                                |                 |                    |     |  |  |  |  |

|                    |                                                                          | ue timer operat<br>timer operation |                      | vice enters Idle i<br>e        | mode            |                    |     |  |  |  |  |

| bit 12-7           | Unimplemen                                                               | ted: Read as '                     | )'                   |                                |                 |                    |     |  |  |  |  |

| bit 6              | <b>TGATE:</b> Timerx Gated Time Accumulation Enable bit <sup>(2)</sup>   |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    | When TCS = 1:                                                            |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    | This bit is ignored.                                                     |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    | $\frac{\text{When TCS} = 0}{1 = \text{Gated time accumulation enabled}}$ |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    |                                                                          | e accumulation                     |                      |                                |                 |                    |     |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                                                               | : Timerx Input                     | Clock Presca         | ale Select bits <sup>(2)</sup> |                 |                    |     |  |  |  |  |

|                    |                                                                          | 11 = 1:256 prescale value          |                      |                                |                 |                    |     |  |  |  |  |

|                    | 10 = 1:64 pre                                                            |                                    |                      |                                |                 |                    |     |  |  |  |  |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres                                           |                                    |                      |                                |                 |                    |     |  |  |  |  |

| bit 3-2            | •                                                                        | ted: Read as '(                    | )'                   |                                |                 |                    |     |  |  |  |  |

| bit 1              | •                                                                        | Clock Source S                     |                      |                                |                 |                    |     |  |  |  |  |

|                    | 1 = External o                                                           | clock from TxCl                    | < pin                |                                |                 |                    |     |  |  |  |  |

|                    | 0 = Internal cl                                                          | lock (Fosc/2)                      |                      |                                |                 |                    |     |  |  |  |  |

| bit 0              | Unimplemen                                                               | tod: Dood on '                     | ·'                   |                                |                 |                    |     |  |  |  |  |

# REGISTER 13-2: TxCON: TIMER CONTROL REGISTER (x = 3 OR 5)

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), these bits have no effect.

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                                      |

|       | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                     |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

# 18.3 UART Control Registers

# REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN   | <1:0> |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|-------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7    |        |          |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | UARTEN: UARTx Enable bit <sup>(1)</sup>                                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN<1:0>                                                                                              |

|         | <ul> <li>UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption<br/>minimal</li> </ul>                                                        |