#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp802-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

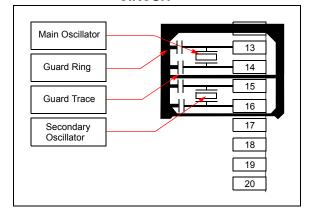

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3. Recommendations for crystals and ceramic resonators are provided in Table 2-1 and Table 2-2, respectively.

# FIGURE 2-3:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Part<br>Number         | Vendor   | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|------------------------|----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| ECS-40-20-4DN          | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-80-18-4DN          | ECS Inc. | 8 MHz  | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-100-18-4-DN        | ECS Inc. | 10 MHz | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-200-20-4DN         | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-40-20-5G3XDS-TR    | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-80-20-5G3XDS-TR    | ECS Inc. | 8 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-100-20-5G3XDS-TR   | ECS Inc. | 10 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-200-20-5G3XDS-TR   | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to 125°C           |

| NX3225SA 20MHZ AT-W    | NDK      | 20 MHz | 8 pF         | 3.2 mm x 2.5 mm | ±50 ppm                | SM               | -40°C to 125°C           |

| Legend: TH = Through I | Hole     | SM     | = Surface I  | Nount           |                        |                  |                          |

### TABLE 2-1: CRYSTAL RECOMMENDATIONS

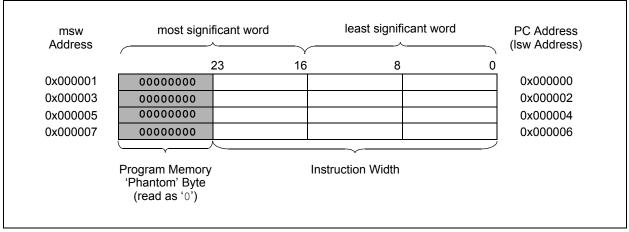

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| R/W-0                   | R/W-0                              | U-0                              | U-0             | U-0                      | U-0              | U-0             | U-0   |

|-------------------------|------------------------------------|----------------------------------|-----------------|--------------------------|------------------|-----------------|-------|

| DAC1LIE <sup>(2)</sup>  | DAC1RIE <sup>(2)</sup>             | _                                | —               | —                        | —                | —               |       |

| bit 15                  |                                    |                                  |                 |                          |                  |                 | bit   |

|                         |                                    |                                  |                 |                          |                  |                 |       |

| U-0                     | R/W-0                              | R/W-0                            | R/W-0           | R/W-0                    | R/W-0            | R/W-0           | U-0   |

| —                       | C1TXIE <sup>(1)</sup>              | DMA7IE                           | DMA6IE          | CRCIE                    | U2EIE            | U1EIE           | —     |

| bit 7                   |                                    |                                  |                 |                          |                  |                 | bit   |

| Lowandi                 |                                    |                                  |                 |                          |                  |                 |       |

| Legend:<br>R = Readable | , hit                              | \\/ = \\/ritabla                 | hit             | II – Unimplor            | monted hit read  |                 |       |

| -n = Value at           |                                    | W = Writable<br>'1' = Bit is set |                 | '0' = Bit is cle         | mented bit, read | x = Bit is unkn | 0.000 |

|                         | FUR                                |                                  | L               |                          | aleu             |                 |       |

| bit 15                  | DAC1LIE: DA                        | C Left Channe                    | el Interrupt En | able bit <sup>(2)</sup>  |                  |                 |       |

|                         | 1 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 14                  | DAC1RIE: DA                        |                                  |                 | nable bit <sup>(2)</sup> |                  |                 |       |

|                         | 1 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 13-7                | 0 = Interrupt r<br>Unimplement     | •                                |                 |                          |                  |                 |       |

| bit 6                   | •                                  |                                  |                 | nterrupt Enable          | o hit(1)         |                 |       |

|                         | 1 = Interrupt r                    |                                  | •               | nterrupt Enable          |                  |                 |       |

|                         |                                    | equest not occ                   |                 |                          |                  |                 |       |

| bit 5                   | DMA7IE: DM                         | A Channel 7 D                    | ata Transfer C  | Complete Interr          | upt Enable bit   |                 |       |

|                         |                                    | equest enable                    |                 |                          |                  |                 |       |

|                         | -                                  | equest not en                    |                 |                          |                  |                 |       |

| bit 4                   |                                    |                                  |                 | Complete Interr          | upt Enable bit   |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

| bit 3                   | CRCIE: CRC                         | •                                |                 | oit                      |                  |                 |       |

| DIL 3                   | 1 = Interrupt r                    |                                  | •               | JIL                      |                  |                 |       |

|                         | 0 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

| bit 2                   | U2EIE: UART                        | 2 Error Interru                  | pt Enable bit   |                          |                  |                 |       |

|                         | 1 = Interrupt r                    | equest enable                    | d               |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | equest not en                    | abled           |                          |                  |                 |       |

| bit 1                   | U1EIE: UART                        |                                  | -               |                          |                  |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

|                         |                                    |                                  |                 |                          |                  |                 |       |

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

2: Interrupts are disabled on devices without Audio DAC modules.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0 | U-0              | U-0                          |                  |                  |                                              |                                                                                                   |

|-----|------------------|------------------------------|------------------|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|

|     |                  | 0-0                          | U-0              | U-0              | U-0                                          | U-0                                                                                               |

|     | —                | _                            |                  | —                | —                                            | —                                                                                                 |

|     |                  |                              |                  |                  |                                              | bit 8                                                                                             |

|     |                  |                              |                  |                  |                                              |                                                                                                   |

| U-0 | U-0              | U-0                          | U-0              | R/W-1            | R/W-0                                        | R/W-0                                                                                             |

|     | —                | _                            | _                |                  | DMA3IP<2:0>                                  |                                                                                                   |

|     |                  |                              |                  |                  |                                              | bit 0                                                                                             |

|     |                  |                              |                  |                  |                                              |                                                                                                   |

|     |                  |                              |                  |                  |                                              |                                                                                                   |

| t   | W = Writable I   | oit                          | U = Unimpler     | nented bit, read | as '0'                                       |                                                                                                   |

| R   | '1' = Bit is set |                              | '0' = Bit is cle | ared             | x = Bit is unkr                              | iown                                                                                              |

|     |                  | — — — — — t — W = Writable I | w = Writable bit |                  | W = Writable bit U = Unimplemented bit, read | —     —     —     DMA3IP<2:0>       t     W = Writable bit     U = Unimplemented bit, read as '0' |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 DMA3IP<2:0>: DMA Channel 3 Data Transfer Complete Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

| U-0              | U-0                            | U-0                                   | U-0             | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |

|------------------|--------------------------------|---------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|

| _                | _                              | —                                     | _               | —                 |                  | DMA4IP<2:0>     |       |  |  |

| bit 15           |                                |                                       |                 |                   |                  |                 | bit 8 |  |  |

|                  |                                | <b>D</b> 444 0                        |                 |                   |                  |                 |       |  |  |

| U-0              | R/W-1                          | R/W-0                                 | R/W-0           | U-0               | U-0              | U-0             | U-0   |  |  |

|                  |                                | PMPIP<2:0>                            |                 | —                 |                  |                 | —     |  |  |

| bit 7            |                                |                                       |                 |                   |                  |                 | bit C |  |  |

| Legend:          |                                |                                       |                 |                   |                  |                 |       |  |  |

| R = Readab       | le bit                         | W = Writable                          | bit             | U = Unimplen      | nented bit, read | 1 as '0'        |       |  |  |

| -n = Value a     | t POR                          | '1' = Bit is set                      |                 | '0' = Bit is clea |                  | x = Bit is unkr | own   |  |  |

|                  |                                |                                       |                 |                   |                  |                 |       |  |  |

| bit 15-11        | Unimpleme                      | ented: Read as '                      | 0'              |                   |                  |                 |       |  |  |

| bit 10-8         | DMA4IP<2:                      | 0>: DMA Chann                         | el 4 Data Tra   | nsfer Complete    | Interrupt Priori | ty bits         |       |  |  |

|                  | 111 = Interr                   | upt is priority 7 (                   | highest priori  | ty interrupt)     |                  |                 |       |  |  |

|                  | •                              |                                       |                 |                   |                  |                 |       |  |  |

|                  | •                              |                                       |                 |                   |                  |                 |       |  |  |

|                  | 001 = Interr                   | upt is priority 1                     |                 |                   |                  |                 |       |  |  |

|                  |                                | upt source is dis                     | abled           |                   |                  |                 |       |  |  |

|                  |                                |                                       |                 |                   |                  |                 |       |  |  |

| bit 7            | Unimpleme                      | ented: Read as '                      | 0'              |                   |                  |                 |       |  |  |

|                  | •                              | ented: Read as '<br>>: Parallel Maste |                 | pt Priority bits  |                  |                 |       |  |  |

|                  | PMPIP<2:0                      |                                       | er Port Interru |                   |                  |                 |       |  |  |

|                  | PMPIP<2:0                      | >: Parallel Maste                     | er Port Interru |                   |                  |                 |       |  |  |

|                  | PMPIP<2:0                      | >: Parallel Maste                     | er Port Interru |                   |                  |                 |       |  |  |

| bit 7<br>bit 6-4 | PMPIP<2:0<br>111 = Interr<br>• | >: Parallel Maste                     | er Port Interru |                   |                  |                 |       |  |  |

#

bit 3-0 Unimplemented: Read as '0'

| REGISTER     | R 9-3: PLLFE | BD: PLL FEE      | DBACK DIV       | ISOR REGIS           | STER "           |                    |           |

|--------------|--------------|------------------|-----------------|----------------------|------------------|--------------------|-----------|

| U-0          | U-0          | U-0              | U-0             | U-0                  | U-0              | U-0                | R/W-0     |

|              | —            | _                | _               | _                    | —                | _                  | PLLDIV<8> |

| bit 15       |              |                  |                 |                      |                  |                    | bit 8     |

| R/W-0        | D/M/ O       |                  |                 | R/W-0                | R/W-0            | R/W-0              |           |

| R/W-U        | R/W-0        | R/W-1            | R/W-1           |                      | R/W-U            | R/W-U              | R/W-0     |

|              |              |                  | PLLD            | IV<7:0>              |                  |                    |           |

| bit 7        |              |                  |                 |                      |                  |                    | bit C     |

|              |              |                  |                 |                      |                  |                    |           |

| Legend:      |              |                  |                 |                      |                  |                    |           |

| R = Readab   | ole bit      | W = Writable     | bit             | U = Unimpler         | mented bit, read | l as '0'           |           |

| -n = Value a | at POR       | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |           |

|              |              |                  |                 |                      |                  |                    |           |

| bit 15-9     | Unimplemen   | ted: Read as '   | 0'              |                      |                  |                    |           |

| bit 8-0      | PLLDIV<8:0>  | >: PLL Feedba    | ck Divisor bits | (also denoted        | as 'M', PLL mu   | ltiplier)          |           |

|              | 111111111    | = 513            |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | 000110000=   | = 50 (default)   |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | •            |                  |                 |                      |                  |                    |           |

|              | 000000010 =  |                  |                 |                      |                  |                    |           |

#### REGISTER 9-3-PLLEBD PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

00000001 = 3 000000000 = 2

Note 1: This register is reset only on a Power-on Reset (POR).

### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0             | U-0 | U-0              | U-0   | U-0              | U-0              | U-0            | U-0   |

|-----------------|-----|------------------|-------|------------------|------------------|----------------|-------|

| _               | —   | _                | _     | —                | —                | _              | —     |

| bit 15          |     |                  |       |                  |                  |                | bit 8 |

|                 |     |                  |       |                  |                  |                |       |

| U-0             | U-0 | U-0              | R/W-1 | R/W-1            | R/W-1            | R/W-1          | R/W-1 |

| —               | —   | —                |       |                  | OCFAR<4:0>       |                |       |

| bit 7           |     |                  |       |                  |                  |                | bit 0 |

|                 |     |                  |       |                  |                  |                |       |

| Legend:         |     |                  |       |                  |                  |                |       |

| R = Readable    | bit | W = Writable     | bit   | U = Unimplei     | mented bit, read | as '0'         |       |

| -n = Value at F | POR | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unk | nown  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0 NOTES:

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                    |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                              |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.</li> <li>Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as $l^2C$ master)                                                                                                                                                        |

|       | 1 = Enables Receive mode for $l^2C$ . Hardware clear at end of eighth bit of master receive data byte<br>0 = Receive sequence not in progress                                                                            |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                        |

|       | 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence<br>0 = Stop condition not in progress                                                                                   |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                             |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                     |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                             |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                              |

|       | <ul><li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li><li>0 = Start condition not in progress</li></ul>                                                         |

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| R/W-0         | R/W-0                             | R/W-0                                                                                | R/W-0                           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

|---------------|-----------------------------------|--------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------|-----------------|-------|--|

|               | F7BI                              | D<3:0>                                                                               |                                 | F6BP<3:0>         |                  |                 |       |  |

| bit 15        |                                   |                                                                                      |                                 |                   |                  |                 | bit 8 |  |

| R/W-0         | R/W-0                             | R/W-0                                                                                | R/W-0                           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

|               | F5BI                              | ><3:0>                                                                               |                                 |                   | F4BF             | P<3:0>          |       |  |

| bit 7         |                                   |                                                                                      |                                 |                   |                  |                 | bit C |  |

|               |                                   |                                                                                      |                                 |                   |                  |                 |       |  |

| Legend:       |                                   | C = Writable                                                                         | bit, but only '0                | ' can be written  | to clear the bi  | t               |       |  |

| R = Readabl   | le bit                            | W = Writable                                                                         | bit                             | U = Unimplen      | nented bit, read | d as '0'        |       |  |

| -n = Value at | t POR                             | '1' = Bit is set                                                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>• | : RX Buffer mas<br>er hits received ir<br>er hits received ir<br>er hits received ir | n RX FIFO buf<br>n RX Buffer 14 |                   |                  |                 |       |  |

|               | 0001                              | er hits received in                                                                  |                                 |                   |                  |                 |       |  |

| bit 11-8      | F6BP<3:0>                         | : RX Buffer mas                                                                      | k for Filter 6 (s               | ame values as     | bit 15-12)       |                 |       |  |

| bit 7-4       | F5BP<3:0>                         | : RX Buffer mas                                                                      | k for Filter 5 (s               | ame values as     | bit 15-12)       |                 |       |  |

|               |                                   |                                                                                      |                                 |                   |                  |                 |       |  |

#### REGISTER 19-13: CiBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| bit 3-0 | F4BP<3:0>: RX Buffer mask for Filter 4 | (same values as bit 15-12) |

|---------|----------------------------------------|----------------------------|

|         |                                        | ,                          |

#### REGISTER 19-14: CiBUFPNT3: ECAN™ FILTER 8-11 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                                                                                                                         | R/W-0                                                                                          | R/W-0                                                            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|------------------|-----------------|-------|

| -             | F11BF                                                                                                                         | P<3:0>                                                                                         |                                                                  | _                | F10BI            | P<3:0>          | -     |

| bit 15        |                                                                                                                               |                                                                                                |                                                                  | 1                |                  |                 | bit 8 |

| DAMA          | <b>D</b> 444.0                                                                                                                | <b>D</b> 4440                                                                                  | <b>D</b> /// 0                                                   | DAMA             |                  | DAMA            | DAALO |

| R/W-0         | R/W-0                                                                                                                         | R/W-0                                                                                          | R/W-0                                                            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|               | F9BP                                                                                                                          | <3:0>                                                                                          |                                                                  |                  | F8BF             | P<3:0>          |       |

| bit 7         |                                                                                                                               |                                                                                                |                                                                  |                  |                  |                 | bit 0 |

| Legend:       |                                                                                                                               | C = Writable                                                                                   | bit, but only '0                                                 | ' can be written | to clear the bit | t               |       |

| R = Readabl   | e bit                                                                                                                         | W = Writable                                                                                   |                                                                  |                  | nented bit, read |                 |       |

| -n = Value at | POR                                                                                                                           | '1' = Bit is set                                                                               |                                                                  | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | : RX Buffer ma<br>hits received in<br>hits received in<br>hits received in<br>hits received in | n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0 | ffer<br>4        |                  |                 |       |

| bit 11-8      | F10BP<3:0>                                                                                                                    | : RX Buffer ma                                                                                 | sk for Filter 10                                                 | ) (same values   | as bit 15-12)    |                 |       |

| bit 7-4       | F9BP<3:0>:                                                                                                                    | RX Buffer mas                                                                                  | k for Filter 9 (                                                 | same values as   | bit 15-12)       |                 |       |

| bit 3-0       | F8BP<3:0>:                                                                                                                    | RX Buffer mas                                                                                  | k for Filter 8 (                                                 | same values as   | bit 15-12)       |                 |       |

|               |                                                                                                                               |                                                                                                |                                                                  |                  |                  |                 |       |

#### REGISTER 22-3: DAC1DFLT: DAC DEFAULT DATA REGISTER

| R/W-0            | R/W-0<br>bit 8 |

|------------------|----------------|

|                  | bit 8          |

|                  | bit 8          |

|                  |                |

| <b>B</b> 8 4 4 6 |                |

| R/W-0            | R/W-0          |

|                  |                |

|                  | bit 0          |

|                  |                |

|                  |                |

| l as '0'         |                |

| x = Bit is unkr  | nown           |

|                  |                |

bit 15-0 DACDFLT<15:0>: DAC Default Value bits

#### REGISTER 22-4: DAC1LDAT: DAC LEFT DATA REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                                   |       |                  | DACLD                              | AT<15:8>             |       |                    |       |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|                                   |       |                  | DACLI                              | DAT<7:0>             |       |                    |       |

| bit 7                             |       |                  |                                    |                      |       |                    | bit ( |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-0 DACLDAT<15:0>: Left Channel Data Port bits

#### REGISTER 22-5: DAC1RDAT: DAC RIGHT DATA REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | DACRDA | AT<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | DACRD  | AT<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit 0 |

|        |       |       |        |          |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

DACRDAT<15:0>: Right Channel Data Port bits bit 15-0

# 24.3 RTCC Registers

| RTCEN <sup>(2)</sup> | U-0                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R-0                                   | R-0                                    | R/W-0           | R/W-0            | R/W-0         |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------|-----------------|------------------|---------------|--|--|

| IN OLIV              | —                                                                                                                                                                                          | RTCWREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RTCSYNC                               | HALFSEC <sup>(3)</sup>                 | RTCOE           | RTCPT            | R<1:0>        |  |  |

| bit 15               | •                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | · · ·                                  |                 | •<br>            | bit           |  |  |

| R/W-0                | R/W-0                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                 | R/W-0                                  | R/W-0           | R/W-0            | R/W-0         |  |  |

|                      |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CAL                                   | <7:0>                                  |                 |                  |               |  |  |

| bit 7                |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                        |                 |                  | bit           |  |  |

| Legend:              |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                        |                 |                  |               |  |  |

| R = Readable         | bit                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                   | U = Unimpleme                          | ented bit, read | l as '0'         |               |  |  |

| -n = Value at F      | POR                                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       | '0' = Bit is clear                     | red             | x = Bit is unkn  | own           |  |  |

| bit 15               |                                                                                                                                                                                            | C Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                        |                 |                  |               |  |  |