Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

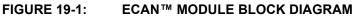

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

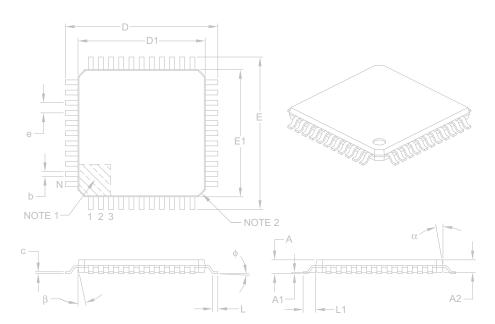

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp802t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 PRODUCT **FAMILIES**

The device names, pin counts, memory sizes, and peripheral availability of each device are listed below. The following pages show their pinout diagrams.

#### TABLE 1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 **CONTROLLER FAMILIES**

|                   |      |                                 |                            |                 |                             | Rem           | appabl                         | e Peri                   | phera | al  |       |                                    |      |                                |               |                                 |                         | r)                                                  |                                               |          |                        |

|-------------------|------|---------------------------------|----------------------------|-----------------|-----------------------------|---------------|--------------------------------|--------------------------|-------|-----|-------|------------------------------------|------|--------------------------------|---------------|---------------------------------|-------------------------|-----------------------------------------------------|-----------------------------------------------|----------|------------------------|

| Device            | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) <sup>(1)</sup> | Remappable Pins | 16-bit Timer <sup>(2)</sup> | Input Capture | Output Compare<br>Standard PWM | Data Converter Interface | UART  | IdS | ECAN™ | External Interrupts <sup>(3)</sup> | RTCC | I <sup>2</sup> C <sup>TM</sup> | CRC Generator | 10-bit/12-bit ADC<br>(Channels) | 16-bit Audio DAC (Pins) | Analog Comparator<br>(2 Channels/Voltage Regulator) | 8-bit Parallel Master<br>Port (Address Lines) | I/O Pins | Packages               |

| dsPIC33FJ128GP804 | 44   | 128                             | 16                         | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 13                              | 6                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128GP802 | 28   | 128                             | 16                         | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 10                              | 4                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ128GP204 | 44   | 128                             | 8                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128GP202 | 28   | 128                             | 8                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64GP804  | 44   | 64                              | 16                         | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 13                              | 6                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64GP802  | 28   | 64                              | 16                         | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 10                              | 4                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64GP204  | 44   | 64                              | 8                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64GP202  | 28   | 64                              | 8                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ32GP304  | 44   | 32                              | 4                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ32GP302  | 28   | 32                              | 4                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

Note RAM size is inclusive of 2 Kbytes of DMA RAM for all devices except dsPIC33FJ32GP302/304, which include 1 Kbyte of DMA RAM. 1:

2: 3: Only four out of five timers are remappable.

Only two out of three interrupts are remappable.

#### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 Digital Signal Controller (DSC) Devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high performance 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### 4.8.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

**Note:** PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop allows the instruction using PSV to access data, to execute in a single cycle.

#### FIGURE 7-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 INTERRUPT VECTOR TABLE

|                                   |                                      | -               |                                                        |

|-----------------------------------|--------------------------------------|-----------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction             | 0x000000        |                                                        |

|                                   | Reset – GOTO Address                 | 0x000002        |                                                        |

|                                   | Reserved                             | 0x000004        |                                                        |

|                                   | Oscillator Fail Trap Vector          |                 |                                                        |

|                                   | Address Error Trap Vector            | _               |                                                        |

|                                   | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000014        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | Interrupt Vector 52                  | 0x00007C        | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53                  | 0x00007E        |                                                        |

| ity                               | Interrupt Vector 54                  | 0x000080        |                                                        |

| Decreasing Natural Order Priority | ~                                    | 7               |                                                        |

| Ē.                                | ~                                    |                 |                                                        |

| de                                | ~                                    |                 |                                                        |

| ō                                 | Interrupt Vector 116                 | 0x0000FC        |                                                        |

| a                                 | Interrupt Vector 117                 | 0x0000FE        |                                                        |

| atu                               | Reserved                             | 0x000100        |                                                        |

| Ž                                 | Reserved                             | 0x000102        |                                                        |

| ing                               | Reserved                             |                 |                                                        |

| eas                               | Oscillator Fail Trap Vector          |                 |                                                        |

| SC                                | Address Error Trap Vector            |                 |                                                        |

| ĕ                                 | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 | 7                                                      |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000114        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 1               |                                                        |

|                                   | ~                                    |                 | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                  | 0x00017C        |                                                        |

|                                   | Interrupt Vector 53                  | 0x00017E        |                                                        |

|                                   | Interrupt Vector 54                  | 0x000180        |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 7               |                                                        |

|                                   | ~                                    | ]               |                                                        |

|                                   | Interrupt Vector 116                 | ]               |                                                        |

| Ļ                                 | Interrupt Vector 117                 | 0x0001FE        |                                                        |

| V                                 | Start of Code                        | 0x000200        |                                                        |

|                                   |                                      | _               |                                                        |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

| Note 1: Se                        | ee Table 7-1 for the list of impleme | ented interrupt | vectors.                                               |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

#### 7.5 CPU Registers

| REGISTER 7-1: | SR: CPU STATUS REGISTER <sup>(1)</sup> |

|---------------|----------------------------------------|

|---------------|----------------------------------------|

|        | 5444.6 | <b>B</b> 8 4 4 6 |       |     |       | 5444 | -     |

|--------|--------|------------------|-------|-----|-------|------|-------|

|        |        |                  |       |     |       |      |       |

| bit 15 |        |                  |       |     |       |      | bit 8 |

| OA     | OB     | SA               | SB    | OAB | SAB   | DA   | DC    |

| R-0    | R-0    | R/C-0            | R/C-0 | R-0 | R/C-0 | R -0 | R/W-0 |

| R/W-0 | R/W-0                     | R/W-0 | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|---------------------------|-------|-----|-------|-------|-------|-------|

|       | IPL<2:0> <sup>(2,3)</sup> |       | RA  | N     | OV    | Z     | С     |

| bit 7 |                           |       |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0               | U-0                                                | U-0              | R/W-0          | R/W-0                | R-0              | R-0     | R-0   |  |  |  |  |

|-------------------|----------------------------------------------------|------------------|----------------|----------------------|------------------|---------|-------|--|--|--|--|

| —                 | —                                                  | —                | US             | EDT                  |                  | DL<2:0> |       |  |  |  |  |

| bit 15            |                                                    |                  |                |                      |                  |         | bit 8 |  |  |  |  |

|                   |                                                    |                  |                |                      |                  |         |       |  |  |  |  |

| R/W-0             | R/W-0                                              | R/W-1            | R/W-0          | R/C-0                | R/W-0            | R/W-0   | R/W-0 |  |  |  |  |

| SATA              | SATB                                               | SATDW            | ACCSAT         | IPL3 <sup>(2)</sup>  | PSV              | RND     | IF    |  |  |  |  |

| bit 7             |                                                    |                  |                |                      |                  |         | bit 0 |  |  |  |  |

| <b></b>           |                                                    |                  |                |                      |                  |         |       |  |  |  |  |

| Legend:           |                                                    | C = Clear only   | y bit          |                      |                  |         |       |  |  |  |  |

| R = Readable      | bit                                                | W = Writable     | bit            | -n = Value at        |                  |         |       |  |  |  |  |

| 0' = Bit is clear | ed                                                 | 'x = Bit is unk  | nown           | U = Unimpler         | mented bit, read | as '0'  |       |  |  |  |  |

|                   |                                                    |                  |                | (2)                  |                  |         |       |  |  |  |  |

| bit 3             | IPL3: CPU In                                       | terrupt Priority | Level Status I | bit 3 <sup>(2)</sup> |                  |         |       |  |  |  |  |

|                   | 1 = CPU interrupt priority level is greater than 7 |                  |                |                      |                  |         |       |  |  |  |  |

0 = CPU interrupt priority level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| U-0                              | R/W-0                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                | U-0                                                                                                                                                         | U-0                 | U-0                   | U-0             | U-0     |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------|---------|--|--|--|--|--|

|                                  | DMA4IE                                                                                                                                                                                                                             | PMPIE                                                                                                                                                                                                                |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| <br>oit 15                       | DIVIAHIL                                                                                                                                                                                                                           |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 | bit     |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 | DIL     |  |  |  |  |  |

| U-0                              | U-0                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                  | R/W-0                                                                                                                                                       | R/W-0               | R/W-0                 | R/W-0           | R/W-0   |  |  |  |  |  |

| _                                |                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                    | DMA3IE                                                                                                                                                      | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE          | SPI2EIE |  |  |  |  |  |

| bit 7                            |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 | bit     |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| Legend:                          |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| R = Readab                       |                                                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                         |                                                                                                                                                             | •                   | nented bit, read      |                 |         |  |  |  |  |  |

| -n = Value a                     | it POR                                                                                                                                                                                                                             | '1' = Bit is se                                                                                                                                                                                                      | t                                                                                                                                                           | '0' = Bit is cle    | ared                  | x = Bit is unkr | nown    |  |  |  |  |  |

| L:4 / F                          |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| bit 15                           | -                                                                                                                                                                                                                                  | ited: Read as                                                                                                                                                                                                        |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| bit 14                           | DMA4IE: DMA Channel 4 Data Transfer Complete Interrupt Enable bit                                                                                                                                                                  |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    | <ol> <li>I = Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>                                                                                                                             |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

|                                  | •                                                                                                                                                                                                                                  | •                                                                                                                                                                                                                    |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| bit 13                           | PMPIE: Parallel Master Port Interrupt Enable bit                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    | request enable                                                                                                                                                                                                       |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    | request not en                                                                                                                                                                                                       | abled                                                                                                                                                       |                     |                       |                 |         |  |  |  |  |  |

|                                  | Unimplemented: Read as '0'                                                                                                                                                                                                         |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                 |         |  |  |  |  |  |

| bit 12-5                         | Unimplemen                                                                                                                                                                                                                         | ted: Read as                                                                                                                                                                                                         | ʻ0 <b>'</b>                                                                                                                                                 |                     |                       |                 |         |  |  |  |  |  |

| bit 12-5<br>bit 4                | •                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      | '0'<br>Data Transfer C                                                                                                                                      | complete Interr     | upt Enable bit        |                 |         |  |  |  |  |  |

|                                  | DMA3IE: DM                                                                                                                                                                                                                         |                                                                                                                                                                                                                      | ata Transfer C                                                                                                                                              | complete Interr     | upt Enable bit        |                 |         |  |  |  |  |  |

|                                  | <b>DMA3IE:</b> DM<br>1 = Interrupt                                                                                                                                                                                                 | IA Channel 3 E                                                                                                                                                                                                       | oata Transfer C<br>d                                                                                                                                        | Complete Interr     | upt Enable bit        |                 |         |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt                                                                                                                                                                                | IA Channel 3 E<br>request enable<br>request has er                                                                                                                                                                   | oata Transfer C<br>d                                                                                                                                        |                     | upt Enable bit        |                 |         |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN                                                                                                                                                           | IA Channel 3 E<br>request enable<br>request has er                                                                                                                                                                   | Data Transfer C<br>ed<br>habled<br>pt Enable bit <sup>(1)</sup>                                                                                             |                     | rupt Enable bit       |                 |         |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN<br>1 = Interrupt                                                                                                                                          | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru                                                                                                                                                | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed                                                                                       |                     | rupt Enable bit       |                 |         |  |  |  |  |  |

|                                  | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN<br>1 = Interrupt<br>0 = Interrupt                                                                                                                         | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en                                                                                                            | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed                                                                                       | )                   |                       |                 |         |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA                                                                                                                        | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en                                                                                                            | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte                                                           | )                   |                       |                 |         |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA<br>1 = Interrupt                                                                                                       | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E                                                                                           | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte                                                           | )                   |                       |                 |         |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt                                                                   | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable                                                                         | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled                                            | )                   |                       |                 |         |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: EC/<br>1 = Interrupt<br>0 = Interrupt<br>SPI2IE: SPI2                                                                      | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en                                                       | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>bit Enable bit                          | )                   |                       |                 |         |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: EC/<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en                                                       | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>ot Enable bit<br>ed                     | )                   |                       |                 |         |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2<br>bit 1 | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt                  | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en<br>2 Event Interrup<br>request enable                 | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>ot Enable bit<br>ed<br>abled            | )                   |                       |                 |         |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>SPI2IE: SPI2<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt              | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en<br>Event Interrup<br>request enable<br>request not en | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>abled<br>ot Enable bit<br>ed<br>abled<br>pt Enable bit | )                   |                       |                 |         |  |  |  |  |  |

#### 7 4 2 ---

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

## REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit |

|-------|----------------------------------------------------|

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

0 = No write collision detected

| REGISTER         | R 9-3: PLLFE | BD: PLL FEE                     | DBACK DIV       | ISOR REGIS       | STER "           |                    |           |  |  |  |  |  |

|------------------|--------------|---------------------------------|-----------------|------------------|------------------|--------------------|-----------|--|--|--|--|--|

| U-0              | U-0          | U-0                             | U-0             | U-0              | U-0              | U-0                | R/W-0     |  |  |  |  |  |

|                  | —            | _                               | _               | —                | —                | _                  | PLLDIV<8> |  |  |  |  |  |

| bit 15           |              |                                 |                 |                  |                  |                    | bit 8     |  |  |  |  |  |

| R/W-0            | D/M/ O       |                                 |                 | R/W-0            | R/W-0            | R/W-0              |           |  |  |  |  |  |

| R/W-U            | R/W-0        | R/W-1                           | R/W-1           |                  | R/W-U            | R/W-U              | R/W-0     |  |  |  |  |  |

|                  |              |                                 | PLLD            | IV<7:0>          |                  |                    |           |  |  |  |  |  |

| bit 7            |              |                                 |                 |                  |                  |                    | bit C     |  |  |  |  |  |

|                  |              |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

| Legend:          |              |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

| R = Readable bit |              | W = Writable                    | bit             | U = Unimpler     | mented bit, read | l as '0'           |           |  |  |  |  |  |

| -n = Value a     | at POR       | '1' = Bit is set                |                 | '0' = Bit is cle | eared            | x = Bit is unknown |           |  |  |  |  |  |

|                  |              |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

| bit 15-9         | Unimplemen   | ted: Read as '                  | 0'              |                  |                  |                    |           |  |  |  |  |  |

| bit 8-0          | PLLDIV<8:0>  | >: PLL Feedba                   | ck Divisor bits | (also denoted    | as 'M', PLL mu   | ltiplier)          |           |  |  |  |  |  |

|                  | 111111111    | = 513                           |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | 000110000=   | 000110000 <b>= 50 (default)</b> |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | •            |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

|                  | 000000010 =  |                                 |                 |                  |                  |                    |           |  |  |  |  |  |

#### REGISTER 9-3-PLLEBD PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

00000001 = 3 000000000 = 2

Note 1: This register is reset only on a Power-on Reset (POR).

| REGISTERS     | 9-5: ACLI                                                                                                                                                 |                                                                                               | ARY CONT     | ROL REGIST             | ER               |                 |       |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|------------------------|------------------|-----------------|-------|--|--|--|--|--|

| U-0           | U-0                                                                                                                                                       | R/W-0                                                                                         | R/W-0        | R/W-0                  | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| _             | _                                                                                                                                                         | SELACLK                                                                                       | AOSCI        | CMD<1:0> APSTSCLR<2:0> |                  |                 |       |  |  |  |  |  |

| bit 15        |                                                                                                                                                           |                                                                                               |              |                        |                  |                 | bit 8 |  |  |  |  |  |

| R/W-0         | U-0                                                                                                                                                       | U-0                                                                                           | U-0          | U-0                    | U-0              | U-0             | U-0   |  |  |  |  |  |

| ASRCSEL       | 0-0                                                                                                                                                       | 0-0                                                                                           | 0-0          | 0-0                    | 0-0              | 0-0             | 0-0   |  |  |  |  |  |

| bit 7         | _                                                                                                                                                         | —                                                                                             |              |                        |                  | —               | bit   |  |  |  |  |  |

|               |                                                                                                                                                           |                                                                                               |              |                        |                  |                 | DIL   |  |  |  |  |  |

| Legend:       |                                                                                                                                                           |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                     | W = Writable I                                                                                | oit          | U = Unimpler           | mented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                       | '1' = Bit is set                                                                              |              | '0' = Bit is cle       | ared             | x = Bit is unkn | iown  |  |  |  |  |  |

|               |                                                                                                                                                           |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

| bit 15-14     | Unimpleme                                                                                                                                                 | ented: Read as '0                                                                             | )'           |                        |                  |                 |       |  |  |  |  |  |

| bit 13        | SELACLK: Select Auxiliary Clock Source for Auxiliary Clock Divider                                                                                        |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | •                                                                                                                                                         | y Oscillators prov                                                                            |              |                        | •                |                 |       |  |  |  |  |  |

| bit 12-11     | <ul> <li>0 = PLL output (Fosc) provides the source clock for the Auxiliary Clock Divider</li> <li>AOSCMD&lt;1:0&gt;: Auxiliary Oscillator Mode</li> </ul> |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 11 = EC External Clock Mode Select                                                                                                                        |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 10 = XT Oscillator Mode Select                                                                                                                            |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 01 = HS Oscillator Mode Select                                                                                                                            |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               |                                                                                                                                                           | 00 = Auxiliary Oscillator Disabled <b>APSTSCLR&lt;2:0&gt;:</b> Auxiliary Clock Output Divider |              |                        |                  |                 |       |  |  |  |  |  |

| bit 10-8      |                                                                                                                                                           |                                                                                               | Clock Output | Divider                |                  |                 |       |  |  |  |  |  |

|               |                                                                                                                                                           | 111 = divided by 1                                                                            |              |                        |                  |                 |       |  |  |  |  |  |

|               | 110 = divided by 2<br>101 = divided by 4                                                                                                                  |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 100 = divided by 8                                                                                                                                        |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 011 = divided by 16                                                                                                                                       |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

|               | 010 = divide                                                                                                                                              | •                                                                                             |              |                        |                  |                 |       |  |  |  |  |  |

|               | 001 = divide                                                                                                                                              | ed by 64<br>ed by 256 (defaul                                                                 | t)           |                        |                  |                 |       |  |  |  |  |  |

| bit 7         |                                                                                                                                                           | Select Reference                                                                              | ,            | e for Auxiliary        | Clock            |                 |       |  |  |  |  |  |

| ~             |                                                                                                                                                           | Oscillator is the                                                                             |              | •                      | 0.001            |                 |       |  |  |  |  |  |

|               |                                                                                                                                                           | y Oscillator is the                                                                           |              |                        |                  |                 |       |  |  |  |  |  |

|               | -                                                                                                                                                         |                                                                                               |              |                        |                  |                 |       |  |  |  |  |  |

# REGISTER 9-5: ACLKCON: AUXILIARY CONTROL REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

Unimplemented: Read as '0'

bit 6-0

| U-0                                | U-0                                                                                                                                                     | U-0                                                                                                                            | R/W-1                           | R/W-1              | R/W-1           | R/W-1           | R/W-1 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|-----------------|-----------------|-------|

| _                                  | —                                                                                                                                                       | —                                                                                                                              |                                 |                    | IC2R<4:0>       |                 |       |

| bit 15                             |                                                                                                                                                         |                                                                                                                                |                                 |                    |                 |                 | bit 8 |

| U-0                                | U-0                                                                                                                                                     | U-0                                                                                                                            | R/W-1                           | R/W-1              | R/W-1           | R/W-1           | R/W-1 |

| —                                  | _                                                                                                                                                       | _                                                                                                                              |                                 |                    | IC1R<4:0>       |                 |       |

| bit 7                              |                                                                                                                                                         |                                                                                                                                |                                 |                    |                 |                 | bit C |

|                                    |                                                                                                                                                         |                                                                                                                                |                                 |                    |                 |                 |       |

| Legend:                            |                                                                                                                                                         |                                                                                                                                |                                 |                    |                 |                 |       |

| R = Readab                         | le bit                                                                                                                                                  | W = Writable                                                                                                                   | bit                             | U = Unimpler       | mented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |                                                                                                                                                         |                                                                                                                                | '0' = Bit is cle                | x = Bit is unknown |                 |                 |       |

|                                    |                                                                                                                                                         | 1 Dit lo oot                                                                                                                   |                                 |                    | arcu            | X = Dit 15 unit |       |

|                                    |                                                                                                                                                         |                                                                                                                                |                                 |                    |                 |                 | 10111 |

| bit 15-13                          |                                                                                                                                                         | nted: Read as '                                                                                                                |                                 |                    |                 |                 |       |

|                                    | Unimpleme                                                                                                                                               |                                                                                                                                | 0'                              |                    |                 |                 |       |