Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp802t-i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

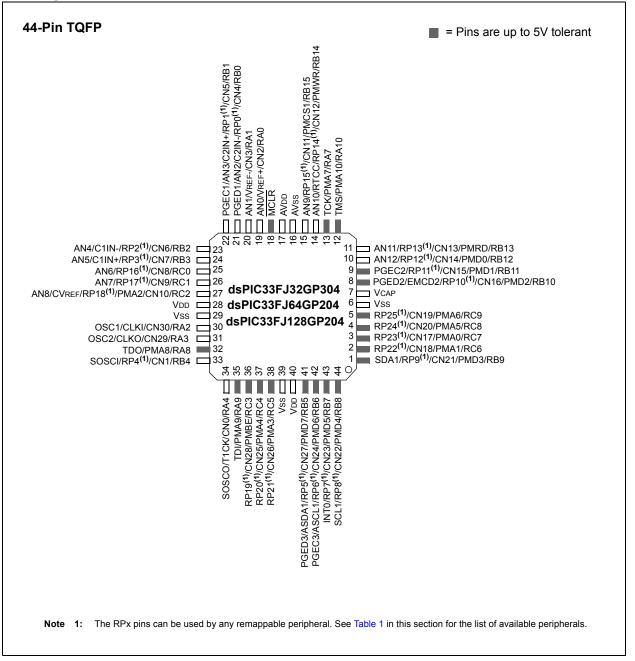

## Pin Diagrams (Continued)

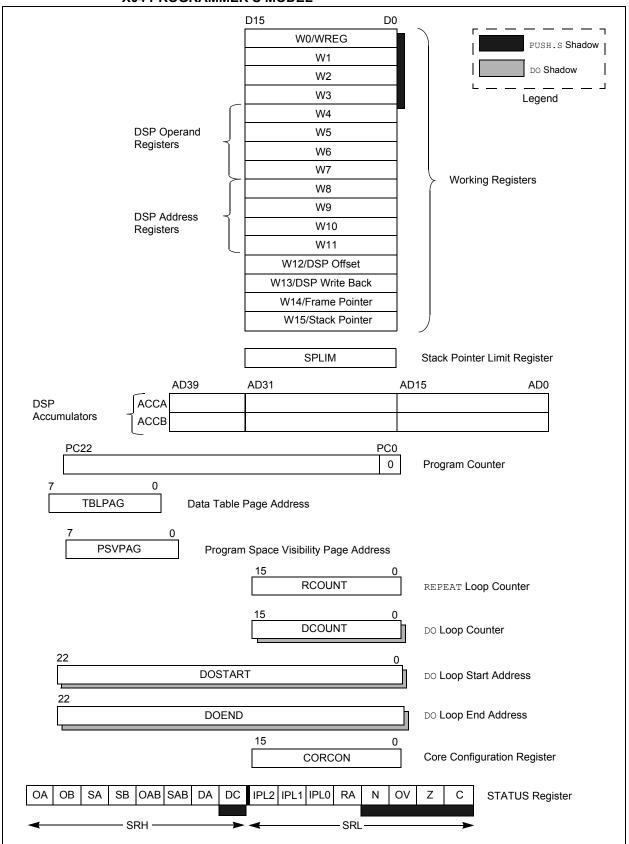

FIGURE 3-2: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 PROGRAMMER'S MODEL

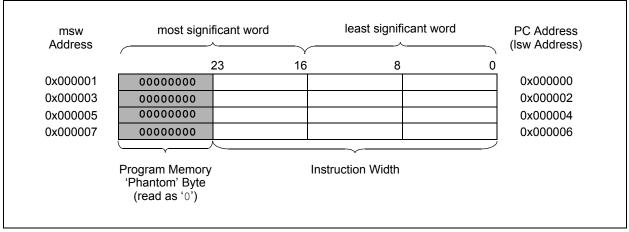

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

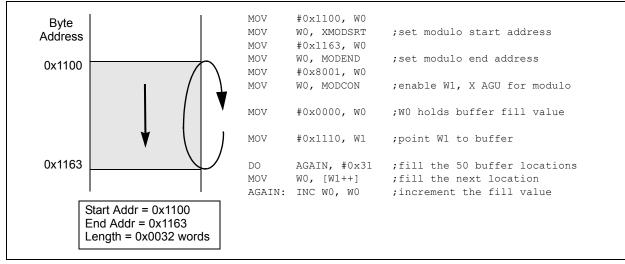

## 4.6 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

## FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

| REGISTER 7      | -5: IFS0:                                                                           | INTERRUPT                                                                           | FLAG STAT         | US REGISTI       | ER 0            |                 |               |  |  |

|-----------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|------------------|-----------------|-----------------|---------------|--|--|

| U-0             | R/W-0                                                                               | R/W-0                                                                               | R/W-0             | R/W-0            | R/W-0           | R/W-0           | R/W-0         |  |  |

|                 | DMA1IF                                                                              | AD1IF                                                                               | U1TXIF            | U1RXIF           | SPI1IF          | SPI1EIF         | T3IF          |  |  |

| bit 15          |                                                                                     |                                                                                     |                   |                  |                 |                 | bit 8         |  |  |

| R/W-0           | R/W-0                                                                               | R/W-0                                                                               | R/W-0             | R/W-0            | R/W-0           | R/W-0           | R/W-0         |  |  |

| T2IF            | OC2IF                                                                               | IC2IF                                                                               | DMA0IF            | T1IF             | OC1IF           | IC1IF           | <b>INT0IF</b> |  |  |

| bit 7           |                                                                                     |                                                                                     |                   |                  |                 |                 | bit 0         |  |  |

| Legend:         |                                                                                     |                                                                                     |                   |                  |                 |                 |               |  |  |

| R = Readable    | bit                                                                                 | W = Writable                                                                        | bit               | U = Unimplei     | mented bit, rea | d as '0'        |               |  |  |

| -n = Value at F | POR                                                                                 | '1' = Bit is se                                                                     | t                 | '0' = Bit is cle | eared           | x = Bit is unkn | own           |  |  |

| hit 1E          | Unimplana                                                                           | nted. Dood oo                                                                       | · • '             |                  |                 |                 |               |  |  |

| bit 15          | -                                                                                   | nted: Read as                                                                       |                   |                  |                 | 1.11            |               |  |  |

| bit 14          |                                                                                     | /A Channel 1 E                                                                      |                   | complete Interi  | upt Flag Status | s bit           |               |  |  |

|                 | •                                                                                   | request has ou<br>request has no                                                    |                   |                  |                 |                 |               |  |  |

| bit 13          | -                                                                                   | 1 Conversion (                                                                      |                   | rupt Flag Statu  | s bit           |                 |               |  |  |

|                 |                                                                                     | request has or                                                                      | •                 | -p               |                 |                 |               |  |  |

|                 |                                                                                     | request has no                                                                      |                   |                  |                 |                 |               |  |  |

| bit 12          | U1TXIF: UA                                                                          | RT1 Transmitte                                                                      | er Interrupt Flag | g Status bit     |                 |                 |               |  |  |

|                 |                                                                                     | request has ou<br>request has no                                                    |                   |                  |                 |                 |               |  |  |

| bit 11          | U1RXIF: UA                                                                          | RT1 Receiver                                                                        | nterrupt Flag S   | Status bit       |                 |                 |               |  |  |

|                 | •                                                                                   | request has or<br>request has no                                                    |                   |                  |                 |                 |               |  |  |

| bit 10          |                                                                                     | 1 Event Interrup                                                                    |                   | bit              |                 |                 |               |  |  |

|                 |                                                                                     | request has o                                                                       |                   |                  |                 |                 |               |  |  |

| L:1 0           |                                                                                     | request has no                                                                      |                   | L 14             |                 |                 |               |  |  |

| bit 9           | SPI1EIF: SPI1 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                                                     |                   |                  |                 |                 |               |  |  |

|                 |                                                                                     | request has of                                                                      |                   |                  |                 |                 |               |  |  |

| bit 8           |                                                                                     | 3 Interrupt Flag                                                                    |                   |                  |                 |                 |               |  |  |

|                 | 1 = Interrupt                                                                       | request has or<br>request has no                                                    | curred            |                  |                 |                 |               |  |  |

| bit 7           | -                                                                                   | -                                                                                   |                   |                  |                 |                 |               |  |  |

| bit i           |                                                                                     | <b>T2IF:</b> Timer2 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                   |                  |                 |                 |               |  |  |

|                 |                                                                                     | request has no                                                                      |                   |                  |                 |                 |               |  |  |

| bit 6           | OC2IF: Outp                                                                         | out Compare Cl                                                                      | nannel 2 Interro  | upt Flag Status  | s bit           |                 |               |  |  |

|                 |                                                                                     | request has ou<br>request has no                                                    |                   |                  |                 |                 |               |  |  |

| bit 5           | IC2IF: Input                                                                        | Capture Chann                                                                       | nel 2 Interrupt F | -lag Status bit  |                 |                 |               |  |  |

|                 |                                                                                     | request has ou<br>request has no                                                    |                   |                  |                 |                 |               |  |  |

| bit 4           | -                                                                                   | /IA Channel 0 E                                                                     |                   | Complete Interr  | upt Flag Status | s bit           |               |  |  |

|                 | 1 = Interrupt                                                                       | request has or<br>request has no                                                    | curred            | •                |                 |                 |               |  |  |

| bit 3           | -                                                                                   | 1 Interrupt Flag                                                                    |                   |                  |                 |                 |               |  |  |

|                 |                                                                                     | request has or                                                                      |                   |                  |                 |                 |               |  |  |

|                 |                                                                                     | request has no                                                                      |                   |                  |                 |                 |               |  |  |

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0                   | R/W-0                                                                                                     | U-0                                     | U-0             | U-0                      | U-0              | U-0             | U-0   |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|--------------------------|------------------|-----------------|-------|--|--|

| DAC1LIE <sup>(2)</sup>  | DAC1RIE <sup>(2)</sup>                                                                                    | _                                       | _               | —                        | —                | —               |       |  |  |

| bit 15                  |                                                                                                           |                                         |                 |                          |                  |                 | bit   |  |  |

|                         |                                                                                                           |                                         |                 |                          |                  |                 |       |  |  |

| U-0                     | R/W-0                                                                                                     | R/W-0                                   | R/W-0           | R/W-0                    | R/W-0            | R/W-0           | U-0   |  |  |

| —                       | C1TXIE <sup>(1)</sup>                                                                                     | DMA7IE                                  | DMA6IE          | CRCIE                    | U2EIE            | U1EIE           | —     |  |  |

| bit 7                   |                                                                                                           |                                         |                 |                          |                  |                 | bit   |  |  |

| Lowandi                 |                                                                                                           |                                         |                 |                          |                  |                 |       |  |  |

| Legend:<br>R = Readable | , hit                                                                                                     | \\/ = \\/ritabla                        | hit             | II – Unimplor            | monted hit read  |                 |       |  |  |

| -n = Value at           |                                                                                                           | W = Writable<br>'1' = Bit is set        |                 | '0' = Bit is cle         | mented bit, read | x = Bit is unkn | 0.000 |  |  |

|                         | FUR                                                                                                       |                                         | L               |                          | aleu             |                 |       |  |  |

| bit 15                  | DAC1LIE: DA                                                                                               | C Left Channe                           | el Interrupt En | able bit <sup>(2)</sup>  |                  |                 |       |  |  |

|                         | 1 = Interrupt r                                                                                           |                                         |                 |                          |                  |                 |       |  |  |

|                         | 0 = Interrupt r                                                                                           | •                                       |                 |                          |                  |                 |       |  |  |

| bit 14                  | DAC1RIE: DA                                                                                               |                                         |                 | nable bit <sup>(2)</sup> |                  |                 |       |  |  |

|                         | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>              |                                         |                 |                          |                  |                 |       |  |  |

| bit 13-7                | Unimplement                                                                                               | •                                       |                 |                          |                  |                 |       |  |  |

| bit 6                   | •                                                                                                         |                                         |                 | ntorrunt Enabl           | o hit(1)         |                 |       |  |  |

|                         | C1TXIE: ECAN1 Transmit Data Request Interrupt Enable bit <sup>(1)</sup><br>1 = Interrupt request occurred |                                         |                 |                          |                  |                 |       |  |  |

|                         |                                                                                                           | equest not occ                          |                 |                          |                  |                 |       |  |  |

| bit 5                   | DMA7IE: DM                                                                                                | A Channel 7 D                           | ata Transfer C  | Complete Interr          | upt Enable bit   |                 |       |  |  |

|                         |                                                                                                           | equest enable                           |                 |                          |                  |                 |       |  |  |

|                         | -                                                                                                         | equest not en                           |                 |                          |                  |                 |       |  |  |

| bit 4                   |                                                                                                           |                                         |                 | Complete Interr          | upt Enable bit   |                 |       |  |  |

|                         | 1 = Interrupt r<br>0 = Interrupt r                                                                        | equest enable                           |                 |                          |                  |                 |       |  |  |

| bit 3                   | •                                                                                                         | •                                       |                 | oit                      |                  |                 |       |  |  |

| DIL 3                   | CRCIE: CRC Generator Interrupt Enable bit<br>1 = Interrupt request enabled                                |                                         |                 |                          |                  |                 |       |  |  |

|                         | 0 = Interrupt request not enabled                                                                         |                                         |                 |                          |                  |                 |       |  |  |

| bit 2                   | U2EIE: UART                                                                                               | U2EIE: UART2 Error Interrupt Enable bit |                 |                          |                  |                 |       |  |  |

|                         | 1 = Interrupt request enabled                                                                             |                                         |                 |                          |                  |                 |       |  |  |

|                         | 0 = Interrupt r                                                                                           | equest not en                           | abled           |                          |                  |                 |       |  |  |

| bit 1                   | U1EIE: UART                                                                                               |                                         | -               |                          |                  |                 |       |  |  |

|                         | 1 = Interrupt r<br>0 = Interrupt r                                                                        | equest enable                           |                 |                          |                  |                 |       |  |  |

|                         |                                                                                                           |                                         |                 |                          |                  |                 |       |  |  |

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

2: Interrupts are disabled on devices without Audio DAC modules.

| U-0         | U-0                                                                                              | U-0                                                                                              | U-0                          | R-1               | R-1              | R-1             | R-1   |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _           | _                                                                                                | _                                                                                                | _                            | - LSTCH<3:0>      |                  |                 |       |  |  |  |  |

| oit 15      | ·                                                                                                |                                                                                                  |                              |                   |                  |                 | bit   |  |  |  |  |

|             |                                                                                                  |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

| R-0         | R-0                                                                                              | R-0                                                                                              | R-0                          | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

| PPST7       | PPST6                                                                                            | PPST5                                                                                            | PPST4                        | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |

| pit 7       |                                                                                                  |                                                                                                  |                              |                   |                  |                 | bit   |  |  |  |  |

| _egend:     |                                                                                                  |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

| R = Readab  | le bit                                                                                           | W = Writable                                                                                     | bit                          | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |

| n = Value a | t POR                                                                                            | '1' = Bit is se                                                                                  | t                            | '0' = Bit is clea |                  | x = Bit is unki | nown  |  |  |  |  |

|             |                                                                                                  |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

| bit 15-12   | Unimplemen                                                                                       |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

| oit 11-8    |                                                                                                  |                                                                                                  | nannel Active I              |                   |                  |                 |       |  |  |  |  |

|             | 1111 = No DI<br>1110-1000 =                                                                      |                                                                                                  | as occurred sir              | ice system Res    | et               |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  | as by DMA Cł                 | nannel 7          |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  | as by DMA Ch                 |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  | 0101 = Last data transfer was by DMA Channel 5<br>0100 = Last data transfer was by DMA Channel 4 |                              |                   |                  |                 |       |  |  |  |  |

|             | 0011 = Last data transfer was by DMA Channel 3<br>0010 = Last data transfer was by DMA Channel 2 |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  | as by DMA Cr<br>as by DMA Cr |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  | as by DMA Cl                 |                   |                  |                 |       |  |  |  |  |

| oit 7       |                                                                                                  |                                                                                                  | -                            |                   |                  |                 |       |  |  |  |  |

|             | PPST7: Channel 7 Ping-Pong Mode Status Flag bit<br>1 = DMA7STB register selected                 |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA7STA                                                                                      | •                                                                                                |                              |                   |                  |                 |       |  |  |  |  |

| oit 6       | PPST6: Chan                                                                                      | PPST6: Channel 6 Ping-Pong Mode Status Flag bit                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 1 = DMA6STE<br>0 = DMA6STA                                                                       | U U                                                                                              |                              |                   |                  |                 |       |  |  |  |  |

| bit 5       | PPST5: Chan                                                                                      | PPST5: Channel 5 Ping-Pong Mode Status Flag bit                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 1 = DMA5STB register selected                                                                    |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA5STA                                                                                      |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

| oit 4       | PPST4: Chan                                                                                      | inel 4 Ping-Po                                                                                   | ng Mode Statu                | ıs Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA4STB register selected                                                                    |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA4STA                                                                                      | -                                                                                                |                              |                   |                  |                 |       |  |  |  |  |

| oit 3       | <b>PPST3:</b> Channel 3 Ping-Pong Mode Status Flag bit                                           |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  | •                                                                                                |                              |                   |                  |                 |       |  |  |  |  |

| oit 2       | 0 = DMA3STA register selected PDST2: Channel 2 Ping-Pong Mode Status Flag bit                    |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | PPST2: Channel 2 Ping-Pong Mode Status Flag bit<br>1 = DMA2STB register selected                 |                                                                                                  |                              |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA2STA                                                                                      | •                                                                                                |                              |                   |                  |                 |       |  |  |  |  |

| oit 1       |                                                                                                  | -                                                                                                | ng Mode Statu                | ıs Flaq bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA1STE                                                                                      | -                                                                                                | -                            | ie i i i g i i i  |                  |                 |       |  |  |  |  |

|             | 0 = DMA1STA                                                                                      | -                                                                                                |                              |                   |                  |                 |       |  |  |  |  |

| bit 0       | PPST0: Chan                                                                                      | -                                                                                                |                              | e Elaa bit        |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                                                                  | ng moue olait                | is riay bit       |                  |                 |       |  |  |  |  |

| JILU        | 1 = DMA0STE                                                                                      | -                                                                                                | -                            | is Flag bit       |                  |                 |       |  |  |  |  |

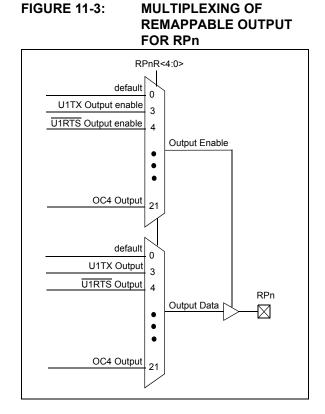

#### 11.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 11-17 through Register 11-29). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

#### Function RPnR<4:0> **Output Name** NULL RPn tied to default port pin 00000 C10UT RPn tied to Comparator1 Output 00001 C2OUT RPn tied to Comparator2 Output 00010 U1TX 00011 RPn tied to UART1 Transmit **U1RTS** 00100 RPn tied to UART1 Ready To Send U2TX RPn tied to UART2 Transmit 00101 U2RTS 00110 RPn tied to UART2 Ready To Send SDO1 RPn tied to SPI1 Data Output 00111 SCK1 01000 RPn tied to SPI1 Clock Output SS1 01001 RPn tied to SPI1 Slave Select Output SDO2 RPn tied to SPI2 Data Output 01010 RPn tied to SPI2 Clock Output SCK2 01011 SS2 RPn tied to SPI2 Slave Select Output 01100 CSDO 01101 RPn tied to DCI Serial Data Output CSCK RPn tied to DCI Serial Clock Output 01110 COFS RPn tied to DCI Frame Sync Output 01111 C1TX 10000 RPn tied to ECAN1 Transmit OC1 RPn tied to Output Compare 1 10010 OC2 RPn tied to Output Compare 2 10011 OC3 RPn tied to Output Compare 3 10100

RPn tied to Output Compare 4

## TABLE 11-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

10101

OC4

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0           | U-0                                                        | U-0                               | R/W-1 | R/W-1                | R/W-1            | R/W-1              | R/W-1 |

|---------------|------------------------------------------------------------|-----------------------------------|-------|----------------------|------------------|--------------------|-------|

| —             | _                                                          | —                                 |       |                      | IC8R<4:0>        |                    |       |

| bit 15        | ·                                                          | ·                                 |       |                      |                  |                    | bit 8 |

| U-0           | U-0                                                        | U-0                               | R/W-1 | R/W-1                | R/W-1            | R/W-1              | R/W-1 |

|               | —                                                          | _                                 |       |                      | IC7R<4:0>        |                    |       |

| bit 7         |                                                            |                                   |       |                      |                  |                    | bit ( |

| Legend:       |                                                            |                                   |       |                      |                  |                    |       |

| R = Readabl   | e bit                                                      | W = Writable                      | bit   | U = Unimpler         | mented bit, read | l as '0'           |       |

| -n = Value at | POR                                                        | '1' = Bit is se                   | t     | '0' = Bit is cleared |                  | x = Bit is unknown |       |

| bit 12-8      | 11111 = Inpu<br>11001 = Inpu<br>•<br>•<br>•<br>•<br>•<br>• | it tied to Vss<br>it tied to RP25 |       |                      | onding RPn pin   |                    |       |

|               | 00000 <b>= Inpu</b>                                        | it tied to RP0                    |       |                      |                  |                    |       |

| bit 7-5       | Unimplemen                                                 |                                   |       |                      |                  |                    |       |

| bit 4-0       | IC7R<4:0>: A<br>11111 = Inpu<br>11001 = Inpu               | it tied to Vss                    |       | to the correspo      | onding RPn pin   |                    |       |

## REGISTER 11-6: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

00001 = Input tied to RP1 00000 = Input tied to RP0

•

## 12.1 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter |

|-------|-----------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                               |

|       | http://www.microchip.com/wwwproducts/                                                   |

|       | Devices.aspx?dDocName=en532311                                                          |

#### 12.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

## 14.1 Input Capture Resources

Many useful resources related to Input Capture are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

#### 14.1.1 KEY RESOURCES

- Section 12. "Input Capture" (DS70198)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                               | U-0 | U-0              | U-0 | U-0                                     | U-0              | U-0      | U-0   |

|-----------------------------------|-----|------------------|-----|-----------------------------------------|------------------|----------|-------|

| —                                 | —   | —                | —   | —                                       | —                | —        | —     |

| bit 15                            |     | ·                |     |                                         |                  |          | bit 8 |

|                                   |     |                  |     |                                         |                  |          |       |

| U-0                               | U-0 | U-0              | U-0 | U-0                                     | R/W-0            | R/W-0    | R/W-0 |

| —                                 | —   | —                | —   | —                                       | DMABL<2:0>       |          |       |

| bit 7                             |     |                  |     |                                         | bit 0            |          |       |

|                                   |     |                  |     |                                         |                  |          |       |

| Legend:                           |     |                  |     |                                         |                  |          |       |

| R = Readable bit W = Writable bit |     |                  | bit | U = Unimpler                            | mented bit, read | d as '0' |       |

| -n = Value at P                   | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |          | nown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

$\tt 001$  = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                        |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                                |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

# 30.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 electrical characteristics. Additional information is provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$      | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | -0.3V to 3.6V        |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                       |                      |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA                |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     |                      |

| Maximum current sunk by all ports                                                 |                      |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

## TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                    |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                         |

|--------------------|--------------------|---------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|-------------------------|

| Param<br>No.       | Symbol             | Characteristic                                                      | Min                                                   | Тур <sup>(1)</sup> | Max | Units | Conditions              |

| Operating Voltage  |                    |                                                                     |                                                       |                    |     |       |                         |

| DC10               | C10 Supply Voltage |                                                                     |                                                       |                    |     |       |                         |

|                    | Vdd                |                                                                     | 3.0                                                   | _                  | 3.6 | V     | Industrial and Extended |

| DC12               | Vdr                | RAM Data Retention Voltage <sup>(2)</sup>                           | 1.8                                                   | _                  | —   | V     | _                       |

| DC16               | VPOR               | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                     | _                  | Vss | V     | _                       |

| DC17               | SVDD               | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.03                                                  | _                  | —   | V/ms  | 0-3.0V in 0.1s          |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

| TABLE 30-8: DC CHARACTERISTICS: DOZE CORRENT (IDOZE) |                        |     |               |                                                       |            |          |           |  |

|------------------------------------------------------|------------------------|-----|---------------|-------------------------------------------------------|------------|----------|-----------|--|

| DC CHARACTERISTICS                                   |                        |     |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |          |           |  |

| Parameter No.                                        | Typical <sup>(1)</sup> | Мах | Doze<br>Ratio | Units                                                 | Conditions |          |           |  |

| DC73a                                                | 20                     | 50  | 1:2           | mA                                                    |            |          |           |  |

| DC73f                                                | 17                     | 30  | 1:64          | mA                                                    | -40°C      | 3.3V     | 40 MIPS   |  |

| DC73g                                                | 17                     | 30  | 1:128         | mA                                                    |            |          |           |  |

| DC70a                                                | 20                     | 50  | 1:2           | mA                                                    |            | 3.3V     |           |  |

| DC70f                                                | 17                     | 30  | 1:64          | mA                                                    | +25°C      |          | 40 MIPS   |  |

| DC70g                                                | 17                     | 30  | 1:128         | mA                                                    |            |          |           |  |

| DC71a                                                | 20                     | 50  | 1:2           | mA                                                    |            |          | / 40 MIPS |  |

| DC71f                                                | 17                     | 30  | 1:64          | mA                                                    | +85°C      | 3.3V     |           |  |

| DC71g                                                | 17                     | 30  | 1:128         | mA                                                    |            |          |           |  |

| DC72a                                                | 21                     | 50  | 1:2           | mA                                                    |            |          |           |  |

| DC72f                                                | 18                     | 30  | 1:64          | mA                                                    | +125°C     | 5°C 3.3V | 40 MIPS   |  |

| DC72g                                                | 18                     | 30  | 1:128         | mA                                                    |            |          |           |  |

## TABLE 30-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** Data in the Typical column is at 3.3V, 25°C unless otherwise stated.

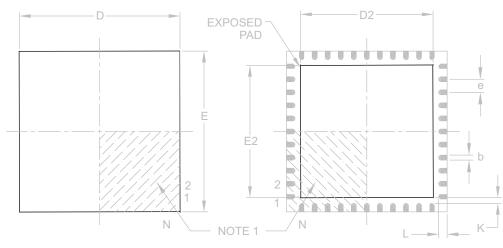

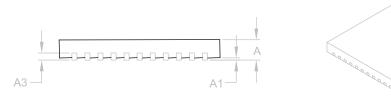

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

**BOTTOM VIEW**

|                        | Units       | MILLIMETERS |      |      |  |

|------------------------|-------------|-------------|------|------|--|

| Dimens                 | sion Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | Ν           | 44          |      |      |  |

| Pitch                  | е           | 0.65 BSC    |      |      |  |

| Overall Height         | Α           | 0.80        | 0.90 | 1.00 |  |

| Standoff               | A1          | 0.00        | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF    |      |      |  |

| Overall Width          | E           | 8.00 BSC    |      |      |  |

| Exposed Pad Width      | E2          | 6.30        | 6.45 | 6.80 |  |

| Overall Length         | D           | 8.00 BSC    |      |      |  |

| Exposed Pad Length     | D2          | 6.30        | 6.45 | 6.80 |  |

| Contact Width          | b           | 0.25        | 0.30 | 0.38 |  |

| Contact Length         | L           | 0.30        | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20        | -    | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

| Section Name                                 | Update Description                                                                                                                                                                 |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Section 30.0 "Electrical<br>Characteristics" | Updated Typical values for Thermal Packaging Characteristics (see Table 30-3).                                                                                                     |  |  |

|                                              | Updated Min and Max values for parameter DC12 (RAM Data Retention Voltage) and added Note 4 (see Table 30-4).                                                                      |  |  |

|                                              | Updated Power-Down Current Max values for parameters DC60b and DC60c (see Table 30-7).                                                                                             |  |  |

|                                              | Updated Characteristics for I/O Pin Input Specifications and added parameter DI21 (see Table 30-9).                                                                                |  |  |

|                                              | Updated Program Memory values for parameters 136, 137, and 138<br>(renamed to 136a, 137a, and 138a), added parameters 136b, 137b, and<br>138b, and added Note 2 (see Table 30-12). |  |  |

|                                              | Added parameter OS42 (Gм) to the External Clock Timing Requirements (see Table 30-16).                                                                                             |  |  |

|                                              | Updated Watchdog Timer Time-out Period parameter SY20 (see Table 30-21).                                                                                                           |  |  |

|                                              | Updated the IREF Current Drain parameter AD08 (see Table 30-37).                                                                                                                   |  |  |

|                                              | Updated parameters AD30a, AD31a, AD32a, AD33a, and AD34a (see<br>Table 30-38)                                                                                                      |  |  |

|                                              | Updated parameters AD30b, AD31b, AD32b, AD33b, and AD34b (see Table 30-39)                                                                                                         |  |  |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Tape and Reel FI<br>Temperature Rar | amily -<br>y Size (<br><br>ag (if a<br>nge | (KB)        |                                                                                                                                                                                                                                                                                 | Examples:<br>a) dsPIC33FJ32GP302-E/SP:<br>General Purpose dsPIC33, 32 KB program<br>memory, 28-pin, Extended temperature,<br>SPDIP package. |

|-------------------------------------|--------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture:                       | 33                                         | =           | 16-bit Digital Signal Controller                                                                                                                                                                                                                                                |                                                                                                                                             |

| Flash Memory Family:                | FJ                                         | =           | Flash program memory, 3.3V                                                                                                                                                                                                                                                      |                                                                                                                                             |

| Product Group:                      | GP3                                        | =           | General Purpose family<br>General Purpose family<br>General Purpose family                                                                                                                                                                                                      |                                                                                                                                             |

| Pin Count:                          | 02<br>04                                   | =           | 28-pin<br>44-pin                                                                                                                                                                                                                                                                |                                                                                                                                             |

| Temperature Range:                  | I<br>E<br>H                                | =<br>=<br>= | -40° C to+85° C (Industrial)<br>-40° C to+125° C (Extended)<br>-40° C to+150° C (High)                                                                                                                                                                                          |                                                                                                                                             |

| Package:                            | SP<br>SO<br>ML<br>MM<br>PT                 | =<br>=<br>= | Skinny Plastic Dual In-Line - 300 mil body (SPDIP)<br>Plastic Small Outline - Wide - 7.5 mil body (SOIC)<br>Plastic Quad, No Lead Package - 8x8 mm body (QFN)<br>Plastic Quad, No Lead Package - 6x6x0.9 mm body (QFN-S)<br>Plastic Thin Quad Flatpack - 10x10x1 mm body (TQFP) |                                                                                                                                             |

٦